1

Изобретение относится к вычислительной технике и может быть использовано при дистанционных исследваниях природных ресурсов Земли, в геологии, медицине, при неразрушающем контроле качества изделий.

Цель изобретения - повышение помхоустойчивости отображения видеоинформации .

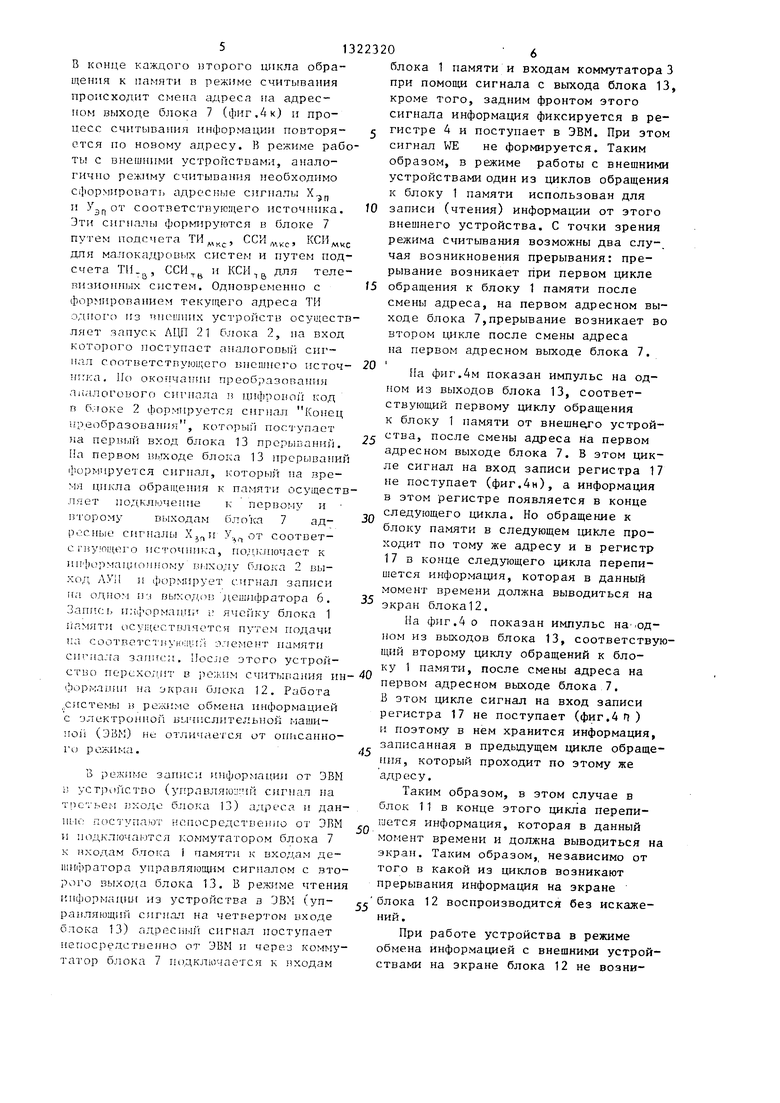

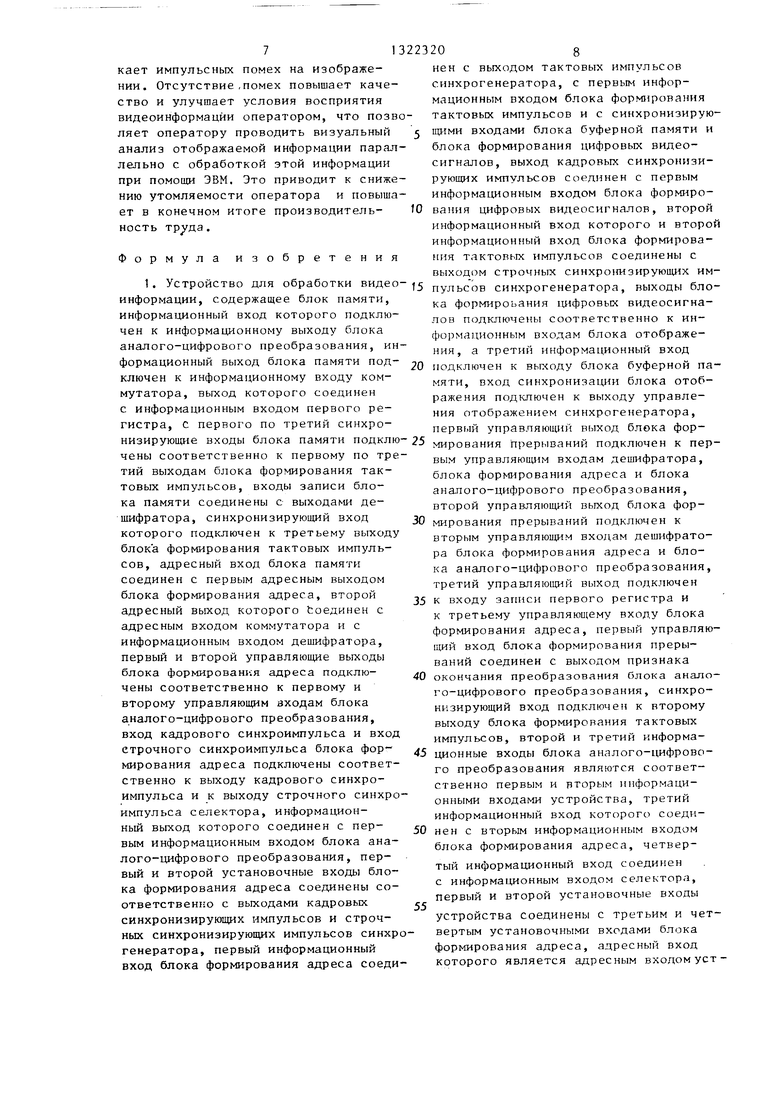

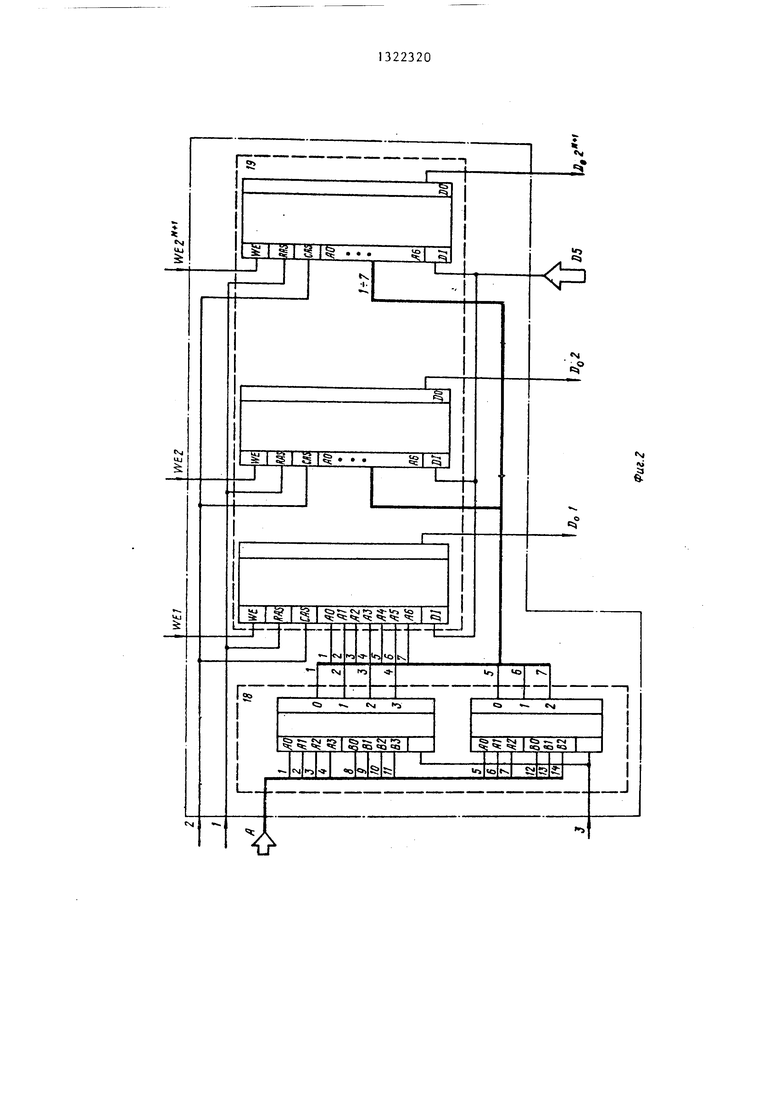

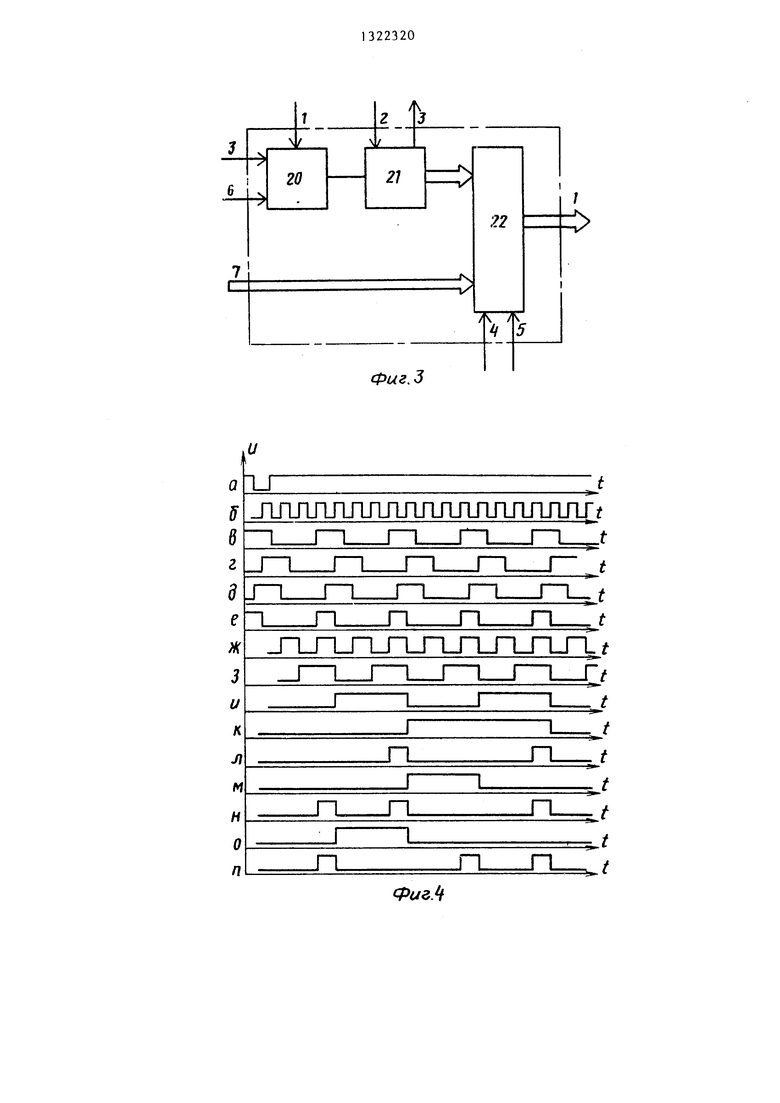

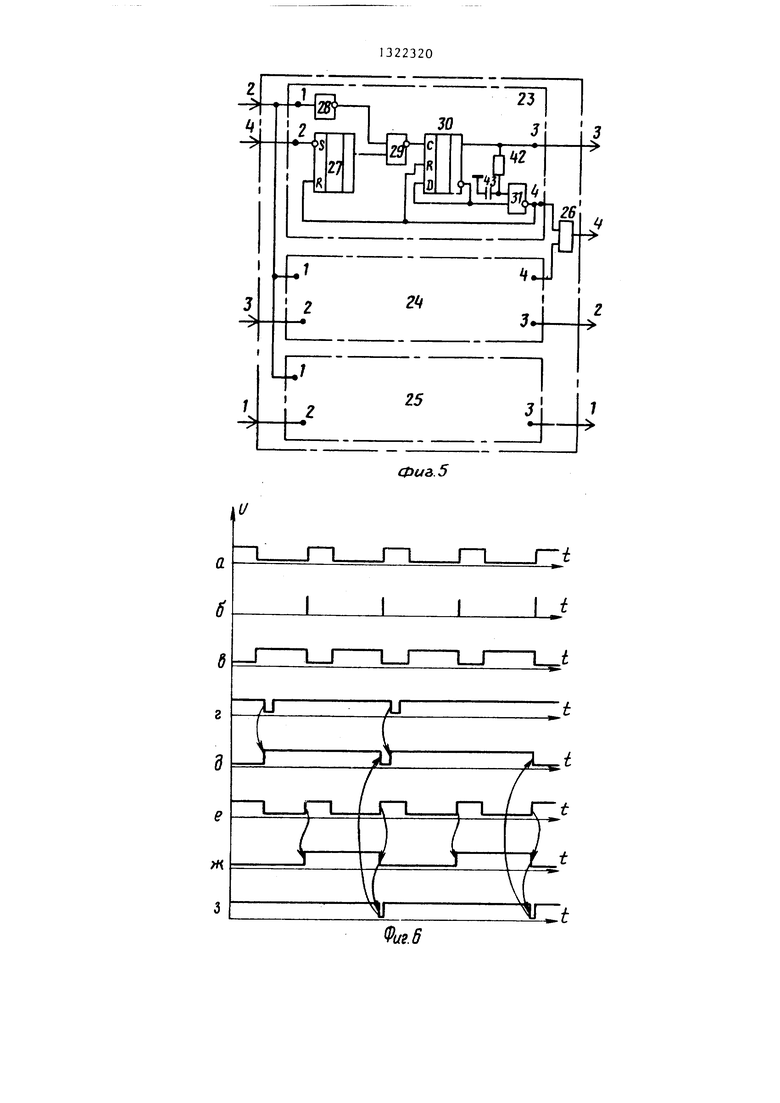

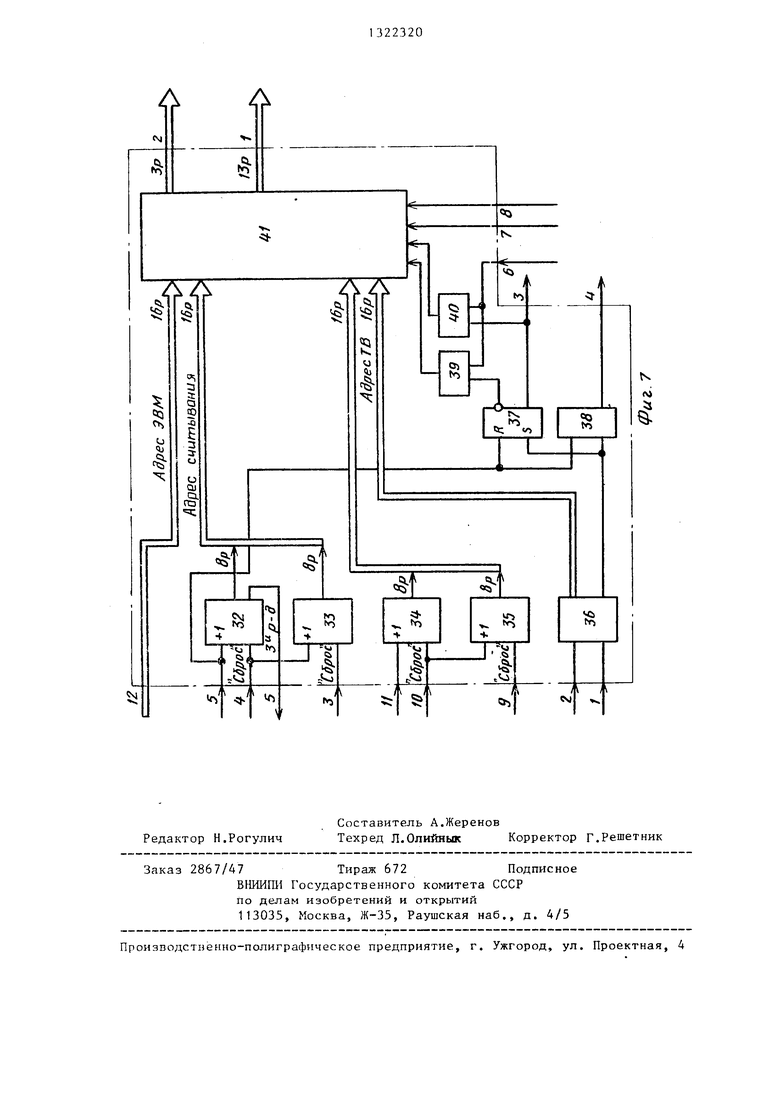

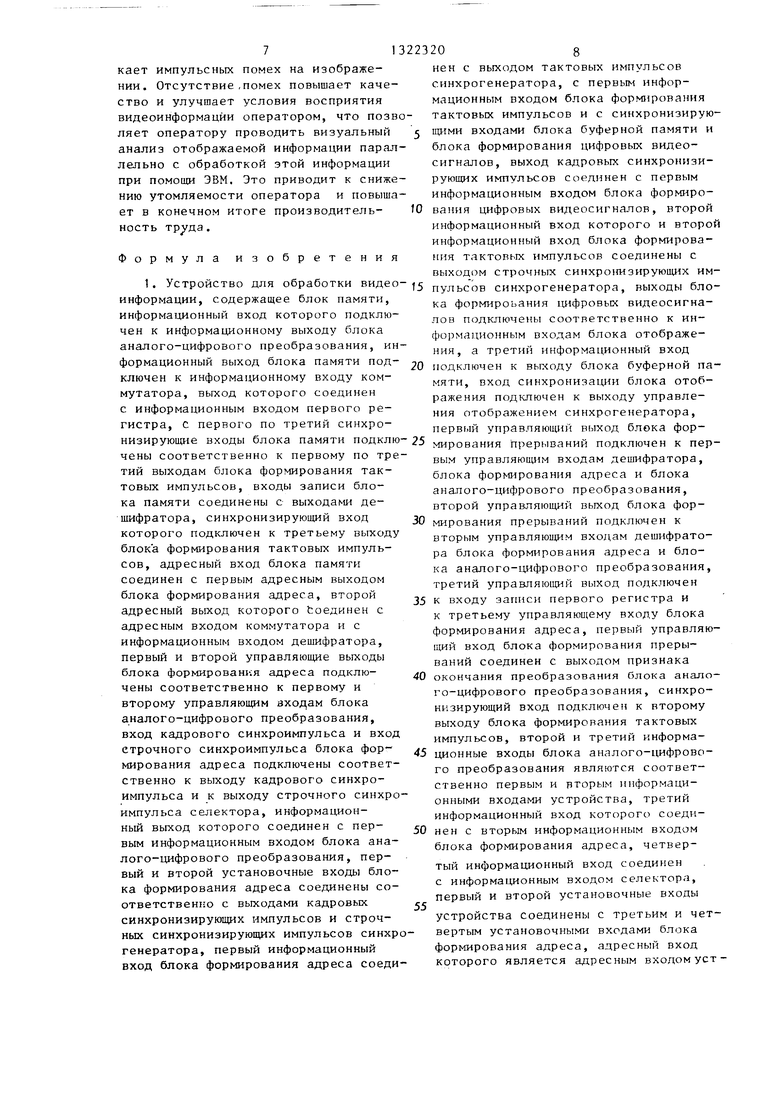

На фиг.1 приведена функциональна схема устройства; на фиг,2 - принципиальная схема блока памяти; на фиг.З - фуикц юнапьная схема блока цифроапалогового преобразования-, на фиг.А - временные диаграммы работы в считывания информации и в режиме обмс); иН ;ормацией с вненими ycтpoйcтIзa iи на фиг.З - принц схема блока прерываний;

на (|)иг.6 - временные диаграммы рабо

блока прерыва} ий; на фиг. 7 - функциональная схема блока формировг1Н11я адреса .

Устройство содержит блок 1 памяти блок 2 аналого-цифрового преобразования, коммутатор 3, регистр 4, блок 5 формирования тактовых импульсов, деип1фратор 6, блок 7 формиро- iKiiniH адреса, селектор 8, синхрогене ратор 9, блок 10 формирования циф- poBiiix -зидеосигналов, 11 буферной , блок 12 отображения, блок 13 (1)ормирован .1я прерываний, э.иемепты 51 14 и 15, элемент НЛИ-НЕ 16 регистр 17, мул1/1 И1локсо з 18, эле- MPiiTi i 19 памяти, ке)мму 1 а ; ор 20 анало Г опмх сигналов, аншюго-цифровой ирооб1)азо затель (ЛИИ) 21, коммутатор 22 ви;г,)орма1г,, узлы 23-25 прерызани; , элемент ИЛИ 26, триггер 27, элемент НЕ 28, элемент И--ПЕ 29, ч риггер 30, элег.1ент И-НЕ 31 счетчики 32-35 коо;)динат, узел 36 задания адреса, триггер 37, элемент ИЛИ 38, элементы И 39 и 40, коммутатор 41, резистор 42 конденсатор 43. I

IjjioK 10 состоит, например, из узла цветового кодирования, узла фор- мпроиация метки и трех цифроаналого- вых преобразователей. Работа узла цветового кодирования основана на сравнении текущего цифрового видео- е;1гвала, поступающего с выхода блока 11 с М пopoгoвы И уровнями, в преобразовании выходного кода схемы сравнения с помощью шифратора в три цч|1эровых видеосигнала с иоследуяжи-ш

3223202

преобразованием этих сигналов в три аналоговых видеосигнала, которые и поступают на соответствующие входы блока 12.

Узел формирования цветовой шкалы формирует в нижней части экрана блока 12 закон цветового кодирования. Цифрознаковый генератор формирует и правой части экрана значения пороговых уровней, заданных в схеме цветового кодирования. Узел формирования метки формирует на экране блока 12 метку в виде мигающей точки, которая мозкет перемещаться. Значение информации, хранящейся в ячейке блока 1 памяти, имеющей адрес, соответствующий координатам метки, выводится через цифрознако- вый генератор на экран блока 12.

10

15

О Блок

5

0

5

0

5

0

5

выполнен на сдвиговых регистрах с параллельной записью, параллельная запись и сдвиг информации осуществляются по отрицательному фронту ТИ, а выбор режима (параллельная запись или сдвиг) определяется сигналом на входе управления .

Блок 12 представляет собой, например, стандартное устройство типа ВК51Ц61, ВК59Ц60, ВКАОЦбО, которыми оснащены телецентры страны, или специальный манитор. Входящий, например в ЭВМ Электроника-85.

Блок 13 предназначен для выделе- мия полного цикла при асинхронном обращении к блоку 1 памяти от внещних устройств. Принципиальная схема для формирования импульсов, соответствующих циклу обращения от одного из внещних источников, приведена на фиг.З, а временные диаграммы работы данной схемы - на фиг.6. Сигнал управления (фиг.6 г) поступает от одного из внешних источников к входам 1,3 и А, по которым происходит выделение цикла. На фиг.6 показан сигнал управления на.втором входе блока 13, а на фиг.6 - границы циклов обращения к блоку 1 памяти. Сигнал, управления, приходящий от одного из внешних источников (фиг.6 г ), поступает на установочный вход триггера 27 и устанавливает его (фиг.6).

Сигнал с выхода триггера 27 разрешает прохождение инвертированного сигнала (фиг.бЬ) через элемент И-НЕ 29 (фиг.6 е ). Сигнал с выхода этого элемента поступает на счетный

31

вход триггера 30 и переключает его положительными перепадами (фиг.бж ). На элементе И-НЕ 31 вьтолнен формирователь импульсов из положительных перепадов на инверсном выходе триггера 30 (фиг.6 J ), Этот импульс сбрасывает триггеры 27 и 30 в исходное состояние и прекращает работу блока до прихода следующего импульса запуска. Этот же импульс с выхода узлов 24 и 25 через элемент ИЛИ 26 является сигналом, свидетельствую- 1ЦИМ об окончании цикла обращения при работе с ЭВМ.

Селектор 8 содержит узлы селекции КСИ и ССИ, которые выделяются из выходного телевизионного видеосигнала , узлы задержки КСИ и ССИ, формирователи КСИ,(выход 1) и ССИ (выход 2), синхроимпульсы с выходов которьк задержаны до начата формирования активной части кадра в источнике телевизионного видеосигнала, формирователь импульсов фик сации и узел фиксап 1И ВС. (выход 3) .

Синхрогенератор 9, например, содержит генератор ТИ, депители, элементы задержки, формирователи, элементы ИЛИ. Синхрогенератор 9 вы- рабатьшает полный телевизионный синхросигнал ССП (выход 4) по ГОСТу,ТИ (выход 3)-. строчные ССИ ц (выход 2) и кадровые КСИ (выход 1), задержанные до начала отображения активной части кадра на экране видеоконтрольного блока.

Устройство работает следуюиц1м образом.

Основным режимом работы является режим считывания цифрового сигнала из блока 1 памяти. Считывание информации осуществляется во время прямого хода разверток блока 12. Блок 1 памяти имеет организацию, например, 256x256x8 бит. Так как длительность развертки одного элемента телевизионного изображения при квадратном растре и числе активных элементов изображения 256x256 составляет 140 НС, а минимальное время цикла считывания (записи) для элементов памяти составляет 510 не, то в схеме реализован принцип параллельно-последовательного считывания информации. С этой целью длительность цикла обращения к памяти выбирается такой, чтобы за это время на экране отображалось 2N элементов изобра204

жения. })а фиг.4 приведены временные диаграммы (для ) основных управляющих адресных сигналов при работе системы в ре-жиме считывания информа- ции из блока 1 памяти. Импульсы с второго выхода синхрогенератора 9 (фиг.4 а ) являются синхроимпульсами строк, задержанными относительно импульсов синхронизации блока 12. Задержка введена для того, чтобы обеспечить считывание информации из блока 1 памяти во время прямого хода развс рток блока 12.

Импульсы с третьего выхода синхрогенератора 9 (фиг.4Б ) имеют период, равный длительности одного элемента телевизионного изображения. Импульсы второго вьЕхода синхрогенератора 9 синхронизируют работу блока 5,

а импульсы первого и второго выходов синхрогенератора 9 - работу блока 7, Диаграммы сигналов на выходах 1-4 блока 5 приведены на фиг.4&,,4,е. Счетчик -(юрми 1ователь адреса по координате Х.. срабатыпает в начале

активной части каж;;ой строки и изменяет свое состояние на 1 с приходом очередного тактового импульса. Диаграммы сигналов четьфех младших

разрядов приведены на фиг.4,л,и,к. Счетчик -(формирователь адреса по координате У, сбрасывает в начале активной части каждого кадра и изменяет свое состояние на 1 с приходом очередного синхроимпульса строк.

Выходные разрядь X ,, и У,,, через коммутатор блока 7 поступают на выходы блока 7, причем на второй выход блока 7 поступает -fi младший

разряд Х , а на первый выход - старшие разряды Х, и разряды У . Кроме

этого, на пятый выход блока 7, минуя коммутатор, поступает сигнал N+1-го разряда (фиг .4п) . В режиме счи

тывания информации на чкран блока 12 информация каждого разряда блока 1 памяти считывается одновременно из

.

2 +1 микросхем памяти и в конце цикла считывания фиксируется положительным фронтом сигнала с четвертого I

выхода блока 5 (фиг.4 е ) в регистре 17. В конце каждого второго цикла информация из регистра 17 по отрицательному фронту ТИ и сигналу управления с выхода элемента И 15 (фиг.4 л) переписывается в блок 11 и при помощи этих же ТИ последовательным способом выводится в блок 10.

В конце каждого 1зторого цикла обращения к памяти в режиме считывания происходит ct-тепа адреса на адресном выходе блока 7 (фиг,4 к) и процесс считыва1Н1Я информации повтори- ется по новому адресу. В режиме рабты С внешними устройствами, аналогично режиму считывания необходимо сформировать адресные сигналы Х и соответстнующего источшша. Эти сигналы формируются в блоке 7 путем подсчета ТИ„, ССИд,,, КСИ для малокадровых систем и иутем подсчета ТИ.|, и КСИ.ц для телевизионных систем. Одновременно с формированием текущего адреса ТИ одного из тп ешних устройств осущестляет запуск ЛЦП 21 блока 2, па вход которого поступает аналоговый сиг- н;гл соответствующего внешнего источ нтгка. Но оког1чапии преобразования а1 алогового сигнала в цифровоГ код в блоке 2 формируется сигнал Конец преобразования, которьп посч упает на первый вход блока 13 прерываний. Па первом выходе блока 13 прерывани (формируется сигнал, который на время обращения к памяти осущестляет подключение к первому и второму выходам блока 7 адресные сигналы Xjr,n У-j,, от соответ- с гпующего источника, ,к -гпочает к nn j)L)pManMoiiHON y Bfjxo;iy блокчт 2 выход ЛУП и формирует сигнал записи на одном им выхо,п,ов дешифратора 6. Зап1К:Г) информации и ячейку блока 1 памяти .1су1 |;ествляется путем подачи п;1 соответст1 ц1:ций элемент памяти сигна;га записи, ilocjje этого устройство переходит в режим считьзвалия и формаиии на экран блока 12. Работа .С1 стемы 1 режиме обмена информацией с электронной Бьгп1слитеольной наши- Hoii (ЭВМ) не отличается от описанного режима.

В режи.е записи информации от ЭВМ i устройство (управляю: П1й сигнал на тпе ;-ьем входе блока 13) адреса и данные поступают непосредственно от ЭВМ и подключаются коммутатором блока 7 к входам блока I памяти к входам дешифратора управляю1цим сигпалом с второго выхода блока 13. В режиме чтения информации из устройства в ЭВМ (управляющий сигнал на четвертом входе блока 13) адресш.и сигнал поступает непосредственно от ЭВМ и через коммутатор блока 7 подключается к входам

5

0

5

0

5

0

5

0

5

блока 1 памяти и входам коммутатора 3 при помощи сигнала с выхода блока 13, кроме того, задним фронтом этого сигнала информация фиксируется в регистре 4 и поступает в ЭВМ, При этом сигнал WE не формируется. Таким образом, в режиме работы с внешними устройствами один из циклов обращения к блоку 1 памяти использован для записи (чтения) информации от этого внешнего устройства. С точки зрения ре;кима считывания возможны два слу-. чая возникновения прерывания: прерывание возникает при первом цикле обращения к блоку 1 памяти после смены адреса, на первом адресном выходе блока 7,прерывание возникает во втором цикле после смены адреса на первом адресном выходе блока 7.

На фиг.4м показан импульс на одном из выходов блока 13, соответствующий первому циклу обращения к блоку 1 памяти от внешнего устройства, после смены адреса на первом адресном выходе блока 7. В этом цикле сигнал на вход записи регистра 17 не поступает (фиг.4н), а информация в этом регистре появляется в конце следующего цикла. Но обращение к блоку памяти в следующем цикле проходит по тому же адресу и в регистр 17 в конце следующего цикла перепишется информация, которая в данный момент времени должна выводиться на экран блока 2,

На фиг.4 о показан импульс на.одном из выходов блока 13, соответствующий второму циклу обращений к блоку 1 памяти, после смены адреса на первом адресном выходе блока 7. В этом цикле сигнал на вход записи регистра 17 не поступает (фиг.4 г ) и поэтому в нем хранится информация, записанная в предыдущем цикле обращения, который проходит по этому же адресу.

Таким образом, в этом случае в блок 11 в конце этого цикла перепишется информация, которая в данный момент времени и должна выводиться на экран. Таким образом, независимо от того в какой из циклов возникают прерывания информация на экране блока 12 воспроизводится без искажений.

При работе устройства в режиме обмена информацией с внешними устройствами на экране блока 12 не возникает импульсных помех на изображении. Отсутствие .помех повышает качество и улучшает условия восприятия видеоинформации оператором, что позволяет оператору проводить визуальный 5 анализ отображаемой информации параллельно с обработкой этой информации при помощи ЭВМ, Это приводит к снижению утомляемости оператора и повыша3223208

нен с выходом тактовых импульсов с.инхрогенератора, с первым информационным входом блока формирования тактовьЕХ импульсов и с синхронизирующими входами блока буферной памяти и блока формирования цифровых видеосигналов, выход кадровых синхронизирующих импульсов соединен с первым информационным входом блока формирования цифровых видеосигналов, второй информационный вход которого и второй информационный вход блока формирования тактовых импульсов соединены с выходом строчных синхронизирующих им1. Устройство для обработки видео-,5 пульс ов синхрогенератора, выходы блока формирования 1Ц1фровых видеосигналов подключены соответственно к информационным входам блока отображения, а третий информационный вход

формационный выход блока памяти под- -щк с л. . Q 1Q 1л , 20 подключен к выходу блока буферной пает в конечном итоге производительность труда.

Формула изобретения

информации, содержащее блок памяти, информационный вход которого подключен к информационному выходу блока аналого-цифрового преобразования, ин10

ключен к информационному входу коммутатора, выход которого соединен с информационным входом первого регистра, С первого по третий синхронизирующие входы блока памяти подклю- 25 чены соответственно к первому по третий выходам блока формирования тактовых импульсов, входы записи блока памяти соединены с выходами дешифратора, синхронизирующий вход которого подключен к третьему выходу блока формирования тактовых импуль30

мяти, вход синхронизации блока отображения подключен к выходу управления отображением синхрогенератора, первый управляюии1й выход блока формирования прерываний подключен к первым управляю дим входам дешифратора, блока формирования адреса и блока аналого-цифрового преобразования, второй управляюш 1й выход блока формирования прерываний подключен к вторым управляюищм входам дешифратора блока формирования адреса и блока аналого-цифрового преобразования, третий управляю ций выход подключен

сов, адресный вход блока памяти соединен с первым адресным выходом блока формирования адреса, второй адресный выход которого Ьоединен с адресным входом коммутатора и с информационным входом дешифратора, первый и второй управляющие выходы блока формирован1-;я адреса подключены соответственно к первому и второму управляющим аходам блока аналого-цифрового преобразования, вход кадрового синхроимпульса и вход строчного синхроимпульса блока формирования адреса подключены соответственно к выходу кадрового синхроимпульса и к выходу строчного синхроимпульса селектора, информационный выход которого соединен с первым информационным входом блока аналого-цифрового преобразования, первый и второй установочные входы блока формирования адреса соединены соответственно с выходами кадровых синхронизирующих импульсов и строчных синхронизирующих импульсов синхргенератора, первый информационный вход блока формирования адреса соеди10

5

0

мяти, вход синхронизации блока отображения подключен к выходу управления отображением синхрогенератора, первый управляюии1й выход блока формирования прерываний подключен к первым управляю дим входам дешифратора, блока формирования адреса и блока аналого-цифрового преобразования, второй управляюш 1й выход блока формирования прерываний подключен к вторым управляюищм входам дешифратора блока формирования адреса и блока аналого-цифрового преобразования, третий управляю ций выход подключен

5 к входу загпюи первого регистра и к третьему управляющему входу блока формирования адреса, первый управляю- ций вход блока формирования прерываний соединен с выходом признака

0 окончания преобразования блока аналого-цифрового преобразования, синхронизирующий вход подключен к второму выходу блока формирования тактовых импульсов, второй и третий информа-

5 ционные входы блока аналого-цифрового преобразования являются соответственно первым и вторым информационными входами устройства, третий информационный вход которого соеди0 нен с вторым информационным входом блока формирования адреса, четвертый информационный вход соединен с информационным входом селектора, первый и второй установочные входы

5

устройства соединены с третьим и четвертым установочными входами блока формирования адреса, адресный вход которого является адресным входом уст

9

ройства, выход первого регистра является информационным выходом устройства, выход сигнала считывания блока формирования прерываний является выходом признака считывания устройства, первый и второй информационные входы блока формирования прерываний являются соответственно пятым и шестым информационными входами устройства, отличающе.еся. тем, что, с целью повышения помехоустойчивости отображения видеоинформации, в него введены второй регистр, два элемента И и элемент 1ШИ-НЕ, причем информационный вход второго регистра соединен с информационным выходом блока памяти, а информационный выход подключен к информационному входу блока буферной памяти, выходы nepBoi o и второго элементов И подключены соответственно к входам записи второго регистра и блока буферной памяти, первый вход второго элемента Н соединен с третьим управляющим выходом блока управ ления, первый вход первого элемента И и второй вход второго элемента И соединены с четвертым выходом блока (формирования тактовых импульсов, nepDbiii,второй и третий управ- ляга1цие выходы блока формирования прерываний подключены соответственно к входам элемента ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента И.

- 2. Устройство по П.1, от л и- чающееся тем, что блок формирования адреса содержит четыре счетчика координат, узел задания адреса, триггер, элемент НИИ, два элемента И и коммутатор, выходы которого являются первым и вторым адресными выход блока, информационные входы коммутатора соединены со

ответственно с выходами разрядов пер- 45 .мента ИЛИ является вторым управляю- вого, второго, третьего и четверто- щим, выходом блока.

fO

20

2232010

го счетчиков координат, с информационным вьп ;одом узла задания адреса и с адресным входом блока, первый информационный вход блока соединен с счетным входом первого счетчика координат, с входом сброса триггера и с первым входом элемента ИЛИ, установочный вход второго счетчика координат является первым установочным входом блока, второй установочный вход которого подключен к установочному входу первого счетчика координат и к счетному входу второго счетчика координат, второй инфорf5 мационный вход блока соединен со счетным входом третьего счетчика координат, установочный вход четвертого счетчика координат является третьим установочным входом блока, четвертый установочный вход которого подключен к установочному входу третьего счетчика координат и к счетному входу четвертого счетчика координат, выход третьего разряда первого счетчика координат является третьим уп- равляюищм выходом блока, входы узла задания адреса являются соответственно входами строчного синхроимпульса и кадрового синхроимпульса

30 узла задания адреса, выход признака которого соединен с вторым входом элемента ИЛИ и с входом установки триггера, прямой выход которого подключен к первог-ту управляющему выходу блока

35 и к первому входу первого элемента И, нулевой выход триггера соединен с первым входом второго элемента И, вторые входы первого и второго элементов И соединены с первым управляю40 шим входом блока, управлякнцие входы коммутатора соединены соответственно с выходами первого и второго элементов И и с вторым и третьим управляющими входами блока, выход элеи

h

Jlj1JlЛJlJlJUlЛJlЛJгпJггlлл

e ж

3 и д л м н о п

п

2 J

Фиг.З

П

J J t t t Л .t

Фиг.

Фиг. 5

r i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения псевдообъемного изображения | 1984 |

|

SU1233302A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1991 |

|

RU2029370C1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1986 |

|

SU1387038A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для ввода информации от аналоговых датчиков | 1986 |

|

SU1381476A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для запоминания и отображения видеоинформации | 1987 |

|

SU1424029A1 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Устройство для регистрации аналоговых сигналов | 1980 |

|

SU911577A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение помехоустойчивости отображения информации. Устройство содержит блок 1 памяти, блс1К аналого-цифрового преобразования, коммутатор 3, регистр 4, блок 5 формирования тактовых импульсов, дешифратор 6, блок 7 формирования адреса, селектор 8, синхрогенератор 9, блок 10 формирования цифровых видеосигналов, блок 11 буферной памяти, блок 12 отображения, блок 13 формирования прерываний, элементы И 14,15, элемент ИЛИ-НЕ 16, регистр 17. 1 з.п. ф-лы, 7 ил. (С (/: с кте lAw - уч7 eCfiitc ,Ks4l

Редактор Н.Рогулич

Составитель А.Жеренов

Техред Л.Олийнык Корректор Г.Решетник

Заказ 2867/47Тираж 672Подписное

ВНИИШ1 Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производстненно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Горный компас | 0 |

|

SU81A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мазурик Б.И., Яковлев В.В | |||

| и др | |||

| О применении и принципах построения систем анализа видеоинформации при неразрушающем контроле качества ма- и изделий электронной техники.-Электронная техника, сер | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механический грохот | 1922 |

|

SU41A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-26—Подача