Изобретение относится к электротехнике и может быть использовано в различных электрофизических устройствах, в которых используется накопление энергии в конденсаторах,

Известно зарядное устройство, в котором реализуется функциональное управление выходным напряжением, основанное на ступенчатой аппроксимация заданной функции выходного напряжения за счет формирования k ступеней из п уровней напряжения. Устройство содержит источник постоянного напряжения, преобразователи с различными выходными напрях ениями, выходы которых шунтированы диодами, емкостной накопитель, блоки управления соответствующими преобразователями, которые управляются с выхода счетчика, вход которого подключен к выходу генератора тактовых ммпульсов 1.

Известно устройство для заряда емкостного накопителя знергии,. содержащее источник питания, п транзисторных преобразователей напряжения, выходы которых соединены последовательно-согласно и через датчик зарядного тока подключены к обкладкам емкостного накопителя, задающий генератор, выход которого соединен с первым входом блока управления, выходы которого соединены с базами транзисторов преобразователей напряжения, второй вход блока управления соединен с выходом порогового элемента, входы последнего со-, единены с толлекторами транзисторов п-го преобразователя, блок управления зарядным процессом, вход которого соединен с выходом датчика зарядного тока, а выход с третьим входом блока управления 2,

Недостатком указанных устройств является необходимость многочисленных коммутаций для реализации алгоритма формир.овзния заданного выходного напряжения, выполнения одним из преобразователей |1ункции токоограничиваюи1его элемента, что отрицательно сказывается на надежности функционирования устройства.

Наиболее близким техническим решением к изобретению является устройство для зарядки накопительного конденсатора, которое содержит источник питания, п транзисторных преобразователей напряжения, первые входы которых соединены с первым выходом источника питания, к второму входу которого через датчик потребляемого тока подключены вторые входы транзисторных преобразователей напряжения, выходы которых через свои мостозые выпрямители соединены последовательносогласно и подключены к обкладкзм емкостного накопителя, параллельно которому

подключен датчик напряжения, задающий генератор, выход которого подключен к первому входу блока управления, выходы которого соединены с управляющими входами

транзисторных преобразователей напряжения, в состав блока управления входят делитель частоты, счетчик импульсов, выходы m младших разрядов которого соединены со входами дешифратора, формирователь коротких импульсов, п узлов формирования скважности, каждый из которых содер кит два элемента ИЛИ, счетчик формирования скважности и два триггера, 5 входы которых соединены с выходами дешифратора, счет5 чик кода задержки и два компаратора 3.

При этом состояние счетчика формирования скважности в процессе функционирования -устройства изменяется непосредственно сигналом датчика потребляемого тока, т.е. состояние счетчика увеличивается только на единицу. В этом случае величина приращения длительности управляющих сигналов выбирается достаточно большой, чтобы обеспечить необходимое

5 приращение величины потребляемого тока. Однако это не исключает возможности сбоев в работе блока управления в конце зарядного цикла, когда длительность приращения ммпульсов п.о сигналу датчика потребляемого тока не обеспечивает необходимого приращения величины потребляемого тока.

Цель изобретения - повышение надежности функционирования устройства за счет улучшения динамических характеристик

5 блока управления и снижения аппаратурных затрат при его реализации.

Указанная цель достигается тем, что в устройство для зарядки емкостного накопителя, содержащее источник питания, п транзисторных преобразователей напряжения, первые входы которых соединены с первым выходом источника питания, ко второму входу которого через датчик потребляемого тока подключены вторые входы транзисторных преобразователей напряжения, выходы которых через свои мостовые выпрямители соединены последовательно согласно и по,цключены к обкладкам емкостного накопителя, параллельно которому подключен

0 датчик напряжения, задающий генератор, выход которого подключен к первому входу блока управления, выходы которого соединены г, управляющими входами транзисторных :;ео5разователей напряжения, в

5 cocTi ,:лока управления входят счетчик импульсоп, выходы гп младших разрядов которого соединены со входами дешифратора, 2 п НЗ-трмггероя, входы которых соединены с выходами дешифратора, счоттк кода задержки, Е блок управления ::-.;:,-;л,.:н1,1 niv-opтивное запоминающее устройство, сумматор и управляемый ключ, при этом первый вход счетчика кода задержки подключен к выходу задающего генератора, второй и третий входы подключены соответственно к выходам датчика потребляемого тока и датчика напряжений, а выход соединены со вторым входом блока управления, адресная шина оперативного запоминающего устройства подключена к выходу сумматора, первая входная шина которого подключена к выходу счетчика импульсов, вторая входная шина сумматора через управляемый ключ подключена ко второму входу блока управления, к первому входу которого подключены вход управления ключа, вход разрешения записи оперативного запоминающего устройства и тактовый вход счетчика импульсов, 2п выходов дешифратора подключены к соответствующим информационным входам оперативного запоминающего устройства, входы установки в нуль RSтриггеров соединены с соответствующими выходами оперативного запоминающего устройства, а выходы RS-триггеров соединены с выходами блока управления, причем выходы первого и (п+Т)-го RS-триггеров являются первым и вторым выходами блока управления, выходы второго и (п+2}-го RSтриггеров - третьим и четвертым его выходами, а выходы Ь-го 2п-го и RS-триггеров ()-м и 2п-м выходами блока управления.

Новым в предлагаемом устройстве является введение в его состав оперативного запоминающего устройства, сумматора и управляемого ключа, что делает возможным более оперативно изменять длительность управляющих сигналов в зависимости от состояния емкостного накопителя и исключает возможность сбоев в работе блока управления..

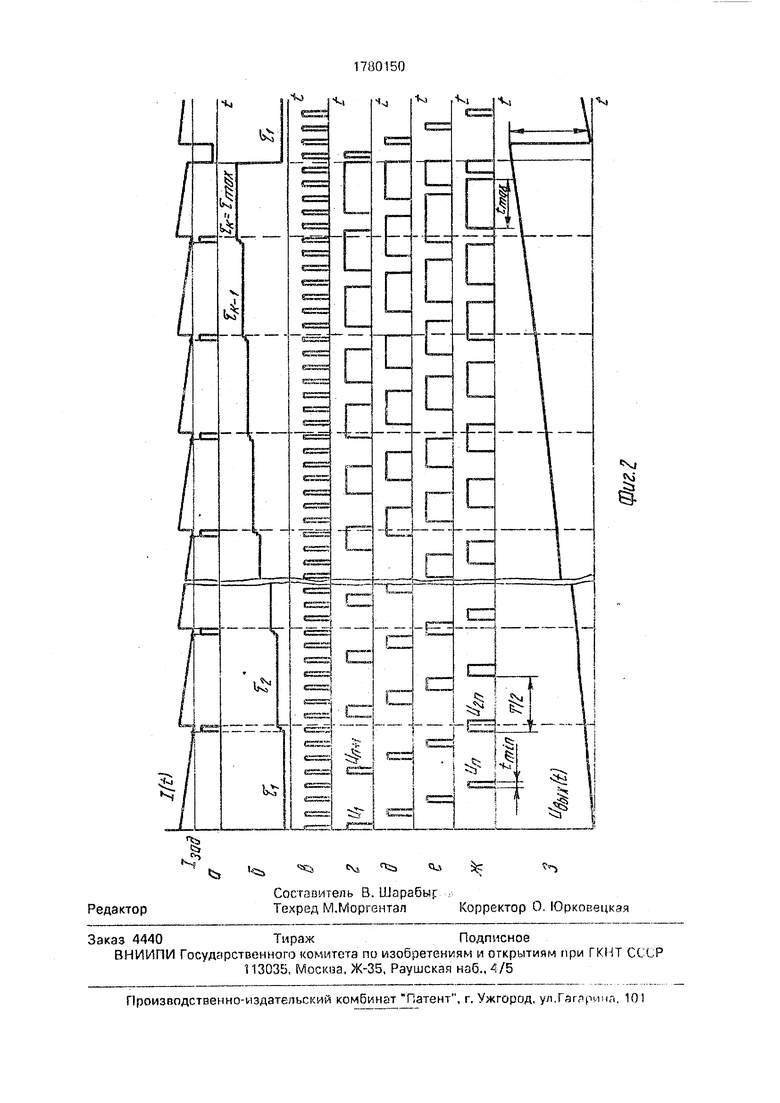

На фиг, 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы его работы.

Устройство содерх ит задающий генератор 1, выход которого подключен к первому входу блока 2 управления, выходы которого соединены с управляющими входами транзисторных преобразовательных модулей 3i...3n, первый и второй силовые входы которых подключены соответственно через-датмик 4 потребляемого тока непосредственно к клеммам источника 5 питания, выходы транзисторных преобразовательных модулей соединены последовательносогласно и подключены к выводам емкостного накопителя 6, параллельно которому подключен датчик 7 напряжения, счетчик 8 кода задержки, первый вход которого подключен к выходу задающего генератора 1, второй и третий входы подключены соответственно к выходам датчика 4 потребляемого тока и датчика 7 напряжения, а выход соединен с вторым входом блока 2 управления, выполненного на базе оперативно запоминающего устройства (ОЗУ) 9, адресная шина которого подключена к выходу сумматора 10, первая входная шина которого подключена к выходу счетчика 11, вторая входная шина сумматора через управляемый ключ 12 подключена к второму входу блока управления, к первому входу которого подключены вход управления ключа 12, вход разрешения записи ОЗУ 9 и тактовый вход счетчика 11, который своими младшими разрядами подключен к информационной шине дешифратора 13. 2п выходов которого подключены соответственно к информационным входам Di...D2n ОЗУ 9 и соединены с входами установки в единицу 2п RS-триггеров 14i.,.142n, входы установки в нуль которых соединены соответственное Q.l...Q2n выходами ОЗУ 9, а выходы триггеров соединены с выходами блока управления, причем выходы первого и (п+1)-го RS-тpиггepo8 являются первым и вторым выходами блока управления, выходы второго и (n-t-2)-ro RSTpMrrepOB - третьим и четвертым его выходами, и т.д., а аыходы п-го и 2п-го RS-тpиггepo8-(2n-1)-м и2п-м выходами блока управления.

Устройство работает следующим образом.

По тактам задающего генератора 1 счетчик 11, разрядность которого 1 изменяет свое состояние. Информация с выхода счетчика 11 поступает на первую шину сумматора 10, на вторую шину которого через управляемый ключ 12 подается код задержки. Сумматор 10 формирует на адресной шине ОЗУ 9 адрес ячейки, в которую записывается или из которой считывается (в зависимости от уровня потенциала на входе разрешения записи ОЗУ) информация, поступающая на информационные шины Db..D2n с выходов деш.ифрагор.а 13, выполняющего роль распределителя сигналов по каналам и управляемого ш-младЩими разрядами счетчика 11, Так, при низком уровне сигнала на сходе разрешения записи ОЗУ 9 последний включается в режим записи, выход ключа 12 блокируется по входу управления и на выходе сумматора 10 формируется базовый адрес As, который П1 ремещается в поле ячеек ОЗУ 9 по тактам задающего генератора 1. При высоком уровне сигнала на входе разрешения записи ОЗУ 9 последний переводится G режим считывания, при этом на вторую шину сумматора 10 поступает

сигнал с выхода управляемого ключа 12, и на выходе сумматора формируется адрес ячейки AIC, из которой будет считана информация, записанная в ОЗУ 9

Ak-CAe- Ti)mod2,(1)

где тк - код задержки при k-м цикле работы устройства (под циклом работы имеется в виду промежуток времени, в течение которого длительность импульсов управления остается неизменной):

I - разрядность ОЗУ 9 и сумматора 10.

Как следует из схемы, выходной сигнал переноса сумматора 10 игнорируется, поэтому операция сложения выполняется по mod 2, поскольку на вторую входную шину сумматора 10 поступают инверсные сигналы, и фактически выполняется операция вычитания кода задержки из кода базового адреса.

Таким образом, перемещаясь в поле ячеек ОЗУ, базовый адрес Аб производит активизацию одной из них в момент прихода импульсов на информационные шины Di...D2n с выходов дешифратора 13, а считана информация из нее будет с задержкой Гк вели.чина которой в каждом цикле работы устройства формируется счетчиком 8 кода задержки по тактам задающего генератора 1 при наличии на его входе 2 сигнала с датчика 4 потребляемого тока (фиг, 2 а, 26).

Сдвиг между, импульсами дешифратора 13 составляет величину Т/2п, гдеТ- период, рабочей частоты транзисторных преобразовательных модулей (фиг. 2в). С появлением импульсов на выходах дешифратора 13 соответствующие RS-триггеры 14i...142n устанавливаются в состояние 1 (фиг, 2г-.ж). каждый из которых опрокинется в исходное нулевое состояние соответствующим сигналом с выходов О:...Q2n ОЗУ 9с задержкой, величина которой в первом цикле работы устройства Г1 (код zl устанавливается на выходе счетчика 8 кода задержки сигна юм НУ при включении устройства). При этом на управляющих входах транзисторных преобразовательных модулей 3i...3n формируются последовательности импульсов длительностью ,H (фиг. 2), и емкостной накопитель Си начинает заряжаться.

Минимальная длительность управлянэщих импульсов. Тмин выбирается так., чтобы в момент запуска устройства забросы потреб.ляемого тока выше заданного ypotм- я были незначительными, и величина ее определяется параметрами трансформзтороо транзисторных преобразователей модулей, индуктивности рассеяния которых выполняют функции токоограничквзющих элементов.

По мере заряда емкостного накопителя б ток, потребляемый от источника 5 питания, уменьшается и становится ниже заданного уровня. В этом случае на выходе

датчика 4 потребляемого тока формируется сигнал, который воздействует на вход 2 счетчика 8 кода за,цержки, и последний по тактам задающего генератора 1 увеличивает на своем выходе код задержки до Г2 (второй цикл работы устройства) и т.д.

Таким образом, по сигналам датчика потребляемого тока 4 длительность управляющих импульсов Ui...U2n увеличивается от Тмин до tMSKc Т/2, чем обеспечивается

формирование выходного напряжения на емкостном накопителе 6 при постоянной мощности, потребляемой от источника питания 5. Выходное напряжение 4 имеет вид многоступенчатой, практически плавно нарастающей кривой Увых (фиг. 2е, где представлено суммарное напряжение модулей после выпрямления и суммирования напряжений выпрямителей). Это достигается незначительным приращением длительности

управляющих импульсов по сигналам датчика гютребляемого тока 4 в процессе формирОЕ.ания выходного напряжения.

При достижении напряжением на накопителе заданного значения UCH по сигналу

датчика 7 напряжения на выходе счетч1/1ка 8 кода задержки устанавливается первоначальное значение кода задержки ri (фиг. 26). Благодаря малой длительности управляюа1их сигналов ti tMifln на емкостном накопитепе 6 с большо л точностью (т.е. без забросов напряжения выше Uc номинального) поддерх ивается заданное напряжение, уменьшение которого связано с его разрядом 3 виде токов утечки, что компенсируется

периодическим подзарядом накопителя,

После разряда емкостного накопителя 6 процесс устройства повторяется.

Разрядность ОЗУ 9 и сумматора 10 зависит от величины задержки г,точности его

установки Бо о и определяется соотношением

IOQ2-f - 1092- -1,(2)

1--О f-O

где - операция выделения целого числа; 1.мак. - максимальная величина задер ючи;

Т пер1Юд рабочей частоты модулей. ;,тота генератора тактовых импульсов

опре. -ляется из условия

Со ,(3)

где m iog22n - число младших рртрпдов счетч тка 11;

п -число преобразоЕЭтельных модулей.

Таким образом, введение в блок управления зарядного устройства новых элементов, а именно ОЗУ 9, сумматора 10 и управляемого 12 ключа (на базе управляемых инверторов) позволяет достаточно простыми схемотехническими средствами повысить надежность функционирования зарядного устройства путем исключения возможности сбоев в работе блока управления, что имеет место в прототипе. Это достигается благодаря тому, что наращивание состояния счетчика кода задержки осуществляется импульсами с выхода задающего генератора при наличии на входе разрешения счета счетчика кода задержки сигнала с выхода датчика потребляемого тока. Благодаря этому обеспечивается высокое быстродействие цепей обратной связи по току и напряжению, т.е. улучшаются динамические свойства блока управления.

.Формула изобретения Устройство для зарядки емкостного накопителя, содержащее источник питания, п транзисторных преобразователей напряжения, первые входы которых соединены с первым выходом источника питания, к второму входу которого через датчик потребляемого тока подключены вторые входы транзисторных преобразователей напряжения, выходы которых через свои мостовые выпрямители соединены последовательносогласно и подключены к обкладкам емкостного накопителя, параллельно которому подключен датчик напряжения, задающий генератор, выход которого подключен к пер. вому входу блока управления, выходы которого соединены с управляющими вхо,цами транзисторных преобразователей напряжения, в состав блока управления входят счетчик импульсов, выходы m младших разрядов которого соединены с входами дешифратора. 2п RS-триггеров, S-входы которыхсоединены с эыходами дешифратора, счетчик кода задержки, отличающееся тем, что, с целью повышения надежности функционирование устройства, в блок управления введены оперативное запоминающее

устройство, сумматор и управляемый ключ, при этом первый вход счетчика кода задержки подключен к выходу задающего генератора, второй и третий входы соответственно к выходам датчика потребляемого тока и датчика нап ряжения, а выход соединен с вторым входом блока управления, адресная шина оперативного запоминающего устройства подключена к выходу сумматора, первая входная шина которого

подключена к. выходу счетчика импульсов, вторая входная шина сумматора через управляемый ключ - к второму входу блока управления, к первому входу которого подключены вход управления ключа, вход разрешения записи оперативного запоминающего устройства и тактовый вход счетчика импульсов. 2п выходов дешифратора подключены к соответствующим информационным входам оперативного

запоминающего устройства, входы установки в О RS-триггеров соединены с соответствующими выходами оперативного запоминающего устройства, а выходы RSтриггеров - с 1зыходами блока управления,

причем выходы первого и (п+1)-го RS-триггеров являются первым и вторым выходами блока управления, выходы второго и (п+2)-го RS-триггеров- третьим и четвертым его выходами, а выходы п-го и 2п-го RS-триггеров (2п-1)-м и 2п-м выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для зарядки емкостного накопителя | 1989 |

|

SU1702523A1 |

| Электромагнитная система для магнитокалорического рефрижератора | 1990 |

|

SU1778867A1 |

| Устройство для зарядки емкостного накопителя | 1990 |

|

SU1780151A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство для программного управления | 1987 |

|

SU1474595A1 |

| Способ заряда емкостного накопителя | 1982 |

|

SU1166248A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Устройство для управления оперативным накопителем | 1977 |

|

SU656106A1 |

| Устройство для управления однофазным автономным инвертором | 1987 |

|

SU1615845A1 |

Изобретение относится к электротехнике и может быть использовано в различных электрофизических устройствах, в которыхиспользуется накопление энергии в конденсаторах от источников питания ограниченной мощности. Устройство содержит зздзющ^^й генератор 1, блок 2 управления, источник 5 питания, п транзисторных преобразовательных модулей 3i...3n, емкостной накопитель 6, датчик 4 потребляемого тока, датчик 1 напряжения, счетчик 8 кода задержки. Новым а предлагаемом устройстве является введение в блок управления оперативного запоминающего устройства 9, сумматора 10 и управляемого ключа 12, что делает возможным оператизно(в цифровом коде) изменять д,г:ительность управляющих сигналов в зависимости от состояния емксют-чого нгкопителя и позволяет надежность ф'ункциокировзния устройства. 2 ил.сл00ело

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для заряда емкостногоНАКОпиТЕля эНЕРгии | 1979 |

|

SU834843A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство для зарядки емкостного накопителя | 1989 |

|

SU1702523A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-07—Публикация

1989-10-11—Подача