второй группы блока управления соединены с одноименными входами первого элемента ИЛИ блока управления, вторые входы элементов И второй группы блока управления соединены с выходом первого элемента НЕ блока управления выход первого элемента ИЛИ блока управления соединен с вторым входом первого и с первым входом второго элементов И блока управления, второй вход второго элемента И и вторые входы элементов И первой группы блока управления соедтшены с выходом второго элемента НЕ блока управления, вход которого соединен с первым входом первого элемента И блока управления, выход второго элемента ИЛИ блока управления соединен с первым входом третьего элемента И блока управления, второй вход которого соединей с выходом первого элемента И блока управления, выход второго элемента ИЖ блока управления соеди нен с входом первого элемента НЕ блока управления,, выход каждого элемента ИЛИ группы блока управления соединен с входом одноименного блока элементов И второй группы, i-й (i 1, ...п, где п - число заявок) 1 5 выход регистра готовности соединен с; первым входом i-ro элемента И группы и с вторым входом i-ro блока элементов И третьей группы, выход второго элемента И блока управления соединен, с вторыми входами элементов И группы, выход третьего элемента И блока управления соединен с входом первого элемента ИЛИ второй группы, одноименные выходы групп выходов i-x блокой элементов И третьей группы соединены с группами входов i-x элеме.нтов ИЛИ второй группы, выходы элементов ИЛИ второй группы соёдииены с группой информационных входов регистра сдвига, одноименные выходам группы выходов блоков элементов И второй группы соединены с группами входов одноименных элементов ИЛИ третьей груйпы, выходы элементов ИЛИ третьей группы соединены с группами входов элементов И первой группы, первая группа выходов каждого регистра хранения группы соединена с группой входов одноименного блока элементов И второй группы , вторая Еруппа выходов казвдого регистра хранения группы соединена с группой входов одноименного блока элементов И третьей группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1983 |

|

SU1151966A1 |

| Устройство для распределения групповых заявок по процессорам | 1985 |

|

SU1254485A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1246096A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1290324A1 |

| Устройство для диспетчеризации заявок | 1985 |

|

SU1247873A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| Устройство для распределения заданий процессорам | 1986 |

|

SU1310821A1 |

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1095181A1 |

| Устройство для распределения заявок по процессорам | 1990 |

|

SU1798782A1 |

УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАЯВОК ПО ПРОЦЕССОРАМ, содержащее группу регистров хранения, регистр готовности, группу элементов И, блок управления, первую группу блоков элементов И, регистр сдвига, первую группу элементоа ИЛИ, элемент ИЛИ, элемент И, группа информационньтх входов первого регистра хранения группы является группой входов заявок устройства, управляющий вход каждого из регистров хранения группы соединен с выходом одноименного элемента И группы, блок управления содержит два элемента ИЛИ и первый элемент И, группа выходов регистра готовности соединена с входами первого элемента ИЛИ блока управления, каждый выход регистра готовности соединен с первым входом одноименного блока элементов И первой группы, вторые входы блоков элементов И первой группы соединены с входами элемента ИЛИ и с выходами регистра сдвига, выход элемента ИЛИ соединен с первьи входом первого элемента И блока управления, первый и второй входы элемента И соединены соответственно с выходами элемента ИЛИ и с первым выходом группы выходов регистра сдвига, выход первого элемента И блока управления соединен с входом управления сдвигом регистра сдвига, тактовый вход которого соединен с выходом элемента И, грутша выходов каждого блока элементов И первой группы соединена с группой входов одноименного элемента ИЛИ первой, группы и с соответствующей группой выходов устройства, первая группа сигнальных входов устройства соединена с группой информационных входов регистра готовности, группа входов сброса которого соединена с выходами элементов ИЛИ первой группы и с группой входов сброса (Л регистра сдвига, о т л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей устройства за счет обслуживания заявки при отказе процессора в. ходе решения задачи, в устройство-введены вторая и третья групга 1 блоков элементов И, ел вторая и третья грзгапы элементов ИЛИ, а в блок управления - две группы элементов И, группа элементов ИЛИ, со два элемента НЕ, второй и третий ; 9д элементы И, причем вторая группа сиг- ; сл нальных входов устройства соединена I с первым входом одно1менного элемента И первой группы блока управления, выходы элементов И первой группы блока управления соединены с входами второго элемента ИЛИ блока управления и с первыми входами одноименных эледентов ИЛИ груптл блока управления, вторые входы элементов ИЛИ группы блока управления соединены с выходами одноименных элементов И второй группы блока управления, первые входы элементов И

Изобретение относится к вычислительной технике и мозйет быть использовано в многопроцессорных вычислительных системах. Известно устройство для распределения заданий- щ оцессорам, содержащее регистр готовности процессоров, соединенньй с входами групп элементов И и бло ка управления, первый вход которого подключен к управляющему входу реги Стра сдвига, при этом регистр сдвига через группБ элементов И подключен к .входам процессоров, а через процессоры и элементы ИЛИ - к регистру готовности и соответственно к входам сбора регистра, выходы которого через элемент ИЛИ подключены к управляющему входу блока управления lj . Недостатками этого устройства являются высокая вероятность потери заявки на решение задачи, вызванная отказом устройства от выполнения задания, если Число свободных процессоров меньйе количества потреб шх, а также ограниченные функциональные возможности, пт оявляющиеся в невозможности арганизацнн очереди заданий. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство . для распределения заявок по процессорам, содержащее регистр готовности процессоров, соединеннь с входами группы блоков элементов И и блока управления, первый выход которого подключен к управляющему входу регистра сдвига, информационные вкоди которого подключены к второй группе выходов последнего из группы последовательно соединенных регистров хранения, управлянщие входы которых соединены с выходами элемектоэ И группы, вход каждого из которых соединен с выходом последукяцего, а

вход последнего соединен с вторым выходом блока управления, первая группа выходов последнего регистра хранения соединена с группой блоков элементов И,- через которые регистр сдв га подключен к входам процессоров, а через процессоры и элементы ИЛИ группы - к регистру готовности и к выходам сброса регистра сдвига, выходы которого через элемент ИЛИ подключены к управляющему входу блока управления, входам элементов И группы элемента И, выход которого соединен с входом сдвига регистра 21 .

Недостатком известного устройства является невыполнение задачи при выходе из строя хотя бы одного из .назначенных процессоров в ходе ее решения.

Цель изобретения - расширение функциональных возможностей устр&йства да счет обслуживания заявки при отказе процессора в ходе решения задачи

Поставленная цель достигается тем, что в устройство для распределения заявок по процессорам, содержащее группу регистров хранения, регистр готовности, группу элементов И, блок управления, первую группу блоков элементов И, регистр сдвига, первую группу элементов ИЛИ, элемент ИЛИ, элемент И, группа информа.ционных входов первого регистра хранения группы является группой входов заявок устройства, .управляющий вход каждого из регистров хранения группы соединен с выходом одноименного элемента И группы, блок управления содержит два элемента ИЛИ и первый элемент И, группа выходов регистра roTOBHoctH соединена с входами первого элемента ИЛИ блока управления, каждый выход регистра готовности соединен с первым входом одногаленного блока элементов И первой группы вторые входы блоков элементов И первой группы соединены с входами элемента ИШ и с выходами регистра сдвига, выход элемента ИЛИ соединен с первым входом первого элемента И блока управления, первьй и второй входы элемента И соединены соответственно с выходами элемента ИЛИ и с первым выходом группы выходов регистра сдвига, выход первого элемента И блока управления соединен с входом управления сдвигом

регистра сдвига, тактовый вход которого соединен с выходом элемента И, группа выходов каждого блока элементов И первой группы соединена с группой входов о.дноименного элемента ИЛИ первой группы и с соответствующей группой выходов устройства, первая группа сигнальных входов устройства соединена с группой информационных входов регистра готовности, группа входов сброса которого соединена с

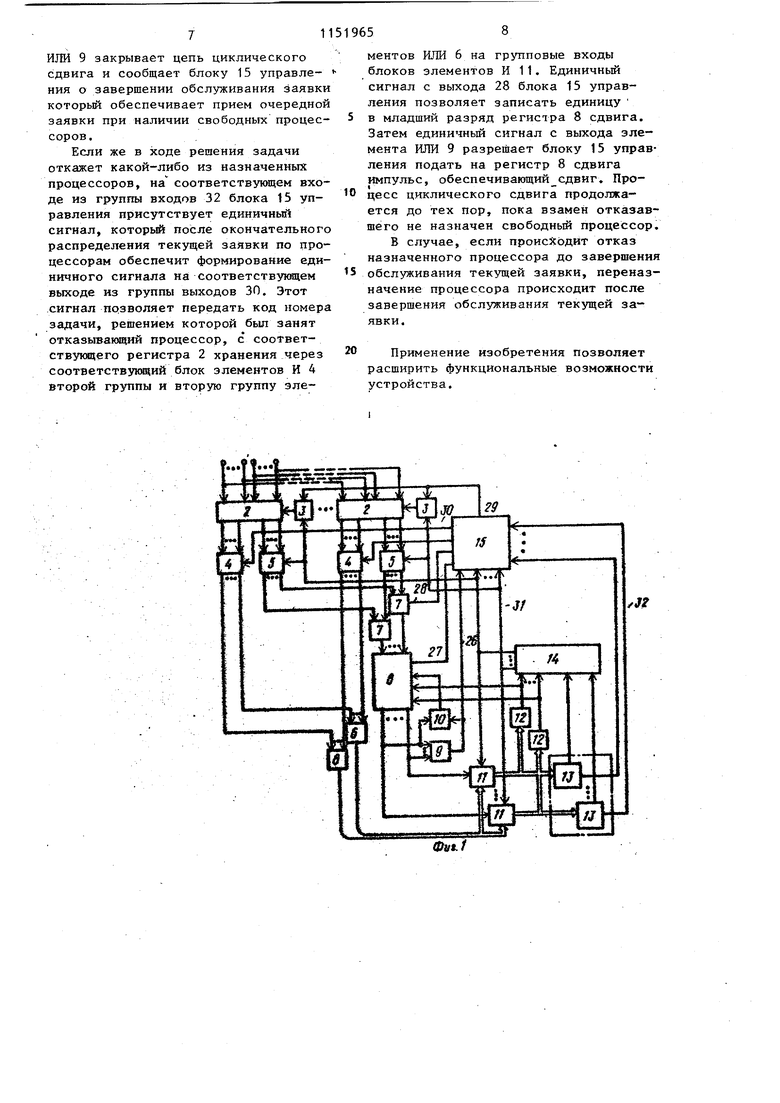

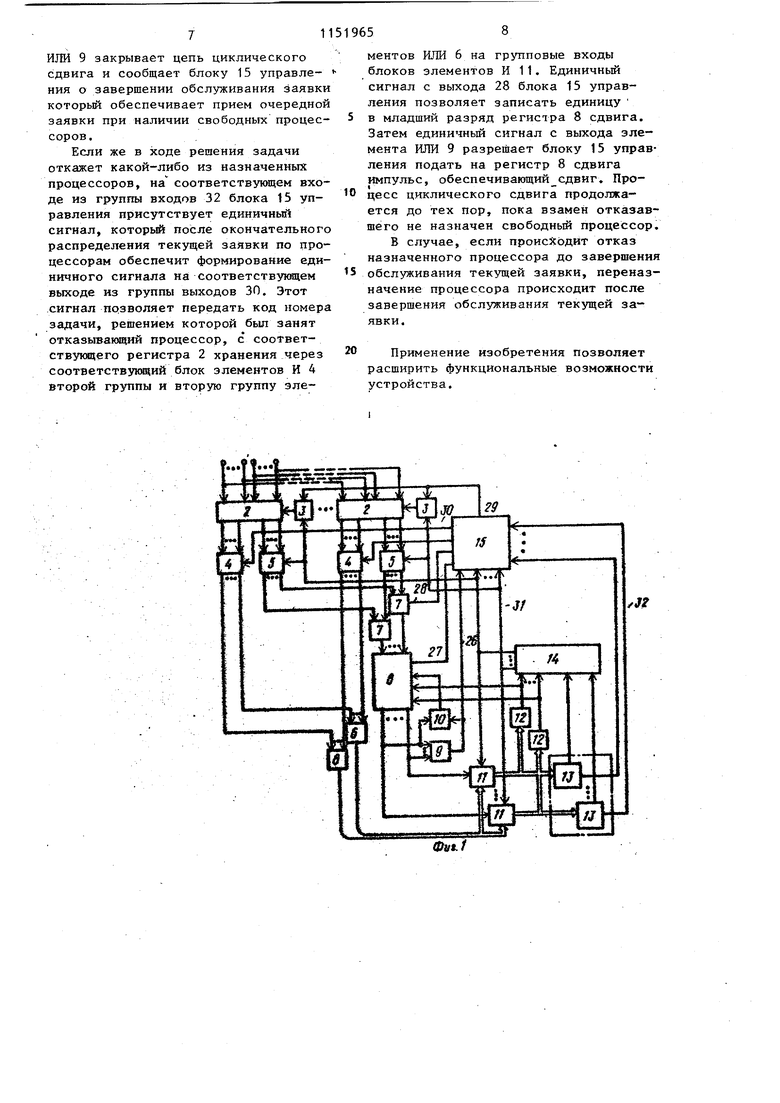

выходами элементов ИЛИ первой группы и с группой входов сброса регистра сдвига, введены вторая и третья группы блоков элементов И, вторая и третья группы элементов ИЛИ, а в блок управления - две группы элементов И, группа элементов ИЛИ, два элемента НЕ, второй и третий элементы И, причем вторая группа сигнальных входов устройства соединена с первым входом одноименного элемента И первой группы блока управления, выходы элементов И первой группы блока управления соединены с входами второго элемента ИЛИ блока управления и с первыми входами одноименных элементов ИЛИ группы блока управления, вторые входы элементов ИЛИ группы блока управления соединены с выходами одноименных элементов И второй группы блока управления, первые входы элементов И второй группы блока управления соединены с одноименными входами первого элемента ИЛИ.блока управления, вторые входы элементов И второй труппы блока управления соединены с выходом первого элемента НЕ блока управления, выход первого элемента ИЛИ блока управления соединен с вторым входом первого и с первым входом второго элементов И блока управления, второй вход второго элемента И и вторые входы элементов И-, первой группы блока управления соединены с выходом второго элемента НЕ блока управления, вход которого соединен с первым входом первого элемента И блока управления, второго элемента ИЛИ блока управления соединен с первым входом третьего элемента И блока управления, второй вход которого соединен с выходом первого элемента И блока управления, выход второго элемента ИЛИ блока управления соединен с входом первого элемента НЕ блока управления, выход каждого элемента ИЛИ ГРУППЫ блока управления соединен с входом одноименного блока элементо И второй группы, i-й (i 1 -п, где п - число заявок) выход регистра готовности соединен с первым входом i-ro элемента И группы и с вторым входом блока элементов И третье группы, выход второго элемента И блока управления соединен с вторыми входами элементов И группы, выход третьего элемента И блока управления соединен с входом первого элемента ИЖ второй группы, одноименные выход групп выходов i-x блоков элементов третьей группы соединены с группами входов 1-х элементов ИЛИ второй груп пы, выходы элементов ИЛИ второй груп пы соединены с группой информационны входов регистра сдвига, одноименные вьшоды группы выходов блока элементов И второй группы соединены с груп пами входов одноименных элементов ИЛ третьей группы, выходы элементов ИЖ третьей группы соединены с группами входов блоков элементов И первой группы, первая группа выходов каждог регистра хранения группы соединена с группой входов одноименного блока элементов И второй группы, вторая группа выходов каждого регистра хранения группы соединена с группой входов одноименного блока элементов И третьей группы. На фиг. 1 представлена структурна схема предлагаемого устройства; на фиг. 2 - структурная схема блока управления. . Устройство содержит группу входов 1заявок устройства, группу регистро 2хранения, группу элементов ИЗ, группу блоков элементов И 4,. группу блоков элементов И 5, группу элементов ИЛИ 6, группу элементов ИЛИ Т регистр 8 сдвига, элемент ИЛИ 9, элемент И 10, группу блоков элементо И 11, группу элементов ИЛИ 12, rpynn процессоров 13, регистр 14 готовност блок 15 управления. Блок 15 управления содержит элементы ИЛИ 16 и 17, элементы НЕ 18и 1 элементы И 20-22, группу элементов И 23, группу элементбв И 24, группу элементов ИЛИ 25, вход 26, вь1ход 27 элемента И 21, выход 28 элемента И 2 выход 29 элемента И 20, выходы 30 элементов НИИ 25, входы 31 элемента ИЛИ 16, группа сигнальных входов 32 устройства. Устройство работает следующим образом. На группу входов 1 устройства поступают заявки на решение задачи, которые вырабатываются планирующей системой. Заявка содержит код номера задачи, которую надо решить, и код потребного для решения числа процессоров. Код числа процессоров представляется в виде соответствующего числа разрядных единиц. Первая заявка первоначально поступает на все регистры 2 хранения, а затем по сигналам блока 15 управления через вторую группу блоков элементов И 4 и вторую группу элементов ИЛИ 6 код номера задачи поступает на групповые входы блоков элемента И 11 первой группы-, а код потребного числа процессоров через третью группу блоков элементов И 5 и третью группу элементов ИЛИ 7 переписывается на регистр 8 сдвига. На выходах блоков элементов И 11 номер задачи будет только в том случае, если соответствуниций процессор 13 группы свободен, о чем сигнализирует единица в соответствующем разряде регистра 14, и если данный процессор 14 группы требуется для решения задачи, о чем сигнализирует единица в соответствующем разряде регистра 8 сдвига. Код номера задачи передается в процессоры 13 группы для исполнения, а через первую группу элементов ИЛИ 12 обнуляет соответствующие разряды регистра 14 и регистра 8 сдвига. При наличии свободных процессоров 13 группы единичный сигнал с выхода 29 блока 15 управления обеспечивает прием очередной заявки в соответствующие регистры 2 хранения. Распределение процессоров для этой заявки производится аналогичньм обра- : зом. Если число назначенных процессоров меньше требуемого числа, не все разряды регистра 8 сдвига обнулены, единичньй сигнал с выхода элемента ШШ 9 открывает элемент И 10 и разрешает блоку 15 управления с выхода 27 подать на регистр 8 сдвига очередной импульс, сдвигающий его содержимое на один разряд. Процесс циклического сдвига продолжается до тех пор, пока не будет назначено требуемое число процессоров. В этом слу- . чае нулевой сигнал с выхода элемента

ИЛИ 9 закрывает цепь циклического сдвига и сообщает блоку 15 управления о завершении обслуживания заявки которьй обеспечивает прием очередной заявки при наличии свободных процессоров.

Если же в ходе решения задачи откажет какой-либо из назначенных процессоров, на соответствуквдем входе из группы входов 32 блока 15 управления присутствует единичньв сигнал, который после окончательного распределения текущей заявки по процессорам обеспечит формирование единичного сигнала на соответствунидем выходе из группы выходов 30. Этот сигнал позволяет передать код номера задачи, решением которой был занят отказывающий процессор, с соответствующего регистра 2 хранения через соответствукмдиЙ блок элементов И 4 второй группы и вторую группу элементов ИЛИ 6 на групповые входы блоков элементов И 11. Единичный сигнал с выхода 28 блока 15 управления позволяет записать единицу в младший разряд регистра 8 сдвига. Затем единичный сигнал с выхода элемента ИЛИ 9 разрешает блоку 15 управления подать на регистр 8 сдвига импульс, обеспечивающий сдвиг. Процесс циклического сдвига продолжается до тех пор, пока взамен отказавшего не назначен свободный процессор.

В случае, если происходит отказ назначенного процессора до завершения обслуживания текущей заявки, переназначение процессора происходит после завершения обслуживания текущей заявки.

Применение изобретения позволяет расширить функциональные возможности

устройства.

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-11-30—Подача