. ми группами входов блока занятия пр цессоров, первая группа выходов которого соединена с вторыми группами входов блоков регистров группы, первые выходы блоков регистров группы являются группой сигнальных выходов устройства, вторая группа выходов блока занятия процессоров соединена с третьими группами входов блоков регистров группы, выходы которых соединены с входами управления соответствующих блоков дешифраторов группы и с группой входов блока выбо ра, каждьй выход группы выходов блока выбора соединен с входом разрешения записи одноименного блока регист ров групп, а блок управления дополнительно содержит мультиплексор и блок памяти, причем группа.входов мультиплексора соединена с первой группой выходов первого регистра, вторая группа быходов которого соеди нена с группой входов второго регист ра и с выходом мультиплексора, первый, второй, третий, четвертый и пятый входы управления которого соединены соответственно с выходом блока хранения заявок, с первым вьссодом блока выбора, с вторым выходом блока выбора, с выходом элемента ИЛИ и с соответствуюцим выходом второй группы выходов первого регистра, группа выходов второго регистра соединена с группой адресных входов блока памяти, группа выходов которого соединена с группой входов первого регистра, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с первым входом первого элемента И, с информационным входом регистра сдвига с первьгм.входом второго элемента И, с входом разрешения записи регистра сдвига и с первым входом третьего элемента И, выход которого соединен с первым входом блока выбора, первый выход генератора импульсов соеди нен с вторыми входами первого, второго и третьего элементов И, выход второго элемента И соединен с вхощом сдвига регистра сдвига, второй выход генератора импульсов соединен с тактовым входом первого регистра и с тактовым входом регистра маскирования, третий выход генератора импульсов соединен с тактовым входом второго регистра и с тактовым входом регистра.дублирования, вход запуска устройства-соединен с единичным входом и с инверсным входом сброса триггера, выход которого соединен с входом запуска генератора импульсов, выход первого элемента И соединен.с тактовым входом блока хранения заявок, выход блока занятия процессоров соединен с вторым входом блока выбора и с входами сброса блока хранения заявок и регистра сдвига, калсдьш вы,ход которого соединен с первым входом одноименного блока элементов И группы, а выход старшего разряда регистра сдвига соединен с информационным входом младшего разряда регистра сдвига, каждый выход регистра готовности процессоров соединен с вторым входом одноименного блока элементов И группы, третья группа выходов блока занйтия процессоров соединена с группой входов сброса ре- гистра готовности процессоров, каждьш вход группы кодовых входов устройства соединен с входом сброса одноименного блока регистров..группы. 2.Устройство по п. 1, о т л и чающееся тем, что блок выбора содержит регистр состояния, регистр сдвига, регистр записи, группу элементов,И, элемент ШШ-НЕ и элемент Hffli, причем группа входов блока соединена с группой единичных входов регистра состояния, единичные выходы которого соединены с первыми входами соответствующих элементов И группы и с входами элемента ИЛИ-НЕ, первый вход блока соединен с входом сдвига регистра сдвига, группа единичных выходов которого соединена- с вторыми входами соответствующих эле- . ме-нтов И группы, кроме того, единичный выход старшего разряда регистра сдвига соединен с единичным входом первого разряда этого регистра, второй вход блока соединен с входом сброса регистра записи, выход элемента ИЛИ-НЕ является первым выходом блока, единичные выходы регистра записи образуют группу выходов блока и соединены с соответствующими нулевыми входами регистра состояния и входами элемента ИЛИ, выход элемента ИЛИ является вторым выходом блока, выходы элементов И группы соединены -с единичными входами регистра записи. 3.Устройство по п. 1, отличающееся тем, что блок занятия процессоров содержит счетчик, дешифратор .шифратор .группу элементов ИЛИ,элемент ИЛИ,первьш и второй одновибраторы, причем группы входов блока соединены с входами соответствующих . элементов ИЛИ группы, выходы которых соединены с соответствукщими входами шифратора, с входами элемента ИЛИ и являются третьей группой выходов блока, выходы шифратора являются первой группой выходов блока, выход

элемента ИЛИ соединен с входом первого одновибратора,выход которого соединен с суммирующим входом счетчика, выходы счетчика соединены с входами дешифратора, выходы которого являются первой группой блока, кроме того, последний выход дешифратора соединен с входом второго одновибратора, выход которого соединен с входом сброса счетчика и с выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1983 |

|

SU1151966A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1095181A1 |

| Микропрограммный диспетчер многопроцессорной вычислительной системы | 1987 |

|

SU1532926A1 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1179364A1 |

| УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПО ПРОЦЕССОРАМ | 1991 |

|

RU2017206C1 |

| Устройство для распределения заданий | 1984 |

|

SU1179340A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1259285A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1453406A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1246096A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

1. УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПРОЦЕССОРАМ, содержащее блок управления, регистр сдвига, регистр готовности процессоров, регистр дублирования, группу блоков элементов И, группу элементов.ИЛИ и элемент ИЛИ, причем блок управления содержит триггер, генератор импульсов, три элемента И и два регистра, выходы регистра сдвига соединены с входами элемента ИЛИ и с первыми входами блоков элементов И группы, выходы элементов ИЛИ группы соединены с единичными входами соответствуюац1х разрядов регистра готовности процессоров, единичные выходы которого соединены с вторыми входами блоков элементов И.группы, выходы блоков элементов И группы являются группой информационньк выходов устройства, группа сигнальных входов устройства соединена с информационными входами соответствующих разрядов регистра дублирования,о т л и ч а ющ е е с я тем, что, с целью повышения достоверности функционирования за счет уменьшения вероятности отказа в обслуживании заяв.ки, оно содержит блок хранения заявок, блок выбора, группу блоков регистров, группу блоков дешифраторов, блок занятия процессоров, блок приоритета, ре- . гистр маскирования, шифратор и группу одновибраторов, выкоды которых соединены с нулевыми входами соответСТВУЙ1ЦИХ разрядов регистра маскирования, группа выходов регистра мас-г кирования соединена с первой группой входов блока приоритета, выходы кос € торого соединены с единичными входами соответствующих разрядов регист(Л ра маскирования и с соответствуюпщми входами ыифратора, группа выходов шифратора соединена с первой группой входов каждого блока регистров группы, группа выходов каждого блока регистров группы соединена с группой входов соответствующего блока со о дешифраторов группы, одноименные выходы каждого блока дешифраторов группы соединены соответственно с оо входами одноименных элементов ШШ О) группы, единичные выходы регистра Од дублирования соединены с второй группой входов блока приоритета, единичные выходы регистра готовности процессоров соединены с входами соответствующих одновибраторов группы, группа информационных входов устройства соединена с группой входов блока хранения заявок, групца информационных выходов которого соединена с группами входов блоков элементов И группы, выходы блоков элементов И группы соединены с соответствующи

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства распределения заданий (задач) в многопроцессорной вычислительной системе.

Цель изобретения - повышение достоверности функционирования за сче уменьшения вероятности отказа в обслуживании заявки.

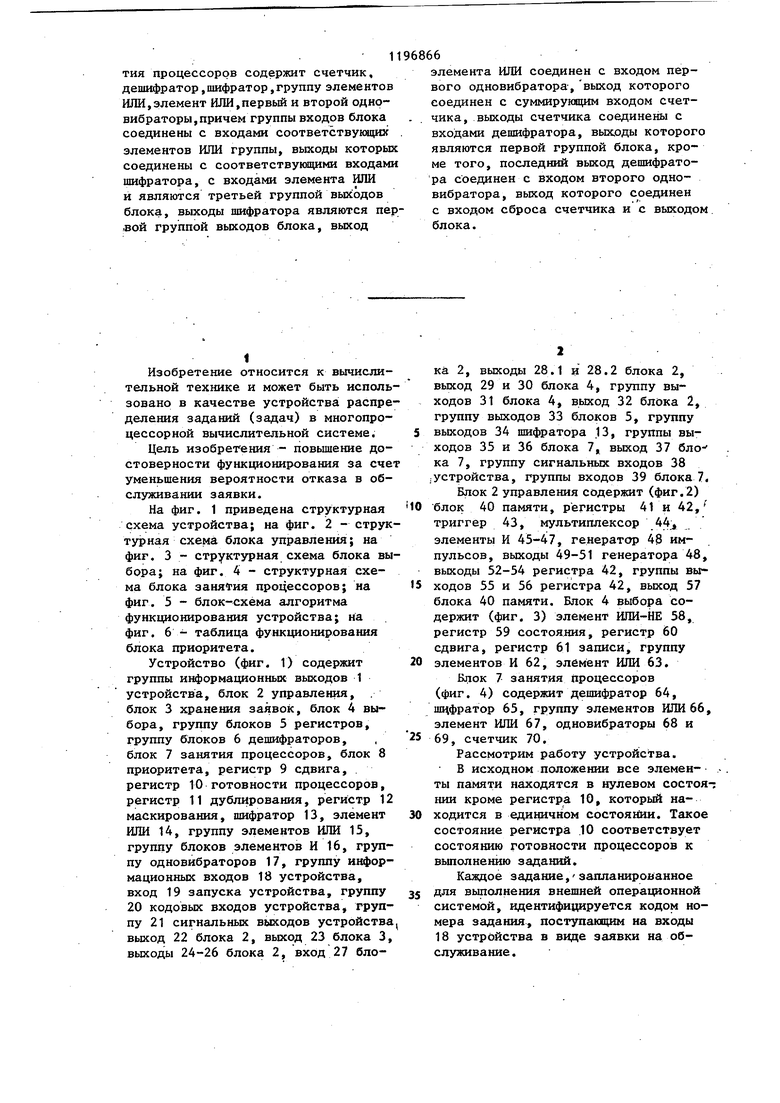

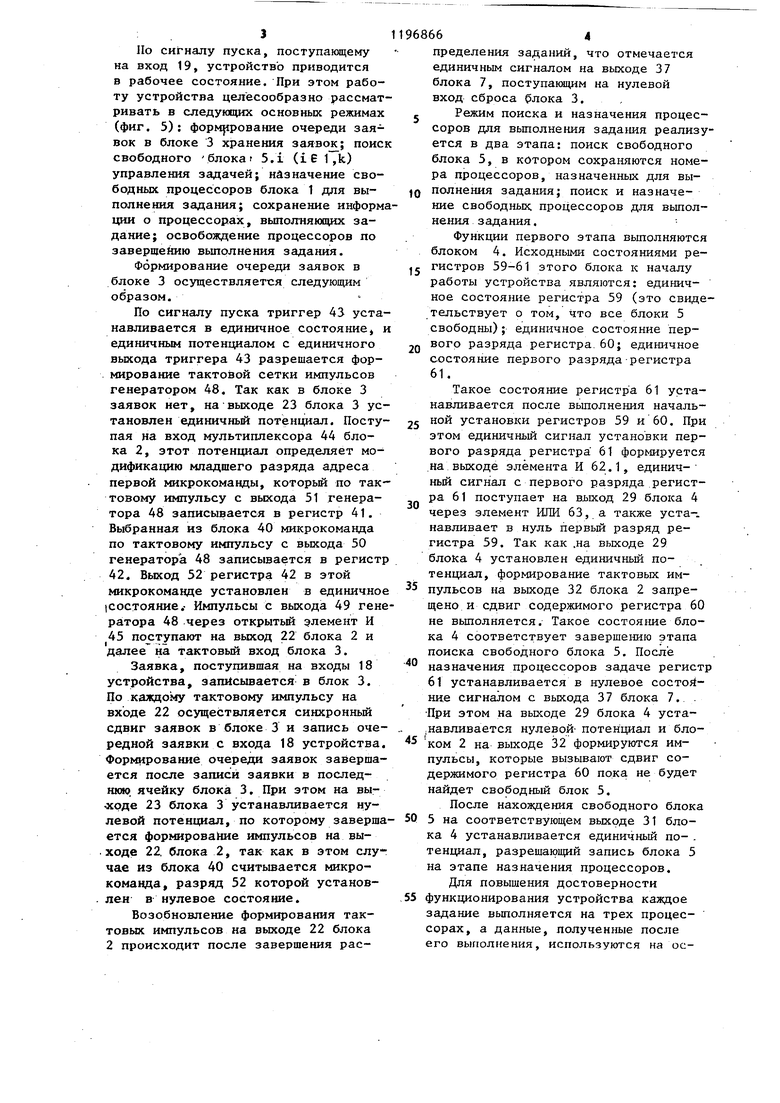

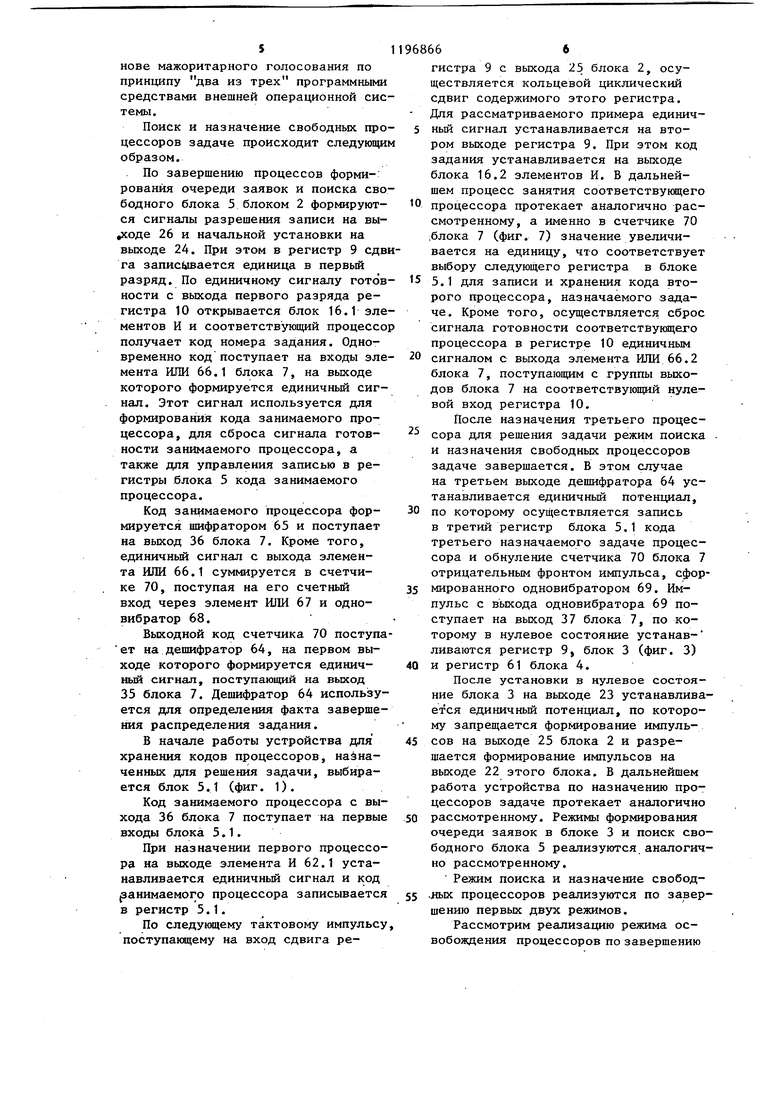

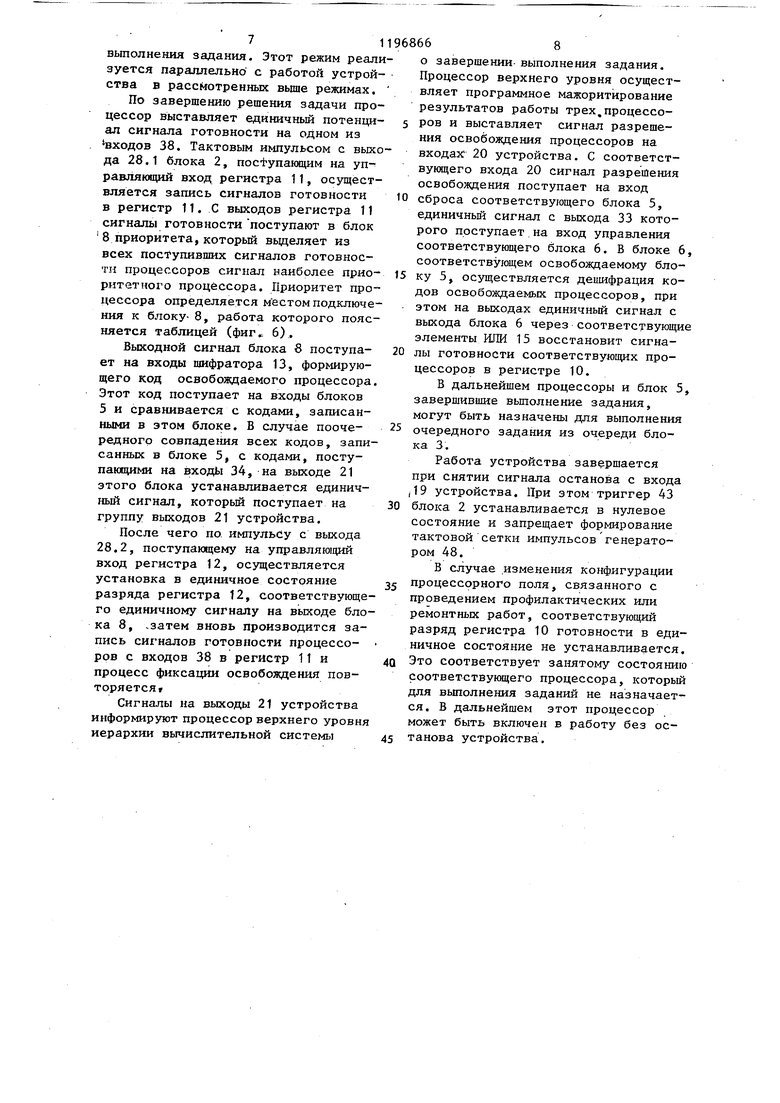

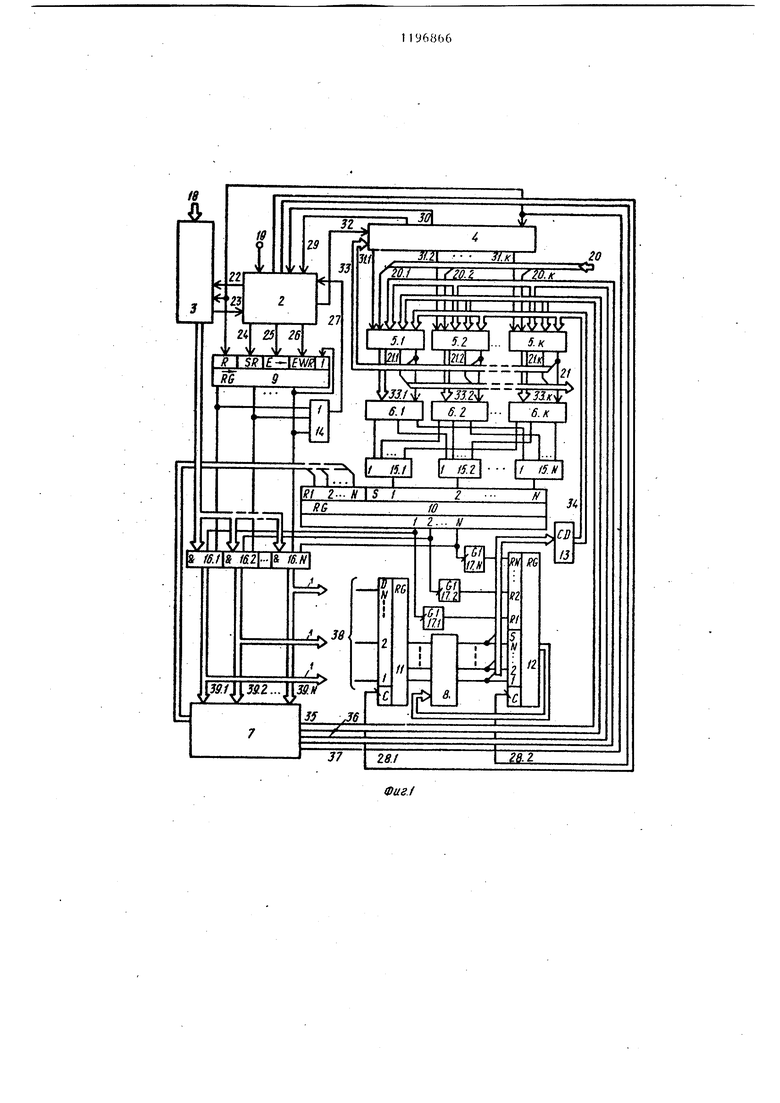

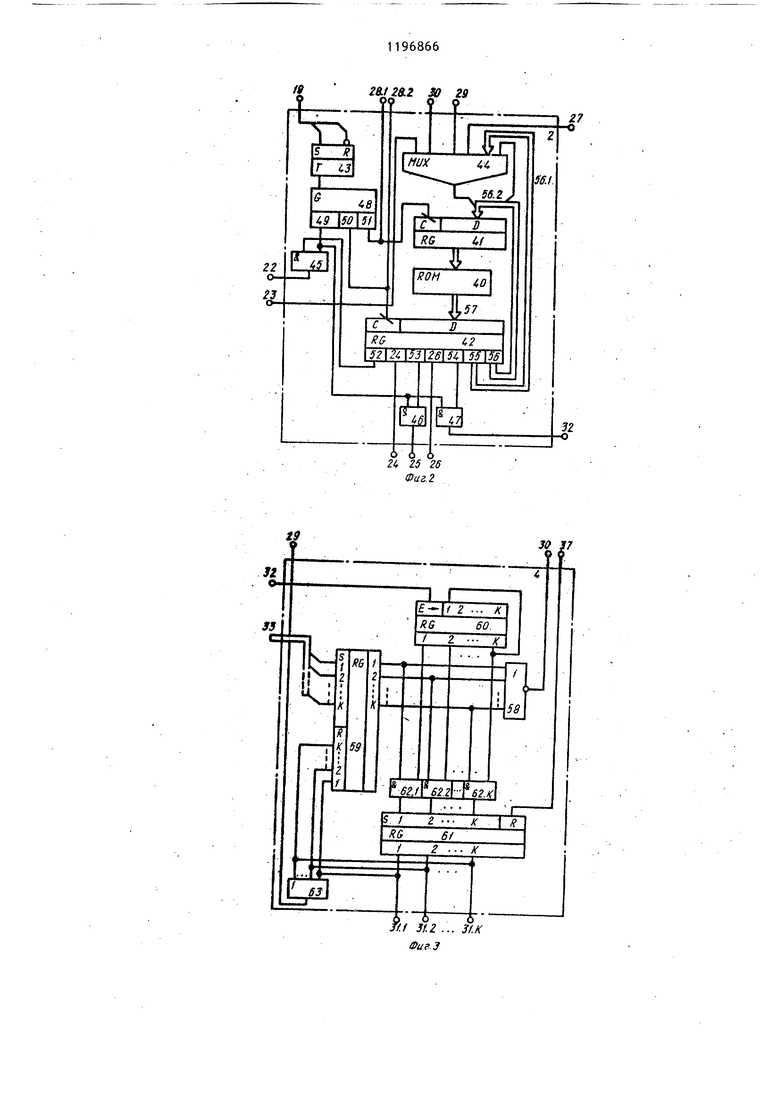

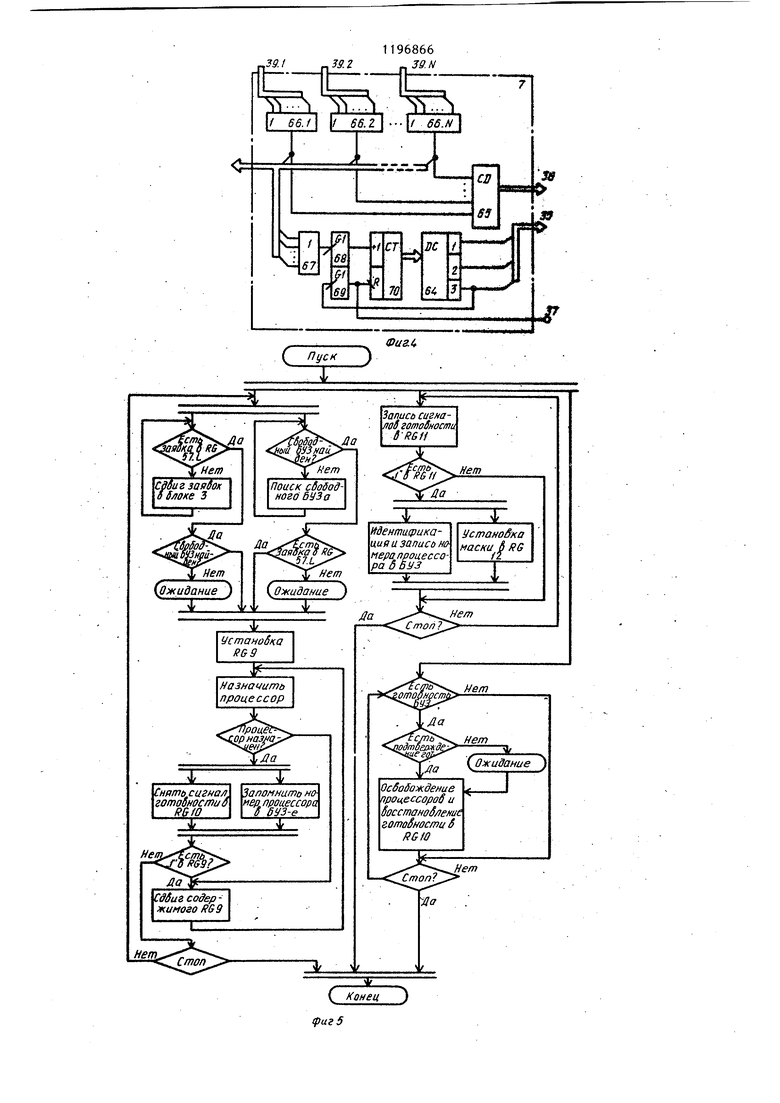

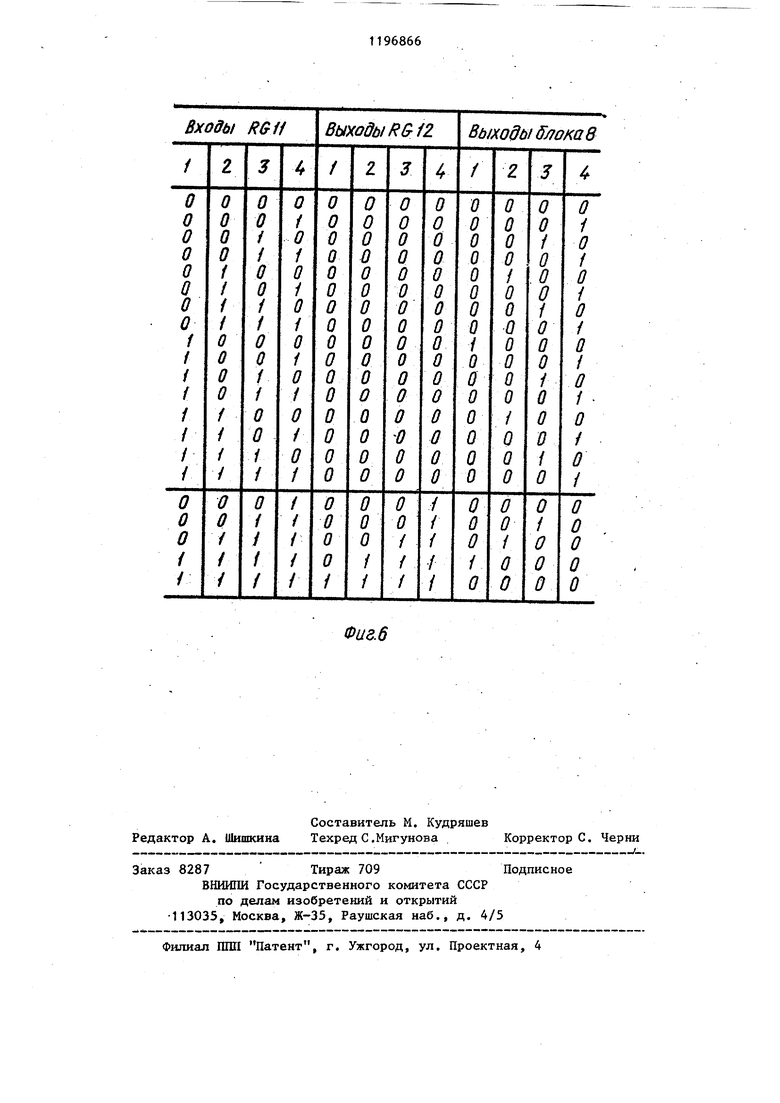

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока управления; на фиг. 3 - структурная схема блока выбора; на фиг. 4 - структурная схема блока занятия процессоров; на фиг. 5 - блок-схема алгоритма функционирования устройства; на фиг. 6 - таблица функционирования блока приоритета.

Устройство (фиг. 1) содержит группы информационных выходов 1 устройства, блок 2 управления, блок 3 хранения заявок, блок 4 выбора, группу блоков 5 регистров, группу блоков 6 дешифраторов, , блок 7 занятия процессоров, блок 8 приоритета, регистр 9 сдвига, регистр 10 готовности процессоров, регистр 11 дублирования, регистр 12 маскирования, шифратор 13, элемент ИЛИ 14, группу элементов ИЛИ 15, группу блоков элементов И 16, группу одновибраторОБ 17, группу информационных входов 18 устройства, вход 19 запуска устройства, группу 20 кодовых входов устройства, группу 21 сигнальных выходов устройства выход 22 блока 2, выход 23 блока 3, выходы 24-26 блока 2, вход 27 блока 2, выходы 28.1 и 28.2 блока 2, выход 29 и 30 блока 4, группу выходов 31 блока 4, выход 32 блока 2, группу выходов 33 блоков 5, группу выходов 34 шифратора 13, группы выходов 35 и 36 блока 7, выход 37 бло-ка 7, группу сигнальных входов 38 .устройства, группы входов 39 блока 7.

Блок 2 управления содержит (фиг.2) блок 40 памяти, регистры 41 и 42, триггер 43, мультиплексор 44, элементы И , генератор 48 импульсов, выходы 49-51 генератора 48, выходы 52-54 регистра 42, группы выходов 55 и 56 регистра 42, выход 57 блока 40 памяти. Блок 4 выбора содержит (фиг. 3) элемент ИПИ-НЕ 58, регистр 59 Состояния, регистр 60 сдвига, регистр 61 записи, группу элементов И 62, элемент ИЛИ 63.

БЛОК 7 занятия процессоров (фиг. 4) содержит дешифратор 64, шифратор 65, группу элементов ИЛИ 66, элемент ИЛИ 67, одновибраторы 68 и 69, счетчик 70.

Рассмотрим работу устройства.

В исходном положении все элементы памяти находятся в нулевом состояНИИ кроме регистра 10, который находится в единичном состоянии. Такое состояние регистра 10 соответствует состоянию готовности процессоров к выполнению заданий.

Каждое задание,запланированное для выполнения внешней операционной системой, идентифицируется кодом номера задания, поступающим на входы 18 устройства в виде заявки на обслуживание .

; . 31

llo сигналу пуска, поступакяцему на вход 19, устройство приводится в рабочее состояние.При этом работу устройства целесообразно рассматривать в следуюощх основных режимах (фиг. 5): формирование очереди заявок в блоке 3 хранения заявок; поиск свободного блока г 5.1 (16 ) управления задачей; назначение свободных процессоров блока 1 для выполнения задания; сохранение информации о процессорах, выполняющих задание; освобождение процессоров по заверщейию выполнения задания.

Формирование очереди заявок в блоке 3 осуществляется следующим образом.

По сигналу пуска триггер 43 устанавливается в единичное состояниеj и единичным потенциалом с единичного выхода триггера 43 разрешается формирование тактовой сетки импульсов генератором 48. Так как в блоке 3 заявок нет, на выходе 23 блока 3 установлен единичньй потенциал. Поступая на вход мультиплексора 44 блока 2, этот потенциал определяет модификацию младшего разряда адреса первой микрокоманды, которьй по тактовому импульсу с выхода 51 генератора 48 записывается в регистр 41. Выбранная из блока 40 микрокоманда по тактовому импульсу с выхода 50 генератора 48 записывается в регистр 42. Выход 52 регистра 42 в этой микрокоманде установлен в единичное Состояние.- Импульсы с выхода 49 генератора 48 через открытьй элемент И 45 поступают на выход 22 блока 2 и далее на тактовый вход блока 3.

Заявка, поступившая на входы 18 устройства, записывается в блок 3. По каждому тактовому импульсу на входе 22 осуществляется синхронный сдвиг заявок в блоке 3 и запись очередной заявки с входа 18 устройства. ормирование очереди заявок завершается после записи заявки в последнюю ячейку блока 3. При этом на высрде 23 блока 3 устанавливается нуевой потенциал, по которому завершается формирование импульсов на выоде 22. блока 2, так как в этом слуае из блока 40 считывается микрооманда, разряд 52 которой установен в нулевое состояние.

Возобновление формирования тактовых импульсов на выходе 22 блока 2 происходит после завершения рас968664

пределения заданий, что отмечается единичным сигналом на выходе 37 блока 7, поступающим на нулевой вход сброса блока 3.

J Режим поиска и назначения процессоров для вьшолнения задания реализуется в два этапа: поиск свободного блока 5, в котором сохраняются номера процессоров, назначенных для выfO полнения задания; поиск и назначение свободных, процессоров для вьшолнения задания.

Функции первого этапа выполняются блоком 4. Исходными состояниями гистров 59-61 этого блока к началу работы устройства являются: единичное состояние регистра 59 (это свидетельствует о том, что все блоки 5 свободны); единичное состояние пер2Q вого разряда регистра.60; единичное состояние первого разряда регистра 61.

Такое состояние регистра 61 устанавливается после вьшолнения начальной установки регистров 59 и 60. При этом единичный сигнал установки первого разряда регистра 61 формируется .на выходе элемента И 62.1, единичньш сигнал с первого разряда регистра 61 поступает на выход 29 блока 4

30 через элемент ШШ 63, а также уста-. навливает в нуль первьй разряд регистра 59. Так как .на выходе 29 блока 4 установлен вдиничньш потенциал, формирование тактовых пульсов на выходе 32 блока 2 запрещено и сдвиг содержимого регистра 60 не вьшолняется. Такое состояime блока 4 соответствует завершению этапа поиска свободного блока 5. После

40 назначения процессоров задаче регистр 61 устанавливается в нулевое состойние сигналом с выхода 37 блока 7. . При этом на выходе 29 блока 4 уста|Навливается нулевой- потенциал и бло ком 2 на выходе 32 формируются импульсы, которые вызывают сдвиг содержимого регистра 60 пока не будет найдет свободный блок 5.

После нахождения свободного блока

50 5 на соответствующем выходе 31 блока 4 устанавливается единичШ)1й по- . тенциал, разрешающий запись блока 5 на этапе назначения процессоров.

Для повышения достоверности 55 функционирования устройства каждое задание выполняется на трех процессорах, а данные, полученные после его выполнения, используются на ос5

нове мажоритарного голосования по принципу два из трех программными средствами внешней операционной системы.

Поиск и назначение свободных процессоров задаче происходит следующи образом.

По завершению процессов формированйя очереди заявок и поиска свободного блока 5 блоком 2 формируются сигналы разрешения записи на выводе 26 и начальной установки на выходе 24. При этом в регистр 9 сдвга записывается единица в первый разряд. По единичному сигналу готовности с выхода первого разряда регистра 10 открывается блок 16.1 элементов И и соответствующий процессо получает код номера задания. Одновременно код поступает на входы элемента ИЛИ 66.1 блока 7, на выходе которого формируется единичный сигнал. Этот сигнал используется для формирования кода занимаемого процессора, для сброса сигнала готовности занимаемого процессора, а также для управления записью в регистры блока 5 кода занимаемого процессора.

Код занимаемого процессора формируется шифратором 65 и поступает на выход 36 блока 7. Кроме того, единичный сигнал с выхода элемента ИЛИ 66.1 суммируется в счетчике 70, поступая на его счетньй вход через элемент ИЛИ 67 и одновибратор 68.

Выходной код счетчика 70 поступает на дешифратор 64, на первом выходе которого формируется единичный сигнал, поступающий на выход 35 блока 7. Дешифратор 64 используется для определения факта завершения распределения задания.

В начале работы устройства для хранения кодов процессоров, найначенных для решения задачи, выбирается блок 5.1 (фиг. 1).

Код занимаемого процессора с выхода 36 блока 7 поступает на первые входы блока 5.1.

При назначении первого процессора на выходе элемента И 62.1 устанавливается единичный сигнал и код занимаемого процессора записывается в регистр 5.1.

По следующему тактовому импульсу поступающему на вход сдвига ре968666

гистра 9 с выхода 25 блока 2, осуществляется кольцевой циклический сдвиг содержимого этого регистра. Для рассматриваемого примера единичный сигнал устанавливается на втором выходе регистра 9. При этом код задания устанавливается на выходе блока 16.2 элементов И. В дальнейшем процесс занятия соответствукяцего

О процессора протекает аналогично рассмотренному, а именно в счетчике 70 .блока 7 (фиг. 7) значение увеличивается на единицу, что соответствует выбору следующего регистра в блоке

5 5.1 для записи и хранения кода второго процессора, назначаемого задаче. Кроме того, осуществляется сброс сигнала готовности соответствующего процессора в регистре 10 единичным

0 сигналом с выхода элемента ИЛИ 66.2 блока 7, поступающим с группы выходов блока 7 на соответствующий нулевой вход регистра 10.

После назначения третьего процессора для решения задачи режим поиска и назначения свободных процессоров задаче завершается. В этом случае на третьем выходе дешифратора 64 устанавливается единичный потенциал,

30 по которому осуществляется запись в третий регистр блока 5.1 кода третьего назначаемого задаче процессора и обнуление счетчика 70 блока 7 отрицательным фронтом импульса, сформированного одновибратором 69. Импульс с выхода одновибратора 69 поступает на выход 37 блока 7, по которому в нулевое состояние устанавливаются регистр 9, блок 3 (фиг. 3)

40 и регистр 61 блока 4.

После установки в нулевое состояние блока 3 на выходе 23 устанавливается единичный потенциал, по которому запрещается формирование импульсов на выходе 25 блока 2 и разрешается формирование импульсов на выходе 22 этого блока. В дальнейшем работа устройства по назначению процессоров задаче протекает аналогично

50 рассмотренному. Режимы формирования очереди заявок в блоке 3 и поиск свободного блока 5 реализуются аналогично рассмотренному.

Режим поиска и назначение свобод55 -яьк процессоров реализуются по завершению первых двух режимов.

Рассмотрим реализацию режима освобождения процессоров по завершению 7 вьтолнения задания. Этот режим реал зуется параллельно с работой устрой ства в рассмотренных выше режимах. По завершению решения задачи про цессор выставляет единичньш потенци ал сигнала готовности на одном из входов 38. Тактовым импульсом с вых да 28.1 блока 2, посфупающим на управлякидий вход регистра 11, осуществляется запись сигналов готовности в регистр 11. С выходов регистра 11 сигналы готовности поступают в блок 8 приоритета, который вьщеляет из всех поступивших сигналов готовности процессоров сигнал наиболее приоритетного процессора. Приоритет процессора определяется ме с т ом подключе ния к блоку- 8, работа которого поясняется таблицей (фиг.. 6). Выходной сигнал блока 6 поступает на входы шифратора 13, формирующего код освобождаемого процессора Этот код поступает на входы блоков 5 и сравнивается с кодами, записанными в этом блоке. В случае пооче редного совпаде1шя всех кодов, записанных в блоке 5, с кодами, поступающими на входЬ 34, на выходе 21 этого блока устанавливается единичный сигнал, который поступает на группу выходов 21 устройства. После чего по импульСу с выхода 28.2, поступающему на управляющий вход регистра 12, осуществляется установка в единичное состояние разряда регистра 12, соответствующего единичному сигналу на выходе блока 8, .затем вновь производится запись сигналов готовности процессоров с входов 38 в регистр 11 и процесс фиксации освобождения повторяется г Сигналы на выходы 21 устройства информируют процессор верхнего уровня иерархии вычислительной системы 668 о завершении- выполнения задания. Процессор верхнего уровня осуществляет программное мажоритирование результатов работы трех.процессоров и выставляет сигнал разрешения освобождения процессоров на входах 20 устройства. С соответствуиицего входа 20 сигнал разрешения освобождения поступает на вход сброса соответствующего блока 5, единичньй сигнал с выхода 33 которого поступает.на вход управления соответствующего блока 6. В блоке 6, соответствующем освобождаемому блоку 5, осуществляется дешифрация кодов освобождаемых процессоров, при этом на выходах единичный сигнал с вьсхода блока 6 через соответствующие элементы ИЛИ 15 восстановит сигналы готовности соответствующих процессоров в регистре 10. В дальнейшем процессоры и блок 5, завершившие вьшолнение задания, могут быть назначены для выполнения очередного задания из очереди блока 3. Работа устройства завершается при снятии сигнала останова с входа 19 устройства. При этом триггер 43 блока 2 устанавливается в нулевое состояние и запрещает формирование тактовой сетки импульсов генератором 48. В случае изменения конфигурации процессорного поля, связанного с проведением профилактических или ремонтных работ, соответствующий разряд регистра 10 готовности в единичное состояние не устанавливается. Это соответствует занятому состоянию соответствующего процессора, который для вьшолнения заданий не назначается. В дальнейшем этот процессор может быть включен в работу без останова устройства.

xs

пь

{ .

м

л /7

/ г

к

58

.

J К

6f

I Оо

Л/ з(.г... 3I.K

,33.2

(Jfжuдaнue

1196866 39.N

Фа 8.6

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-28—Подача