eii) счетчика, выход которого ггоразрядно соединен с вторым входом блока формирования и распределения отпирающих импульсов.

2. Устройство по п.1, отличающееся тем, что оно снабжено входами управления минимальным и максимальным углами включения вентилей, блок сравнения выполнен четьфехвходовым в виде преобразователя код-аналог, трех компараторов, элемента И и элемента ИЛИ, причем вход преобразователя код-аналог является вторым входом блока сравнения, первый вход первого компаратора является первым

1 1 5

1

входом блокп сравнения., первые входы второго и третьего компа1)яторов являются третьим и четверт1 1Г1 входами блока сравнения и соединены соответственно с входами управления минималным и максимальным углами включения вентилей, вторые входы компараторов подключены к выходу преобразователя код-аналог, выходы первого и второго компараторов через элемент И подключены к первому входу элемента ИЛИ, второй вход которого подключен к выходу третьего компаратора, выход элемента ИЛИ является выходом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для импульсно-фазового управления вентильным преобразователем | 1982 |

|

SU1086544A1 |

| Одноканальное цифровое устройство для управления @ -фазным @ -пульсным вентильным преобразователем | 1990 |

|

SU1757057A1 |

| Способ фазового управления вентильным преобразователем | 1985 |

|

SU1257784A1 |

| Одноканальное цифровое устройство для импульсно-фазового управления вентильным преобразователем | 1982 |

|

SU1185546A1 |

| Цифровой синтезатор частот | 1976 |

|

SU799100A1 |

| Устройство для измерения скоростиРАСпРОСТРАНЕНия ульТРАзВуКА | 1979 |

|

SU849066A1 |

| Способ фазового управления асинхронным электродвигателем и устройство для его осуществления | 1978 |

|

SU928582A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| Устройство для управления @ -фазным вентильным преобразователем | 1989 |

|

SU1721756A1 |

| Преобразователь линейного перемещения в код | 1984 |

|

SU1274156A1 |

1. УСТРОЙСТВО ДЛЯ ИМПУЛЬСНОФАЗОВОГО УПРАВЛЕНИЯ Р-ПУЛЬСНЬМ ВЕНТИЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЕМ, содержащее блок синхронизации, генератор импульсов, первый счетчик, установочный вход которого соединен с первым выходом блока синхронизации, регистр памяти, информационный вход которого поразрядно соединен с выходом первого счетчикаj а синхронизирующий вход соединен с вторым выйсодом блока синхронизации, блок форьшрования и распределения отпирающих импульсов, блок сравнения, первый вход которого соединен с управляющим входом устройства нмпульсно-фазового управления, о т л и ч а ю ц е е с я тем, что, с це.лью повышения точности и симметрии отпирающих импульсов при одновременном упрощении канала синхронизации, в него введены первый делитель частоты, включенный между выходсж генератора импульсов и счетным входом первого счетчика, второй делитель частоты с управляемым кодом коэффициентом деления, второй счетчик, третий счетчик, выполненный на f состояний, преобразователь кодов и трехвходовый элемент И, причем вход второго делителя частоты соединен с выходом генератора импульсов, а управляющий коэффициентом деления вход поразрядно соединен с выходом регистра памяти, счетный вход второго счетчика соединен с выходом второго делителя частдты, а установочный вход соединен с одним из выходов блока синхрониза:S ции, которьй выполнен одноканальяым, первый вход преобразователя кодов поразрядно соединен с i -старвиши разрядами второго счетчика, где С разрядность числа р-1, второй вход преобразователя кодов поразрядно соединен с выходом третьего счетчика, второй вход блока сравнения своими 5-старшими разрядаьш поразрядно сое|динен с первым выходом преобразовате:п ля кодов, а остальными разрядами с остальньфш разрядами второго сяет:чика, где 5- разрядность числа - 1, округленного ближайяюго большего или равного «г- -1 целого чис;ла, а в - диапазон регулирования устройства импульсйо-фазового зтравлеяия, первый вход элемента И соедииеи с выходом блока срав1 ения, второй вход соединен с вторым выходом преобразователя кодов, третий вход еоедииен с выходом второго делителя частоты, а выход соединен с первьм входом блока формирования и распределения отпирающих импульсов и счетн1Л4 входом треть

Изобретение относится к электротехнике, а именно к устройствам, пред назначенным для импульсно-фазового управления вентильными преобразова- телями, работающими в условиях как постоянной, так и переменной частоты на входе.

Известно устройство импульснофазового управления, содержащее в каждом канале нуль-орган,счетчик,управ ляемый напряжением генератор импульсов цифровой компаратор, фазовый детектор и формирователь импульсов flj .

Недостатком данного устройства является низкое быстродействие по отношению к изменению частоты на входе преобразователя, связанное с большой инерционностью кольца фазовой автоподстройки частоты.

Наиболее близким к изобретению является устройство для импульснофазового управления, содержащее блок синхронизации, генератор импульсов, счетчик, регистр памяти, обратно пропорциональный преобразователь коданалог, интегрирующие устройства с зарядными конденсаторами, разрядные ключи, управляющие входы которых соединены с выходами блока синхронизации компараторы, первые входы которых соединены с входнбй управляющей шиной, и блок формирования и распределения отпирающих импульсов L2j

Это устройство обладает недостаточно высокой то.ностью и симметрией

отпирающих импульсов. Кроме того, устройство синхронизируется с питающей преобразователь сетью с помощью многофазного синхронизирующего трансформатора и требует выполнения блока синхронизации по многоканальной схеме

Целью изобретения является повышение точности и симметрии отпираннцих импульсов при одновременном упрощении канала синхронизации.

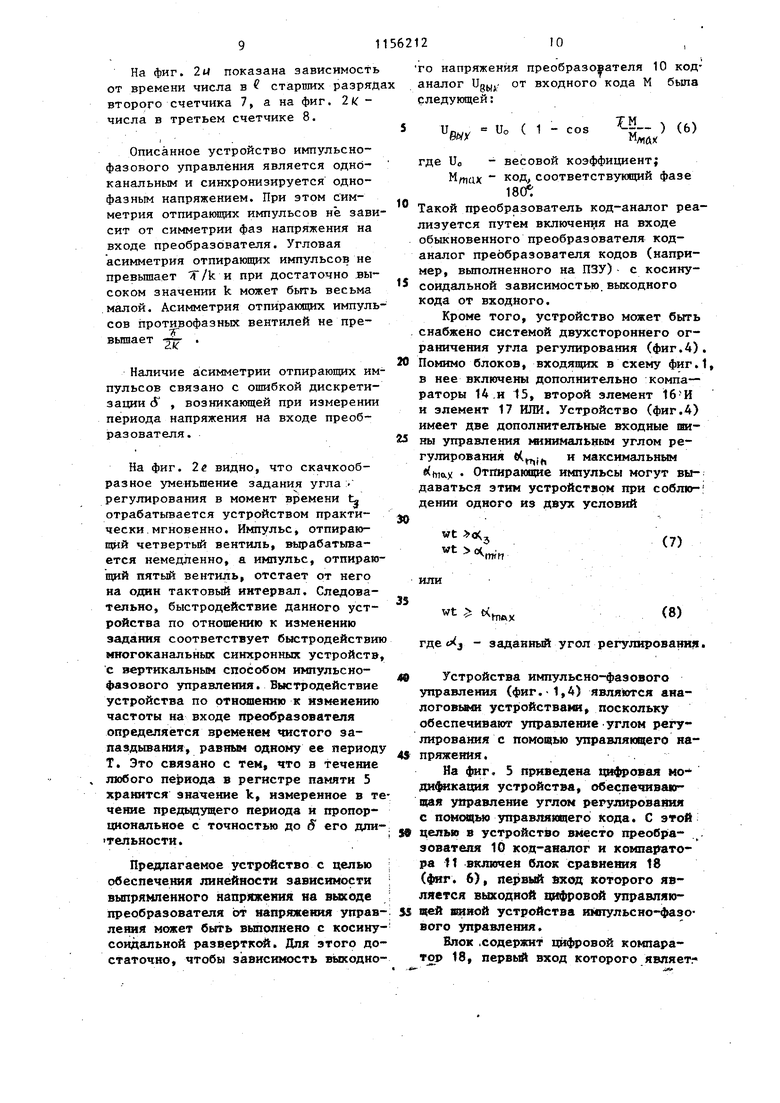

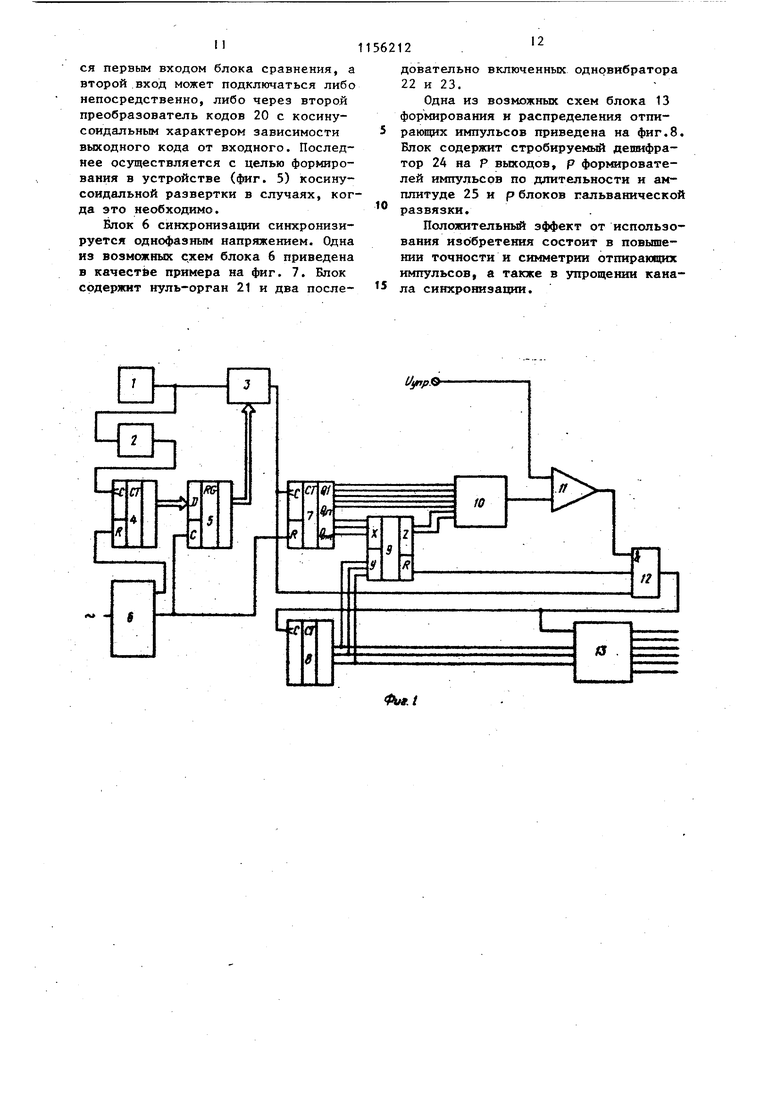

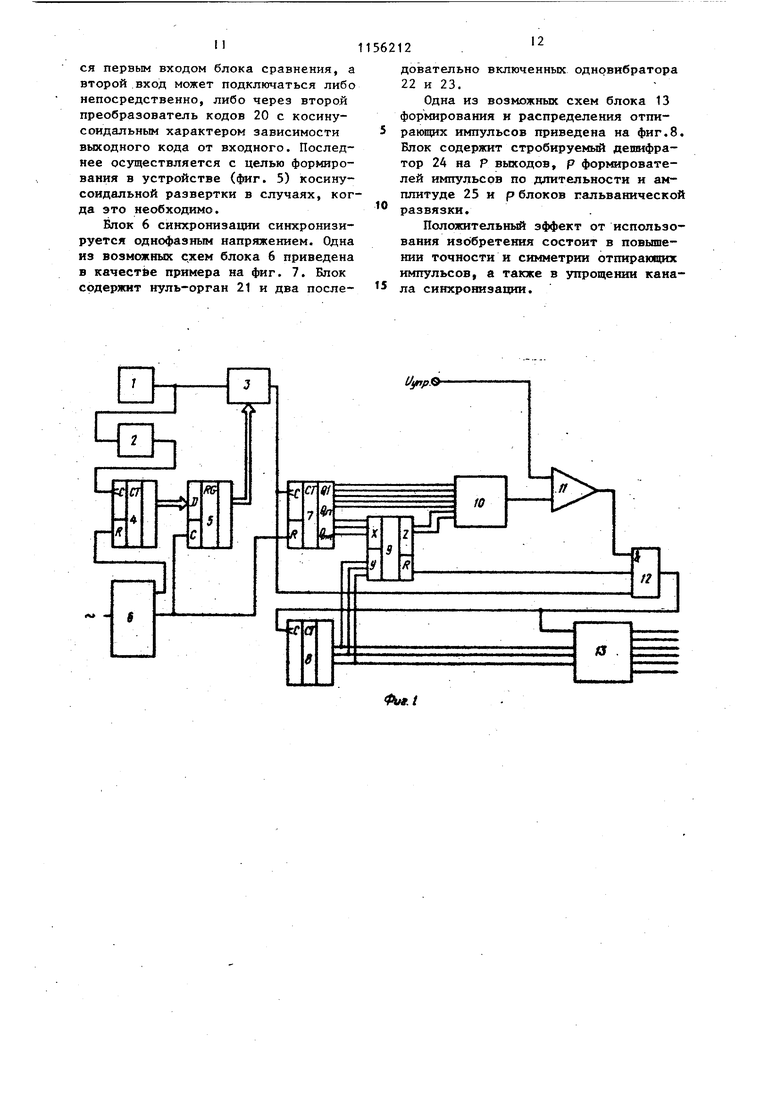

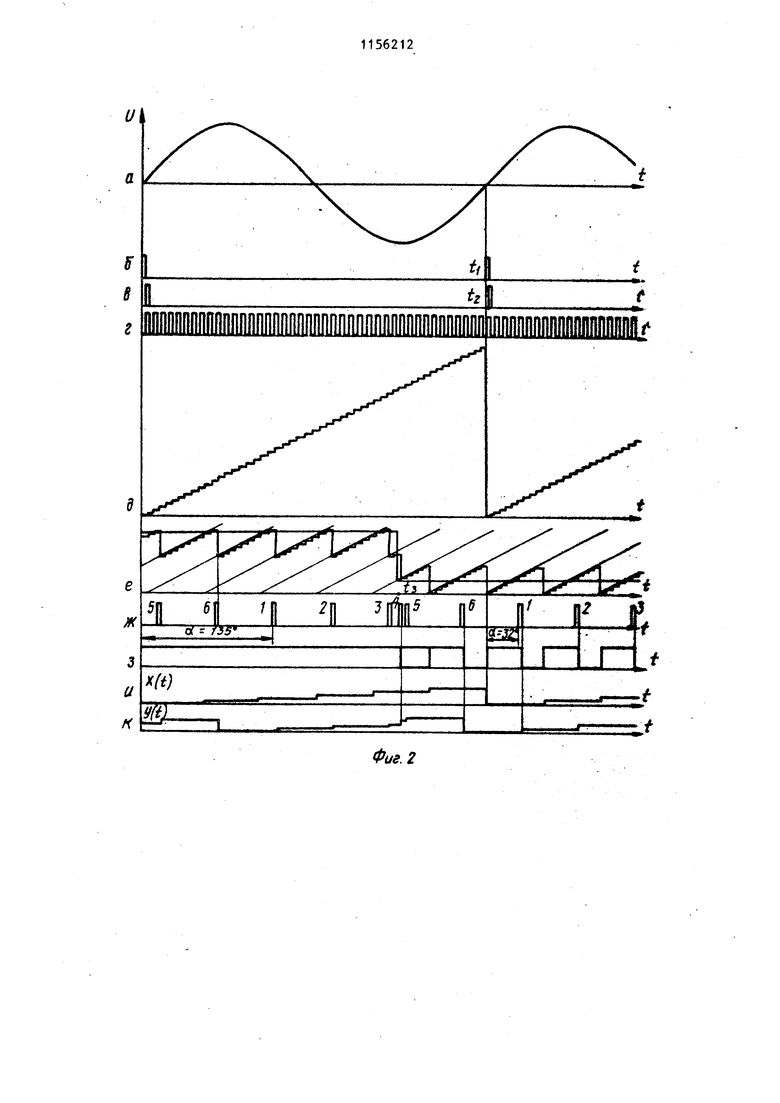

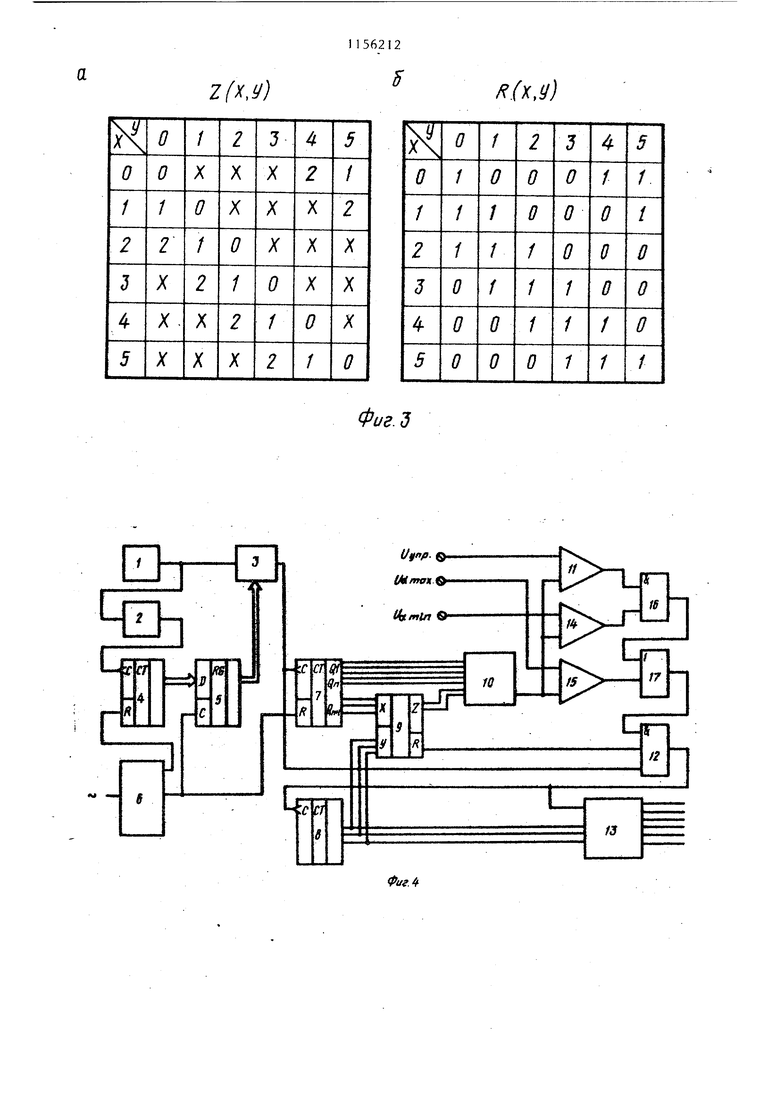

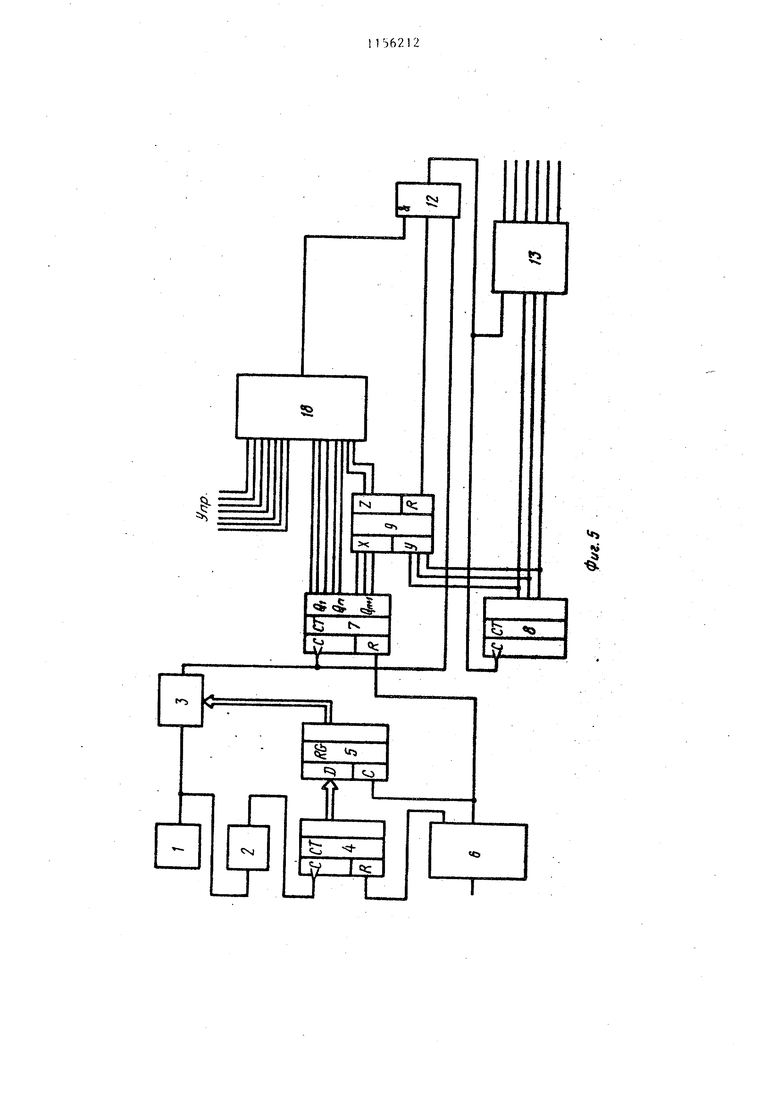

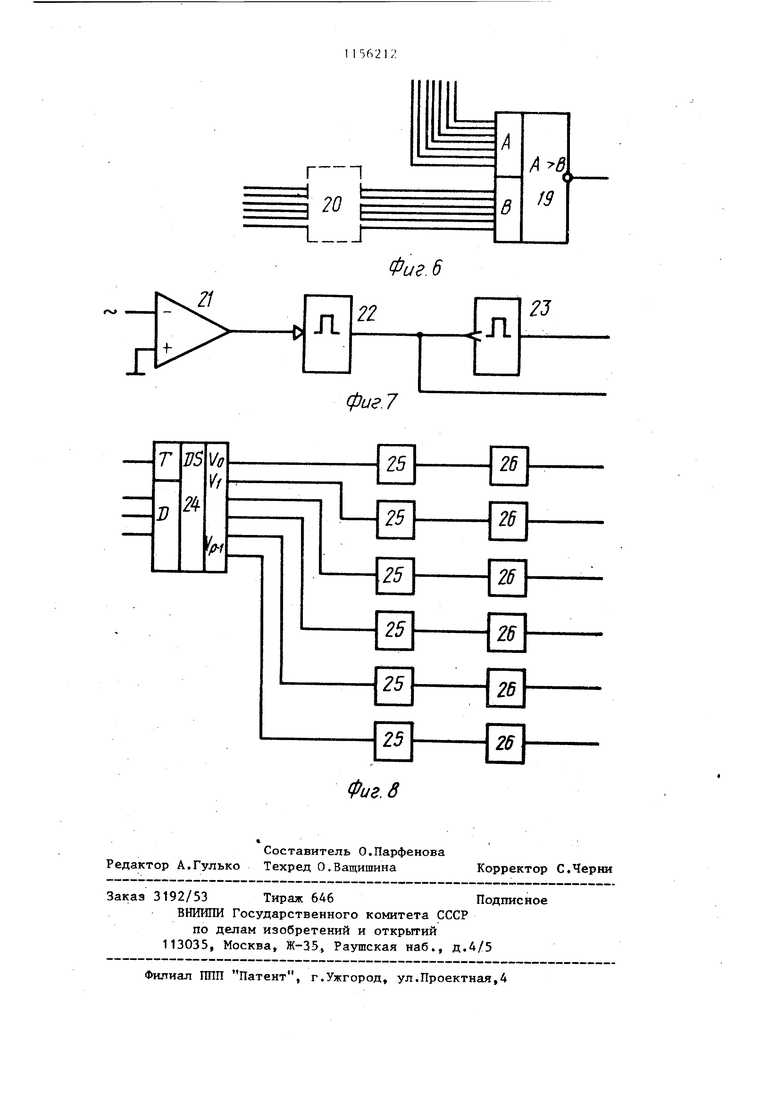

Цель достигается тем, что в устройство для импульсно-фазового управления р -пульснь)м вентильным преобразователем, содержащее блок синхронизации, генератор импульсов,первый счетчик, установочный вход которого соединен с первым выходом блока синхронизащга, регистр памяти, информационный вход которого поразрядно соединен с выходом первого счетчика, а синхронизирующий вход соединен с вторым выходом блока синхронизации,блок формирования и распределения отпирающих импульсов, первый блок сравнения, первьй вход которого соединен с управляющим входом устройства импульснофазового управления, введены первый делитель частоты, включенный между выходом генератора импульсов и счетным входом первого счетчика, второй делитель частоты с управляемым кодом коэффициентом деления, второй счетчик третий счетчик, выполненный на Р состояний, преобразователь кодов и трехвходовый элемент И, причем вход второго делителя частоты соединен с выходом генератора импульсов, а управляющий коэффициентом деления вход поразрядно соединен с выходом регистра памяти, счетньй вход второ го счетчика соединен с выходом второго делителя частоты, а установочный вход соединен с одним из выходов блока синхронизации, который выполйен одноканальным, первый вход преобразователя кбдов поразрядно соединен с :Х-старшими разрядами второго счетчика, где В. - разрядность числа Р-1, второй вход преобразователя кодов поразрядно соединен с выходом третьего счетчика, вход первого блока сравнения код-аналог своими 5старшими разрядами поразрядно соединен с первым выходом преобразоватёля кодов, а остальными разрядами с остальными разрядами второго счетчика, где 5- разрядность числа -1, округленного до ближайшего большег или равного - -1 целого числа, а в диапазон регулирования устройства ийпульсно-фазового управления, первый вход злемента И соединен с выходом первого блока сравнения, второй вход соединен с вторым выходом преобразователя кодов, третий вход соединен с выходом второго делителя частоты, а выход соединен с первым входом блока формирования и распределения отпирающих импульсов и счетным входом третьего счетчика, выход которого поразрядно с вторым входом блока формирования и распределения отпирающих импульсов. Устройство может быть снабжено входами управления минимальным и мак симальным углами включения вентилей блок сравнения выполнен четьфехвходовым в виде преобразователя коданалог, трех компараторов, элемента И и элемента ИЛИ, причем вход преобразователя код-аналог является вто. рым входом блока сравнения, первый вход первого компаратора является первым входом блока сравнения, первые входы второго и третьего ixoMnaраторов являются третьим и четвертым входами блока сравнения и соединены соответственно с входами управления минимальным и максимальным углами включения вентилей, вторые входы компараторов подключены к выходу преобразователя код-аналог, выходы первого и второго компараторов через элемент И подключены к первому входу элемента. ИЛИ, второй вход которого подключен к выходу третьего компаратора, выход элемента ИЛИ является выходом блока сравнения. На фиг. 1 показана схема устройства импульсно-фазового управления; на фиг. 2 - диаграммы, поясняющие работу схемы; на фиг. 3 :- таблица соответствий преобразователя кодов; на фиг. 4 схема управления; на фиг.5схема с цифровым блоком сравнения: на фиг. 6 - вариант выполнения цифрового блока сравнения; на фиг. 7 пример вьшолнения блока синхрониза- , ции; на фиг. 8 - пример выполнения блока формирования и распределения отпирающих импульсов. Устройство содержит генератор импуль сов I,первый делитель 2 частоты,второй делитель 3 частоты с зшравляемым кодом коэффициентом деления,первьй счетчик 4 , регистр 5памяти,блок 6синхронизации, второй счетчик 7,третий счетчик 8 на р состояний, преобразователь 9 кодов, блок сравнения, состоящий из преобразователя 10 код-аналог с линёйньм или косинусоидальным характером зависимости выходного сигнала от входного кода и компаратора 1t, элемент 12 и блок 13 формирования и распределения отпирающих импульсов. Устройство работает слеДуницим образом. Генератор 1 импульсов генерирует импульсы с постоянной частотой следования F, превьшающей во много раз частоту f на входе преобразователя. Второй делитель 3 частоты делит частоту F на некоторую целую переменную К таким образом, чтобы на счетном входе второго счетчика 7 всегда поддерживалась частота в р-2 раз, пре вышающая частоту f на входе преобразователя, которая может быть переменной и изменяться в широких пределах. Таким образом, код коэффи1р1ента деления К выбирается автоматически в зависимости от длительности периода частоты f. В общем случае частота F превьшает частоту f в некотрое достаточно большое переменное число В раз. Условно разобьем число В на два сомножителя, один из которых р2 является постоянным целым коэффициентом, а другой сомножитель обратно пропорционален f. Наличие огаибки дискретизации if связано с тем, что делитель частоты 3 может разделить частоту F только на целое число k в то время, как отношение частот F и f может оказаться дробным, Тогда справедливо уравнение, связывающее переменные f и k : F B-f p. 2 (k +(5) -f где -1 C (Г . 1. Делитель частоты 2 делит частоту F на р- 2 и на его выходе выделяются импульсы, следующие с постоянной частотой (k ) f. Напряжение синхронизации, действующее на входе блока 6, показано на фиг,20 Оно изменяет свой знак с отрицательного на положительньй в момент естес твенного отпирания первого вентиля. Блок 6 синхронизации вьщеляет на своих втором и первом выходах узкие импульсы (фиг. 2 S VL соответственно) , следующие с частотой f. Первый счетчик 4 осуществляет подсчет импульсов делителя частоты 2, следующих с постоянной частотой (k +(f)f в течение периода частоты f. По окон чании периода в момент времени t/ (фиг. 2б) число импульсов, сосчитанное первьтм счетчиком, равное целой части k величины k (У, переписьгоается в регистр 5 памяти. В момент времени Ъ(фиг. 2) первый счетчик 4 сбрасывается. Таким образом, в регистре памяти записан коэффициент деления k управляемого кодом делителя частоты 3, которьй с точностью до С пропорционален периоду Т напряжения на входе преобразователя и об ратно пропорционален частоте f. Частота на выходе второго делителя час тоты 3 с управляемым кодом коэффициентом деления составляет p. p.a(/M-f(2 Импульсы, следукяцие с этой частотой вьзделяются на выходе делителя частоты 3 (фиг. tj). Зная, что величина S по модулю не превышает единицы, полагаем частоту этих импульсов равнойр.2(11 4- )-f При достаточно большой величине k ошибкой дискретизации можно пренебречь, поэтому в дальнейшем будем считать частоту на выходе делителя частоты 3 с управляемым кодом коэффициентом деления равной р. f Таким образом, за период Т 1/f на выходе делителя 3 частоты вьщеляется Р2 импульсов (фиг. ), а за интервал времени Т/р - 2 импульсов. Второй счетчик 7 осуществляет подсчет этих импульсов в течение -периода частоты f и сбрасывается импульсом (фиг, 25), Зависимость от времени числа во втором счетчике 7 приведена на фиг. 2й. Разрядность второго счетчика равна разрядности числа р. 2 -1, равной п+ , где разрядность числа р-1. Так, например, при р 6 3 (разрядность числа 5). Число во втором счетчике пропорционально с некоторой точностью дискретизации фазе wt, отсчитываемой от момента естественного отпирания первого вентиля, причем число в его 2 старших разрядах (фиг. 2ц) соответствует номеру от О до р-1 интервала длительностью Т/р, в котором в данный момент находится фаза wt, а число в его остальных П разрядах соответствует угловому положению текущей фазы относительно начала этого интервала. Фаза, отсчитанная от момента естественного отпирания любого вентиля, отличается от фазы wt, отсчитанной от момента естественного отпирания первого вентиля, на угол, кратный 2/Г/р, Следовательно, число, соответствующее фазе, отсчитанной от момента естественного отпирания любого вентиля (в том числе очередного), отличается от числа во втором счетчике 7 лишь своими старшими t разрядами. Фаза анодного напряжения очередного вентиля однозначно определяется его номером и фазой анодного напряжения первого вентиля. При этом младшие л разрядов числа импульсов, поступивших на счетный вход второго счетчика, начиная с момента естественного отпирания очередного вентиля, соответствуют гг мпадшим разрядам числа во втором счетчике, а остальные разряды этого числа однозначно связаны с числом в остальных t разрядах второго счетчика и номером очередного вентиля. Число в третьер счетчике 8, выполненном на р состояний (от О до р-1/ всегда на единицу меньше номера очередного вентиля (фиг. 2к) . Так, например, при , если очередной вентиль шестой, число в счетчике 8 равно 5. Преобразо1йатель кодов 9 преобразует число в i старших разрядах второго счетчика и число в i разряда третьего счетчика (номер очередного вентиля без единицы) таким образом, что на входе преобразователя 10 коданалог присутствует код фазы анодного напряжения очередного вентиля.Кроме того,преобразователь 9 кодов снабжен вторым одноразрядным выходом R, на котором присутствует логическая единица, если фаза анодного напряжения лежит в пределах диапазона регулирования О -0 , и логический ноль, если фаза находится вне этих пределов. Преобразователь кодов 9 реализуется на базе постоянных запоминающих устройств (ПЗУ).Разрядность его первого вьжода z равна разрядности величины - 1, округленной до целого числа в сторону увеличения, т.е. разрядности уменьшающегося на единицу числа интервалов длительностью Т 7р, умещакицихся в диапазоне регулировакия. Пример зависимостей состояния выходов z(x,y) и R(x,y) преобразователя кодов 9, выполненного для , 6 Т от состояния его входов показан на фиг. Зо соответственно. Значения чисел z(x,y) и R(x,y) (фиг. 3) совместно с соответствующими адресами х,у, будучи переведенными в двоичную систему счисления, представляют собой программу для записи ПЗУ, например типа К556РТ5. Преобразователь кодов 9 для , 0 27Г реализуется на одной микросхеме типа К556РТ5 путем пpoгpa в и рования 144х ячеек последней. Состояния кода Z, помеченные знаком X в таблице истинности преобразователя кодов (фиг. За.), безразличны, посколь ку и фаза в этих состояниях лежит вне пределов диапазона регулирования (в дальнейшем для простоты будем считать; что z(xvy) в этих случаях равно нулю). Если происходит вьщача импульса, отпирающего очередной вентиль s состояние третьего счетчика В изменяется, если при этом R продолжает оставаться равньм единице, код на втором входе преобразователя 10 код-аналог уменьшается на 2 . На фиг. 2с показаны зависимости от времени напряжения.на выходе преобразователя 10 код-аналог (при этом предполагается, что преобразователь коданалог выполнен линейным) и задания на управляющем входе устройства импульсно-фазового управления. Тонкими линиями показаны зависимости от времени текущих фаз анодных напряжений вентилей, откуда видно, что при код на входе преобразователя код-аналог с точностью дискретизации пропорционален фазе анодного напряжения очередного вентиля. Зависимость от времени напряжения на втором выходе R преобразователя кодов приведена на фиг. 2л. Из этой диаграммы видно, что , когда очередной вентиль отпирается, а момент естественного отпирания следующего еще не наступил, т.е. фаза анодного напряжения следукяцего вентиля отрицательна. Компаратор 1t срабатьгаает при достижении фазой анодного напряжения очередного вентиля величины, заданной на управлякяцем входе устройства, и после поступления очередного импульса с выхода делителя частоты 3 срабатывает элемент И 12, а на его выходе выделяется импульс (фиг.2.) .Появле- «ие этого импульса вызьгаает срабатывание блока 13 формирования и распределения отпирающих импульсов и вьщачу отпирающего импульса на управляющий электрод очередного вентиля. Окончание импульса на выходе элемента И (фиг. 2)|с) вызывает изменение состояния третьего счетчика В, после чего, если , на втором входе компаратора начинает вьщеляться напряжение, пропорциональное с точностью дискретизации фазе анодного напряжения следукяцего вентиля. Если после изменения состояния третьего счетчика В на выходе R преобразователя кодов вьщеляется напряжение логического нуля, это означает, что момент естественного отпирания елеДУЩ о вентиля еще не наступил (фаза отрицательна), а код фазы анодного напряжения установится на входе преобразователя код-аналог после его наступления. Из фиг. 22 видно, что R может равняться нулю лишь при 4 -2Г условии „ . . .. О о( где nl. - угол регулирования. На фиг. 2ч показана зависимость от времени числа в старпшх разряд второго счетчика 7, а на фиг. 2к числа в третьем счетчике 8. Описанное устройство импульснофазового управления является одноканальным и синхронизируется однофазным напряжением. При этом симметрия отпирающих импульсов не зави сит от симметрии фаз напряжения на входе преобразователя. Угловая асимметрия отпирающих импульсов не превышает T/k и при достаточно .высоком значении k может быть весьма .малой. Асимметрия отпирающих импуль сов противофазных вентилей не превьшает -гг- Наличие асимметрии отпирающих им пульсов связано с ошибкой дискретизации (У , возникающей при измерении периода напряжения на входе преобразователя. На фиг. 2е видно, что скачкообразное уменьшение задания угла регулирования в момент времени U отрабатьгаается устройством практически мгновенно. Импульс, отпирающий четвертый вентиль, вырабатывается немедленно, а импульс, отпирающий пятый вентиль, отстает от него на один тактовый интервал. Следовательно, быстродействие данного устройства по отношению к изменению зада1шя соответствует быстродействию многоканальных синхронных устройств с вертикальным способом импульснофазового управлетм. Быстродействие устройства по отнсяпению к изменению частоты на входе преобразователя определяется временем чистого запаздывания, равным одному ее периоду Т. Это связано с тем, что в течение любого периода в регистре памяти 5 хранится значение k, измеренное в те чение пред1едущего периода и пропорциональное с точностью до S его длительности. Предлагаемое устройство с целью обеспечения линейности зависимости выпрямленного напряжения на выходе преобразователя от напряжения управления может быть выполнено с косину соидальной разверткой. Для этого достаточно, чтобы з;ависимость выходно о напряжения преобразователя 10 коданалог Ugy, от входного кода М бьша рледукщей: ) Uo ( 1 - COS М/утйх где Uo - весовой коэффициент; код, соответствующий фазе Такой преобразователь код-аналог реализуется путем включения на входе обыкновенного преобразователя коданалог преобразователя кодов (например, выполненного на ПЗУ) с косинус оидал ьной 3 ависимост ью.выходного кода от входного. Кроме того, устройство может быть снабжено системой двухстороннего ограничения угла регулирования (фиг.4). Помимо блоков, входящих в схему фиг.1, в нее включены дополнительно компа- раторы 14.и 15, второй злемент 16-И и элемент 17 ШШ. Устройство (фиг.4) имеет две дополнительные входные шины управления в1нимальным углом регулирования e(fT,ih максимальным tnax Отпирающие импульсы могут выдаваться этим устройством при соблюдении одного из двух условий wt к, Wt wt.- (8) где - заданный угол регулирования, Устройства импульсно-фазового управления (фиг.-1,4) являются аналоговюос устройствами, поскольку обеспечивают управление-углом регулирования с помощью управляющего напряжения .. На фиг. 5 приведена цифровая моди кадия устройства, обеспечивающая у11равление углом регулирования с помощью згправлямцегЪ кода. С этой целью в устройство вместо преобра- .. зоватеяя 10 код-аналог и компаратора 11 включен блок сравнения 18 (г. 6), первый йхед которого является выходной {щфровой управляющей кияой устройства импульсно-фазового управления. Влок .содержит цифровой компаратор 18, первый вкод которого является первым входом блока сравнения, а второй .вход может подключаться либо непосредственно, либо через второй преобразователь кодов 20 с косинусоидальным характером зависимости выходного кода от входного. Последнее осуществляется с целью формирования в устройстве (фиг. 5) косинусоидальной развертки в случаях, когда это необходимо.

Блок 6 синхронизации синхронизируется однофазным напряжением. Одна из возможных схем блока б приведена в качестве примера на фиг. 7. Блок содержит нуль-орган 21 и два последовательно включенных одновибратора 22 и 23.

Одна из возможных схем блока 13 формирования и распределения отпирающих импульсов приведена на фиг.8. Блок содержит стробируемый депмфратор 24 на Р выходов, р формирователей импульсов ПС длительности и амплитуде 25 и р блоков гальванической развязки.

Положительный эффект от использования изобретения состоит в повышении точности и симметрии отпирающих импульсов, а также в упрощении канала синхронизации.

а

2(.У}

/(х,У)

Фиг.д

L

П

Г

c 4

to t

t к

3

tr.

i

J

t: «NJ

i/

1Л

Ni1

US

ct

1

Uf

4s

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Материалы конференции IAS, IEEE-TAS, 1979 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-05-15—Публикация

1983-10-05—Подача