(54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с дробным переменным коэффициентом деления | 1974 |

|

SU506130A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Синтезатор частот | 1979 |

|

SU785943A1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Синтезатор частот | 1980 |

|

SU1059673A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Синтезатор частот | 1987 |

|

SU1555862A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Синтезатор частот | 1978 |

|

SU824451A1 |

1

Изобретение относится к радиотехнике и может использоваться в системах радиосвязи и измерительной аппаратуре.

Известен делитель частоты с дробным коэффициентом деления, состоящий из последовательно соединенных блока управления, программирукицего блока, блока исключения импульсов и счетчика, выход блока управления соединен с управляющим входом счетчика а вход делителя соединен с сигнальным входом блока исключения импульсов и с сигнальным входом программирующего блока,.управляющий вход которого связан с выходом делителя 1. . Наиболее близким по технической сущности к предлагаемому является цифровой синтезатор частот, соДерх ащий соединенные в кольцо синхронизируемый генератор, делитель частоты с дробным коэффициентом деления, импульсно-фазовый детектор, сумматор и фильтр нижних частот, ко входу импульсно-фазового детектора подключен выход источника опорной частоты, а ко входу сумматора подсоединен выход цифроаналогового преобразователя 2} Однако известный цифровой синтезатор частот не обеспечивает высокого подавления в выходном сигнале помех, кратных шагу сетки частот.

Цель изобретения - улучшение подавления в ввлходном сигнале помех, кратных шагу сетки частот.

Поставленная цель достигается тем, что, в цифровой синтезатор частот. ме)щу поразрядными информационными выходами пересчетных схем дробного

10 остатка программирующего блока и соответствующими поразрядными входами цифроаналогового преобразователя ; дополнительно введен блок памяти, управляющий вход которого соединен с

15 ,выходом делителя.

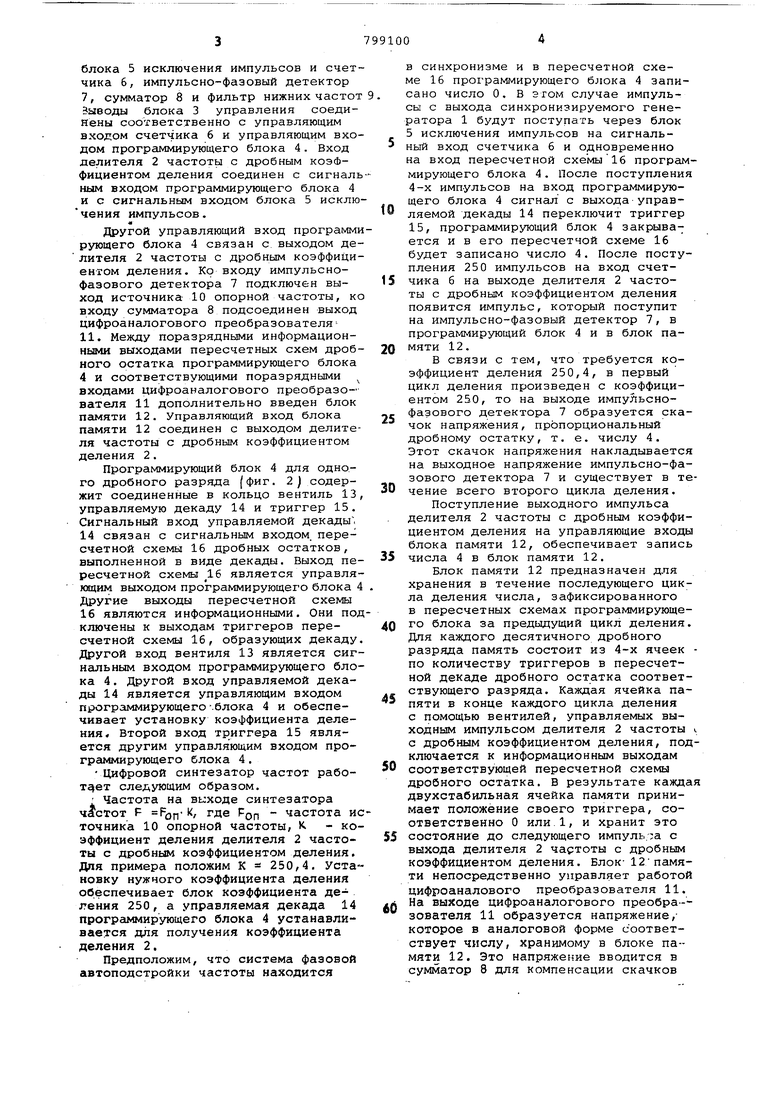

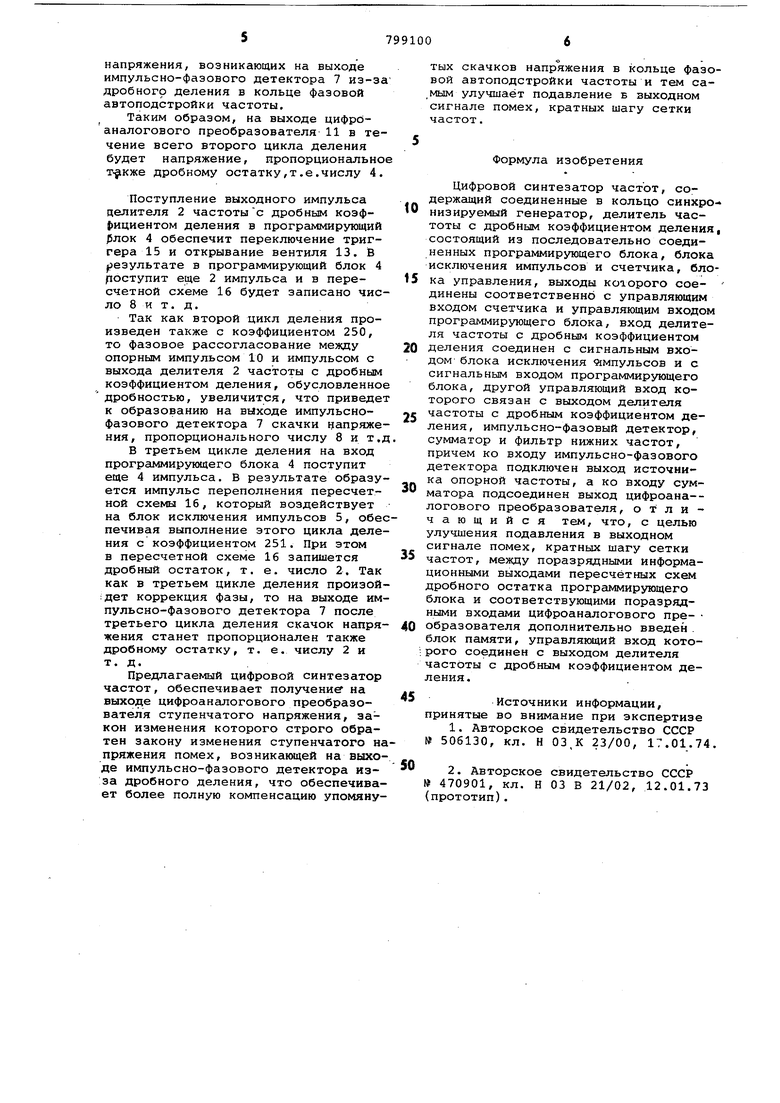

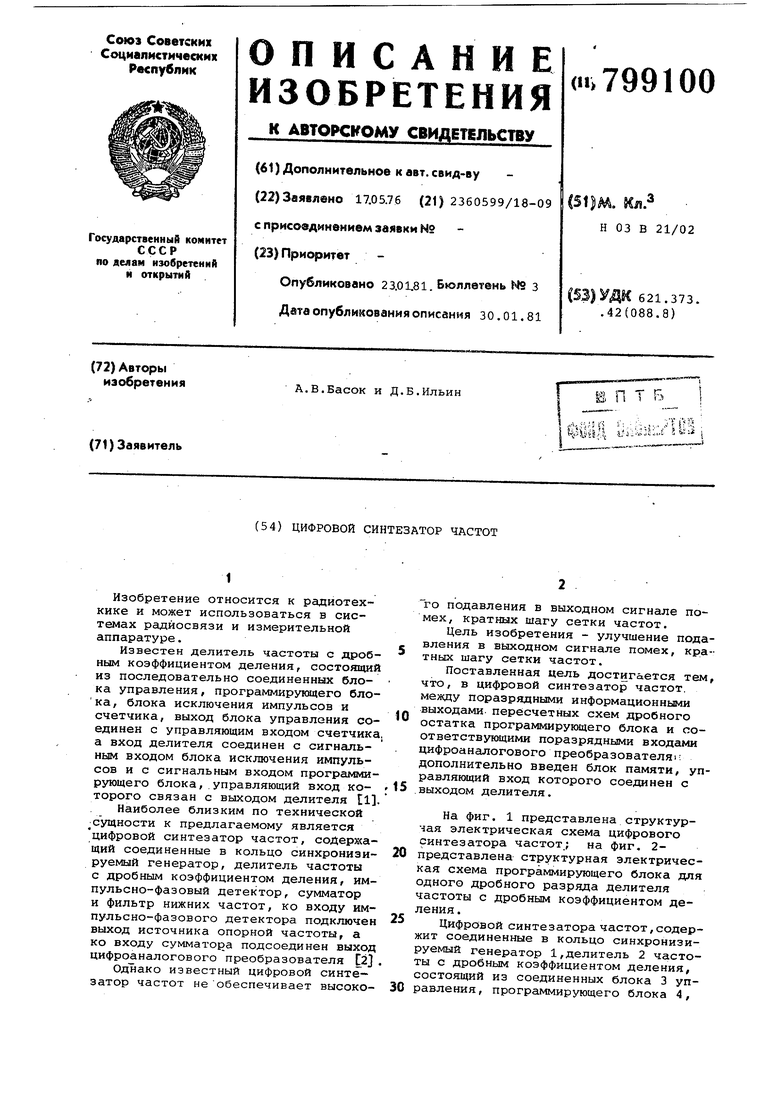

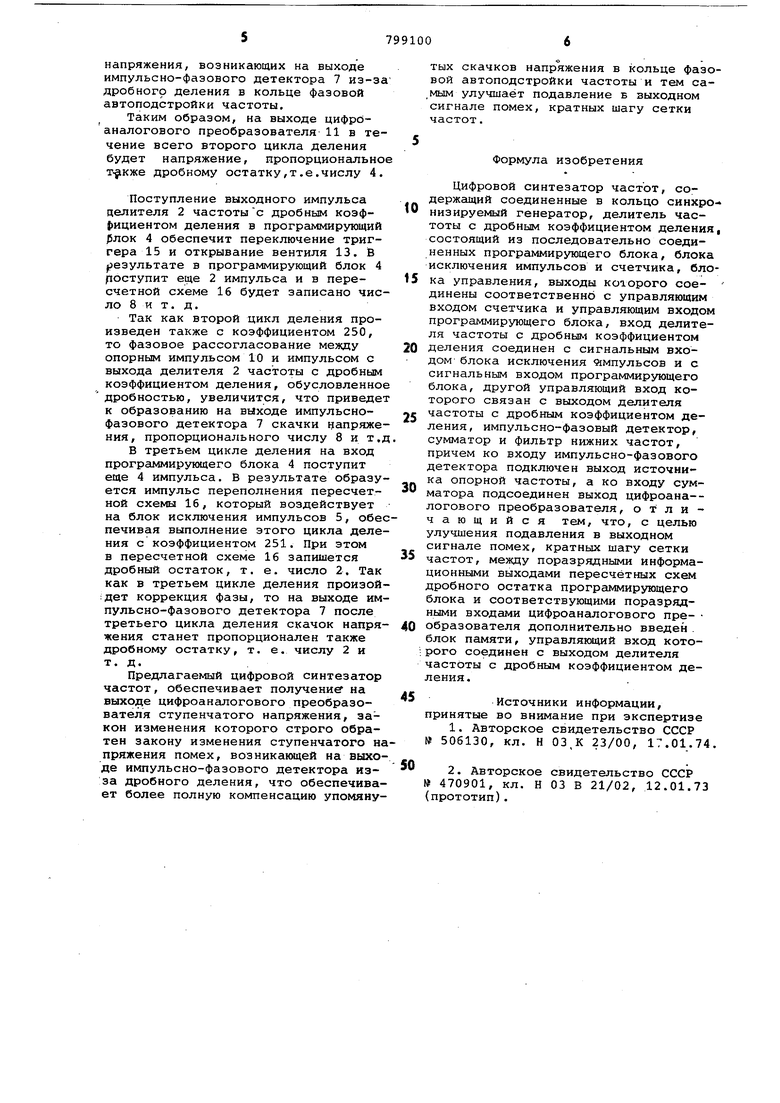

На фиг. 1 представлена структурчая электрическая схема цифрового синтезатора частот; на фиг, 220представлена структурная электрическая схема программирующего блока для одного дробного разряда делителя частоты с дробным коэффициентом деления .

25

Цифровой синтезатора частот,содержит соединенные в кольцо синхронизируемый генератор 1,делитель 2 частоты с дробным коэффициентом деления, состоящий из соединенных блока 3 уп30равления, программирующего блока 4,

блока 5 исключения импульсов и счетчика 6, импульсно-фаэовый детектор 7, сумматор 8 и фильтр нижних частот Выводы блока 3 управления соединены соответственно с управляющим входом счетчика 6 и управляющим входом программирующего блока 4. Вход делителя 2 частоты с дробным коэффициентом деления соединен с сигнальным входом программирующего блока 4 и с сигнальным входом блока 5 исключения импульсов.

Другой управляющий вход программирующего блока 4 связан с выходом делителя 2 частоты с дробным коэффициентом деления. Ко входу импульснофаэового детектора 7 подключен выход источника 10 опорной частоты, ко входу сумматора 8 подсоединен выход цифроаналогового преобразователя 11. Между поразрядными информационными выходами пересчетных схем дробного остатка программирующего блока 4 и соответствующими поразрядными входами цифроаналогового преобразователя 11 дополнительно введен блок памяти 12. Управляющий вход блока памяти 12 соединен с выходом делителя частоты с дробным коэффициентом деления 2.

Программирующий блок 4 для одного дробного разряда (фиг. 2) содержит соединенные в кольцо вентиль 13, управляемую декаду 14 и триггер 15. Сигнальный вход управляемой декады , 14 связан с сигнальным входом, пересчетной схемы 16 дробных остатков, выполненной в виде декады. Выход пересчетной схемы Дб является управляющим выходом программирующего блока 4 Другие выходы пересчетной схемы 16 являются информационными. Они подключены к выходам триггеров пересчетной схемы 16, образующих декаду. Другой вход вентиля 13 является сигнальным входом программирующего блока 4. Другой вход управляемой декады 14 является управляющим входом программирующего -.блока 4 и обеспечивает установку коэффициента деления. Второй вход триггера 15 является другим управляющим входом программирующего блока 4.

Цифровой синтезатор частот работ ет следующим образом.

/ Частота на выходе синтезатора частот F Fbn яе РОГ, - частота источника 10 опорной частоты, К. - коэффициент деления делителя 2 частоты с дробным коэффициентом деления. Для примера положим К - 250/4. Уста™ новку нужного коэффициента деления обеспечивает блок коэффициента дегення 250, а управляемая декада 14 программирующего блока 4 устанавливается для получения коэффициента деления 2.

Предположим, что система фазовой автоподстройки частоты находится

в синхронизме и в пересчетной схеме 16 программирующего блока 4 записано число 0. В эгом случае импульсы с выхода синхронизируемого генератора 1 будут поступать через блок 5 исключения импульсов на сигнальный вход счетчика 6 и одновременно на вход пересчетной схемы16 программирующего блока 4. После поступления 4-х импульсов на вход программирующего блока 4 сигнал с выхода управляемой декады 14 переключит триггер 15, программирующий блок 4 закрывается и в его пересчетчой схеме 16 будет записано число 4. После поступления 250 импульсов на вход счетчика б на выходе делителя 2 частоты с дробным коэффициентом деления появится импульс, который поступит на импульсно-фазовый детектор 7, в программирующий блок 4 и в блок памяти 12.

В связи с тем, что требуется коэффициент деления 250,4, в первый цикл деления произведен с коэффициентом 250, то на выходе импульснофазового детектора 7 образуется скачок напряжения, пропорциональный дробному остатку, т. е. числу 4. Этот скачок напряжения накладывается на выходное напряжение импульсно-фазового детектора 7 и существует в течение всего второго цикла деления.

Поступление выходного импульса делителя 2 частоты с дробным коэффициентом деления на управляющие входы блока памяти 12, обеспечивает запись числа 4 в блок памяти 12.

Блок памяти 12 предназначен для хранения в течение последующего цикла деления числа, зафиксированного в пересчетных схемах программирующего блока за предыдущий цикл деления. Для каждого десятичного дробного разряда память состоит из 4-х ячеек по количеству триггеров в пересчетной декаде дробного остатка соответствующего разряда. Каждая ячейка папяти в конце каждого цикла деления с помощью вентилей, управляемых выходным импульсом делителя 2 частоты с дробным коэффициентом деления, подключается к информационным выходам соответствующей пересчетной схемы дробного остатка. В результате кажда двухстабильная ячейка памяти принимает положение своего триггера, соответственно О или 1, и хранит это состояние до следующего импуль :а с выхода делителя 2 частоты с дробным коэффициентом деления. Блок- 12памяти непосредственно управляет работой цифроаналового преобразователя 11. На выходе цифроаналогового преобра-зователя 11 образуется напряжение,которое в аналоговой форме Соответствует числу, хранимому в блоке памяти 12. Это напряжение вводится в сумматор 8 для компенсации скачков

напряжения, возникающих на выходе импульсно-фаэовсго детектора 7 из-за дробного деления в кольце фазовой автоподстройки частоты.

Таким образом, на выходе цифроаналогового преобразователя 11 в течение всего второго цикла деления будет напряжение, пропорциональное дробному остатку,т.е.числу 4.

Поступление выходного импульса делителя 2 частотыс дробным коэффициентом деления в программирующий РЛОК 4 обеспечит переключение триггера 15 и открывание вентиля 13. В результате в программирующий блок 4 поступит еще 2 импульса и в пересчетной схеме 16 будет записано число 8 и т. д.

Так как второй цикл деления произведен также с коэффициентом 250, то фазовое рассогласование между опорным импульсом 10 и импульсом с выхода делителя 2 частоты с дробным коэффициентом деления, обусловленное дробностью, увеличится, что приведет к образованию на выходе импульснофазового детектора 7 скачки напряжения, пропорционального числу 8 и т.д

В третьем цикле деления на вход программирующего блока 4 поступит еще 4 импульса. В результате образуется импульс переполнения пересчетной схемы 16, который воздействует на блок исключения импульсов 5, обеспечивая выполнение этого цикла деления с коэффициентом 251. При этом в пересчетной схеме 16 запишется дробный остаток, т. е. число 2. Так как в третьем цикле деления произой;дет коррекция фазы, то на выходе импульсно-фазового детектора 7 после третьего цикла деления скачок напряжения станет пропорционален также дробному остатку, т. е. числу 2 и т. д.

Предлагаемый цифровой синтезатор частот, обеспечивает получение на выходе цифроаналогового преобразователя ступенчатого напряжения, закон изменения которого строго обратен закону изменения ступенчатого напряжения помех, возникающей на выходе импульсно-фазового детектора изза дробного деления, что обеспечивает более полную компенсацию упомянутых скачков напряжения в кольце фазовой автоподстройки частоты и тем самым улучшает подавление в выходном сигнале помех, кратных шагу сетки частот.

Формула изобретения

Цифровой синтезатор частот, содержащий соединенные в кольцо синхро

0 низируемый генератор, делитель частоты с дробным коэффициентом деления, состоящий из последовательно соединенных программирующего блока, блока исключения импульсов и счетчика, бло5ка управления, выходы которого соединены соответственно с управляющим входом счетчика и управляющим входом программирующего блока, вход делителя частоты с дробным коэффициентом

0 деления соединен с сигнальным входом блока исключения импульсов и с сигнальным входом программирующего блока, другой управляющий вход которого связан с выходом делителя частоты с дробным коэффициентом де5ления, импульсно-фазовый детектор, сумматор и фильтр нижних частот, причем ко входу импульсно-фазового детектора подключен выход источника опорной частоты, а ко входу сум0матора подсоединен выход цифроана-логового преобразователя, отличающийся тем, что, с целью улучшения подавления в выходном сигнале помех, кратных шагу сетки

5 частот, между поразрядными информационными выходами пересчётных схем дробного остатка программирующего блока и соответствующими поразрядными входами цифроаналогового пре-

0 образователя дополнительно введен . блок памяти, управлякмций вход кото;рого соединен с выходом делителя частоты с дробным коэффициентом деления.

5

Источники информации, принятые во внимание при экспертизе

506130, кл. Н 03,К 23/00, 17.01.74.

0

470901, кл. Н 03 В 21/02, 12.01.73 (прототип).

Авторы

Даты

1981-01-23—Публикация

1976-05-17—Подача