Изобретение относится к преобразовательной технике и. может найти применение в системах управления вентильным преоб- в системах управления вентильными преобразователями и в вентильном электроприводе.

Цель изобретения - повышение точности и симметрии отпирающих импульсов.

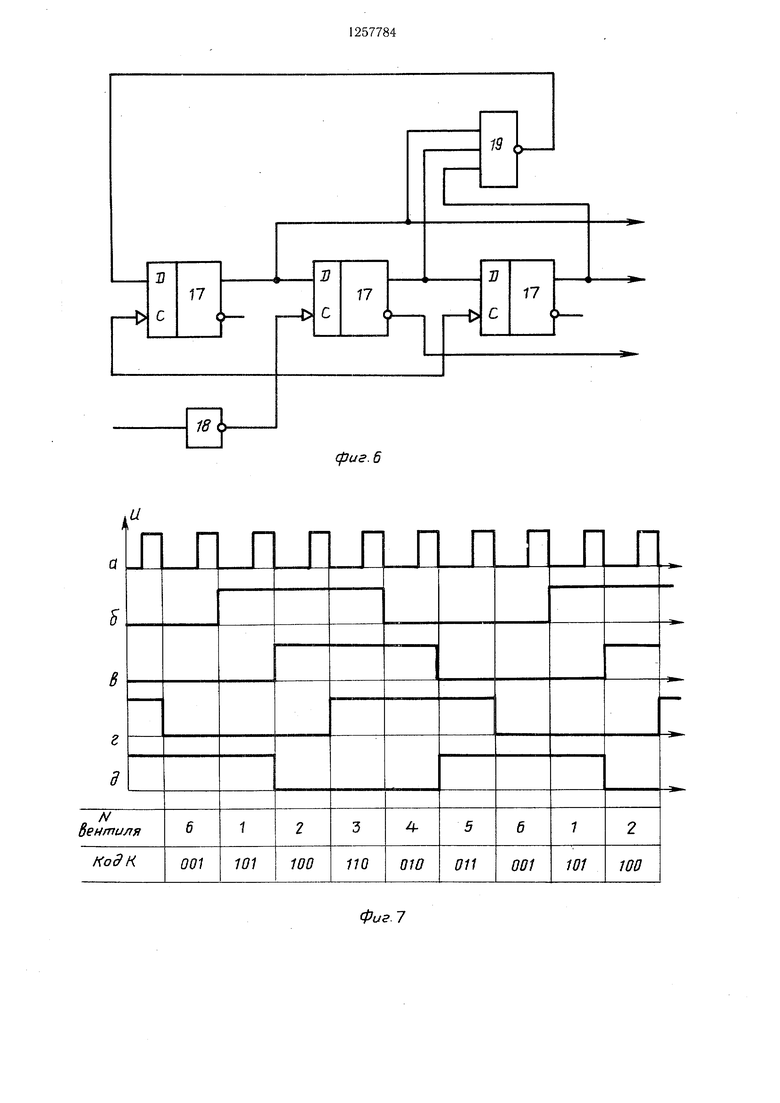

На фиг. 1 представлены диаграммы, поясняющие способ фазового управления, на фиг, 2 - то же; на фиг. 3 - схема устройства фазового управления; на фиг. 4- схема блока синхронизации; на фиг. 5 - диаграммы, поясняющие формирование циклического кода в блоке синхронизации; на фиг. 6 - схема второго счетчика; на

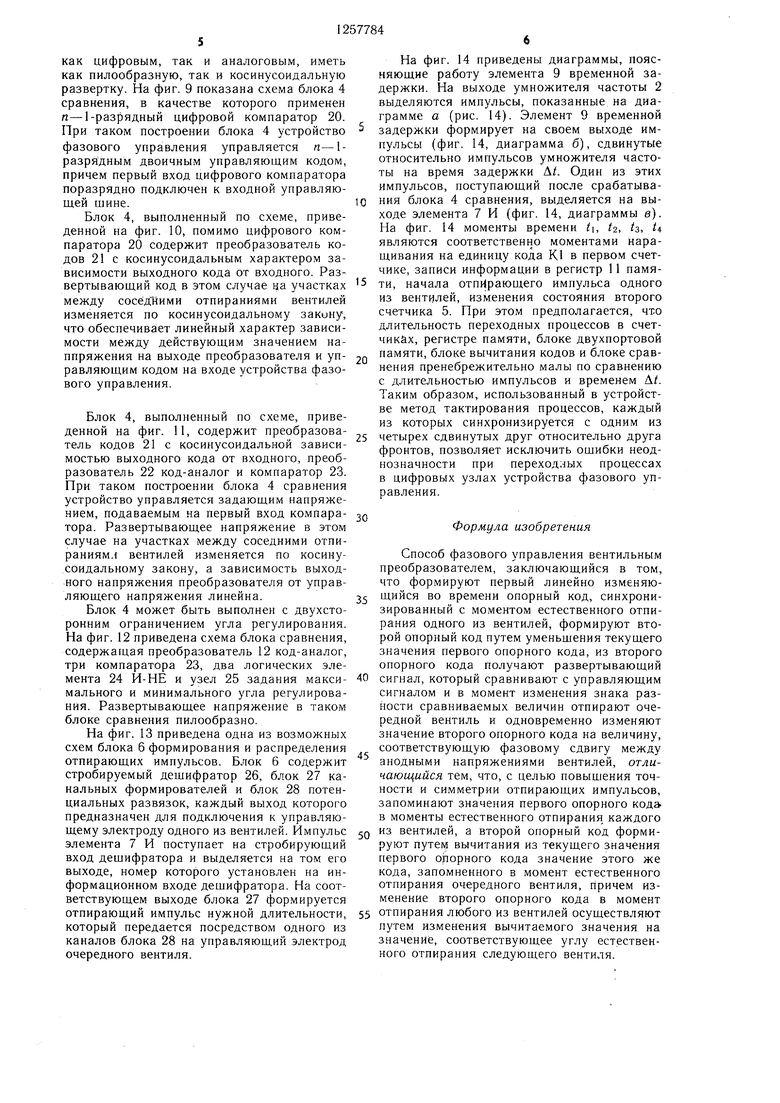

фиг. 7 - диаграммы, поясняющие-форми- рование циклического кода во втором счетчике; па фиг. 8 - диаграммы, поясняющие работу устройства фазового управления; на фиг. - схемы различных модификаций блока сравнения; на фиг. 13 - схема блока формирования и распределения отпирающих импульсов; на фиг. 14 - диаграммы поясняющие работу элемента временной задержки.

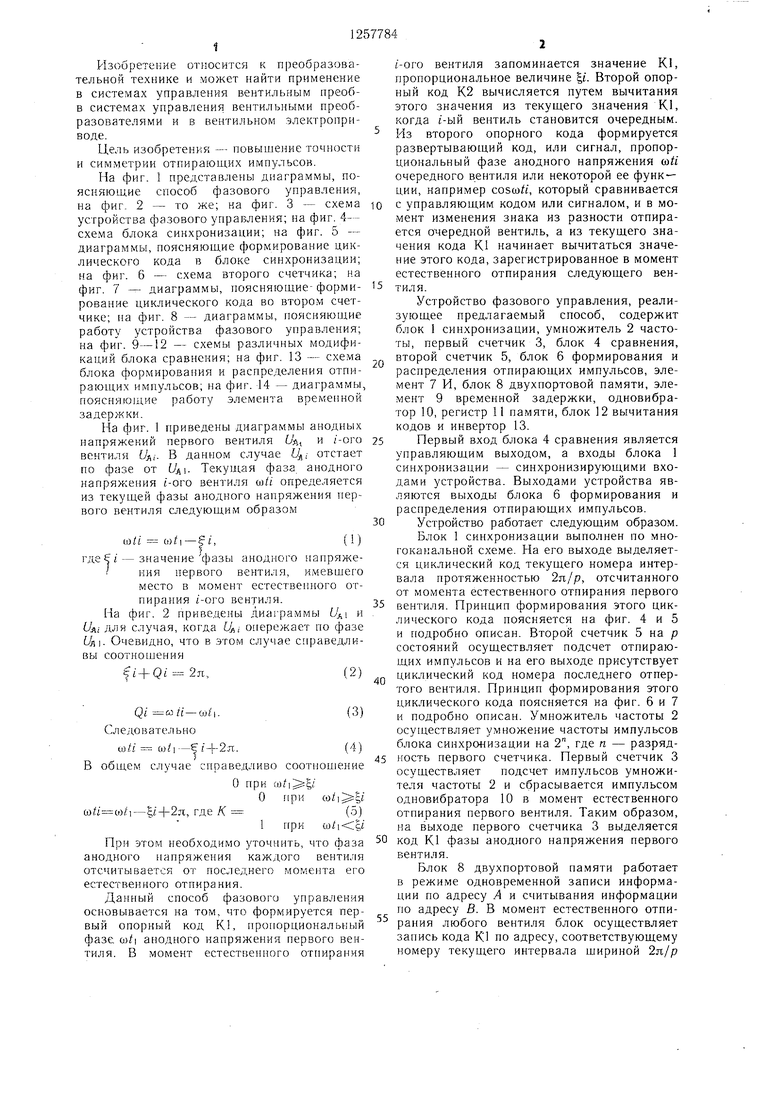

На фиг. 1 приведены диаграммы анодных напряжений первого вентиля Ut и /-ого вентиля . В данном случае -L, отстает по фазе от ( Текущая фаза анодного напряжения t -oro вентиля ш/( определяется из текущей фазы анОлЧного напряжения первого вентиля следующим образом

lo/f (D/i-f г,()

- значение фазы анодного напряже- ния первого вентиля, имевшего место в момент естественного отпирания i -oro вентиля. На фиг. 2 приведены диаграммы Uf, и UM для случая, когда 0, опережает по фазе Uf,. Очевидно, что в этом случае справедливы соотношения

(2)

f i + Q d 2 я,

(-со;:,.(3) Следовательно

ы// 0)1- 1 + 2 я,.(4)

В общем случае справе.гушвосоотношение

О при .i

0.при ,i )/i - г-|-2я, где К (5)

ti),i

При этом необходимо уточнить, что фаза анодного напря.жения каждого вентиля отсчитывается от последнего момента его естественного отпирания.

Данный способ фазового управления основывается на том, что формируется первый опорный код К1, про 10рциональный фазе а)/ анодного напряжения первого вентиля. В момент естественного отпирания

тиля,

г -ого вентиля запоминается значение К1, пропорциональное величине |t. Второй опорный код К2 вычисляется путем вычитания этого значения из текущего значения К1, когда t-ый вентиль становится очередным. Из второго опорного кода формируется развертывающий код, или сигнал, пропорциональный фазе анодного напряжения соЯ очередного вентиля или некоторой ее функции, например coscj i, который сравнивается с управляющим кодом или сигналом, и в момент изменения знака из разности отпирается очередной вентиль, а из текущего значения кода К1 начинает вычитаться значение этого кода, зарегистрированное в момент естественного отпирания следующего вен5 тиля,

5

0

Устройство фазового управления, реализующее предлагаемый способ, содержит блок 1 синхронизации, умножитель 2 частоты, первый счетчик 3, блок 4 сравнения, второй счетчик 5, блок 6 формирования и распределения отпирающих импульсов, элемент 7 И, блок 8 двухпортовой памяти, элемент 9 временной задержки, одновибра- тор 10, регистр 11 памяти, блок 12 вычитания кодов и инвертор 13.

Первый вход блока 4 сравнения является управляющим выходом, а входы блока 1 синхронизации - синхронизирующими входами устройства. Выходами устройства являются выходы блока 6 формирования и распределения отпирающих импульсов.

Устройство работает следующим образом.

Блок 1 синхронизации выполнен по мно- гока}1альной схеме. На его выходе выделяется циклический код текущего номера интервала протяженностью 2л//з, отсчитанного от момента естественного отпирания первого 5 вентиля. Принцип формирования этого циклического кода поясняется на фиг. 4 и 5 и подробно описан. Второй счетчик 5 на р состояний осуплествляет подсчет отпирающих импульсов и на его выходе присутствует циклический код номера последнего отпертого вентиля. Принцип формирования этого циклического кода поясняется на фиг. 6 и 7 и подробно описан. Умножитель частоты 2 осуществляет умножение частоты импульсов блока синхронизации на 2, где п - разряд- 5 кость первого счетчика. Первый счетчик 3 осуществляет подсчет импульсов умножителя частоты 2 и сбрасывается импульсом одновибратора 10 в момент естественного отпирания первого вентиля. Таким образом, на выходе первого счетчика 3 выделяется 0 код К1 фазы анодного напряжения первого вентиля.

Блок 8 двухпортовой памяти работает в режиме одновременной записи информации по адресу А и считывания информации по адресу В. В момент естественного отпирания любого вентиля блок осуществляет запись кода К1 по адресу, соответствующему номеру текущего интервала шириной 2п/р

0

55

в циклическом коде. Когда этот вентиль становится очередным, значение К1, записанное в момент его естественного йтпирания выделяется на выходе порта В блока 8 двухпортовой памяти.

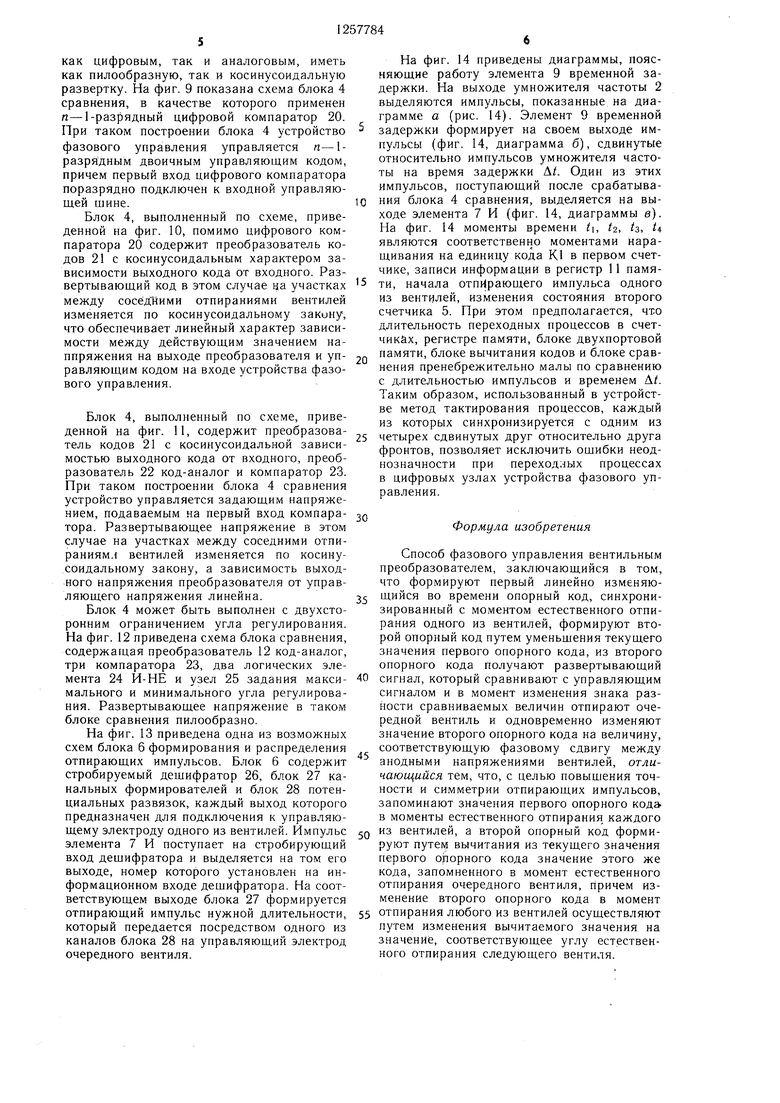

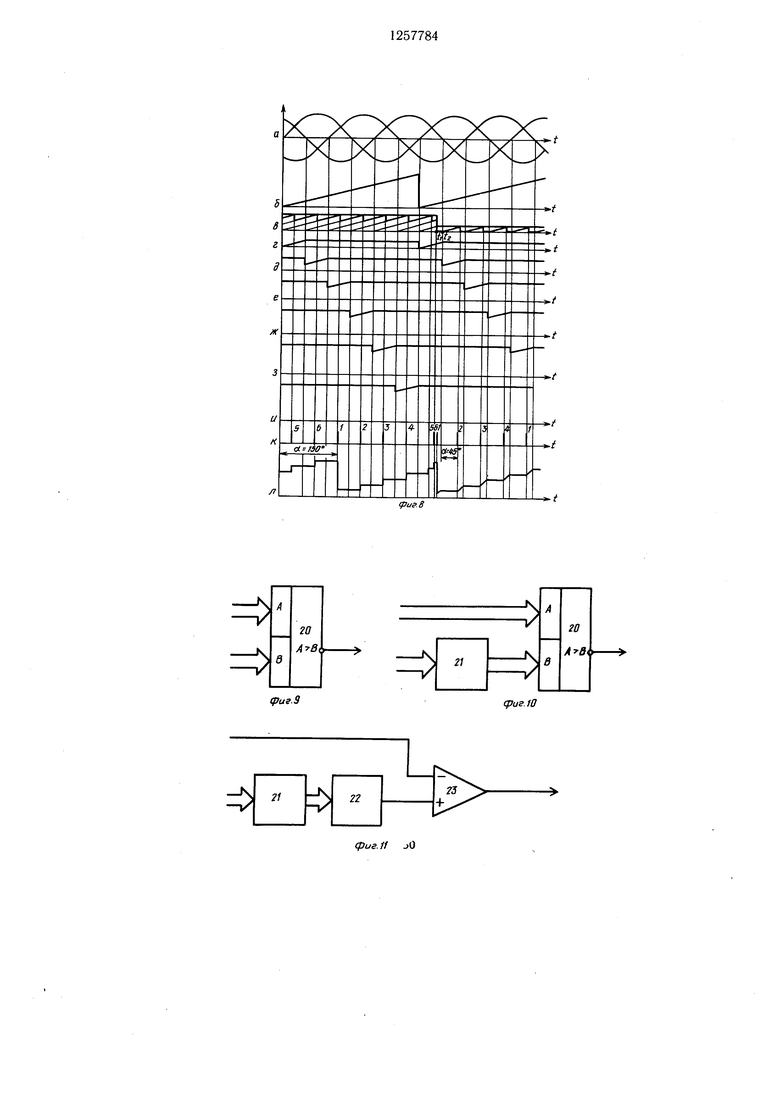

На фиг. 8 приведены временные диаграммы, поясняющие работу схемы в случае, когда . Диаграмма (фиг. 8) представляет собой осциллограмму трехфазного напряжения на выходе блока 1 синхронизации.

кода на выходе второго счетчика 5. Необходимо уточнить, что изменение кодов во времени показано на фиг. 8 непрерывным, в то время, как оно носит дискретный, ступенчатый характер, который не может быть отражен на диаграммах в данном масштабе. На фиг. 8 показано, что в момент времени t заданный угол регулирования скачкообразно уменьшается с 150 до 43 эл. град. Это приводит к немедленному отпиранию

Диаграмма на фиг. 86 представляет собой ,д шестого вентиля, а также к отпиранию пер- зависимость от времени кода KI в первом вого вентиля, происходящему через один счетчике 3. Диаграммы на фиг. 8г, д, е, ж, тактовый интервал длительностью 2л/2 3, и представляют собой зависимости от вре- после скачка задания. Если заданный угол мени содержимого ячеек блока 8 двухпор- регулирования меньще, чем 2л/р в момент товой памяти с адресами 101, 100, ПО, 010, отпирания очередного вентиля код К2 скач- 011 и 001 соответственно. Диаграмма на ts кообразно уменьшается до нулевого значе- фиг. 8л представляет собой зависимость от „ия и остается нулевым вплоть до наступле- времени кода на выходе порта В блока 8 ния момента естественного отпирания еле- двухпортовой памяти. Этот код вычитается дующего вентиля. При этом в блоке 8 двух- блоком 12 вычитания кодов из кода К1 и на портовой памяти имеет место режим прямого выходе блока 12 формируется второй опор- прохождения первого опорного кода К1 из ный код К2. В общем случае разность двух порта А в порт В. Это, например, происходит «-разрядных чисел имеет п+1 разряд, тде . в интервале между моментами времени t п4-1-ый разряд - знаковый. Изменение и 2 (фиг. 8), когда произощло отпирание на единицу содержимого этого разряда соот- первого вентиля, а момент естественного ветствует добавлению к коду К2 числа 2, отпирания второго вентиля еще не наступил, т. е. добавление к разности кодов фаз со/г 25 Режим прямого прохождения информации и g/ кода угла 2п, причем содержимое осталь- в блоке 8 возникает потому, что адреса ных п разрядов при этом не меняется. По- на двух его адресных входах совпадают, скольку знаковый разряд отбрасывается,На фиг. 4 приведена одна из возможных

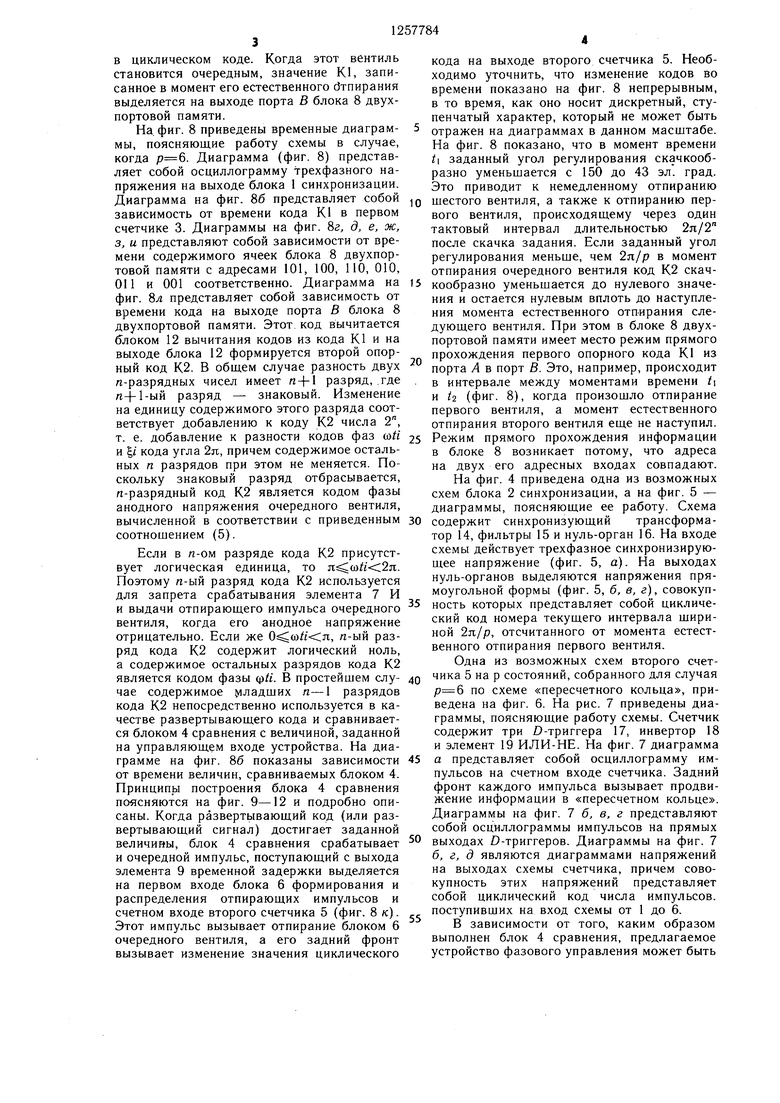

rt-разрядный код К2 является кодом фазы схем блока 2 синхронизации, а на фиг. 5 - анодного напряжения очередного вентиля, диаграммы, поясняющие ее работу. Схема вычисленной в соответствии с приведенным зо содержит синхронизующий трансформа- соотнощением (5).тор 14, фильтры 15 и нуль-орган 16. На входе

Если в п-ом разряде кода К2 присутст- схемы действует трехфазное синхронизирую- вует логическая единица, то . Щ напряжение (фиг. 5, а). На выходах Поэтому п-ьт разряд кода К2 используется нуль-органов выделяются напряжения пря- для запрета срабатывания элемента 7 И моугольной формы (фиг. 5, б, в, г), совокуп- и выдачи отпирающего импульса очередного которых представляет собой циклический код номера текущего интервала шириной 2л//7, отсчитанного от момента естественного отпирания первого вентиля.

Одна из возможных схем второго счетявляется кодом фазы ф/г. В простейшем слу- до 5 на р состояний, собранного для случая чае содержимое младших л-1 разрядов по схеме «пересчетного кольца, при- кода К2 непосредственно используется в ка- ведена на фиг. 6. На рис. 7 приведены диа- честве развертывающего кода и сравнивает- граммы, поясняющие работу схемы. Счетчик ся блоком 4 сравнения с величиной, заданной содержит три О-триггера 17, инвертор 18 на управляющем входе устройства. На диа- и элемент 19 ИЛИ-НЕ. На фиг. 7 диаграмма грамме на фиг. 86 показаны зависимости 45 а представляет собой осциллограмму им- от времени величин, сравниваемых блоком 4. пульсов на счетном входе счетчика. Задний Принципь построения блока 4 сравнения фронт каждого импульса вызывает продви- поясняются на фиг. 9-12 и подробно опи-жение информации в «пересчетном кольце,

саны. Когда развертьгвающий код (или раз- Диаграммы на фиг. 7 б, в, г представляют вертывающий сигнал) достигает заданной собой осциллограммы импульсов на прямых величины, блок 4 сравнения срабатывает выходах D-триггеров. Диаграммы на фиг. 7

6, г, д являются диаграммами напряжений на выходах схемы счетчика, причем совокупность этих напряжений представляет собой циклический код числа импульсов.

вентиля, когда его анодное напряжение отрицательно. Если же 0(, л-ый разряд кода К2 содержит логический ноль, а содержимое остальных разрядов кода К2

и очередной импульс, поступающий с выхода элемента 9 временной задержки выделяется на первом входе блока 6 формирования и распределения отпирающих импульсов и счетном входе второго счетчика 5 (фиг. 8 к). Этот импульс вызывает отпирание блоком 6 очередного вентиля, а его задний фронт вызывает изменение значения циклического

поступивших на вход схемы от 1 до 6.

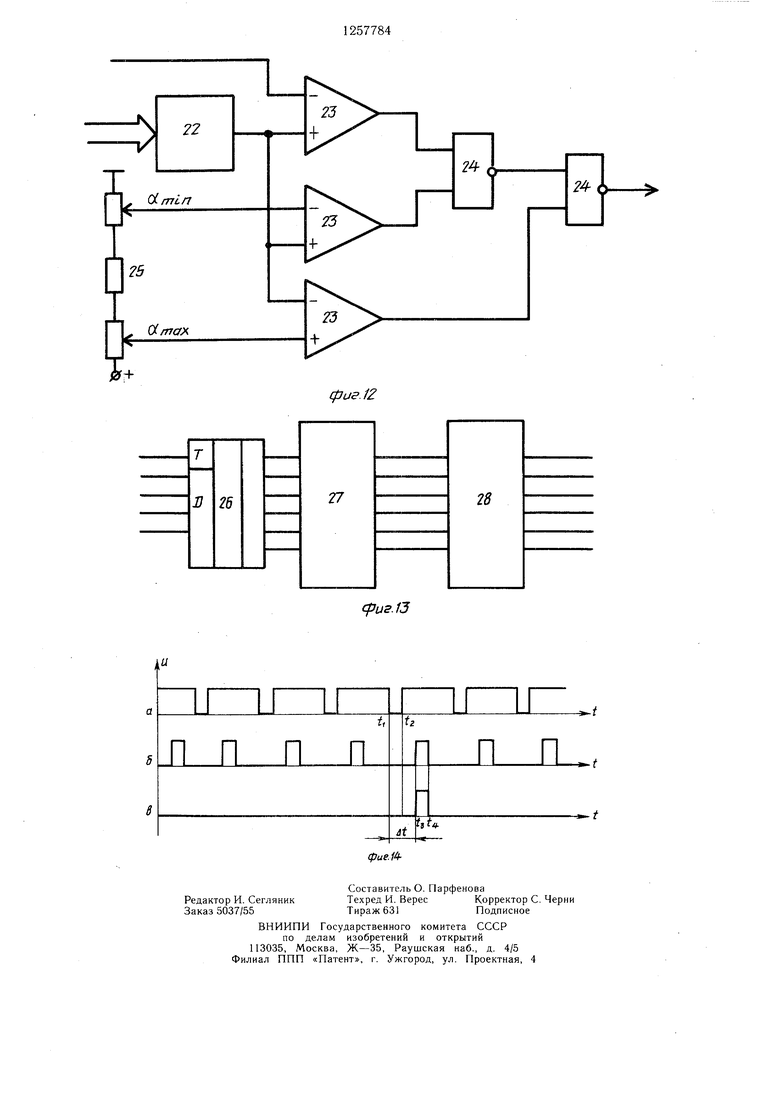

В зависимости от того, каким образом выполнен блок 4 сравнения, предлагаемое устройство фазового управления может быть

кода на выходе второго счетчика 5. Необходимо уточнить, что изменение кодов во времени показано на фиг. 8 непрерывным, в то время, как оно носит дискретный, ступенчатый характер, который не может быть отражен на диаграммах в данном масштабе. На фиг. 8 показано, что в момент времени t заданный угол регулирования скачкообразно уменьшается с 150 до 43 эл. град. Это приводит к немедленному отпиранию

шестого вентиля, а также к отпиранию пер- вого вентиля, происходящему через один тактовый интервал длительностью 2л/2 после скачка задания. Если заданный угол регулирования меньще, чем 2л/р в момент отпирания очередного вентиля код К2 скач- кообразно уменьшается до нулевого значе- „ия и остается нулевым вплоть до наступле- ния момента естественного отпирания еле- дующего вентиля. При этом в блоке 8 двух- портовой памяти имеет место режим прямого прохождения первого опорного кода К1 из порта А в порт В. Это, например, происходит в интервале между моментами времени t и 2 (фиг. 8), когда произощло отпирание первого вентиля, а момент естественного отпирания второго вентиля еще не наступил, Режим прямого прохождения информации в блоке 8 возникает потому, что адреса на двух его адресных входах совпадают, На фиг. 4 приведена одна из возможных

поступивших на вход схемы от 1 до 6.

В зависимости от того, каким образом выполнен блок 4 сравнения, предлагаемое устройство фазового управления может быть

как цифровым, так и аналоговым, иметь как пилообразную, так и косинусоидальную развертку. На фиг. 9 показана схема блока 4 сравнения, в качестве которого применен п-1-разрядный цифровой компаратор 20.

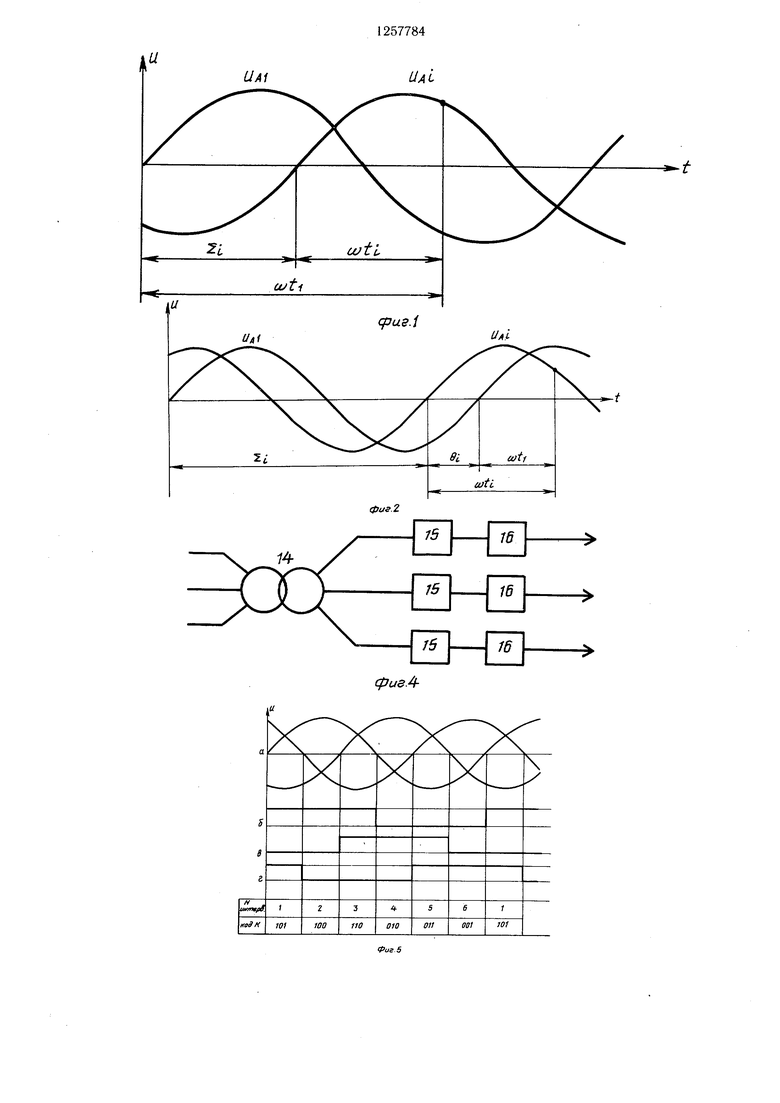

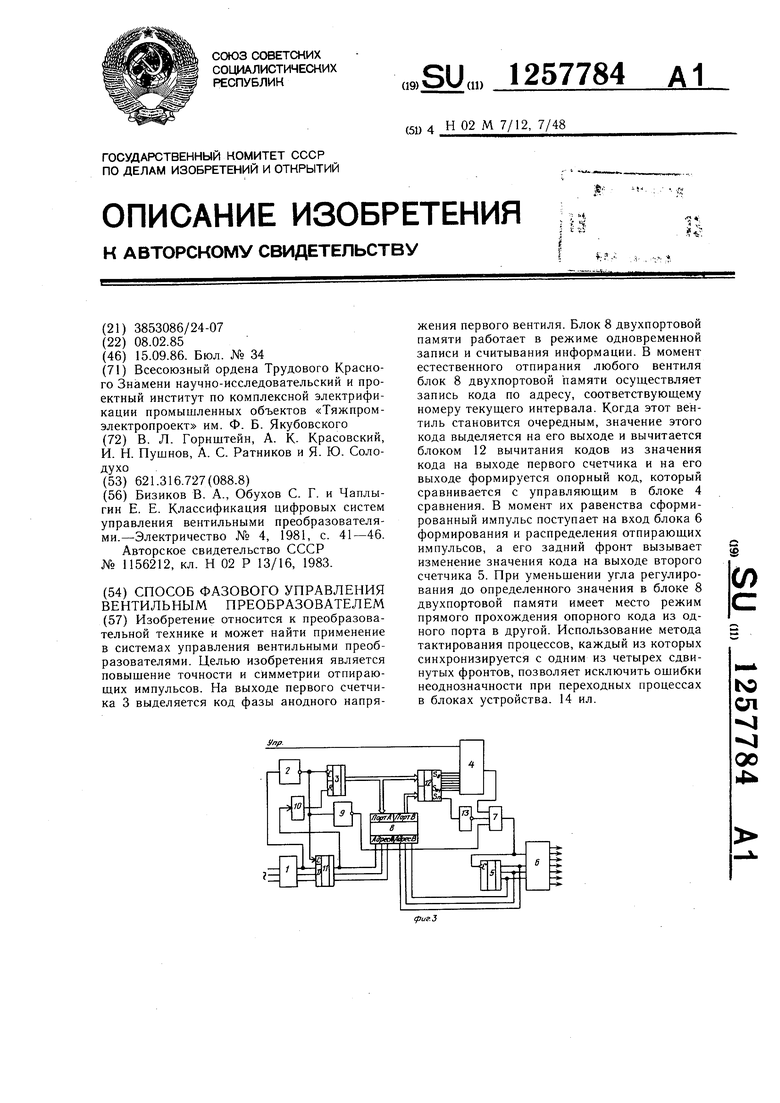

На фиг. 14 приведены диаграммы, поясняющие работу элемента 9 временной задержки. На выходе умножителя частоты 2 выделяются импульсы, показанные на диаграмме а (рис. 14). Элемент 9 временной

разрядным двоичным управляющим кодом, причем первый вход цифрового компаратора поразрядно подключен к входной управляющей шине.

Блок 4, выполненный по схеме, приведенной на фиг. 10, помимо цифрового компаратора 20 содержит преобразователь кодов 21 с косинусоидальным характером зависимости выходного кода от входного. РазПри таком построении блока 4 устройство задержки формирует на своем выходе им- фазового управления управляется пульсы (фиг. 14, диаграмма б), сдвинутые

относительно импульсов умножителя частоты на время задержки Д/. Один из этих импульсов, поступающий после срабатыва- 10 НИН блока 4 сравнения, выделяется на выходе элемента 7 И (фиг. 14, диаграммы в). На фиг. 14 моменты времени i tz, з, U являются соответственно моментами наращивания на единицу кода К1 в первом счетчике, записи информации в регистр 11 памявертывающий код в STOivTслучае на участках 5 ти, начала отпирающего импульса одного между соседними отпираниями вентилей из вентилей, изменения состояния второго изменяется по косинусоидальному закину, счетчика 5. При этом предполагается, что что обеспечивает линейный характер зависи- длительность переходных процессов в счет- мости между действующим значением на- чикйх, регистре памяти, блоке двухпортовой ппряжения на выходе преобразователя и уп- JQ памяти, блоке вычитания кодов и блоке срав- равляющим кодом на входе устройства фазо- нения пренебрежительно малы по сравнению

с длительностью импульсов и временем А/. Таким образом, использованный в устройстве метод тактирования процессов, каждый ,из которых синхронизируется с одним из

денной на фиг. 11, содержит преобразова- четырех сдвинутых друг относительно друга тель кодов 21 с косинусоидальнои зависи- фронтов, позволяет исключить ощибки неодвого управления.

Блок 4, выполненный по схеме, привемостью выходного кода от входного, преобразователь 22 код-аналог и компаратор 23. При таком построении блока 4 сравнения устройство управляется задающим напряжением, подаваемым на первый вход компара- 30 тора. Развертывающее напряжение в этом случае на участках между соседними отпи- раниямл вентилей изменяется по косину- .соидальному закону, а зависимость выходного напряжения преобразователя от управляющего напряжения линейна.

Блок 4 может быть выполнен с двухсторонним ограничением угла регулирования. На фиг. 12 приведена схема блока сравнения, содержащая преобразователь 12 код-аналог, три компаратора 23, два логических э.тенозначности при переходных процессах в цифровых узлах устройства фазового управления.

Формула изобретения

Способ фазового управления вентильным преобразователем, заключающийся в том, что формируют первый линейно изменяю- 32 щийся во времени опорный код, синхронизированный с моментом естественного отпирания одного из вентилей, формируют второй опорный код путем уменьщения текущего значения первого опорного кода, из второго опорного кода получают развертывающий

мента 24 И-НЕ и узел 25 задания макси- 40 сигнал, который сравнивают с управляющим мального и минимального угла регулирова- сигналом и в момент изменения знака раз- ния. Развертывающее напряжение в тако.м блоке сравнения пилообразно.

45

ности сравниваемых величин отпирают очередной вентиль и одновременно изменяют значение второго опорного кода на величину, соответствующую фазовому сдвигу между анодными напряжениями вентилей, отличающийся тем, что, с целью повышения точности и симметрии отпирающих импульсов, запоминают значения первого опорного кода- в моменты естественного отпирания, каждого

На фиг. 13 приведена одна из возможных схем блока 6 формирования и распределения отпирающих импульсов. Блок 6 содержит стробируемый дешифратор 26, блок 27 канальных формирователей и блок 28 потенциальных развязок, каждый выход которого предназначен для подключения к управляющему электроду одного из вентилей. Импульс jg вентилей, а второй опорный код форми- элемента 7 И поступает на стробирующий руют путем вычитания из текущего значения

первого опорного кода значение этого же кода, запомненного в момент естественного отпирания очередного вентиля, ггричем изменение второго опорного кода в момент

отпирающий импульс нужной длительности, 55 отпирания любого из вентилей осуществляют который передается посредством одного из путем изменения вычитаемого значения на

значение, соответствующее углу естественного отпирания следующего вентиля.

вход дешифратора и выделяется на том его выходе, номер которого установлен на информационном входе дещифратора. На соответствующем выходе блока 27 формируется

каналов блока 28 на управляющий электрод очередного вентиля.

На фиг. 14 приведены диаграммы, поясняющие работу элемента 9 временной задержки. На выходе умножителя частоты 2 выделяются импульсы, показанные на диаграмме а (рис. 14). Элемент 9 временной

задержки формирует на своем выходе им- пульсы (фиг. 14, диаграмма б), сдвинутые

нозначности при переходных процессах в цифровых узлах устройства фазового управления.

Формула изобретения

Способ фазового управления вентильным преобразователем, заключающийся в том, что формируют первый линейно изменяю- щийся во времени опорный код, синхронизированный с моментом естественного отпирания одного из вентилей, формируют второй опорный код путем уменьщения текущего значения первого опорного кода, из второго опорного кода получают развертывающий

сигнал, который сравнивают с управляющим сигналом и в момент изменения знака раз-

сигнал, который сравнивают с управляющим сигналом и в момент изменения знака раз-

ности сравниваемых величин отпирают очередной вентиль и одновременно изменяют значение второго опорного кода на величину, соответствующую фазовому сдвигу между анодными напряжениями вентилей, отличающийся тем, что, с целью повышения точности и симметрии отпирающих импульсов, запоминают значения первого опорного кода- в моменты естественного отпирания, каждого

вентилей, а второй опорный код форми- руют путем вычитания из текущего значения

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для импульсно-фазового управления @ -пульсным вентильным преобразователем | 1983 |

|

SU1156212A1 |

| Одноканальное цифровое устройство для импульсно-фазового управления вентильным преобразователем | 1982 |

|

SU1185546A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Одноканальное цифровое устройство для управления @ -фазным @ -пульсным вентильным преобразователем | 1990 |

|

SU1757057A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Устройство для импульсно-фазового управления вентильным преобразователем | 1982 |

|

SU1086544A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1991 |

|

RU2077415C1 |

| СПОСОБ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ ПРИ ПОМОЩИ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ | 1996 |

|

RU2107982C1 |

| Микропроцессорное устройство для управления вентильным преобразователем | 1985 |

|

SU1356155A1 |

Изобретение относится к преобразовательной технике и может найти применение в системах управления вентильными преобразователями. Целью изобретения является повышение точности и симметрии отпирающих импульсов. На выходе первого счетчика 3 выделяется код фазы анодного напряУпр. жения первого вентиля. Блок 8 двухпортовой памяти работает в режиме одновременной записи и считывания информации. В момент естественного отпирания любого вентиля блок 8 двухпортовой памяти осуществляет запись кода по адресу, соответствующему номеру текущего интервала. Когда этот вентиль становится очередным, значение этого кода выделяется на его выходе и вычитается блоком 12 вычитания кодов из значения кода на выходе первого счетчика и на его выходе формируется опорный код, который сравнивается с управляющим в блоке 4 сравнения. В момент их равенства сформированный импульс поступает на вход блока 6 формирования и распределения отпирающих импульсов, а его задний фронт вызывает изменение значения кода на выходе второго счетчика 5. При уменьщении угла регулирования до определенного значения в блоке 8 двухпортовой памяти имеет место режим прямого прохождения опорного кода из одного порта в другой. Использование метода тактирования процессов, каждый из которых синхронизируется с одним из четырех сдвинутых фронтов, позволяет исключить ощибки неоднозначности при переходных процессах в блоках устройства. 14 ил. с (Л to сд 00

сригЛ

wnntflS.

твК

т

WO по 010 ott oat 101

1

фиг. 6

Фиг.7

X

, ct

ISO

:

20

(риг 9

X

X

X

-«

сриг. 10

фиг. 11

(flue. 12

s

26

77

Составитель О. Парфенова

Техред И. ВересКорректор С. Черни

Тираж 631Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

28

сриг. 13

| Бизиков В | |||

| А., Обухов С | |||

| Г | |||

| и Чаплыгин Е | |||

| Е | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Механический грохот | 1922 |

|

SU41A1 |

| Устройство для импульсно-фазового управления @ -пульсным вентильным преобразователем | 1983 |

|

SU1156212A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-09-15—Публикация

1985-02-08—Подача