Изобретение относится к технике передачи цифровых данных через приводные линии связи с трансформаторной развязкой и может использоваться непосредственно для демодуляции сигналов, модулированных кодом с расщепленной фазой, а при выполнении дополнительной операции декодирования - и других разновидностей двухфазных самосинхронизирующихся кодов, имеющих переходы в центре каждого разрядного интервала (центральные переходы).

Целью изобретения является повышение помехоустойчивости.

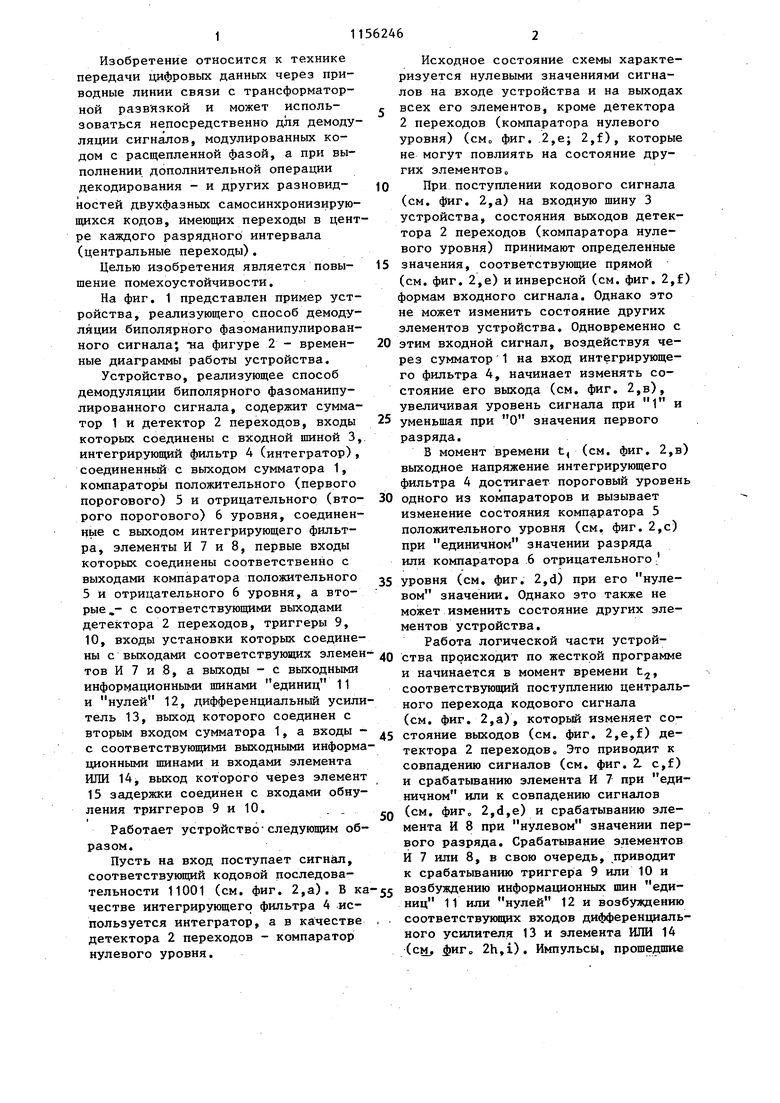

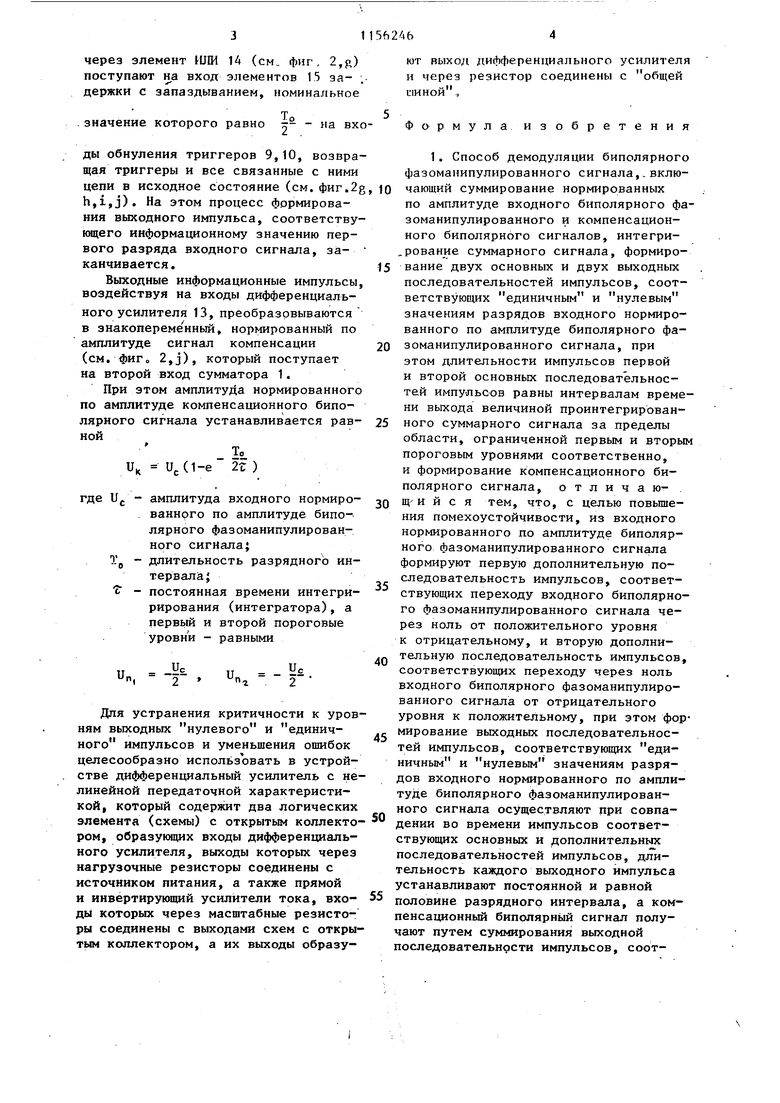

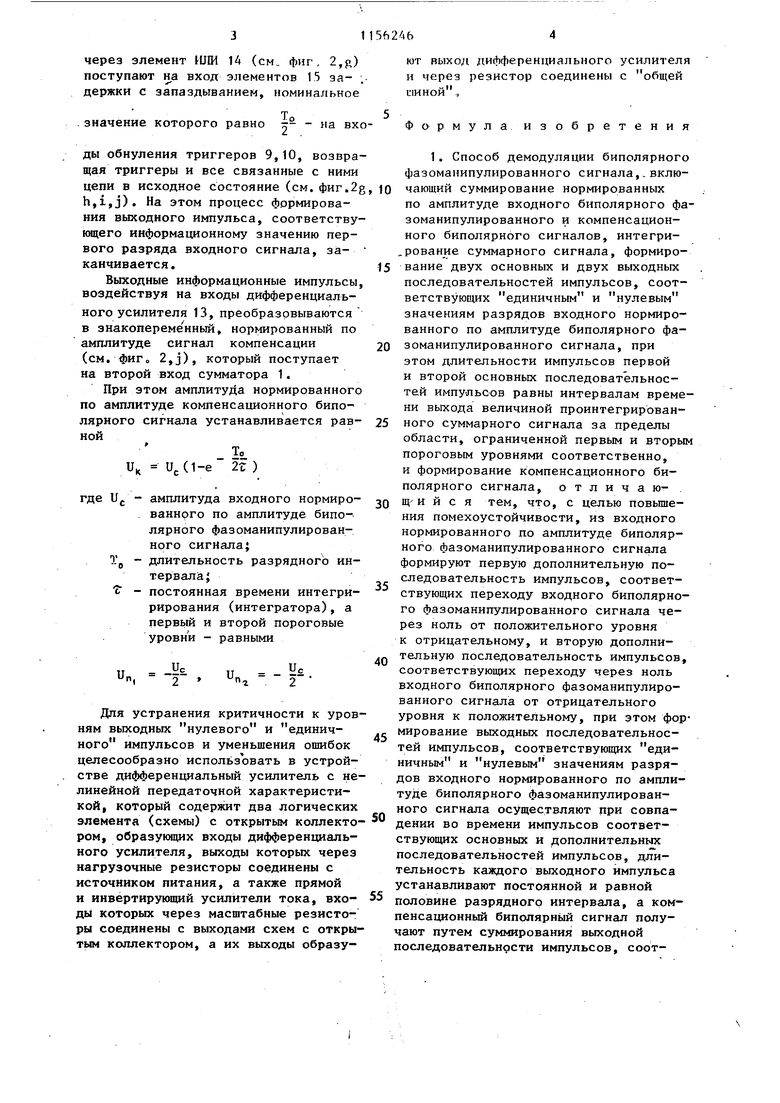

На фиг. 1 представлен пример устройства, реализующего способ демодуляции биполярного фазоманипулированного сигнала; на фигуре 2 - временные диаграммы работы устройства.

Устройство, реализующее способ демодуляции биполярного фазоманипулированного сигнала, содержит сумматор 1 и детектор 2 переходов, входы которых соединены с входной шиной 3, интегрирующий фильтр 4 (интегратор), соединенный с выходом сумматора 1, компараторы положительного (первого порогового) 5 и отрицательного (второго порогового) 6 уровня, соединенные с выходом интегрирующего фильтра, элементы И 7 и 8, первые входы которых соединены соответственно с выходами компаратора положительного 5 и отрицательного 6 уровня, а вторые .- с соответствующими выходами детектора 2 переходов, триггеры 9, 10, входы установки которых соединены с выходами соответствующих элементов И 7 и .8, а выходы - с выходными информационными шинами единиц 11 и нулей 12, дифференциальный усилитель 13, выход которого соединен с вторым входом сумматора 1, а входы с соответствующими выходными информационными шинами и входами элемента ИЛИ 14, выход которого через элемент 15 задержки соединен с входами обнуления триггеров 9 и 10.

Работает устройствоследующим образом.

Пусть на вход поступает сигнал, соответствующий кодовой цоследова- тельности 11001 (см. фиг. 2,а). В качестве интегрирующего фильтра 4 используется интегратор, а в качестве детектора 2 переходов - компаратор нулевого уровня.

Исходное состояние схемы характеризуется нулевыми значениями сигналов на входе устройства и на выходах

всех его элементов, кроме детектора 2 переходов (компаратора нулевого уровня) (см„ фиг. 2,е; 2,f), которые не могут повлиять на состояние других элементов„

При поступлении кодового сигнала (см. фиг. 2,а) на входную шину 3 устройства, состояния выходов детектора 2 переходов (компаратора нулевого уровня) принимают определенные

значения, соответствующие прямой

(см. фиг. 2,е) и инверсной (см. фиг. 2,f) формам входного сигнала. Однако это не может изменить состояние других элементов устройства. Одновременно с

этим входной сигнал, воздействуя через сумматор 1 на вход интегрирующего фильтра 4, начинает изменять состояние его выхода (см. фиг. 2,в), увеличивая уровень сигнала при 1 и

уменьшая при О значения первого разряда.

В момент времени t, (см. фиг. 2,в) выходное напряжение интегрирующего фильтра 4 достигает пороговый уровень

одного из компараторов и вызывает изменение состояния компаратора 5 положительного уровня (см. фиг. 2,с) при единичном значении разряда или компаратора .6 отрицательного;

уровня (см, фиг. 2,d) при его нулевом значении. Однако это также не может изменить состояние других элементов устройства.

Работа логической части устройства происходит по жесткой программе и начинается в момент времени t, соответствующий поступлению центрального перехода кодового сигнала (см. фиг. 2,а), который изменяет состояние выходов (см. фиг, 2,e,f) детектора 2 переходов. Это приводит к совпадению сигналов (см, фиг, 2. c,f) и срабатыванию элемента И 7 при единичном или к совпадению сигналов

(см, фиг 2,d,e) и срабатыванию элемента И 8 при нулевом значении первого разряда. Срабатывание элементов И 7 или 8, в свою очередь, приводит к срабатыванию триггера 9 или 10 и

возбуждению информационных шин единиц 11 или нулей 12 и возбуждению соответствуничих входов дифференциального усилителя 13 и элемента ИЛИ 14 (cMj фиг„ 2h,i), Импульсы, прошедшие

через элемент ШШ (см. фнг, 2,g) поступают на вход элементов 15 задержки с запаздыванием, номинальное .значение которого равно - - на вх ды обнуления триггеров 9,10, возвра щая триггеры и все связанные с ними цепи в исходное состояние (см. фиг.22 h,i,j). На этом процесс формирования выходного импульса, соответствующего информационному значению первого разряда входного сигнала, заканчивается. Выходные информационные импульсы воздействуя на входы дифференциального усилителя 13, преобразовываются в знакопеременный, нормированный по амплитуде сигнал компенсации (см, фиг о 2,j), который поступает на второй вход сумматора 1. При этом амплитуда нормированного по амплитуде компенсационного биполярного сигнала устанавливается равнойUK Uc(1 2t ) где Uj - амплитуда входного нормиро. ванного по амплитуде биполярного фазоманипулированного сигнала длительность разрядного интервала}постоянная времени интегририрования (интегратора), а первый и второй пороговые уровни - равными Для устранения критичности к уров ням выходных нулевого и единичного импульсов и уменьшения ошибок целесообразно использовать в устройстве дифференциальный усилитель с не линейной передаточной характеристикой, который содержит два логических элемента (схемы) с открытым коллекто ром, образующих входы дифференциального усилителя, выходы которых через нагрузочные резисторы соединены с источником питания, а также прямой и инвертирующий усилители тока, входы которых через масштабные резисторы соединены с выходами схем с откры тым коллектором, а их выходы образуют выход дифференциального усилителя и через резистор соединены с общей

шиной, Формула изобретения 1. Способ демодуляции биполярного фазоманипулированного сигнала,, включающий суммирование нормированных по амплитуде входного биполярного фазоманипулированного и компенсационного биполярного сигналов, интегрирование суммарного сигнала, формирование двух основных и двух выходных последовательностей импульсов, соответствующих единичным и нулевым значениям разрядов входного нормированного по амплитуде биполярного фазоманипулированного сигнала, при этом длительности импульсов первой и второй основных последовательностей импульсов равны интервалам времени выхода величиной проинтегрированного суммарного сигнала за пределы области, ограниченной первым и вторым пороговым уровнями соответственно, и формирование компенсационного биполярного сигнала, отличаю- , щ и и с я тем, что, с целью повышения помехоустойчивости, из входного нормированного по амплитуде биполярного фазоманипулированного сигнала формируют первую дополнительную последовательность импульсов, соответствующих переходу входного биполярного фазоманипулированного сигнала через ноль от положительного уровня к отрицательному, и вторую дополнительную последовательность импульсов, соответствующих переходу через ноль входного биполярного фазоманипулированного сигнала от отрицательного уровня к положительному, при этом формирование выходных последовательностей импульсов, соответствующих единичным и нулевым значениям разрядов входного нормированного по амплитуде биполярного фазоманипулированного сигнала осуществляют при совпадении во времени импульсов соответствующих основных и дополнительных последовательностей импульсов, длительность каждого выходного импульса устанавливают постоянной и равной половине разрядного интервала, а коменсационный биполярный сигнал полуают путем суммирования выходной оследовательности импульсов, соответствующих единичным, и взятой с обратным знаком выходной последовательности импульсов, соответствующих нулевым значениям разрядов входного нормированного по амплитуде биполярного фазоманипулированного сигнала.

2. Способ по п. 1, о т л и ч а ющ и и с я тем, что амплитуду нормированного по амплитуде компенсационного биполярного сигнала устанавливают равной:

и, U,(),

е U(. - амплитуда входного нормированного по амплитуде биполярного фазоманипулированного сигнала;

TIJ - длительность разрядного интервала J

- постоянная времени интегрирования,

первый и второй пороговые уровни вными:

Uc

U 2

и

Un,

2

пг

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ демодуляции биполярного фазоманипулированного сигнала | 1985 |

|

SU1330761A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1510087A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1559407A2 |

| Способ преобразования электрических импульсов в код Манчестер и устройство для его осуществления | 2016 |

|

RU2644530C2 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛА В МАНЧЕСТЕРСКОМ КОДЕ | 2006 |

|

RU2394368C2 |

| МНОГОЗОННЫЙ ЧАСТОТНО-ШИРОТНО-ИМПУЛЬСНЫЙ РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2461875C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ПИКОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2708687C1 |

Изобретение относится к технике передачи цифровых данных через проводные линии связи с транформаторной развязкой и может использоваться непосредственно для демодуляции сигналов, модулированных кодом с расщепленной фазой. изобретения является повышение помехоустойчивости. Устройство, реализующее способ демодуляции биполярного фазоманипулированного сигнала, содержит сумматор 1 и детектор 2 переходов, входы которых соединены с входной шиной 3, интегрирующий фильтр 4, соединенный с выходом сумматора 1, компараторы положительного 5 и отрицательного 6 уровня, соединенные с выходом интегрирующего фильтра 4, элементы И 7 и 8, первые входы которых соединены соответственно с выходами компараторов положительного 5 и отрицательного 6 уровня, а вторые - с соответствующими выходами детектора 2 переходов, триггеры 9,10, входы установки которых соединены с выходами соответствующих элементов И 7 и 8, а выходы - с выходными информационными шинами единиц 11 и нулей 12, I дифференциальный усилитель 13, выход которого соединен с вторым входом (Л сумматора 1, а входы - с соответствующими выходными информационными шинами и входами элемента ИЛИ 14, выход которого через элемент 15 задержки соединен со входами обнуления триггеров 9 и 10. 1 з.п. ф-лы, 2 ил. ел 4 05

Ц}и2.1

| Патент США № 3820031, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Демодулятор импульсного сигнала,модулированного методом расщепленной фазы | 1980 |

|

SU951690A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-05-15—Публикация

1982-10-15—Подача