Область техники, к которой относится изобретение

Изобретение относится к электронным информационным техническим решениям общего назначения, в которых требуется управление и регулирование для согласования каналов обработки и передачи информации, в которых код Манчестер предпочтителен, так как приемнику не требуется иметь сведения о скорости передачи информации в таком коде.

Уровень техники

Известны устройства [4, 5, 6] предназначенные для преобразования нормированных импульсов и кода Манчестер ячейки MIL-STD 1553 производства фирмы AIT USA, US Patent №5,325,359, 5,367,641 и др., а также устройства и способы [6, 7, 8] для управления сигналами и удержания их в заданных состояниях US 5564090А (18 dec, 1997), US 2015/0286607 A1 (Oct 8, 2015) с приоритетом от 1997 и 2015 г. Кроме того, известны микропроцессорные устройства, например макетно-отладочная плата ЕВ-552 [1] производства фирмы КТЦ-МК.

Известное устройство MIL-STD 1553 выпускается серийно в разных исполнениях: для шины PXI станции обработки сигналов National Instruments PXI на базе визуального программирования в среде LabView, которое является очень громоздким, что приводит к необходимости строить программу из нескольких блоков на самом начальном этапе, а основная задача оказывается не решена (аппаратная и программная сложность и стоимость при таком подходе существенно возрастают); для шины PCI в исполнении AIT1553 для 32-битной платформы; а также в исполнении с интерфейсом USB. Некоторые известные устройства, удобные для простого исполнения и программной реализации на языке Ассемблер, такие как плата ЕВ-552, не предназначены для работы с сигналами и кодами в формате Манчестер. Плата ЕВ-552 не имеет организованного USB порта, однако имеет удобную для работы шину I2C (US 2015/0286607 A1 и др.) с разъемом для периферийного расширения. Таким образом, способ, применяемый в прототипе [1], позволяет обрабатывать только стандартные (нормированные) импульсы и не позволяет преобразовать их в код Манчестер.

Код Манчестер [5] п. 4.3.3 ГОСТ Р 52070-2003 (Интерфейс магистральный последовательный системы электронных модулей. Общие требования) использует биполярный фазоманипулированный код (Манчестер II). Единица передается как биполярный кодированный сигнал 1/0 (за положительным импульсом следует отрицательный импульс). Нуль передается как биполярный кодированный сигнал 0/1 (за отрицательным импульсом следует положительный импульс). Переход через нулевой уровень осуществляется в середине интервала времени, в течение которого передается информационный разряд.

Раскрытие изобретения

Предлагаемый способ состоит в том, что последовательность импульсов с входа устройства подвергается инверсии знака для каждого четного импульса, посредством сохранения в памяти состояния входа на предыдущем шаге с помощью вспомогательного триггера, если на предыдущем шаге уровень сигнала был зафиксирован, то текущий шаг вычислений рассматривается в качестве четного. Последовательность импульсов на входе подвергается инверсии, чтобы обеспечить срабатывание триггера детектора сигнала на предыдущем шаге в противофазе по отношению к основному триггеру, на который и поступает полученная промежуточная последовательность импульсов с инверсией знака для каждого четного импульса, которая перед этим подвергается дополнительной коррекции (см. фиг. 1; 17; 18; 19 и фиг 3.; 16, 17, 18).

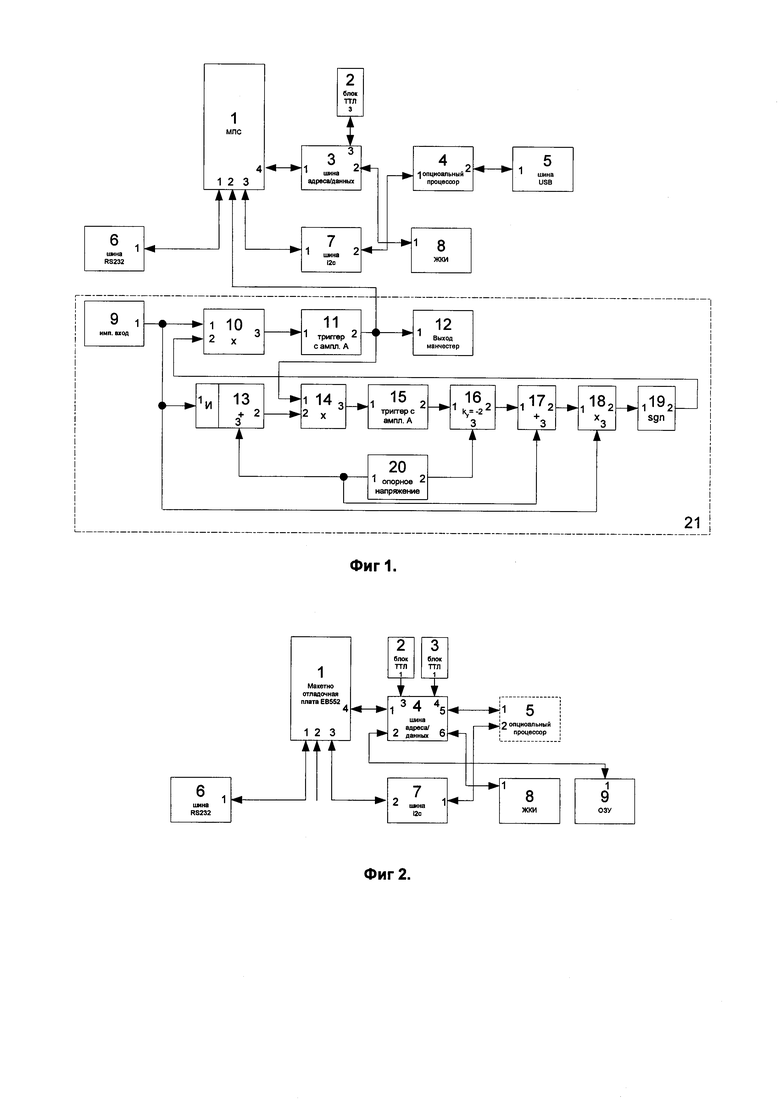

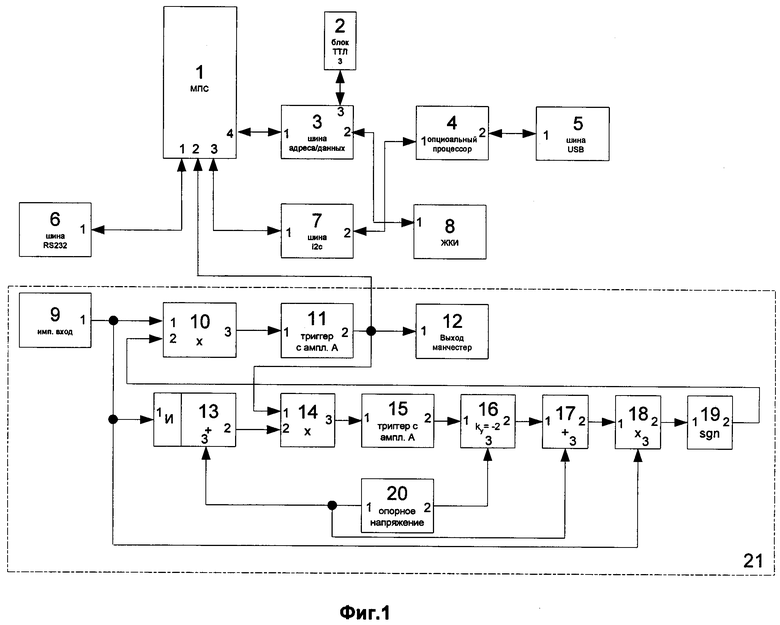

Устройство [фиг. 1] для осуществления способа (п. 9) состоит из двух триггеров с амплитудой А, в котором первый триггер поддерживает главный выход при нулевом входом воздействии, а второй триггер имеет инвертор на входе с коррекцией через произведение с выхода первого триггера, и с коррекцией на выходе, для выравнивания веса обратной связи, в которой установлен второй триггер, и последовательной инверсией полярности для каждого четного импульса, поступающего с входа устройства, на вход первого триггера, выход которого является выходом устройства, которое оснащается микропроцессорной системой, в которой связывание микросхем осуществляется с применением интерфейса I2C, и установкой на нем дополнительного процессора для поддержки интерфейса USB. Коррекция выходных цепей второго триггера требует установки усилителя, единственного требующего точной подстройки, поэтому сами триггеры, также как схемы, реализующие непосредственно предлагаемый способ, не нужно отдельно снимать для настройки на вспомогательном агрегате и выполнять в виде отдельной платы.

Описание способа:

последовательность импульсов со входа устройства подвергается инверсии знака для каждого четного импульса, посредством сохранения в памяти состояния входа на предыдущем шаге с помощью вспомогательного триггера,

если на предыдущем шаге уровень сигнала был зафиксирован, то текущий шаг вычислений рассматривается в качестве четного,

затем последовательность импульсов на входе подвергается инверсии, чтобы обеспечить срабатывание вспомогательного триггера детектора сигнала на предыдущем шаге в противофазе по отношению к основному триггеру,

состояние уровня, определяемого полученной последовательностью импульсов с инверсией знака для каждого четного импульса, которая перед этим подвергается дополнительной коррекции, фиксируется на выходе основного триггера,

полученная в ходе фиксации в основном триггере, а в целом полученная в результате общего преобразования последовательность импульсов представляет из себя результирующий сигнал, в котором смена уровня происходит при поступлении бита исходной последовательности импульсов,

т.е. при поступлении бита входящей последовательности, на выходе происходит смена уровня сигнала с инверсией знака выхода, что соответствует передачи сигнала в формате кода Манчестер, не требующем нормировки по скорости передачи данных, таким образом, внешнему приемнику, для которого подготавливается выходной информационный пакет, задавать скорость передачи данных не требуется.

Описание устройства

Устройство для осуществления способа преобразования электрических импульсов в код Манчестер [фиг. 1]:

содержит микропроцессорную системы (1), блок транзистор-транзисторной логики (2) для управления шиной адреса/данных (3), дополнительного опционального процессора (4) с портом USB (5); разъема RS232 (6); второго опционального процессора, подключаемого по шине I2C (7) и жидкокристаллического индикатора (8); разъема для входа импульсного сигнала (9); трех блоков произведения (10; 14; 18); двух триггеров со срабатыванием по произвольной амплитуде входа (11; 15); разъема выхода в формате Манчестер (12); двух сумматоров (13; 17); усилителя с точной настройкой напряжения подпора (17); блока определения знака (ограничителя уровня сигнала) sgn (19) и генератора опорного напряжения (20), переключательную схему получения последовательности импульсов в коде Манчестер (21);

микропроцессорная система (1) имеет дуплексный последовательный порт RS232 (1.1), выделенный стандартный порт процессора (1.2) или вход PWM (1.2) для сигнала с широтно-импульсной модуляцией (ШИМ), а также дуплексный последовательный порт I2C (1.3);

разъем RS232 (6) с микропроцессорной системой (1) связывает дуплексная связь через порт (1.1) блока (1) и порт (6.1) блока (6); разъем шины I2C (6) с микропроцессорной системой (1) связывает дуплексная связь через порт (1.3) блока (1) и порт (7.1) блока (7); сигнал с выхода в формате Манчестер - порт (12.1) разъема (12) поступает через связь на выделенный стандартный порт или вход ШИМ, т.е. на дуплексный порт (2.1); шина адреса/данных работает под управлением дуплексного порта (3.3) блока транзистор-транзисторной логики (2);

шина адреса/данных первых дуплексным портом (3.1) связана с ответным портом (1.4) микропроцессорной системы, а второй дуплексный порт шины адреса/данных (3.2) связан с ответным дуплексным (8.1) жидкокристаллического индикатора (8);

порт (9.1) разъема импульсного входа (9) связан с входом (10.1) блока произведения (10); кроме того, порт (9.1) связан с первым инверсным входом (13.1) сумматора (13);

выход сумматора (13.2) соединен с входом (14.2) блока произведения (14); выход (10.3) блока произведения (10) связан с входом (11.1) триггера (11);

выход (11.2) триггера (11) связан с портом (12.1) разъема выхода сигнала в формате Манчестер;

не инвертированный вход (13.3) сумматора (13) связан с выходом (20.1) источника опорного напряжения (20);

выход (11.2) триггера (11) связан с входом (14.1) блока произведения (14);

выход (14.3) блока произведения (14) связан с входом (15.1) триггера (15);

выход (15.2) триггера (15) связан с входом (базой) (16.1) усилителя-инвертора (16) с входом для подпор (16.3), связанного с выходом (20.2) источника опорного напряжения (20);

выход (16.2) усилителя-инвертора (16) связан с входом (17.1) сумматора (17);

выход (17.2) сумматора (17) связан с входом (18.1) блока произведения (18);

вход (17.3) связан с выходом (20.1) источника опорного напряжения (20);

вход (18.3) блока произведения (18) связан с портом (9.1) импульсного входа (9);

выход (18.2) связан с входом (19.1) блока ограничения уровня и определения знака сигнала (19);

выход (19.2) блока определения знака сигнала (19) связан с входом (10.2) блока произведения (10).

Чтобы подготовить входной сигнал для устройства, следует получить промежуточное преобразование, выполнив выдачу импульсов на повышенной частоте, чем частота канала, из которого получена информация, например шина I2C, тогда повышенная частота передачи импульсов по входу устройства будет меньше 512 кбод (максимальной скорости передачи по шине I2C), но может быть больше и существенно, чем скорость передачи данных по интерфейсу RS232 на скорости не более 19200 бод.

Описание устройства прототипа

Макетно-отладочная плата ЕВ552 (прототип) [фиг. 2] состоит из: микропроцессорной системы (1), двух блоков транзистор-транзисторной логики (2) и (3) для управления шиной адреса/данных (4), дополнительного опционального процессора (5) альтернативного центральному процессору микропроцессорной системы; разъема RS232 (6); второго опционального процессора, подключаемого по шине I2C (7) и жидкокристаллического индикатора (8); ОЗУ - оперативного запоминающего устройства (9);

порт (6.1) разъем шины RS232 (6) связан с аналогичным портом RS232 (1.1) микропроцессорной системы (1);

стандартный порт (1.2) микропроцессорной системы (1) выведен на макетное пространство платы;

дуплексный порт (1.3) шины i2c макетно-отладочной платы ЕВ552 выведен на порт (7.2) разъема шины I2C (7);

дуплексный порт (2.2) шины i2c второго опционального процессора макетно-отладочной платы ЕВ552 выведен на порт (7.1) разъема шины I2C (7);

порт (1.4) макетно-отладочной платы ЕВ552 (1) связан с портом (4.1) шины адреса/данных (4)

выход (2.1) блока транзистор-транзисторной логики (2) связан с портом (4.3) шины адреса/данных (4);

выход (3.1) блока транзистор-транзисторной логики (2) связан с портом (4.4) шины адреса/данных (4);

порт (4.2) шины ардеса/данных прототипа связан с портом управления (8.1) оперативного запоминающего устройства (8);

порт (4.6) шины ардеса/данных прототипа связан с портом управления (9.1) жидкокристаллического индикатора (8);

порт (4.5) шины адреса/данных (4) использован для подключения опционального процессора (5) и является главным по сравнению с портом (5.2);

порт (4.5) шины адреса/данных (4) связан с портом (5.1) шиной/адреса данных второго опционального процессора (5).

Формула изобретения в части способа

Способ преобразования последовательности электрических импульсов в код Манчестер, состоящий в том, что исходная последовательность импульсов, нормированная по скорости, обрабатывается с помощью прошиваемого в процессор алгоритма программы, представляемой на языке ассемблер для компилятора А51, при этом передача информационных импульсов проводится с определением уровня амплитуды импульса с помощью компаратора в течение заранее настраиваемой и задаваемой длительности импульса, при таком нормировании периода и длительности импульса, выдача информационного бита ограничивается минимальными длительностью и периодом, а алгоритм обработки для окончательного преобразования последовательности импульсов в заданный код осуществляется предлагаемым способом, отличающийся тем, что последовательность импульсов подвергается инверсии знака для каждого четного импульса, посредством сохранения в памяти состояния входа на предыдущем шаге с помощью вспомогательного триггера, если на предыдущем шаге уровень сигнала был зафиксирован, то текущий шаг вычислений является четным, после чего последовательность импульсов на входе подвергается инверсии, чтобы обеспечить срабатывание вспомогательного триггера детектора сигнала на предыдущем шаге в противофазе по отношению к основному триггеру, состояние уровня, определяемого полученной последовательностью импульсов с инверсией знака для каждого четного импульса, которая перед этим подвергается дополнительной коррекции, фиксируется на выходе основного триггера, полученная в ходе фиксации в основном триггере, а в целом полученная в результате общего преобразования последовательность импульсов представляет из себя результирующую последовательность импульсов, в которой смена уровня происходит при поступлении бита исходной последовательности импульсов, в результате чего при поступлении бита исходной последовательности импульсов, на выходе происходит смена уровня сигнала с инверсией знака выхода, что соответствует передачи сигнала в формате кода Манчестер, а интервал и период импульсов не ограничены минимальными величинами.

Формула изобретения в части устройства

Устройство для осуществления способа преобразования последовательности электрических импульсов в код Манчестер, содержащее микропроцессорную систему, включающую в себя базовую систему ввода вывода с блоком транзистор-транзисторной логики для управления шиной адреса/данных, дополнительного опционального процессора, альтернативного центральному процессору микропроцессорной системы, интерфейса RS232 с разъемом, шины I2C с разъемом, второго опционального процессора, подключаемого по шине I2C, и жидкокристаллического индикатора, отличающееся тем, что в состав устройства введены преобразователь информационного импульсного сигнала в выход в формате Манчестер; опциональный процессор, подключаемый по шине I2C для обеспечения USB порта, переключательная схема устройства содержит главный импульсный вход, два триггера со срабатыванием по произвольной амплитуде, блоки произведения, предназначенные для управления входом триггеров; блоки коррекции выхода второго триггера, и усилитель с точной настройкой для коррекции выхода второго триггера, сумматор смещения сигнала и блок произведения с выдачей опорного константного сигнала единичного уровня с блока опорного напряжения, причем после коррекции выхода второго триггера уровень сигнала, амплитуда которого не менее единицы по модулю, ограничивается блоком определения знака сигнала sgn, соединенные между собой таким образом, что выходной сигнал после коррекции и ограничения со второго триггера имеет амплитуду минус один вольт для каждого четного импульса, и плюс один вольт для каждого нечетного, таким образом при поступлении информационного бита на главный вход, обеспечивая переключение первого триггера со сменой уровня, при этом второй триггер работает в противофазе по отношению к первому триггеру и получает входной сигнал с главного входа через инвертор, в отличие от первого триггера, определяя состояние на предыдущем такте при нулевом уровне на главном входе, что позволяет избежать применения звеньев запаздывания как для Манчестер преобразования или появления запаздывания в процессе программной обработки сигнала с помощью микропроцессорной системы устройства.

Описание чертежей

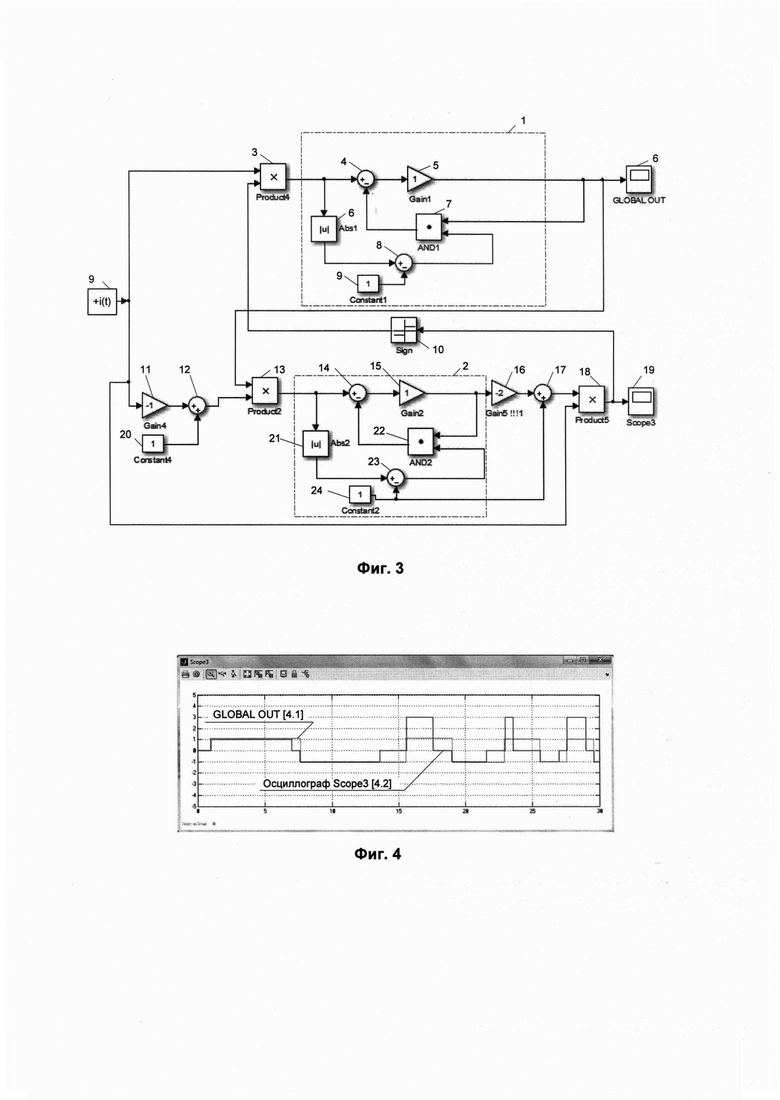

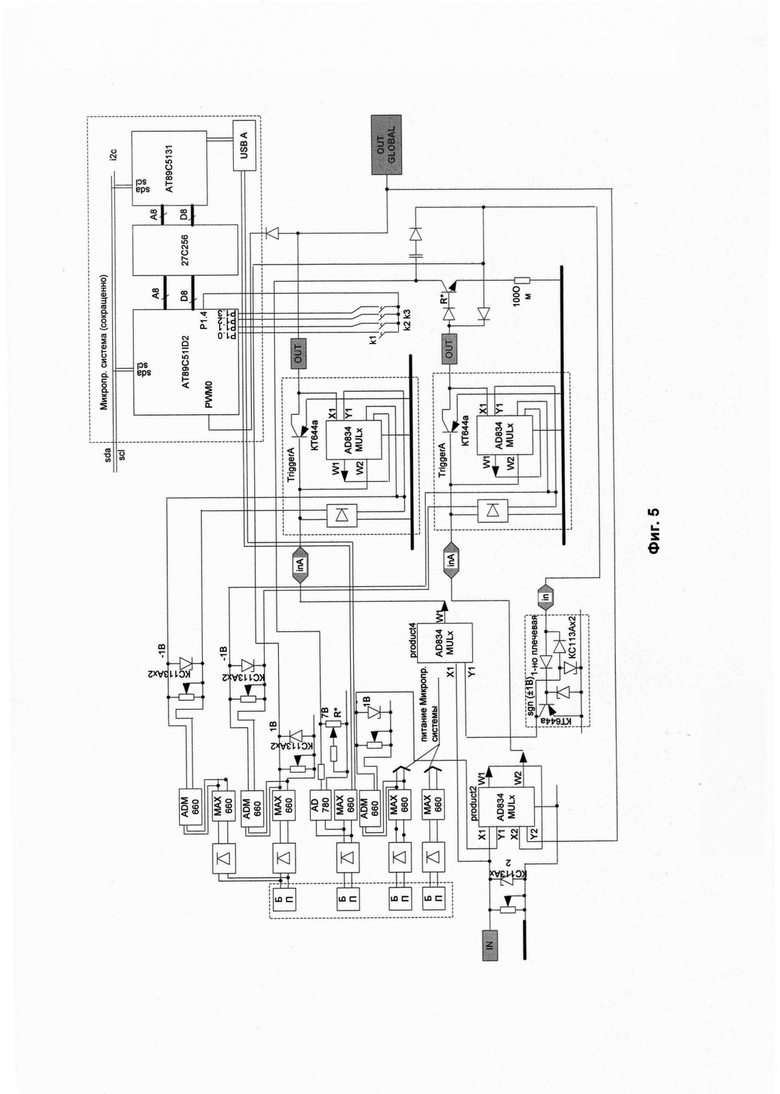

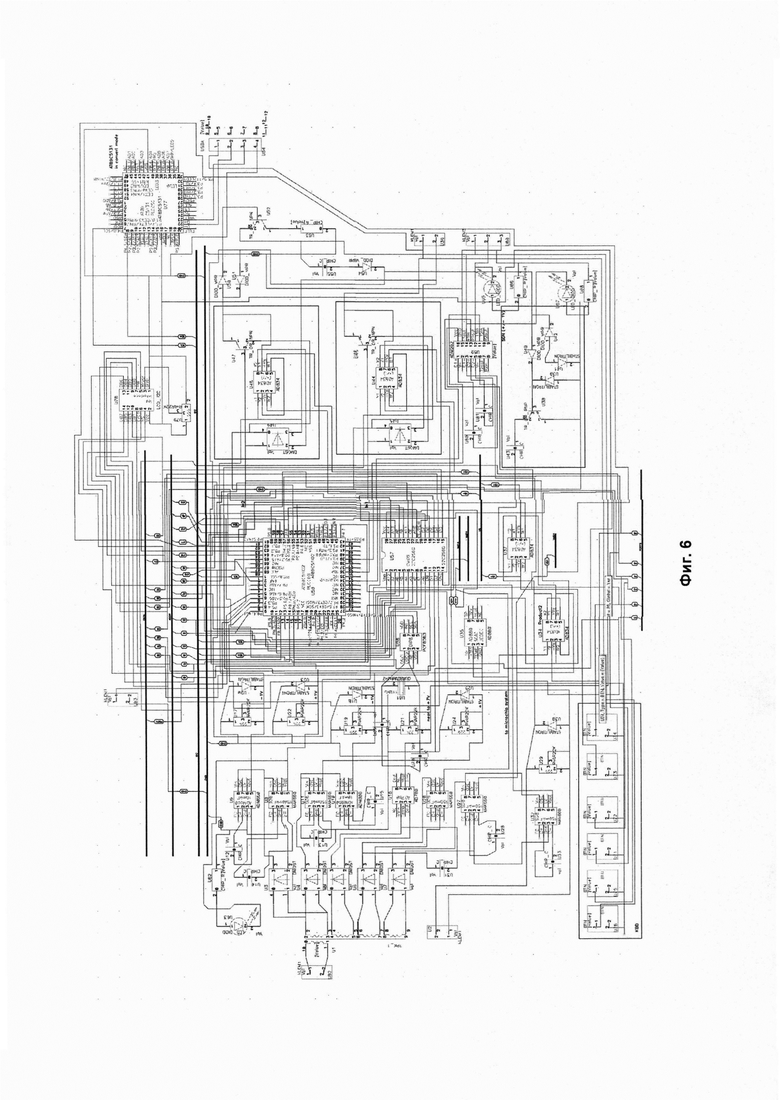

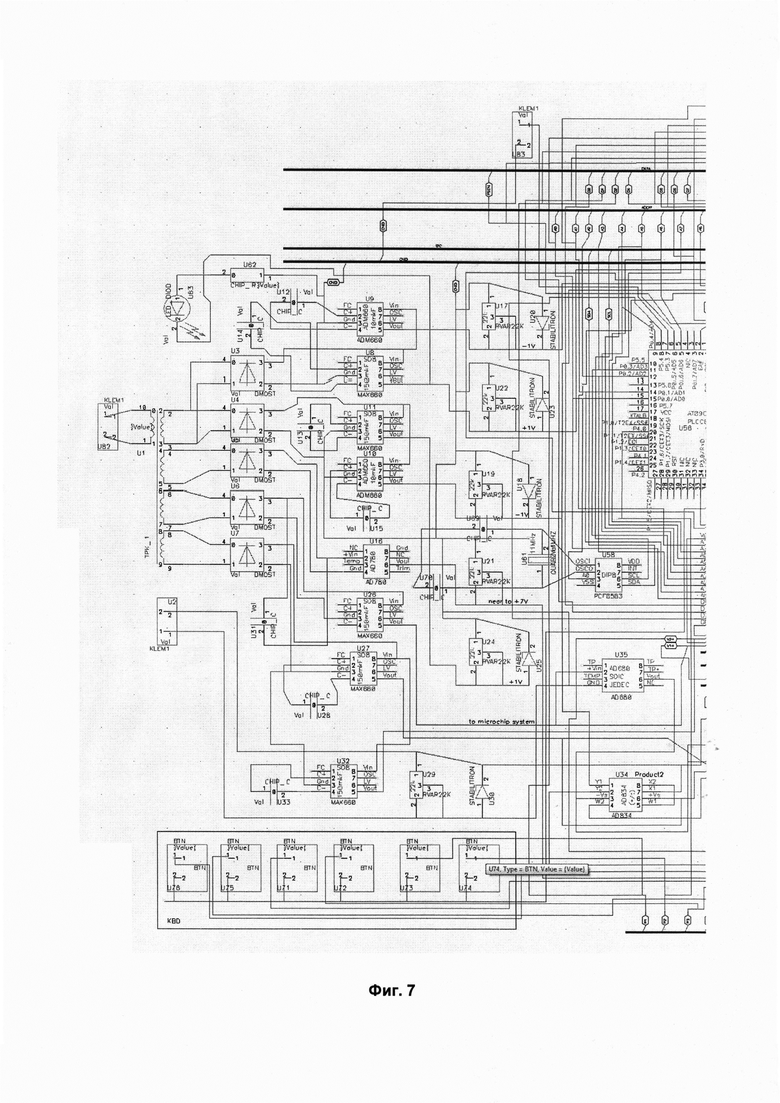

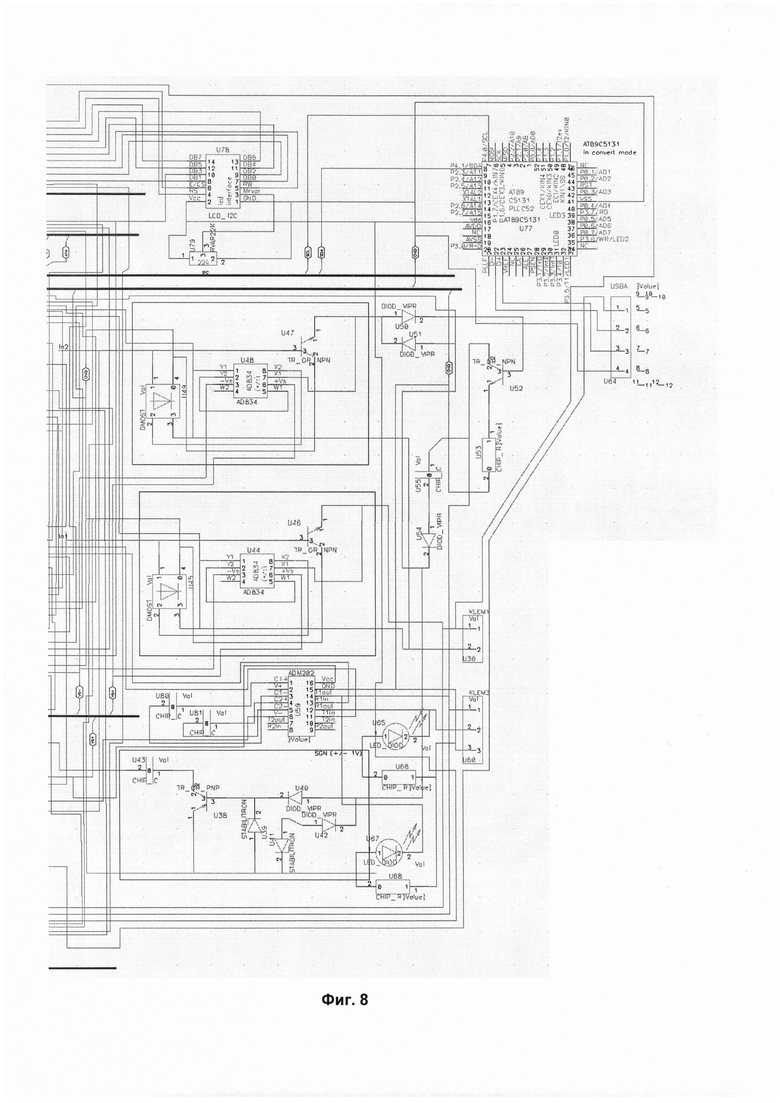

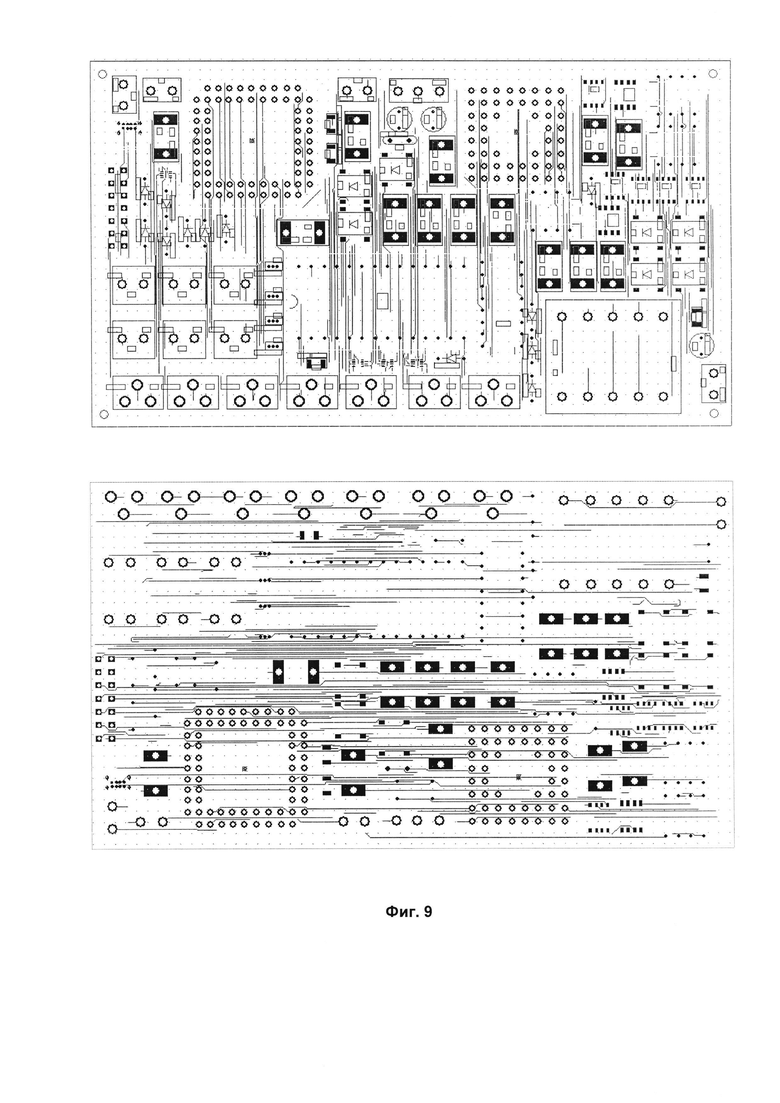

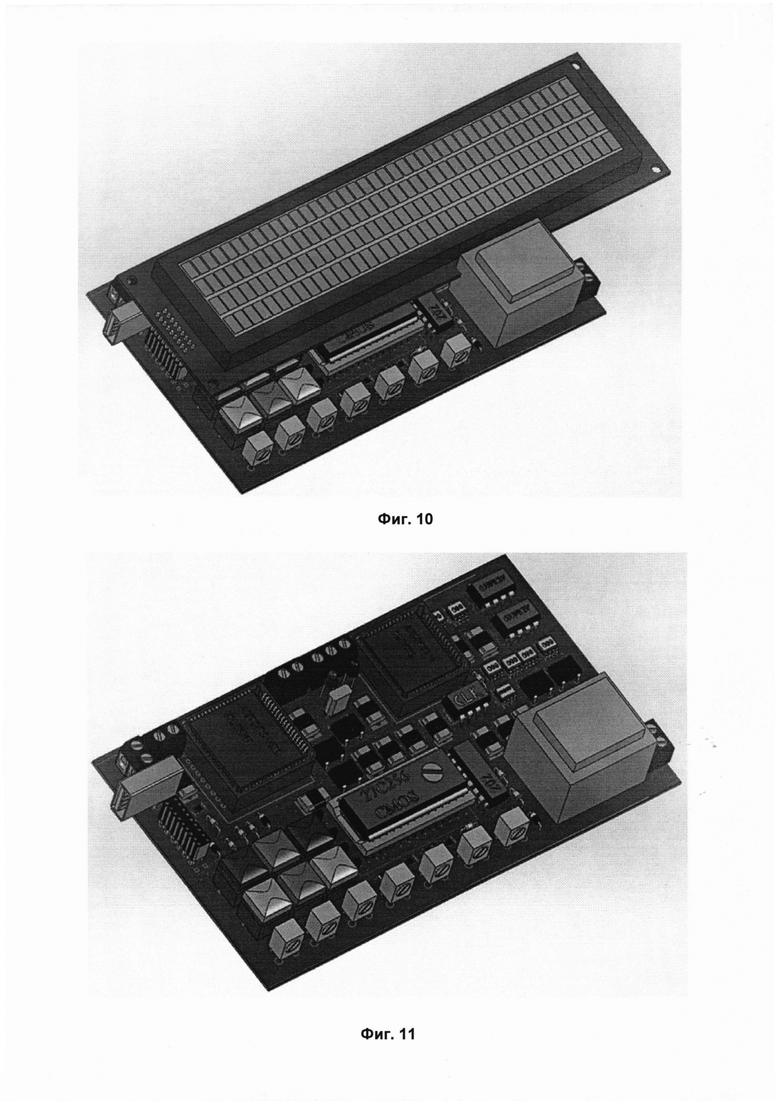

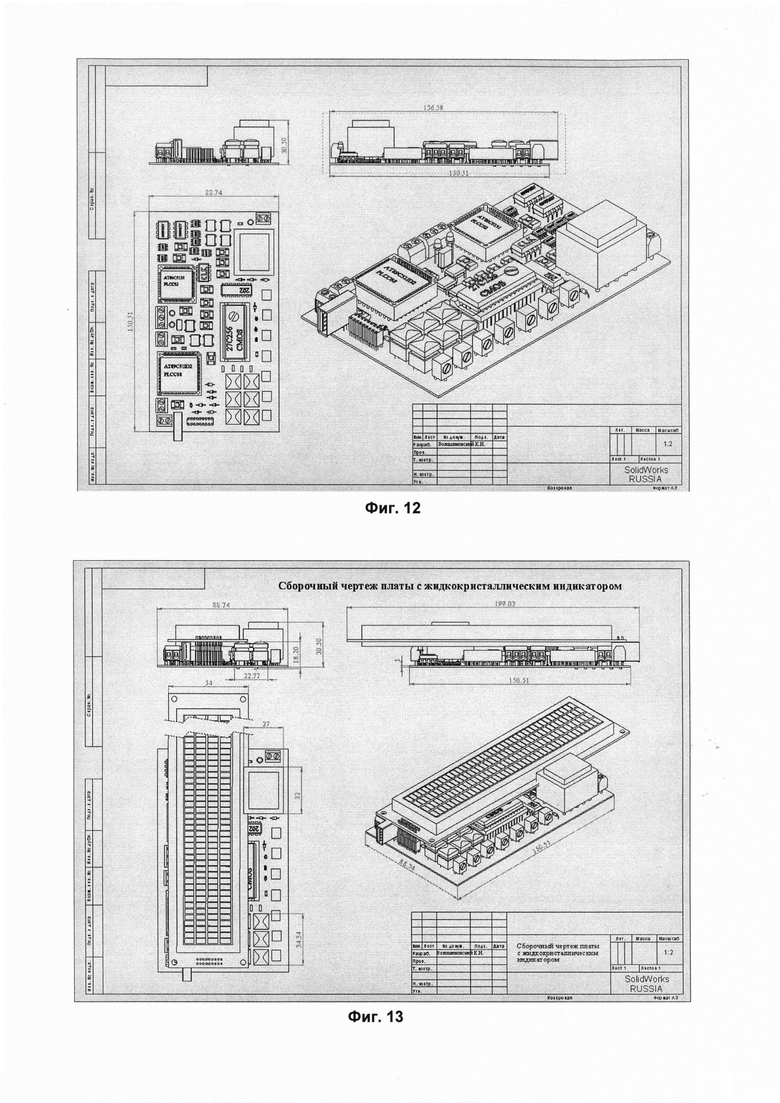

На фиг 1. представлена схема устройства для осуществления способа преобразования электрических импульсов в код Манчестер. На фиг 2. представлена краткая схема прототипа макетно-отладочной платы ЕВ-552. На фиг. 3 приводится схема, поясняющая реализацию предлагаемого способа. На фиг. 4 показана смена полярности при преобразовании однополярных импульсов на входе в сигнал для управления переключательным триггером [фиг. 1; 10, 11] [фиг 3; 1, 3] устройства для реализации предлагаемого способа. На фиг. 5 представлена схема для аппаратной реализации способа [фиг. 3]. На фиг. 6 приводится общий вид ориентировочной принципиальной схемы для предлагаемого устройства. На фиг. 7. и 8 показаны участки принципиальной схемы в масштабе. На фиг. 9. представлена разводка принципиальной схемы предлагаемого устройства. На фиг. 10 представлен внешний вид устройства с жидкокристаллическим индикатором DV40400. На фиг. 11 представлен внешний вид устройства для реализации предлагаемого способа с микропроцессорной системой управления. Ориентировочный вид промышленной реализации предлагаемого устройства в сборке с жидкокристаллическим индикатором (ЖКИ) приводится на фиг. 12, и без ЖКИ на фиг 13.

Функционирование изобретения

Устройство фиг. 1 работает следующим образом: на вход 9 поступает входной информационный импульсный сигнал, в котором информация передается в двоичном коде с установкой условного единичного уровня напряжения на время длительности передачи бита, например с предварительного кодера, далее с помощью сложного триггера [фиг. 1; 9-20] исходный сигнал преобразуется в сигнал, в котором определение единичного и нулевого бита производится не по фиксации единичного или нулевого уровня напряжения, например, с помощью компаратора, а в процессе смены уровня, например при смене уровня с 1,3 В на 0 В, считается, что передан ноль, а при смене уровня напряжения с 0 В на 1,3 В считается, что передана единица, или наоборот. Полученный выход вводится в микропроцессорную систему [фиг.1; 1-8] на обычный порт процессора или порт PWM широтно-импульсного модулятора, информация о выходном сигнале может накапливаться в микросхеме ПЗУ EEPROM АТ24С64 или другой с интерфейсом I2C, а синхронизация мониторинга во времени проводится с помощью микросхемы часов-календаря, например PCF8583.

Осуществление устройства изобретения выполняется на базе микропроцессорной системы с процессорами AT89C51id2 и АТ89С5131 на микросхемах произведения AD834 [фиг. 5]. Блок определения знака выхода второго триггера может быть выполнен на транзисторе КТ644а с ограничением амплитуды с помощью стабилитронов KC113A. Получение плечей отрицательного напряжения -1 В производится с помощью микросхем ADM660 с приближенной подстройкой и ограничением с помощью стабилитрона. Таким образом, когда все уровни среза напряжений приведены к одну уровню стабилизации, а напряжение 1,3 В из стандартного ряда можно считать ориентировочным напряжением единичного уровня. Коррекция обратной связи выхода второго переключательного триггера выполняется с помощью высокочастотного транзистора КТ295а, с подпором +7 В и коэффициентом усиления -2 (минус два), причем +7 В единственное входное напряжение подпора, которое требует точной подстроки. Таким образом, точно настраивается только одна ручка, остальные лишь ориентировочно с расчетом на последующее ограничение стабилитроном.

Описание блоков схемы предварительного моделирования [фиг. 3], подтверждающей реализуемость предлагаемого способа

Схема предварительного моделирования преобразователя импульсного сигнала (9) в код Манчестер на главном выходе схемы (6) состоит из:

- двух триггеров с произвольной амплитудой входа (1, 2);

- двух блоков произведения (3, 13, 18);

- инвертора в составе усилителя-инвертора (11) сумматора (12) и источника единичного напряжения (20);

- усилителя инвертора (16) с коэффициентом усиления ky=-2 (минус два);

- сумматора (17);

- осциллографа контроля управляющего напряжения (19);

- блока ограничения сигнала по амплитуде и определения сигнала sgn (10).

Первый триггер (1) с произвольной амплитудой входа состоит из: сумматоров (4) и (8); усилителя развязки с единичным коэффициентом усиления (5); блока определения модуля входного напряжения (6); блока произведения (7); источника напряжения 1 B (9). Второй триггер (2) с произвольной амплитудой входа состоит из: сумматоров (14) и (23); усилителя развязки с единичным коэффициентом усиления (15); блока определения модуля входного напряжения (21); блока произведения (22); источника напряжения 1 B (24).

Сначала импульсы входа (9), имеющие положительную амплитуду, преобразуются в управляющий сигнал [фиг. 4.2] с инверсией полярности для каждого четного импульса, после чего полярность управляющего сигнала запоминается первым триггером (1), на время пока на входе нулевой уровень напряжения. Таким образом, на выходе первого триггера при поступлении импульса на входе происходит смена уровня, что соответствует передаче данных в коде Манчестер.

Список литературы

Прототип:

1. Голов А.А. ЕВ552. Техническое издание. КТЦ-МК, 1998, 8 с.

Аналоги:

2. MIL-STD 1553. Getting starting manual. AIM USA. Avioncs interface mofules. Elkhorn, NE 68022.

3. USB1553-1/2. Single or Dual Stream MIL-STD-1552A/B. Test&Simulation module for USB. AIT USA Omaha, NE 68022.

4. US Patent 5,367,641. MIL-STD-1553 Interface device having a bus controller minor frame timer. Nov 22, 1994.

5. US Patent 5,325,359. MIL-STD-1553 Interface device having concurrent remote terminal and monitor terminal operation. Jan 28, 1994.

6. US 6212224B1. MIL-STD-1553 buffer/driver. 18 dec, 1997.

7. US 2015/0286607 A1. Determination of the state of an I2C bus. Oct 8, 2015.

8. US 5564090 A. Method apparatus for dynamical adjusting receiver squelch threshold. Oct 8, 1996.

Источники, определяющие технический уровень предлагаемого изобретения

9. Ремизевич Т.В. Микроконроллеры для встраиваемых приложений: от общих подходов к семействам НС05 и НС08 фирмы Motorola. М.: ДОДЭКА, 2000, - 272 с.

10. Хаммел Р.Л. Последовательная передача данных. Руководство для программиста. М.:МИР СК ПРЕСС, 1996, - 752 с.

11. Волошиновский К.И. Свидетельство об официальной регистрации программы для ЭВМ №2012615700, 22 июня 2012 г., Программа для макетно-отладочной платы ЕВ552 с модулями-драйверами для порта RS232, шины I2C, часов PCF8583, EEPROM АТ24С64, ЖКИ, электронного корректора Sevc-91 и модулем описания портов Atmel (Intel) - совместимого 8-битного процессора.

12. Волошиновский К.И. Свидетельство об официальной регистрации программы для ЭВМ №2005611489, 20 июня 2005 г. Модуль опроса и обработки архивных данных микропроцессорных вычислителей ПРИЗ (ПРИ3-WIN).

13. Волошиновский К.И. Исследование и испытание и приборов и систем. Учеб. Пособие. - М.: МГГУ, 2014. - 120 с.

14. Волошиновский К.И. Свидетельство об официальной регистрации программы для ЭВМ №2015619051, 24 августа 2015 г. Переключательные триггеры на непрерывных элементах и двоичные.

Термины и определения

15. ГОСТ Р 52070-2003. Интерфейс магистральный последовательный системы электронных модулей. Общие требования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА АВТОМАТИЧЕСКОГО КОНТРОЛЯ КОТЕЛЬНОЙ | 2017 |

|

RU2656670C1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для управления многокоординатным оборудованием | 1987 |

|

SU1427334A1 |

| Устройство управления аналого-цифровым преобразователем | 1978 |

|

SU748399A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УГЛОВ | 2021 |

|

RU2768504C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОГОПРОЦЕССОРНОЕ УСТРОЙСТВО ВЫЧИСЛЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2006 |

|

RU2333531C1 |

Изобретение относится к электронным информационным техническим решениям общего назначения. Технический результат заключается в обеспечении устранения взаимовлияния прямого тракта и обратной связи, а также устранение апериодического эффекта от обратной связи. Предлагаемый способ состоит в том, что последовательность импульсов с входа устройства подвергается инверси знака для каждого четного импульса, посредством сохранения в памяти состояния входа на предыдущем шаге с помощью вспомогательного триггера, если на предыдущем шаге уровень сигнала был зафиксирован, то текущий шаг вычислений рассматривается в качестве четного. Последовательность импульсов на входе подвергается инверсии, чтобы обеспечить срабатывание триггера детектора сигнала на предыдущем шаге в противофазе по отношению к основному триггеру, на который и поступает полученная промежуточная последовательность импульсов с инверсией знака для каждого четного импульса, которая перед этим подвергается дополнительной коррекции. 2 н.п. ф-лы, 13 ил.

1. Способ преобразования последовательности электрических импульсов в код Манчестер, состоящий в том, что исходная последовательность импульсов, нормированная по скорости, обрабатывается с помощью прошиваемого в процессор алгоритма программы, представляемой на языке ассемблер для компилятора А51, при этом передача информационных импульсов проводится с определением уровня амплитуды импульса с помощью компаратора в течение заранее настраиваемой и задаваемой длительности импульса, при таком нормировании периода и длительности импульса выдача информационного бита ограничивается минимальными длительностью и периодом, а алгоритм обработки для окончательного преобразования последовательности импульсов в заданный код осуществляется предлагаемым способом, отличающийся тем, что последовательность импульсов подвергается инверсии знака для каждого четного импульса, посредством сохранения в памяти состояния входа на предыдущем шаге с помощью вспомогательного триггера, если на предыдущем шаге уровень сигнала был зафиксирован, то текущий шаг вычислений является четным, после чего последовательность импульсов на входе подвергается инверсии, чтобы обеспечить срабатывание вспомогательного триггера детектора сигнала на предыдущем шаге в противофазе по отношению к основному триггеру, состояние уровня, определяемого полученной последовательностью импульсов с инверсией знака для каждого четного импульса, которая перед этим подвергается дополнительной коррекции, фиксируется на выходе основного триггера, полученная в ходе фиксации в основном триггере, а полученная в результате преобразования последовательность импульсов представляет из себя результирующую последовательность импульсов, в которой смена уровня происходит при поступлении бита исходной последовательности импульсов, в результате чего при поступлении бита исходной последовательности импульсов на выходе происходит смена уровня сигнала с инверсией знака выхода, что соответствует передаче сигнала в формате кода Манчестер, а интервал и период импульсов не ограничены минимальными величинами.

2. Устройство для осуществления способа преобразования последовательности электрических импульсов в код Манчестер, содержащее микропроцессорную систему, включающую в себя базовую систему ввода вывода, с блоком транзистор-транзисторной логики для управления шиной адреса/данных, дополнительного опционального процессора, альтернативного центральному процессору микропроцессорной системы, интерфейса RS232 с разъемом, шины I2C с разъемом, второго опционального процессора, подключаемого по шине I2C, и жидкокристаллического индикатора, отличающееся тем, что в состав устройства введены преобразователь информационного импульсного сигнала в выход в формате Манчестер; опциональный процессор, подключаемый по шине I2C для обеспечения USB порта, переключательная схема устройства содержит главный импульсный вход, два триггера со срабатыванием по произвольной амплитуде, блоки произведения, предназначенные для управления входом триггеров; блоки коррекции выхода второго триггера и усилитель с точной настройкой для коррекции выхода второго триггера, сумматор смещения сигнала и блок произведения, с выдачей опорного константного сигнала единичного уровня с блока опорного напряжения, причем после коррекции выхода второго триггера уровень сигнала, амплитуда которого не менее единицы по модулю, ограничивается блоком определения знака сигнала sgn, соединенные между собой таким образом, что выходной сигнал после коррекции и ограничения со второго триггера имеет амплитуду минус один вольт для каждого четного импульса, и плюс один вольт для каждого нечетного, таким образом при поступлении информационного бита на главный вход, обеспечивая переключение первого триггера со сменой уровня, при этом второй триггер работает в противофазе по отношению к первому триггеру и получает входной сигнал с главного входа через инвертор, в отличие от первого триггера, определяя состояние на предыдущем такте при нулевом уровне на главном входе, что позволяет избежать применения звеньев запаздывания как для Манчестер преобразования или появления запаздывания в процессе программной обработки сигнала с помощью микропроцессорной системы устройства.

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

Авторы

Даты

2018-02-12—Публикация

2016-03-11—Подача