2.Иэмеритепь по По1, отличающийся тем, что микропроцессор содержит оперативный запоминающий блок, информационный вход которого является первым входом микропроцессора, а вход управления и адрес {ый вход подключены к первому выходу постоянного, запоминающего блока и адресному выходу центрального процессорного элемента соответственно, второй вход микропроцессора соединен с входом формирователя начального адреса/ выход которого подключен к блока микропрограммного управления, выход которого соединен с входом постоянного запоминающего блока, второй выход которого подключен к управляющему входу центрального процессорного элемента, а третий выход соединен с управляющим входом блока микропрограммного управления, причем информационный выход центрального процессорного элемента является одновременно и выходом микропроцессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель коэффициента гармоник | 1986 |

|

SU1366964A1 |

| Устройство для поверки ваттметров | 1985 |

|

SU1267312A1 |

| Устройство для измерения параметров пассивного комплексного двухполюсника | 1983 |

|

SU1244598A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для автоматического измерения времени распространения ультразвука | 1988 |

|

SU1523924A1 |

| Устройство для контроля параметров | 1988 |

|

SU1665390A1 |

| Устройство для построения гистрограммы -интервалов | 1978 |

|

SU721079A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для исследования электрических цепей | 1985 |

|

SU1332340A1 |

| Устройство для сигнализации | 1986 |

|

SU1481824A1 |

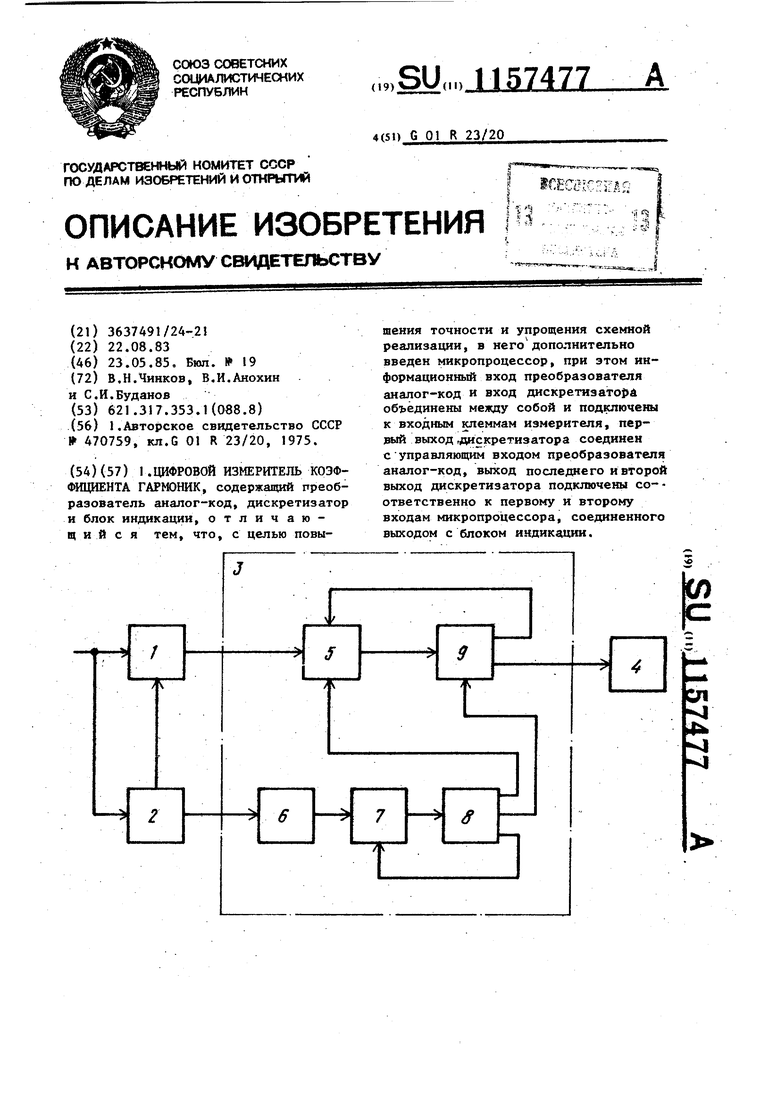

I.ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КОЭФ«МЩИЕНТА ГАРМОНИК, содержащий преобразователь аналог-код, дискретизатор и блок индикации, отличающийся тем, что, с целью повышения точности и упрощения схемной реализации, в него дополнительно введен микропроцессор, при этом информационный вход преобразователя аналог-код и вход дискретизаторй обьединены между собой и подключены к входным клеммам измерителя, первый выходлискретизатора соединен суправляющим входом преобразователя аналог-код, выход последнего и второй выход дискретизатора подключены со- ответственно к первому и второму входам микропроцессора, соединенного выходом с блоком индикации.

Изобретение относится к области электро- и радиоизмерений и может быть использовано при измерении коэ фициента гармоник. Цель изобретения - повышение точ ности и упрощение схемной реализации . На чертеже изображена блок-схема предлагаемого устройства. В состав измерителя коэф(1«циента гармоник входят преобразователь 1 аналог-код, дискретизатор 2, микропроцессор 3, блок 4 индикации. Микропроцессор 3 включает операт ный запоминающий блок 5, формирователь 6 начального адреса, блок 7 микропрограммного управления, посто янный запоминающий блок 8, централь ный процессорный элемент 9. Информадиониьй вход преобразователя 1 аналог-код и вход дискретизатора 2 объединены между собой и подключены к входу прибора. Первый выход дискретизатора 2 соединен с управляющим входом преобразователя аналог-код. Выход преобразователя 1 аналог-код-родключен к первому входу микропроцессора 3. Второй выход дискретизатора 2. соединен с вторым входом микропроцессора 3, выход которого подключен к входу блока 4 индикации. К первому и второму входам микропроцессора подключен соответственно информационный вход оператийного запоминающего блока 5 и вход формирователя 6 начального адр са. Выход формирователя 6 начальног адреса соединен с первым входом бло ка 7 микропрограммного управления, второй вход которого подключен к третьему выходу постоянного запоминающего блока 8. .Выход блока 7 микропрограммного управления соединен с входом постоянного запоминающего блока 8,первый и второй выходы которого подключены соответственно к управляющему входу оперативного запоминающего блока 5 и управляющему входу центрального процессорного элемента 9. Выход оперативного запоминающего блока 5 соединен с информационным входом центрального процессорного элемента 9. Первый и второй выходы центрального процессорного элемента 9 подключены соответственно к адресному входу оперативного запоминающего блока 5 и к выходным клеммам микропроцессора 3. Устройство работает следующим образом. Исследуемый сигнал f (t) поступает на преобразователь 1 аналог-код и дискретизатор 2. Дискретизатор 2 формирует N точек дискретизации t за период (или несколько периодов ) исследуемого сигнала и в эти моменты вьщает команду на запуск преобразователя I аналог-код. Кроме того, пер- вый импульс запуска преобразователя 1 аналог-код, фopмиpye в Iй дискретизатором 2, по второму выходу дискретизатора 2 поступает на второй вход микропроцессора 3 и по этому входу - на вход формирователя 6 начального адреса. Формирователь 6 начального адреса задает начальный адрес программы измерения. Этот адpec по выходу формирователя 6 начального адреса поступает на информационный вход блока 7 микропрограм много управления.Последний организу ет последовательную вьщачу команд программы с постоянного запоминающе го блока 8 стандартным способом. При этом инструкции для формировани следующего адреса поступают по управляющему входу на блок 7 микропрограммного управления с третьего выхода постоянного запоминающего блока 8. Сформированный блоком 7 микропрограммного управления первый адрес программы по его выходу поступает на вход постоянного запоминающего блока 8. При этом на выходе последнего появляется первая команда программы измерения. По этой команде оперативный запоминающий блок 5 переводится в режим записи, центральный процессорный элемент 9 форм рует первый адрес, который подается на адресный вход оперативного запоминающего блока 5, а блок 7 микропрограммнбго управления формирует следующий адрес программы измерения В результате выполнения этой команды программы измерения в первой ячейке оперативного запоминающего блока 5 записан первый код мгновенного значения исследуемого сигнала -По 2,3,4,,..., N команде работа прй бора аналогична описанной за исключением того, что центральный процес сорный элемент 9 формирует соответственно 2,3,4..., N адрес выбора ячейки оперативного запоминающего блока 5. После N циклов в оперативном запоминающем блоке 5 записано N кодов мгновенных значений исслед емого сигнала f (i:) . По (N+1) команде оперативный запоминающий блок 5 переводится в режим считывания и в центральном процессорном элементе 9 непосредственно организуется процесс вычисления коэффициента гармоник. При этом на первом этапе вычисля ются квадратурные составляющие амплитуды первой гармоники исследуе мого сигиапа В и С, согласно формулам м f(,nu,t. ;

4

f(ii).

1 1

m-1

tn-l

2 E Slnwtn ; .cosw ЛД cixO q. ei,

Я Коды нормированных гармоник siniot и cos40-1 i подаются в центральный процессорный элемент по управляющему входу с постоянного запоминающего блока 8. На втором этапе определяется действующее значение Y первой гармоники согласно формуле На третьем этапе определяется дей-. ствующее значение высших гармоник исследуемого сигнала V : . V y-l-2I rf(t.V6sinu t.-Ccosu)t,1 . I Ha четвертом этапе непосредственно вычисляется коэффициент гармоник Kj. согласно формуле К /Y . Результаты вычисления отображаются на блоке 4 индикации. В предлагаемом измерителе достигается более высокая точность за счет того, что действующие значе1шя первой и высших гармоник вычисляются по одним и тем же кодам мгновенных значений исследуемого сигнала, что приводит к снижению методической погрешности, обусловленной нестабильностью исследуемого напряжения. Оценим относительную погрешность при измерении коэффициента гармоник ((/к J.) соответственно известттм и предлагаемым устройствами. Обозначим через . погрешность преобразования мгновенного значения f (-t ) в код при измерении действующего значения Y первой гармоники, а через 2 погрешность преобразования при измерении: действующего значения высших гармоник. Введем обозначение а, { (t;)-Ssinwt--С cosujt, . Погрешность величины с , обусловенную погрешность , обозначим ерез - . Тогда измеренное значение еличины d равно с.. «%ач . де о - истинное значение, при от утствии погрешности Е .r.-iftsiMjO-t -flCcos uj-t ; (1)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-05-23—Публикация

1983-08-22—Подача