Изобретение относится к вычислительной технике и предназначено для исследования электрических цепей.

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности определения токов и напряжений в узлах и элементах цепи в заданные моменты времени,

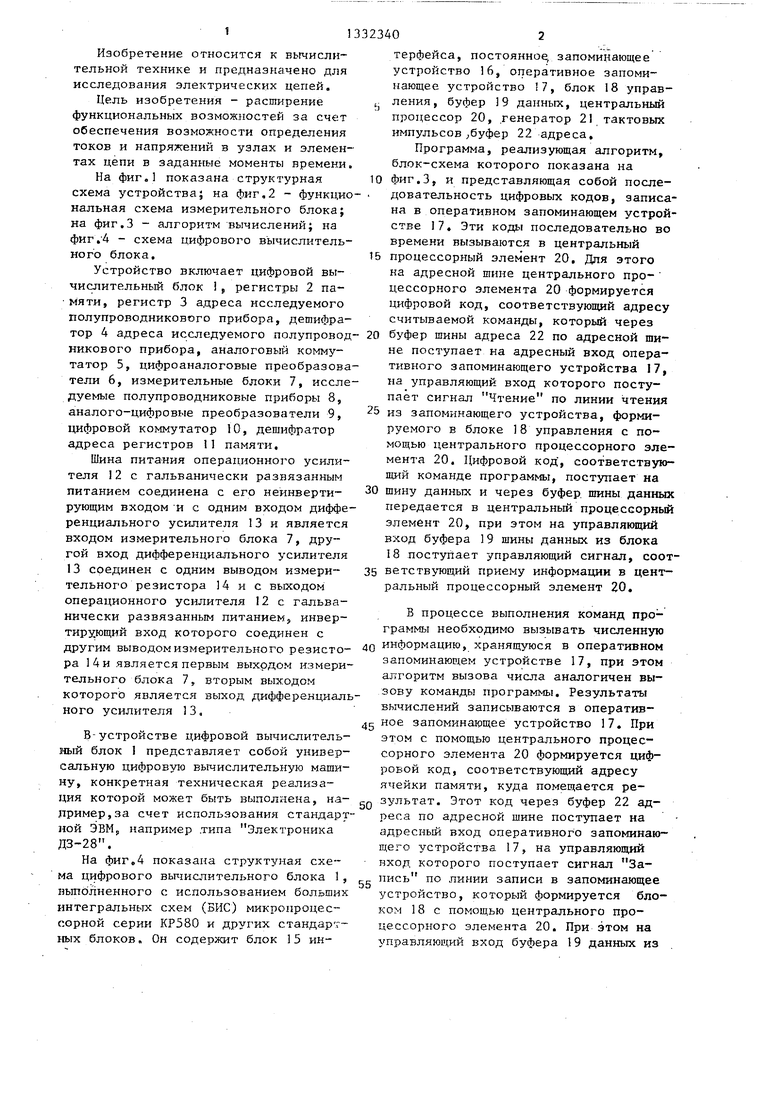

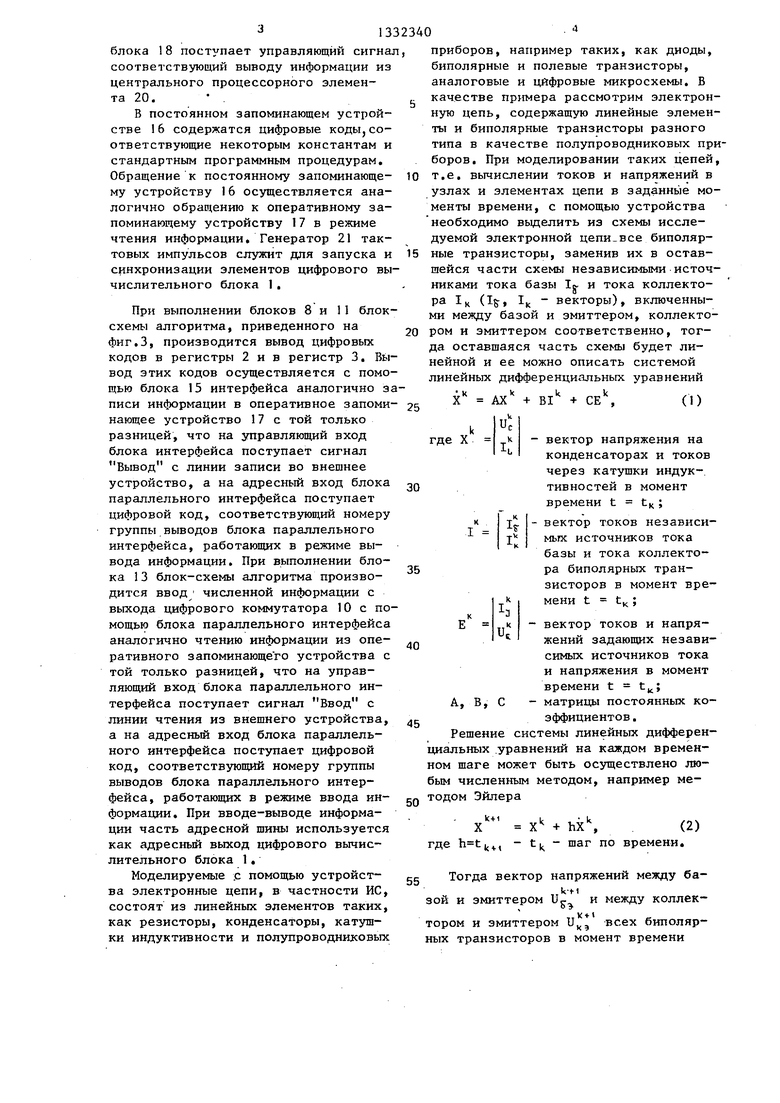

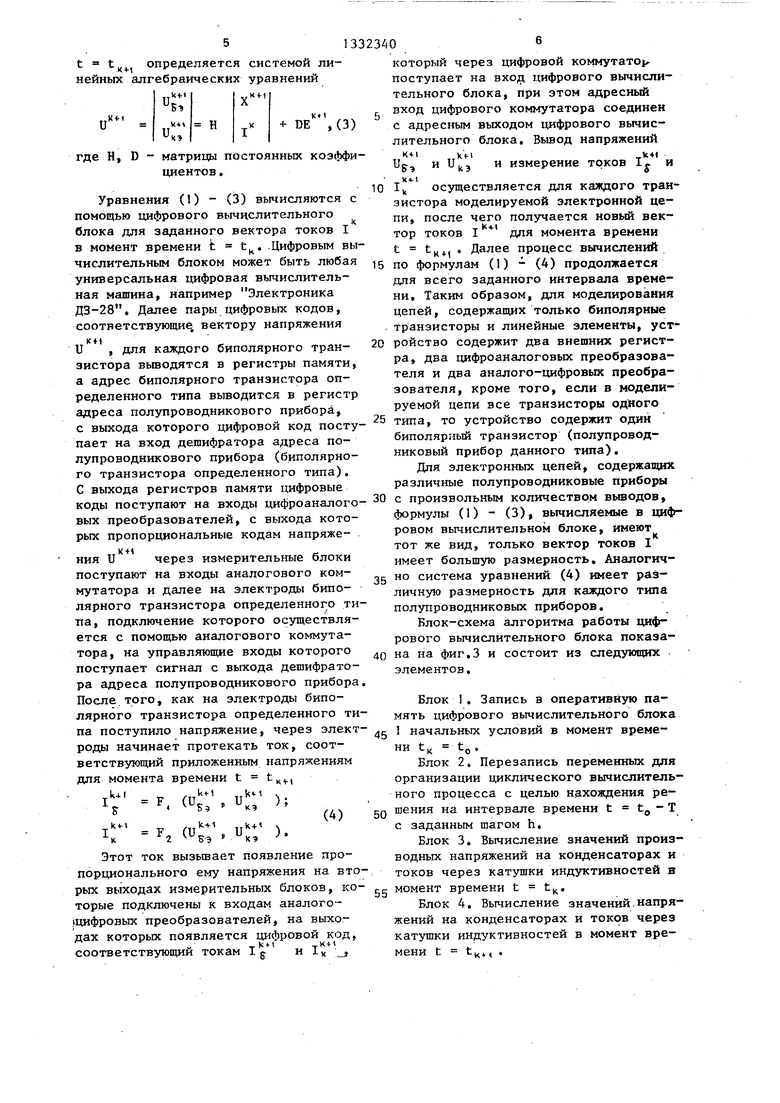

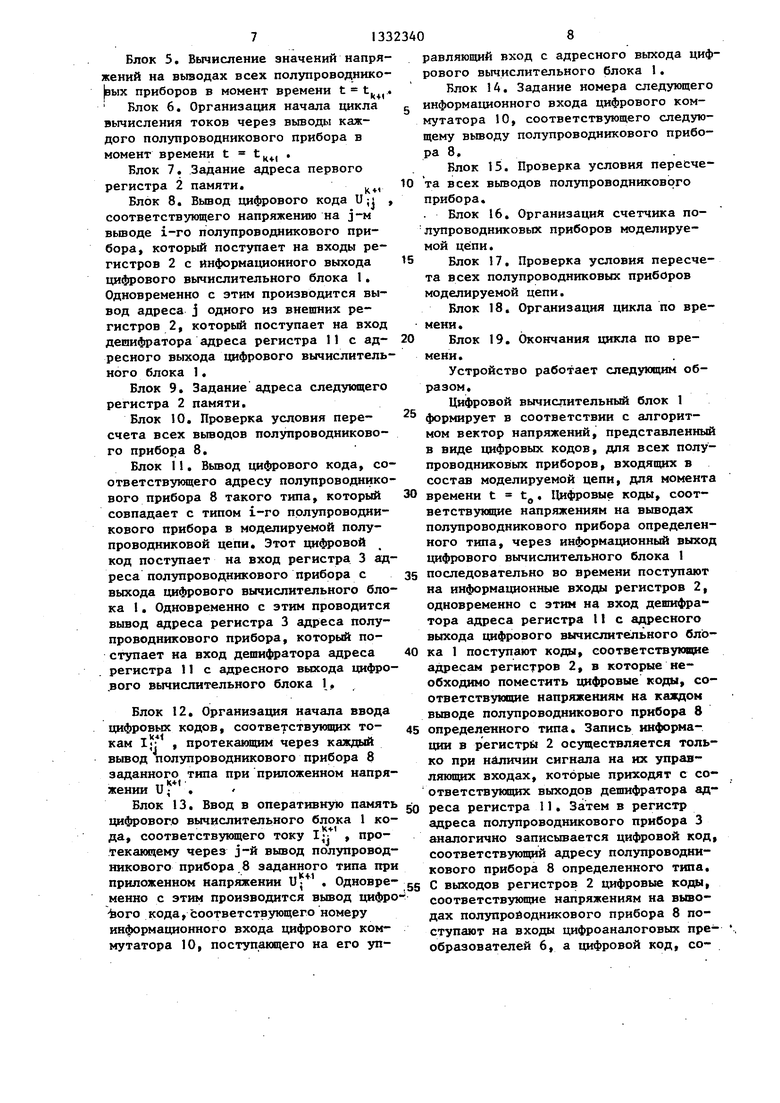

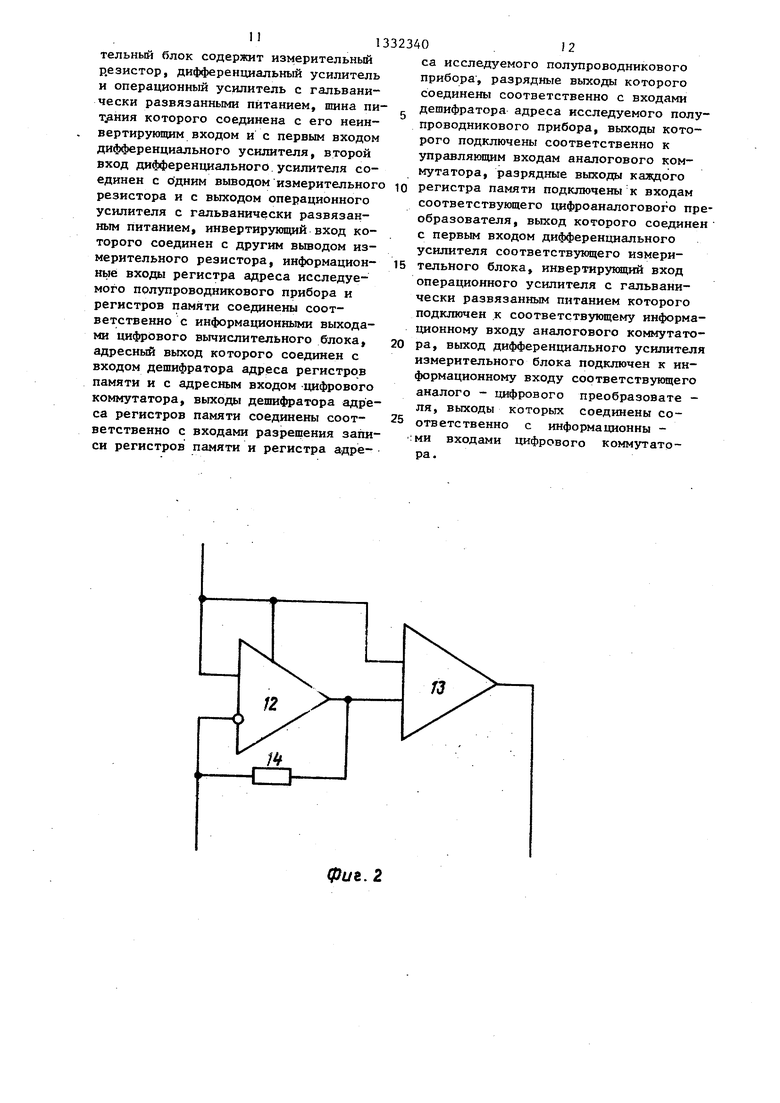

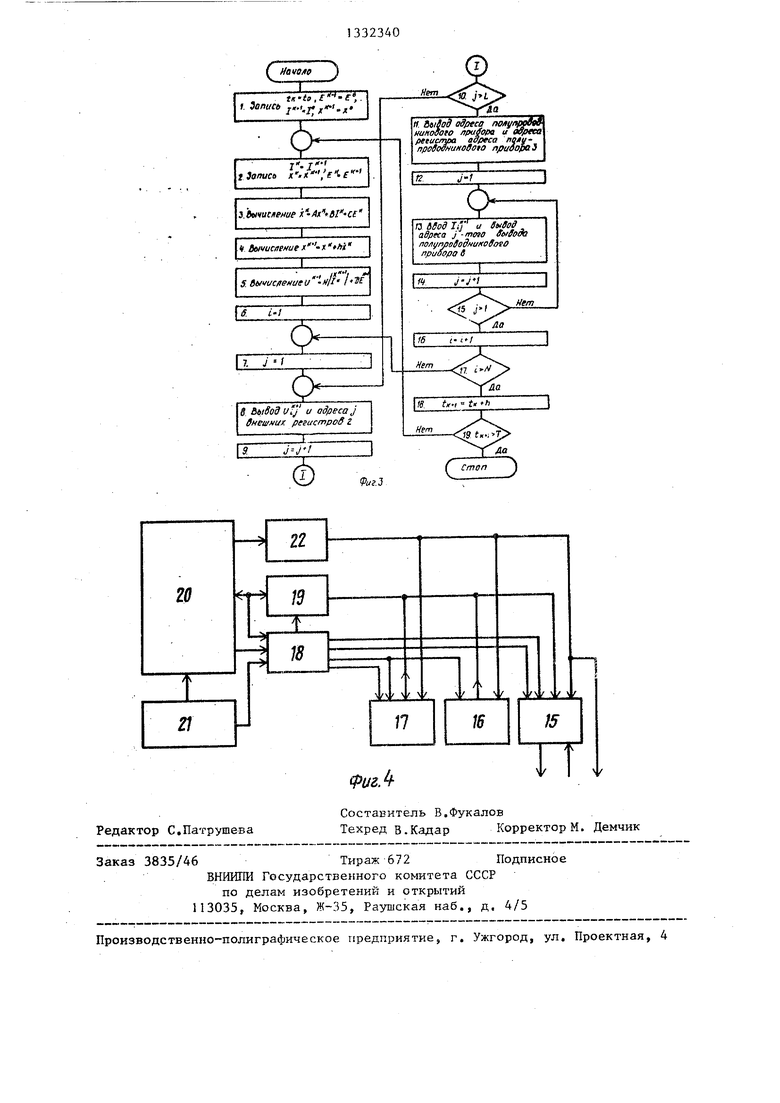

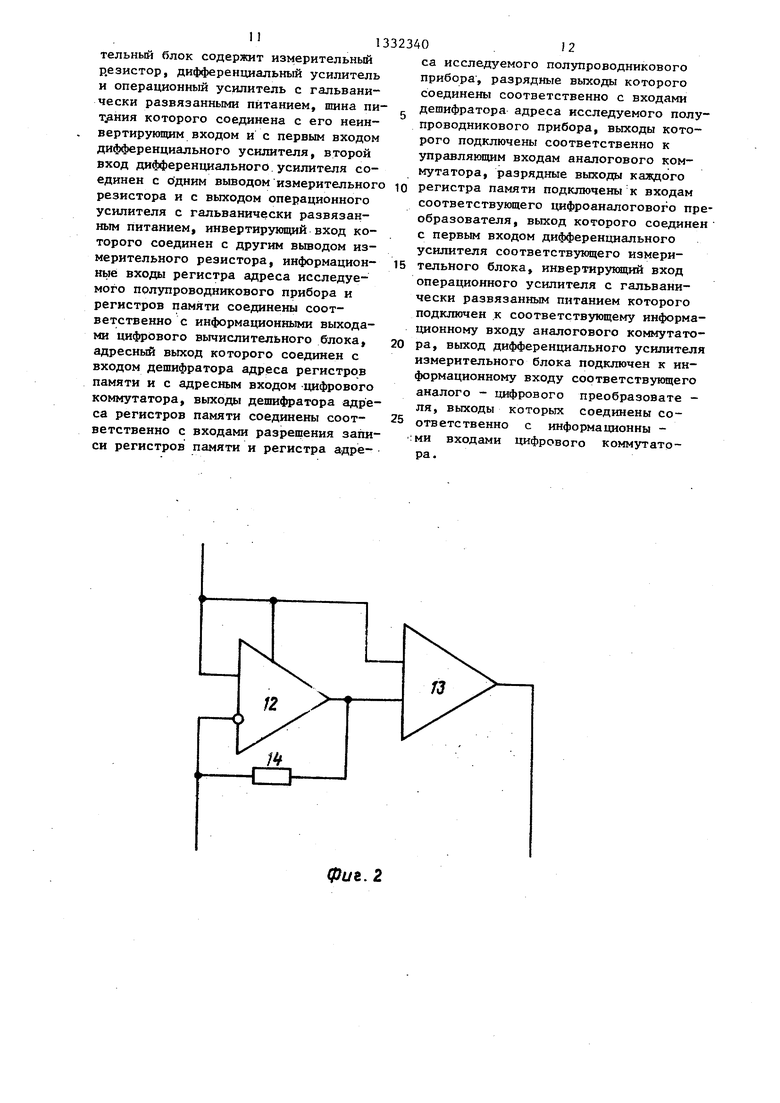

На фиг.1 показана структурная схема устройства; на фиг,2 - функциональная схема измерительного блока; на фиг.З - алгоритм вычислений; на фиг . 4 - схема цифрового вычислительного блока.

Устройство включает цифровой вычислительный блок f регистры 2 памяти, регистр 3 адреса исследуемого полупроводникового прибора, дешифратерфейса, постоянное, запоминающее устройство 16, оперативное запоминающее устройство 7, блок 18 управJ ления, буфер 19 данных, центральный процессор 20, генератор 21 тактовых импульсов ;буфер 22 адреса.

Программа, реализующая алгоритм, блок-схема которого показана на

10 фиг.З, и представляющая собой последовательность цифровых кодов, записана в оперативном запоминающем устройстве I7. Эти коды последовательно во времени вызываются в центральный

15 процессорный элем ент 20. Для этого на адресной шине центрального про- цессорного элемента 20 формируется цифровой код, соответствующий адресу

считываемой команды, который через тор 4 адреса исследуемого полупровод- 20 буфер шины адреса 22 по адресной ши- никового прибора, аналоговьпЧ комму- не поступает на адресный вход оперативного запоминающего устройства 17, на управляющий вход которого поступает сигнал Чтение по линии чтения 25 из запоминающего устройства, формируемого в блоке 18 управления с помощью центрального процессорного элемента 20. Цифровой код, соответствующий команде программы, поступает на 30 шину данных и через буфер, шины данных передается в центральный процессорньй элемент 20, при этом на управляющий вход буфера 19 шины данных из блока 18 поступает управляющий сигнал, соот- 35 ветствующий приему информации в центральный процессорный элемент 20.

татор 5, цифроаналоговые преобразователи 6, измерительные блоки 7, исследуемые полупроводниковые приборы 8, аналого-цифровые преобразователи 9, цифровой коммутатор 10, дешифратор адреса регистров 11 памяти.

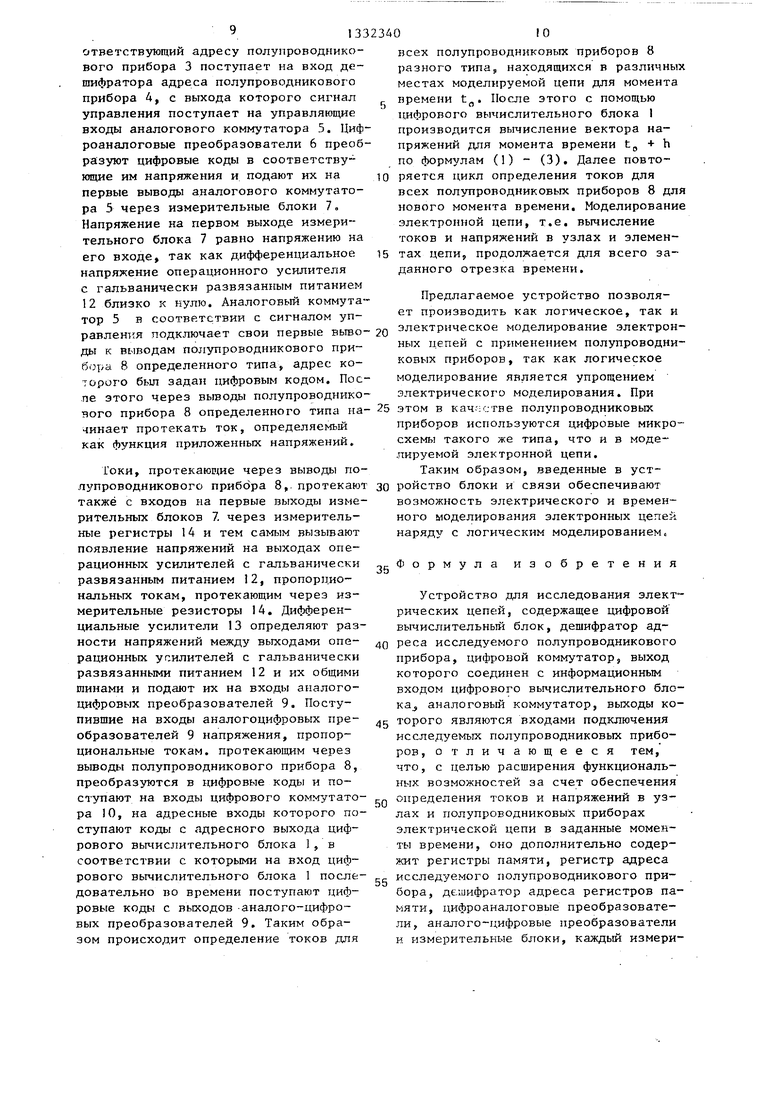

Шина питания операционного усилителя 12 с гальванически развязанным питанием соединена с его неинвертирующим входом И с одним входом дифференциального усилителя 13 и является входом измерительного блока 7, другой вход дифференциального усилителя 13 соединен с одним выводом измерительного резистора 14 и с вьжодом операционного усилителя 12 с гальванически развязанным питанием, инверВ процессе выполнения команд программы необходимо вызывать численную

В процессе выполнения команд программы необходимо вызывать численную

тирующий вход которого соединен с

другим выводом измерительно го резисто- 40 инФоР ацию,. хранящуюся в оперативном

запоминающем устройстве 17, при этом алгоритм вызова числа аналогичен вызову команды программы. Результаты Бьгаислений записываются в оператив- g ное запоминающее устройство 17. При этом с помощью центрального процесра 14 и является первым выходом измерительного блока 7, вторым выходом которого .является выход дифференциального усилителя 13,

В-устройстве цифровой вычислительный блок 1 представляет собой универсальную цифровую вычислительную машину, конкретная техническая реализация которой может быть выполнена, например, за счет использования стандартной ЭВМр например .типа Электроника ДЗ-28.

На фиг,4 показана структуная схема цифрового вычислительного блока 1, вьтблненного с использованием больших интегральных схем (БИС) микропроцессорной серии КР580 и других стандартных блоков. Он содержит блок 15 ин50

55

сорного элемента 20 формируется цифровой код, соответствующий адресу ячейки памяти, куда помещается результат. Этот код через буфер 22 адреса по адресной шине постзшает на адресный вход оперативного запоминающего устройства 17, на управляющий вход которого поступает сигнал Запись по линии записи в запоминающее устройство, который формируется блоком 18 с помощью центрального процессорного элемента 20. При этом на управляюпщй вход буфера 19 данных из

терфейса, постоянное, запоминающее устройство 16, оперативное запоминающее устройство 7, блок 18 управления, буфер 19 данных, центральный процессор 20, генератор 21 тактовых импульсов ;буфер 22 адреса.

Программа, реализующая алгоритм, блок-схема которого показана на

фиг.З, и представляющая собой последовательность цифровых кодов, записана в оперативном запоминающем устройстве I7. Эти коды последовательно во времени вызываются в центральный

процессорный элем ент 20. Для этого на адресной шине центрального про- цессорного элемента 20 формируется цифровой код, соответствующий адресу

В процессе выполнения команд программы необходимо вызывать численную

0

5

сорного элемента 20 формируется цифровой код, соответствующий адресу ячейки памяти, куда помещается результат. Этот код через буфер 22 адреса по адресной шине постзшает на адресный вход оперативного запоминающего устройства 17, на управляющий вход которого поступает сигнал Запись по линии записи в запоминающее устройство, который формируется блоком 18 с помощью центрального процессорного элемента 20. При этом на управляюпщй вход буфера 19 данных из

блока 18 поступает управляющий сигна соответствующий выводу информации из центрального процессорного элемента 20.

В постоянном запоминающем устройстве 16 содержатся цифровые коды,соответствующие некоторым константам и стандартным программным процедурам. Обращение к постоянному запоминающему устройству 16 осуществляется аналогично обрап4ению к оперативному запоминающему устройству 17 в режиме чтения информации. Генератор 21 тактовых импульсов служит для запуска и синхронизации элементов цифрового вычислительного блока 1.

При выполнении блоков 8 и 11 блок- схемы алгоритма, приведенного на фиг.З, производится вывод цифровых кодов в регистры 2 и в регистр 3. Вывод этих кодов осуществляется с помощью блока 15 интерфейса аналогично записи информации в оперативное запоминающее устройство 17 с той только разницей, что на заправляющий вход блока интерфейса поступает сигнал Вывод с линии записи во внешнее устройство, а на адресный вход блока параллельного интерфейса поступает цифровой код, соответствующий номеру группы выводов блока параллельного интерфейса, работающих в режиме вывода информации. При выполнении блока 13 блок-схемы алгоритма производится ввод численной информации с выхода цифрового коммутатора 10 с помощью блока параллельного интерфейса аналогично чтению информации из оперативного запоминающего устройства с той только разницей, что на управляющий вход блока параллельного интерфейса поступает сигнал Ввод с линии чтения из внешнего устройства, а на адресный вход блока параллельного интерфейса поступает цифровой код, соответствующий номеру группы выводов блока параллельного интерфейса, работающих в режиме ввода информации. При вводе-выводе информации часть адресной щины используется как адресный выход цифрового вычислительного блока 1,

Моделируемые .с помощью устройства электронные цепи, в частности ИС, состоят из линейных элементов таких, как резисторы, конденсаторы, катушки индуктивности и полупроводниковых

0

5

0

приборов, например таких, как диоды, биполярные и полевые транзисторы, аналоговые и цифровые микросхемы, В качестве примера рассмотрим электронную цепь, содержащую линейные элементы и биполярные транзисторы разного типа в качестве полупроводниковых приборов. При моделировании таких цепей, т,е, вычислении токов и напряжений в узлах и элементах цепи в заданные моменты времени, с помощью устройства необходимо вьщелить из схемы исследуемой электронной цепи.все биполярные транзисторы, заменив их в оставшейся части схемы независимыми источниками тока базы 1 и тока коллектора 1 (1 IK векторы), включенными между базой и эмиттером, коллектором и эмиттером соответственно, тогда оставшаяся часть схемы будет линейной и ее можно описать системой линейных дифференциальных уравнений

25

X АХ + BI + СЕ

О)

где X

0

.1

If I

5

0

и:

-вектор напряжения на конденсаторах и токов через катушки индук-. тивностей в момент времени t

-вектор токов независимых источников тока базы и тока коллектора биполярных транзисторов в момент времени t t ;

-вектор токов и напряжений задающих независимых источников тока и напряжения в момент

времени t t

к

А, В, С

45

- матрицы постоянных коэффициентов ,

Решение системы линейных дифференциальных .уравнений на каждом временном шаге может быть осздцествлено любым численным методом, например ме- gQ тодом Эйлера

lC+1

,5, Х -ь

Ч hx .

(2) шаг по времени.

55

Тогда вектор напряжений между баk-t-t

ЗОЙ И эмиттером Ug и между коллекК 1-

тором и эмиттером U, всех биполярных транзисторов в момент времени

определяется системой линейных алгебраических уравнений

1

и

S-

и

кэ

Н

.

I

,(З)

где Н, D матрицы постоянных коэффициентов .

Уравнения (1) - (3) вычисляются с помощью цифрового вычислительного блока для заданного вектора токов I в момент времени t t. .Цифровым вычислительным блоком может быть любая универсальная цифровая вычислительная машина, например Электроника ДЗ-28, Далее пары цифровых кодов, соответствующие, вектору напряжения

и , для каждого биполярного транзистора вьюодятся в регистры памяти, а адрес биполярного транзистора определенного типа выводится в регистр адреса полупроводникового прибора, с выхода которого цифровой код поступает на вход дешифратора адреса полупроводникового прибора (биполярного транзистора определенного типа). С выхода регистров памяти цифровые коды поступают на входы цифроаналого вых преобразователей, с выхода которых пропорциональные кодам напряжения и через измерительные блоки поступают на входы аналогового коммутатора и далее на электроды биполярного транзистора определенного типа, подключение которого осуществляется с помощью аналогового коммутатора, на управляющие входы которого поступает сигнал с выхода дешифратора адреса полупроводникового прибора После того, как на электроды биполярного транзистора определенного типа поступило напряжение, через электроды начинает протекать ток, соответствующий приложенным напряжениям для момента времени t t

r

k+-t

F.

(U (U

Ui-1 5э

H-H В-Э

и

U

k4

КЭ

k+

K9

K(

); ).

(4)

Этот ток вызьшает появление пропорционального ему напряжения на вто-,

рых выходах измерительньгх блоков, ко

торые подключены к входам аналого-цифровых преобразователей, на выходах которых появляется цифровой код,

-k + i T. соответствующий токам i и 1х j

)

13323АО6

который через цифровой коммутато поступает на вход цифрового вычислительного блока, при этом адресный вход цифрового коммутатора соединен с адресным выходом цифрового вычислительного блока, Вьшод напряжений

0

0

и U

kf 1

k3

K4I

И измерение токов If и

к %,

lC4-t

I осуществляется для каждого транзистора моделируемой электронной цепи, после чего получается новый вектор

t

. K4-I

ТОКОВ I для момента времени t, . Далее процесс вычислений по формулам

15 по формулам (1) - (А) продолжается для всего заданного интервала времени. Тактам образом, для моделирования цепей, содержащих только биполярные транзисторы и линейные элементы, уст0 ройство содержит два виешних регистра, два цифроаналоговых преобразователя и два аналого-цифровых преобразователя, кроме того, если в моделируемой цепи все транзисторы одного

5 типа, то устройство содержит один биполярный транзистор (полупроводниковый Прибор данного типа).

Для электронных цепей, содержащих различные полупроводниковые приборы

0 с произвольным количеством выводов, формулы () - (3), вычисляемые в цифровом вычислительном блоке, имеют тот же вид, только вектор токов 1 имеет большую размерность, Аналогич5 но система уравнений (4) имеет различную размерность для каждого типа полупроводниковых приборов.

Блок-схема алгоритма работы цифрового вычислительного блока показа0 на на фиг.З и состоит из следующих элементов.

Блок 1. Запись в оперативную память цифрового вычислительного блока 5 2 начальных условий в момент времени t| t .

Блок 2. Перезапись переменных для организации циклического вычислительного процесса с целью нахождения решения на интервале времени t t - Т с заданным шагом h.

Блок 3. Вьтисление значений производных напряжений на конденсаторах и токов через катушки индуктивностей в

t t.

момент времени

Блок 4. Вычисление значений,напряжений на конденсаторах и токов через катзшки индуктивностей в момент времени t tux, .

Блок 5. Вычисление значений напряжений на вьгаодах всех полупроводниковых приборов в момент времени t t .

Влок 6. Организация начала цикла вычисления токов через выводы каждого полупроводникового прибора в момент времени t t|, .

Блок 7 Задание адреса первого регистра 2 памяти.

Блок 8. Вывод цифрового кода Uji соответствующего напряжению на j-м вьюоде i-ro полупроводникового прибора, который поступает на входы регистров 2 с информационного выхода цифрового вычислительного блока 1. Одновременно с этим производится вывод адреса j одиого из внешних регистров 2, который поступает на вход дешифратора адреса регистра 11 с ад- ресиого выхода цифрового вычислительного блока 1.

Блок 9. Задание адреса следующего регистра 2 памяти.

Блок 10, Проверка условия пересчета всех вьгаодов полупроводникового прибора 8,

Блок 1I, Вывод цифрового кода, соответствующего адресу полупроводникового прибора 8 такого типа, который совпадает с типом i-ro полупроводникового прибора в моделируемой полупроводниковой цепи. Этот цифровой код поступает на вход регистра 3 адреса полупроводникового прибора с выхода цифрового вычислительного блока 1, Одновременно с этим проводится вывод адреса регистра 3 адреса полупроводникового прибора, который поступает на вход дешифратора адреса регистра 11 с адресного выхода цифро- .вого вычислительного блока 1.

Блок 12, Организация начала ввода цифровых кодов, соответствукмцих токам ijj , протекакицим через каждый вывод полупроводникового прибора 8 заданного типа при приложенном напряжении и ,

Блок 13, Ввод в оперативную память цифрового вычислительного блока 1 кода, соответствующего току , протекающему через j-й вьшод полупроводникового прибора 8 заданного типа при

,К+1

20

25

равляющий вход с адресного выхода ци рового вычислительного блока 1,

Блок 14, Задание номера следующег

с информационного входа цифрового коммутатора 10, соответствующего следую щему вьшоду полупроводникового прибо ра 8,

Блок 15. Проверка условия пересче

10 та всех выводов полупроводникового прибора.

Блок 16, Организация счетчика по- лупроводниковых приборов моделируемой цепи,

15 Блок 17, Проверка условия пересче та всех полупроводниковых приборов моделируемой цепи,

Блок 18, Организация цикла по вре мени.

Блок 19, Окончания цикла по времени.

Устройство работает следуюоцм образом ,

Цифровой вычислительный блок 1 формирует в соответствии с алгоритмом вектор напряжений, представленны в виде цифровых кодов, для всех полу проводниковых приборов, входящих в состав моделируемой цепи, для момент

30 времени t t, 1и{фровые коды, соответствующие напряжениям на выводах полупроводникового прибора определен ного типа, через информационный выхо цифрового вычислительного блока I

35 последовательно во времени поступают на информационные входы регистров 2, одновременно с этим на вход дешифратора адреса регистра II с адресного выхода цифрового вычислительного бло

40 ка 1 поступают коды, соответствукяцие адресам регистров 2, в которые необходимо поместить цифровые коды, со ответствукоше напряжениям на каждом выводе полупроводникового прибора 8

45 определенного типа. Запись информации в регистры 2 осуществляется толь ко при наличии сигнала на их управляющих входах, которые приходят с со ответствующих выходов дешифратора ад

50 реса регистра 11, Затем в регистр адреса полупроводникового прибора 3 аналогично записывается цифровой код соответствующими адресу полупроводникового прибора 8 определенного типа.

приложенном напряжении U, , Одновре- 55 с выходов регистров 2 цифровые коды, менно с этим производится вывод цифро Ього кода, соответствующего номеру информационного входа цифрового коммутатора 10, поступакщего на его упсоответствуюпще напряжениям на вьто- дах полупроводникового прибора 8 поступают на входы цифроанапоговых пре образователей 6, а цифровой код, со

20

25

равляющий вход с адресного выхода цифрового вычислительного блока 1,

Блок 14, Задание номера следующего

с информационного входа цифрового коммутатора 10, соответствующего следующему вьшоду полупроводникового прибора 8,

Блок 15. Проверка условия пересче10 та всех выводов полупроводникового прибора.

Блок 16, Организация счетчика по- лупроводниковых приборов моделируемой цепи,

15 Блок 17, Проверка условия пересчета всех полупроводниковых приборов моделируемой цепи,

Блок 18, Организация цикла по времени.

Блок 19, Окончания цикла по времени.

Устройство работает следуюоцм образом ,

Цифровой вычислительный блок 1 формирует в соответствии с алгоритмом вектор напряжений, представленный в виде цифровых кодов, для всех полупроводниковых приборов, входящих в состав моделируемой цепи, для момента

30 времени t t, 1и{фровые коды, соответствующие напряжениям на выводах полупроводникового прибора определенного типа, через информационный выход цифрового вычислительного блока I

35 последовательно во времени поступают на информационные входы регистров 2, одновременно с этим на вход дешифратора адреса регистра II с адресного выхода цифрового вычислительного бло40 ка 1 поступают коды, соответствукяцие адресам регистров 2, в которые необходимо поместить цифровые коды, со- ответствукоше напряжениям на каждом выводе полупроводникового прибора 8

45 определенного типа. Запись информации в регистры 2 осуществляется только при наличии сигнала на их управляющих входах, которые приходят с со- ответствующих выходов дешифратора ад50 реса регистра 11, Затем в регистр адреса полупроводникового прибора 3 аналогично записывается цифровой код, соответствующими адресу полупроводникового прибора 8 определенного типа.

55 с выходов регистров 2 цифровые коды, с выходов регистров 2 цифровые коды,

соответствуюпще напряжениям на вьто- дах полупроводникового прибора 8 поступают на входы цифроанапоговых преобразователей 6, а цифровой код, соответствующий адресу полупроводникового прибора 3 поступает на вход дешифратора адреса полупроводникового прибора 4, с выхода которого сигнал управления поступает на управляющие входы аналогового коммутатора 5. Циф- роаналоговые преобразователи 6 преоб- ра:зуют цифровые коды в соответствующие им напряжения и подают их на первые выводы аналогового коммутатора 5 через измерительные блоки 7« Напряжение на первом выходе измерительного блока 7 равно напряжению на его входе, так как дифференциальное напряжение операционного усилителя с гальванически развязанным питанием 12 близко к нулю. Аналоговый коммутаПредлагаемое устройство позволяет производить как логическое, так и

тор 5 в соответствии с сигналом управлешш подключает свои первые вьшо- 20 электрическое моделирование электрон- ды к выводам полупроводникового прибора 8 определенного типа, адрес которого был задан цифровым кодом. После этого через вьгаоды полупроводниковых цепей с применением полупроводниковых приборов, так как логическое моделирование является упрощением электрического моделирования. При

вого прибора 8 определенного типа на- 25 этом в кач.-;стве полупроводниковых чинает протекать ток, определяемьй как функция приложенных напряжений.

Гоки, протекающие через выводы поприборов используются цифровые микросхемы такого же типа, что и в моделируемой электронной цепи.

Таким образом, введенные в уст35

40

лупроводникового прибора 8, протекают зо ройство блоки и связи обеспечивают также с входов на первые выходы измерительных блоков 7. через измерительные регистры 14 и тем самым вызывают появление напряжений на выходах операционных усилителей с гальванически развязанным питанием 12, пропорциональных токам, протекающим через измерительные резисторы 14. Дифференциальные усилители 13 определяют разности напряжений между выходами операционных усилителей с гальванически развязанными питанием 12 и их общими шинами и подают их на входы аналого- цифровых преобразователей 9. Поступившие на входы аналогоцифровых преобразователей 9 напряжения, пропорциональные токам. протекаю1цим через выводы полупроводникового прибора 8, преобразуются в цифровые коды и поступают на входы цифрового коммутатора 10, на адресные входы которого поступают коды с адресного выхода цифрового вычислительного блока 1, в соответствии с которыми на вход цифрового вычислительного блока 1 последовательно во времени поступают цифровые коды с выходов -аналого-цифровых преобразователей 9. Таким образом происходит определение токов для

возможность электрического и времен ного моделирования электронных целе наряду с логическим моделированием,

Формула изобретени

Устройство для исследования элек рических цепей, содержащее цифровой вычислительный блок, дешифратор адреса исследуемого полупроводниковог прибора, цифровой коммутатор, выход которого соединен с информационным входом цифрового вычислительного бл ка аналоговый коммутатор, выходы к 45 торого являются входами подключения исследуемых полупроводниковых прибо ров, отличающееся тем, что, с целью расширения функциональ ных возможностей за счет обеспечени определения токов и напряжений в уз лах и полупроводниковых приборах электрической цепи в заданные момен ты времени, оно дополнительно содер жит регистры памяти, регистр адреса исследуемого полупроводникового при бора, дешифратор адреса регистров п мяти, цифроаналоговые преобразовате ли, аналого-цифровые преобразовател и измерительные блоки, каждый измер

50

55

всех полупроводниковых приборов 8 разного типа,, находящихся в различных местах моделируемой цепи дпя момента времени t. После этого с помощью цифрового вычислительного блока I производится вычисление вектора напряжений для момента времени tj, + h по формулам (1) - (3). Далее повторяется цикл определения токов для всех полупроводниковых приборов 8 для нового момента времени. Моделирование электронной цепи, т.е. вычисление токов и напряжений в узлах и элементах цепи, продолжается для всего заданного отрезка времени.

Предлагаемое устройство позволяет производить как логическое, так и

электрическое моделирование электрон-

вых цепей с применением полупроводниковых приборов, так как логическое моделирование является упрощением электрического моделирования. При

этом в кач.-;стве полупроводниковых

приборов используются цифровые микросхемы такого же типа, что и в моделируемой электронной цепи.

Таким образом, введенные в уст

ройство блоки и связи обеспечивают

возможность электрического и временного моделирования электронных целей наряду с логическим моделированием,

Формула изобретения

Устройство для исследования электрических цепей, содержащее цифровой вычислительный блок, дешифратор адреса исследуемого полупроводникового прибора, цифровой коммутатор, выход которого соединен с информационным входом цифрового вычислительного бло- ка аналоговый коммутатор, выходы ко- торого являются входами подключения исследуемых полупроводниковых приборов, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения определения токов и напряжений в узах и полупроводниковых приборах электрической цепи в заданные моменты времени, оно дополнительно содержит регистры памяти, регистр адреса сследуемого полупроводникового прибора, дешифратор адреса регистров паяти, цифроаналоговые преобразоватеи, аналого-цифровые преобразователи измерительные блоки, каждый измери

тельный блок содержит измерительный р.езистор, дифференциальный усилитель и операционный усилитель с гальванически развязанными питанием, шина пи которого соедииена с его неинвертирующим входом и с первым входом дифференциальиого усилителя, второй вход дифференциального усилителя соединен с Ьдним выводом измерительног резистора и с выходом операциоиного усилителя с гальванически развязанным питанием, иивертирунзщий вход которого соединен с другим вьшодом измерительного резистора, ииформацион- ныё входы регистра адреса исследуемого полупроводникового прибора и регистров памяти соединеиы соот- ветственио с информационными выходами цифрового вычислительного блока, адресный выход которого соедииеи с входом дешифратора адреса регистров памяти и с адресным входом цифрового коммутатора, выходы дешифратора адреса регистров памяти соединены соот- ветствеино с входами разрешения записи регистров памяти и регистра адре12

1

dDфи. 2

са исследуемого полупроводникового прибора, разрядные выходы которого соединены соответственно с входами дешифратора адреса исследуемого полупроводникового прибора, выходы которого подключены соответственно к управляющим входам аналогового коммутатора, разрядные выходы каждого регистра памяти подключены к входам соответствующего цифроаиалогового преобразователя, выход которого соединен с первым входом дифференциального усилителя соответствующего измерительного блока, инвертирующий вход операциоиного усилителя с гальванически развязанным питанием которого подключен к соответствующему информационному входу аналогового коммутатора, выход дифференциального усилителя измерительного блока подключен к информационному входу соответствующего аиалого - цифрового преобразовате - ля, выходы которых соединены соответственно с информационны - :ми входами цифрового коммутатора.

ГЗ

Г Иаиоио J

9.J--J

Редактор С.Патрушева

Составитель В.Фукалов

Техред В.Кадар КорректорМ. Демчик

Заказ 3835/46Тираж 672 Подписное

ВНИИГ1И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Да

Риг.5

С Стоп J

гг

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1977 |

|

SU631991A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для испытания радиоэлектронных приборов на помехоустойчивость | 1987 |

|

SU1422195A1 |

| Устройство для контроля параметров полупроводниковых приборов | 1978 |

|

SU781721A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство управления тепловой обработкой бетона | 1985 |

|

SU1312525A1 |

| Аналого-цифровое вычислительное устройство | 1986 |

|

SU1388913A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

Изобретение относится к вычислительной технике и предназначено для моделирования электрических цепей. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности определения токов и напряжений в узлах и полупроводниковых приборах э.|1ектрической цепи в заданные моменты времени. Устройство содержит цифровой вьтчислительной блок 1, регистры 2 памяти, регистр 3 адреса исследуемого полупроводникового прибора, дешифратор 4 адреса исследуемого полупроводникового прибора, аналоговый .коммут атор 5, цифроаналоговые преобразователи 6, измерительные блоки 7, аналого-цифровые преобразователи 9, цифровой коммутатор 10, дешифратор 1I адреса регистров памяти, а также исследуемые полупроводниковые приборы 8. 4 ил. f i (Л с: 00 со to со 4

Авторы

Даты

1987-08-23—Публикация

1985-07-01—Подача