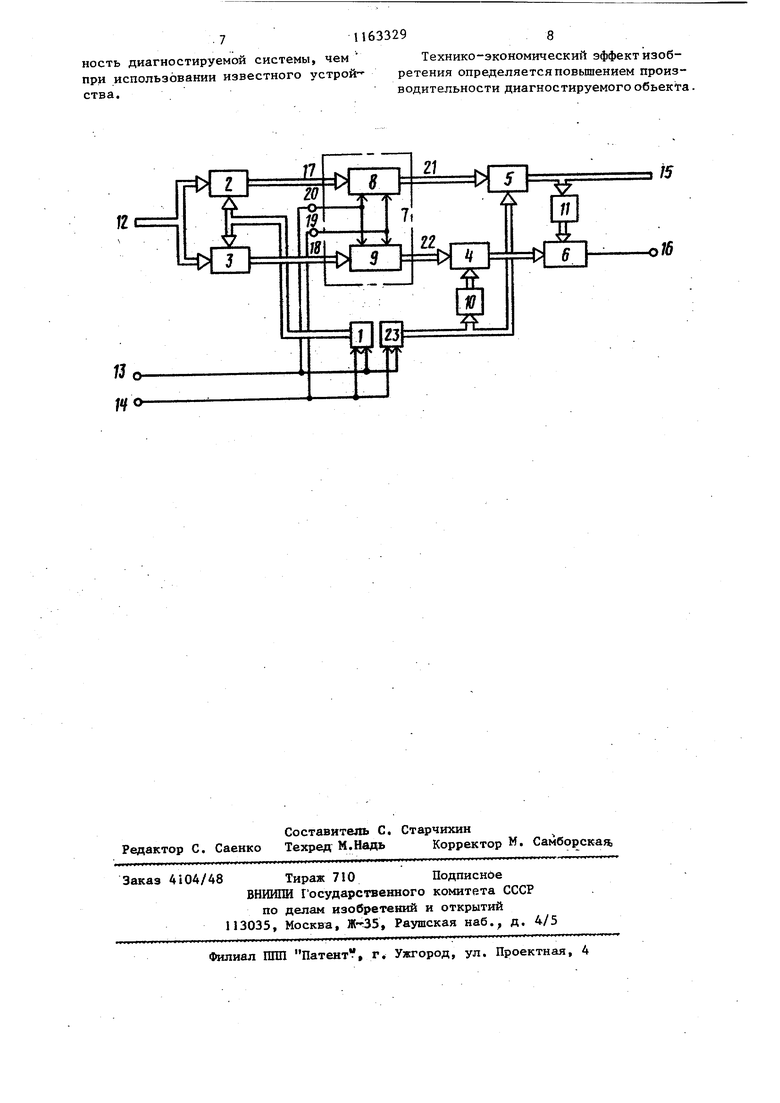

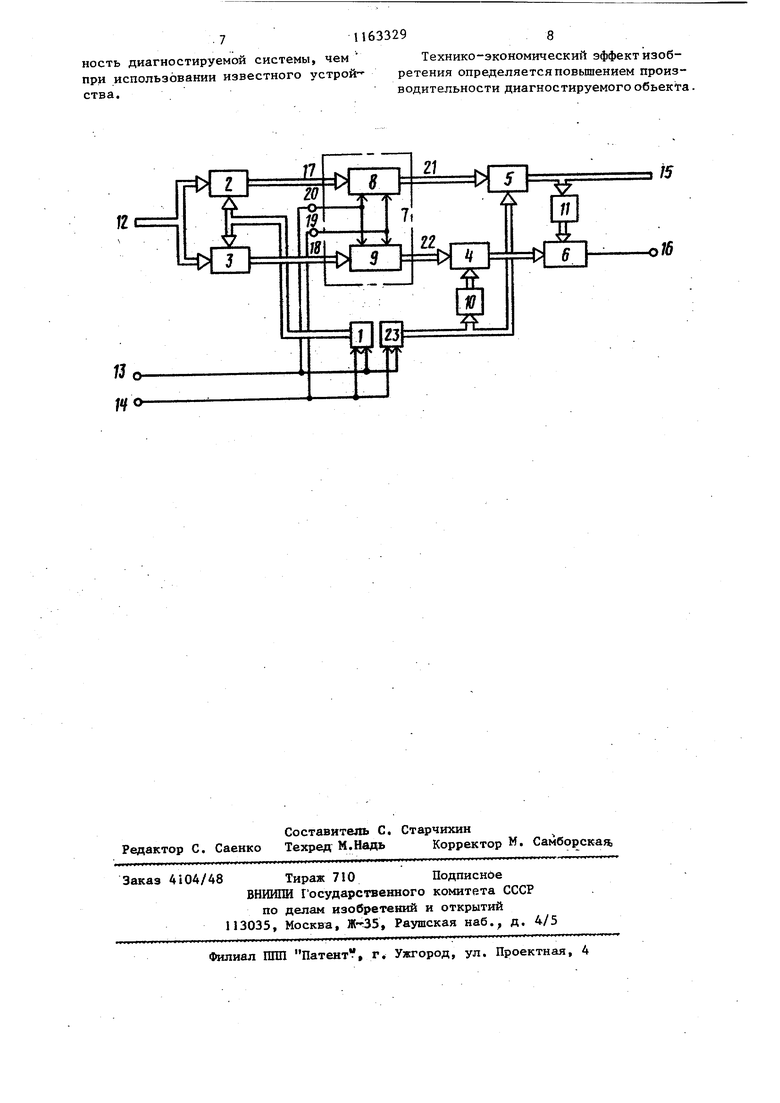

Изобретение относится к вычислительной технике. Известны устройства тестового диа ностирования, содержащие генератор тестовых воздействий, блок эталонов и блок сравнения. Испытательные сиг налы с выхода генератора тестовых воздействий поступают на вход диаг ностируемого устройства, а сигналы эталонных реакций - на блок сравнени где устанавливается идентичность или различие их с фактическими реакциями диагностируемого устройства Cl Недостатками таких устройств яв ляются необходимость наличия пере-рывов в работе диагностируемого устройства и невозможность диагностиро вания вiрабочем режиме. Для диагностирования в рабочем режиме используются устройства функционального диагностирования, состо-ящие из основного устройства, вспомо гательного устройства и решающего органа, вырабатываняцего сигнал ошибк при несоответствии выходных векторов основного и вспомогательного устройств, имеющем место в случае возни новения дефектов из заданного класса В большинстве случаев вспомогательно устройство является более-простым (п аппаратурным затратам) по сравнению с основным (диагностируемым) устрой ством и лишь в иекоторых (неблагопри ятных) частных случаев является дублем основного D J. ,Недостаток устройств функдиональ ного диагностирования заключается в необнаружении таких дефектов в такте их возникновения, которые не приводят к искажению выходного вектора в данном такте. В результате может произойти накопление своевременно не обнаруженных дефектов, обнаруживающая способность устройства функционального диагностирования будет превьшена, и искажение выходного сигнала основного устройства обнаружено не будет. Наиболее близким по технической супщости к изобретению является устройство непрсрьшиого тестового диагностирования линейных динамических систем, позволяющее повысить точность диагност,9рования линейных систем по сравнению с устройствами функционального диагностирования и исключить перерывы в работе объекта диагностирования характерные для стройств тестового диагностирования, и содержащее генератор тестовых воздействий и эталонных реакций, блок сравнения, сумматоры, блоки вычитания, блоки умножения на Z, объект диагностирования, состоящий из двух идентичных линейных систем, информационный, синхронизирующий и установочный входы устройства, информационные выходы и входы для подключения диагностируемых ,систем, выход реакции устройства на входные воздействия и выход сигнала ошибки устройства 2J. Основными недостатками прототипа являются следуклцие. Однако известное устройство непригодно для непрерывного тестового диагностирования линейных в поле вычетов по модулю два цифровых систем из-за отсутствия разницы между суммированием и вычитанием в этом поле. Кроме того, для осуществления непрерывного тестового диагностирования требуется наличие у объекта диагностирования значительной аппаратурной избыточности (непрерывному тестовому диагностированию подлежат лишь дублированные системы). Введение большой избыточности 18 исходную линейную цифровую систему с целью обеспечения ее непрерывного тестового диагностирования приводит к значительному снижению ее надежности. Цель изобретения - повьш1ение точности непрерывного диагностирования с одновременным расширением функциональных возможностей устройства путем обеспечения диагностирования цифровых систем, линейных в поле вычетов по модулю два, а также систем, обладающих избыточностью меньшей, чем дублированные системы. Поставленная цель достигается тем, что в устройство непрерывного тестового диагностирования линейных циф ровых систем, содержащее генератор тестовых воздействий, блок хранения эталонных реакций, первый и второй блоки суммирования, первый и второй блоки вычитания и блок сравнения, причем первый и второй информационные входы первого блока суммирования и первого блока вычитания соединены соответственно с информационным входом устройства и выходом генератора тестовых воздействий, а их выходы - соответственно с первым и вторым ин- формационными входами диагностируемых систем, синхронизирующий и устаковочный входы устройства соединены с соответствующими входами диагностируемых систем, генератора тестовых воздействий и блока хранения эталонных реакций, первые информационные входы второго блока вычитания и вто рого блока суммирования соединены с соответствующими выходами диагностируемых систем, выход блока сравнения является выходом сигнала ошибки устройства, введены первый и второй фор мирователи контрольных разрядов, при чем вход первого формирователя контрольных разрядов соединен с вторым информационным входом второго блока вычитания и с выходом блока хранения эталонных реакций, выход первого фор мирователя контрольных разрядов соединен с вторым информационным входом второго блока суммирования, выход которого подключен к первому входу блока сравнения, второй вход которого соединен с выходом второго формирователя контрольных разрядов, выход второго блока вычитания соединен с входом второго формирователя контрол ных разрядов и является выходом реак ций на входные воздействия устройства. На чертеже изображено предлагаемо устройство. Устройство содержит генератор 1 тестовых воздействий, первый суммато 2, первый блок 3 вычитания, второй сумматор 4, второй блок 5 вычитания, блок 6 сравнения, объект 7 диагности рования, состоящий из основной 8 и вспомогательной 9 линейных цифровых систем, первый 10 и второй 11 формирователи контрольных разрядов, инфор мационный 12, синхронизирующий 13 и установочный 14 входы, выход 15 реак ции устройства на входные воздействи выход 16 сигнала ощибки устройства, информационные входы 17 и 18 основной и вспомогательной линейных цифро вых систем соответственно, синхронизирующий 19 и установочный 20 входы диагностируемых систем, информационные выходы 21 и 22 диагностируемых систем, блок 23 хранения эталонных реакций. Формирователи 10 и 11 контрольных разрядов - это формирователи избыточных разрядов линейных разделимых кодов с обнаружением ошибок заданной кратности, они идентичны. каждый из них может быть реализован на i комбинационных сумматорах по заданному модулю, где I - размерность ( число компонент )выходного вектора вспомогательной цифровой системы 9. Если в векторе выхода основной цифровой системы 8 требуется обнаружение однократной ошибки, то 1, формирователь 10 (П) контрольных разрядов - комбинационный сумматор с числом входов, равным размерности .выходного вектора основной цифровой системы 8. Блоки 2, 4 и 3, 5 являются асинхронными безынерционными устройствами покомпонентного суммирования (2, 4) и вычитания (3, 5) по заданному модулю. Такие блоки для цифровых систем могут быть реализованы на комбинационных сумматорах, работающих в прямом и дополнительном кодах. Устройство работает следующим образом. В начальный момент времени на вход 14 устройства подается сигнал начальной установки, который, поступая на установочные входы генератора 1 тестовых воздействий, блока 23 хранения эталонных реакций,на вход 19 диагностируемых систем, осуществляет начальную установку генератора 1 тестовых воздействий, блока 23 хранения эталонных реакций основной 8 и вспомогательной 9 цифровых систем так, что вьтолняется равенство у(0) Ну(О) , где у (О) и у.(0) - значения векторов выхода основной В и вспомо гательной 9 цифровых систем соответственно в начальный момент времени;, : Н - матрица, определяющая закон формирования избыточных разрядов. В процессе обработки информации системами 8 и 9 входной сигнал с входа 1 2 и тестовый сигнал с выхода генератора 1 тестовых воздействий, покомпонентно складываясь в сумматоре 2, поступают на информационный вход 17 линейной цифровой системы 8, где они обрабатьшаются в соответствии с функцией этой системы. Одновременно на информационный вход 18 динамической системы-9 поступает покомпонентная разность входного и тестового сигналов, образующаяся на выходе вычитающего блока 3. Выходной сигнал с информационного выхода 22 динами ческой системы 9 покомпонентно складывается в блоке 4 с преобразованной с помощью блока IО эталонной реакци ей блока 23, и суммарньй сигнал с выхода блока 4 поступает на первый вход блока 6 сравнения. Эталонная реакция, поступающая с выхода блока 23, покомпонентно вычитается в блоке 5 из выходного, с информацион кого выхода 21, сигнала системы 8, в результате чего на выходе блока 5 выделяется сигнал реакции системы на входное воздействие, Этот сигнал ре акции поступает на выход 15 устройства, а также на вход блока 11, вы ход которого связан с вторым входом блока 6 сравнения. Сигнал с выхода блока сравнения, являющийся сигналом ошибки, поступает на выход 16 устройства. Синхронность работы блоков 1, 8, 9 и 23 обеспечивается путем сигнала синхронизации с входа 13 устройства на синхровходы генератора 1 тестовых воздействий, блока 23 и на вход 20 диагностируемых систем. Пусть входной сигнал устройства X, тестовый t, функции передачи основной системы L, дополнительной L эталонная реакция на выходе генератора 1 равна L(t), Н - матрица, описы вающая закон формирования избыточных разрядов линейного разделимого кода с обнаружением ошибок заданной крат-ности. Тогда ЬгСх) HL(х) при отсутствии ошибок в выходном сигнале основной системы и LjCx) i HL(x) при наличии ошибок кратности, не прё вьшающей заданную в выходном векторе основной системы, где L - функция передачи основной системы при нали чии в ней дефекта. При отсутствии дефектов сигналы на входах блоков 8 и 9 равны (х + t) и (х - t), а на их выходах - соответственно L(х + t и - t). Последние сигналы по- даются на входы блоков 5 и 4, поэтому сигнал на выходе каждого из блоко вследствие линейности L и L, равен соответственно -L(х + t) - L(t) Ц(х) и - t) 4- HL(t) Ljx+ L(t) L (x). Сигналы, поступающи на вход блока 6 сравнения, соответственно равны ) и HL(x) L j(x) в результате чего сигнал на выходе блока сравнения равен нулю. При появ лении дефектов в линейной динамической системе 8 или 9 выход системы 8 не равен L(х + t) либо выход системы 9 не равен L Сх - t), поэтому сигнал на выходе блока 4 не равен Lj. (х) либо на выходе блока 5 не равен L-(x) икак следствие, на выходе блока I 1 не равен L-Cx) и, далее, за счет неравенства выходных сигналов блоков 4 и 11 на выходе блока 6 появляется сигнал ошибки. Обнаруживаются и те дефекты, которые не приводят к искажению L(х) или L(х), так как значение L (t) или L,j(t) хотя бы на одном из тестовых воздействий искажается (условие полноты теста), что приводит к неравенству сигналов на входе блока сравнения и, как следствие, к появлению сигнала ошибки. Дефекты в одном из блоков 2, 3, 4, 5, 10 и 11, приводящие к изменению их передаточной функции, непосредственно приводят к искажению сигналов на одном из входов блока 6 сравнения, в результате чего на его выходе появляется сигнал ошибки. Предлагаемое устройство в отличие от известного пригодно и для непрерывного тестового диагностирования линейных в поле вычетов по модулю два цифровых систем, при этом блоки 2-5 будут блоками покомпонентного суммирования по модулю два (операции суммирования и вычитания в поле вычетов по модулю два совпадают ),Таким образом, использование предлагаемого устройства позволяет повысить.точность непрерывного диагностирования (по сравнению с устройствами функционального диагностирования) линейных в поле вычетов по модулю два цифровых систем. Очевидно, что линейные цифровые системы 8 и 9 могут различаться (система 9 в смысле аппаратур- . ных затрат не сложнее системы 8 ), достаточно только чтобы их передаточные функции бьши связаны соотношением ) HL (х). В частном случае, когда закон функционирования избыточных разрядов Н задается единичной матрицей, вспомогательная линеГшая цифровая система 9 является дублем основной системы 8. Таким образом, в общем случае для осуществления непрерьшного тестового диагностирования с помощью предлагаемого устройства требуется меньшая избыточ.711633298

ность диагностируемой системы, чем Технико-экономический эффектизобпри использовании известного устрой ретения определяется повышением произства.водительности диагностируемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для непрерывного диагностирования линейных динамических систем | 1988 |

|

SU1624454A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Устройство непрерывного тестового диагностирования линейных динамических систем | 1981 |

|

SU983710A1 |

| Устройство для диагностирования логических узлов | 1979 |

|

SU892447A1 |

| Устройство для диагностирования цифровых систем | 1980 |

|

SU955075A1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ НЕИСПРАВНОСТЕЙ ДИНАМИЧЕСКИХ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2084945C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 2009 |

|

RU2430406C2 |

| СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1997 |

|

RU2127447C1 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

| Устройство для диагностики цифровых блоков | 1988 |

|

SU1674129A1 |

УСТРОЙСТВО НЕПРЕРЫВНОГО ТЕСТОВОГО ДИАГНОСТИРОВАНИЯ ЛИНЕЙНЫХ ЦИФРОВЫХ СИСТЕМ, содержащее генера-тор тестовых воздействий, блок хра нения эталонных реакций, первый и второй блоки суммирования, первый и второй блоки вычитания и блок срав нения, причем первый и второй инфор мационные входы первого блока суммирования и первого б:лока вычитания соединены соответственно с информационным входом устройства и выходом генератора тестовых воздействий, а их выходы соответственно с первым и вторым информационными входами т диагностируемых систем, синхронизирующий и установочный входы устройства соединены с соответствующими входами г.иагностируемых систем, генератора тестовых воздействий и блока хранения эталонных реакций, первые информационные входы второго блока вычитания и второго блока суммирования соединены с соответствующими выходами диагностируемых систем, выход блока сравнения является выходом сигнала ошибки устройства, о тличающееся тем, что, с целью повьшения точности непрерывного диагностирования, в него вв.дены первый и второй формирователи контрольных разрядов, причем вход первого формирователя контрольных разрядов соединен с вторым информационО) ным входом второго блока вычитания и с выходом блока хранения эталонных реакций, выход первого формирователя контрольных разрядов соединен с вторым информационным входом .второго блока суммирования, выход которого подключен к первому входу Од блока сравнения, второй вход котоО9 СО рого соединен с выходом второго формирователя контрольных разрядов, ьэ вькод второго блока вычитания соесо динен с входом второго фop шpoвaтeля контрольных разрядов и является выходом реакций на входные воздействия устройства.

W

щоZf

Авторы

Даты

1985-06-23—Публикация

1983-07-25—Подача