Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах диагностирования цифровых логических схем.

Цель изобретения - уменьшение времени локализации неисправности.

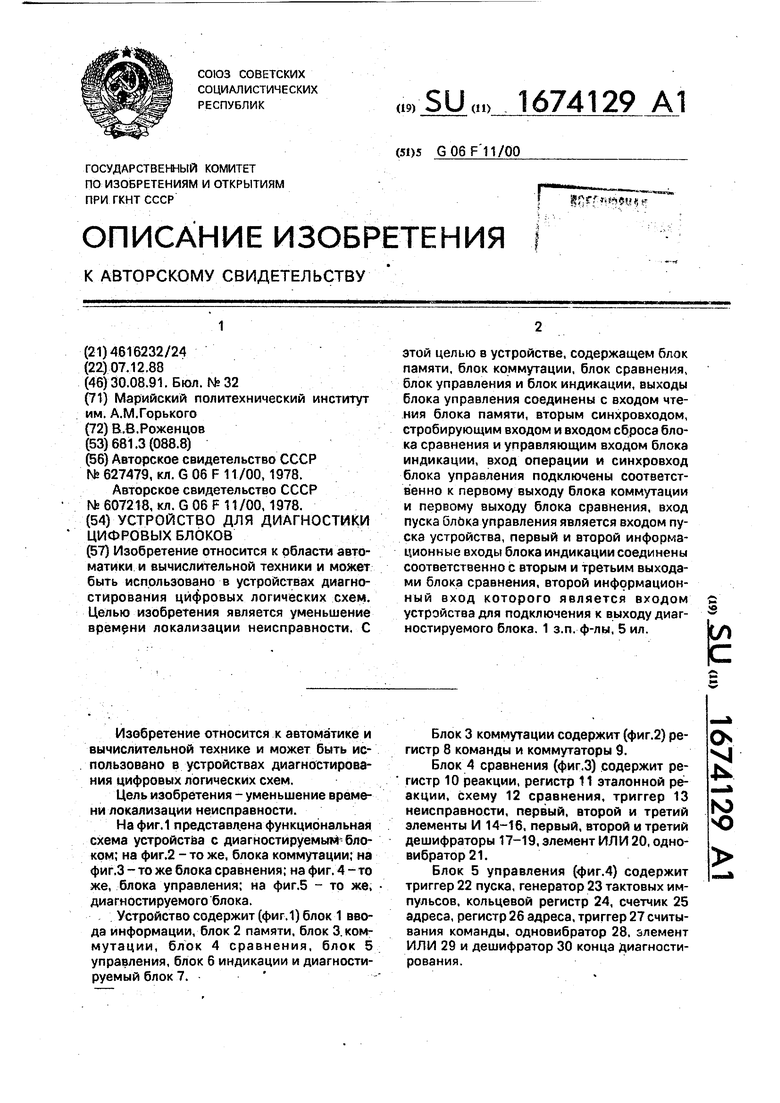

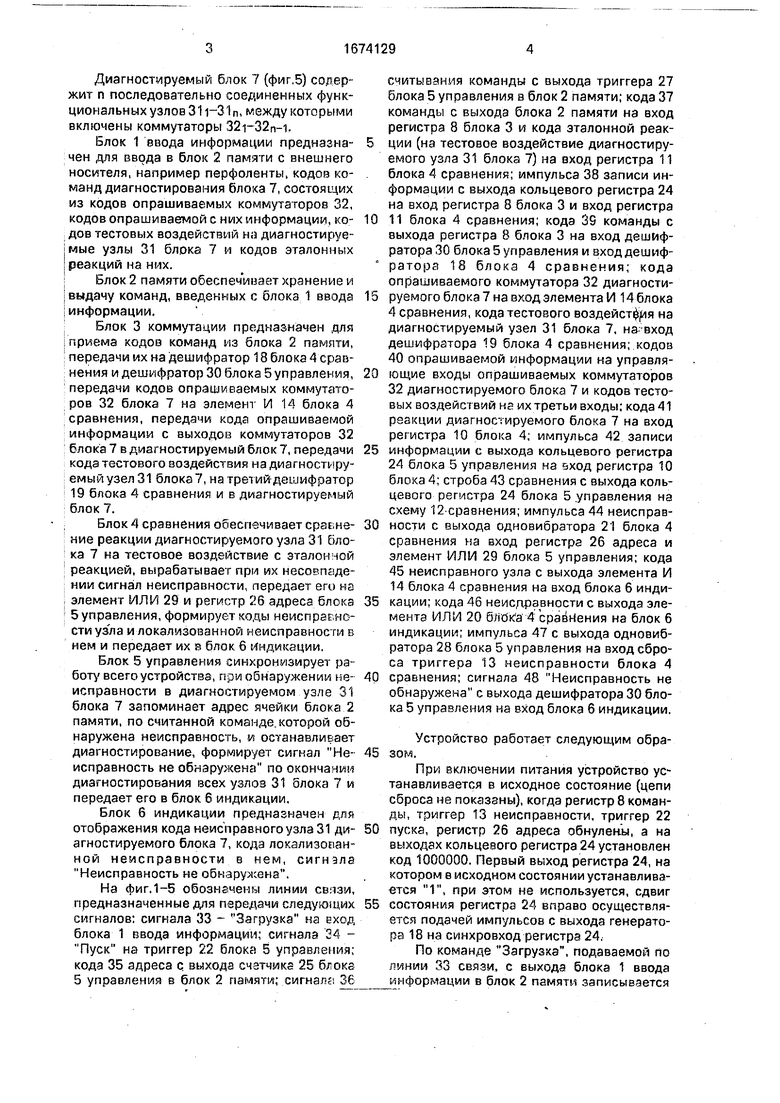

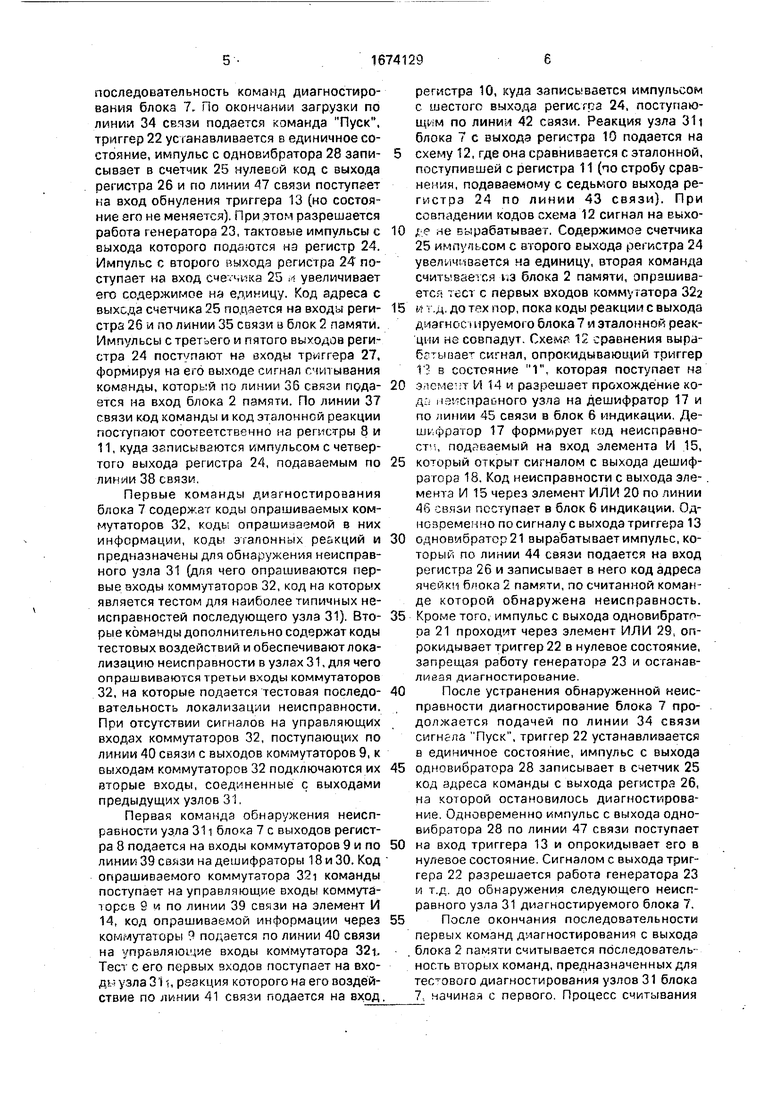

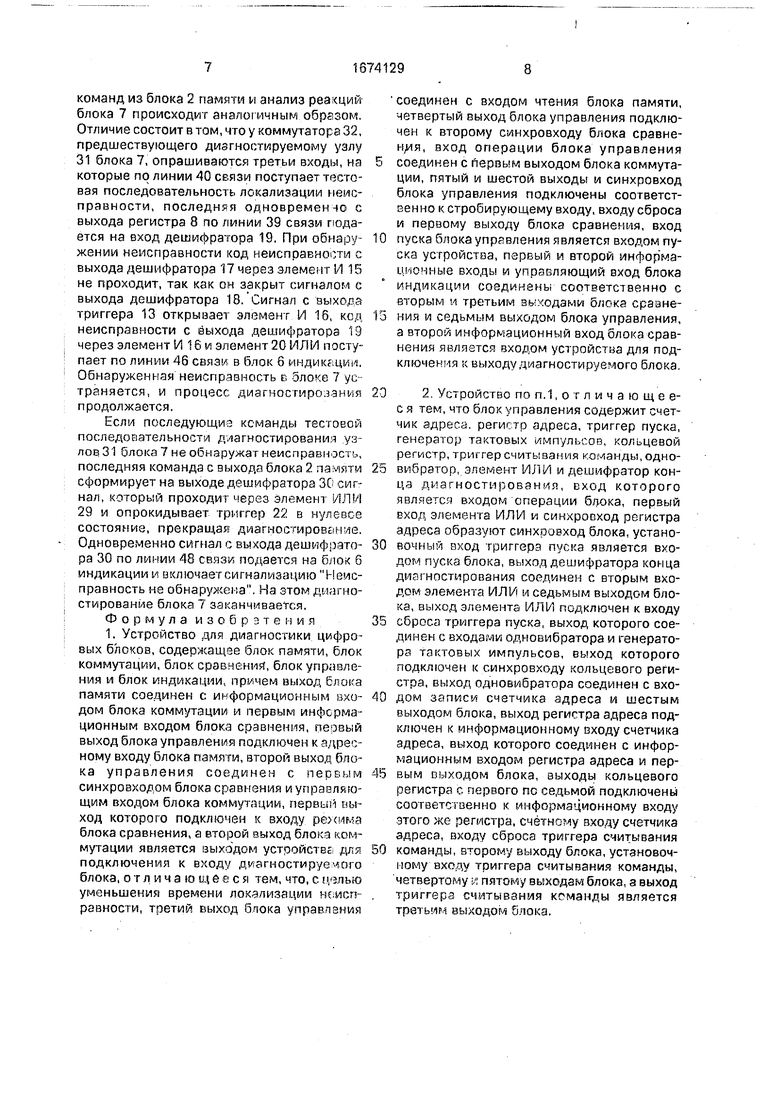

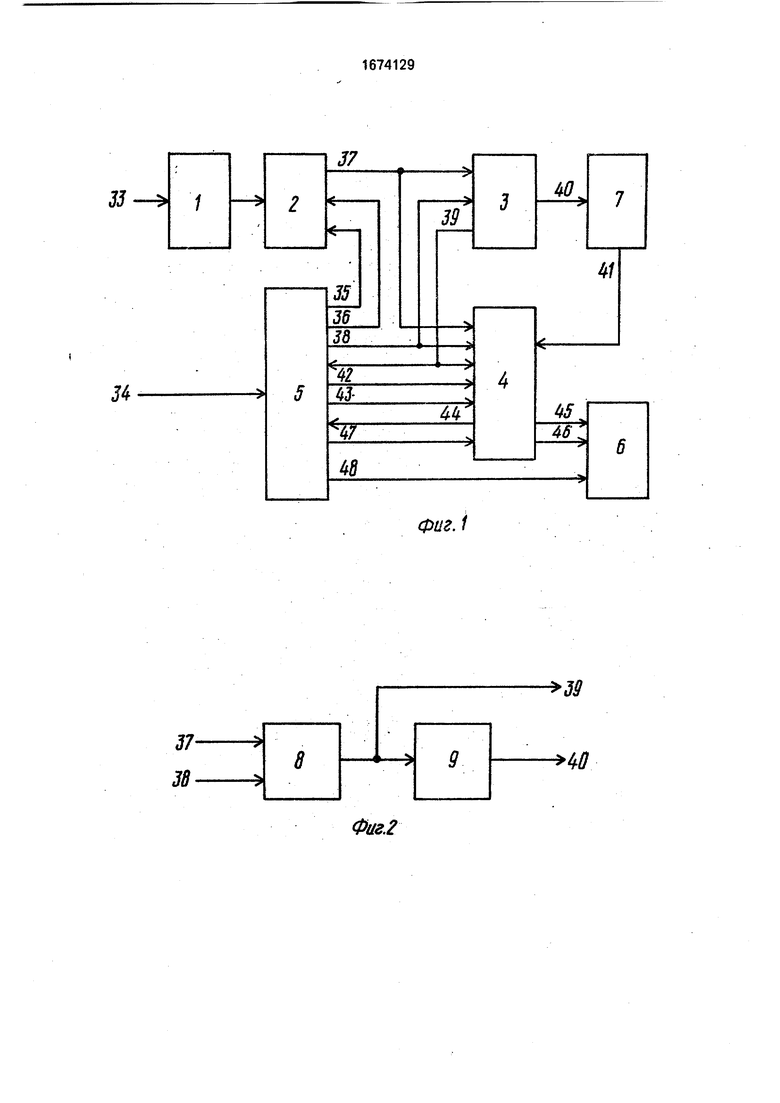

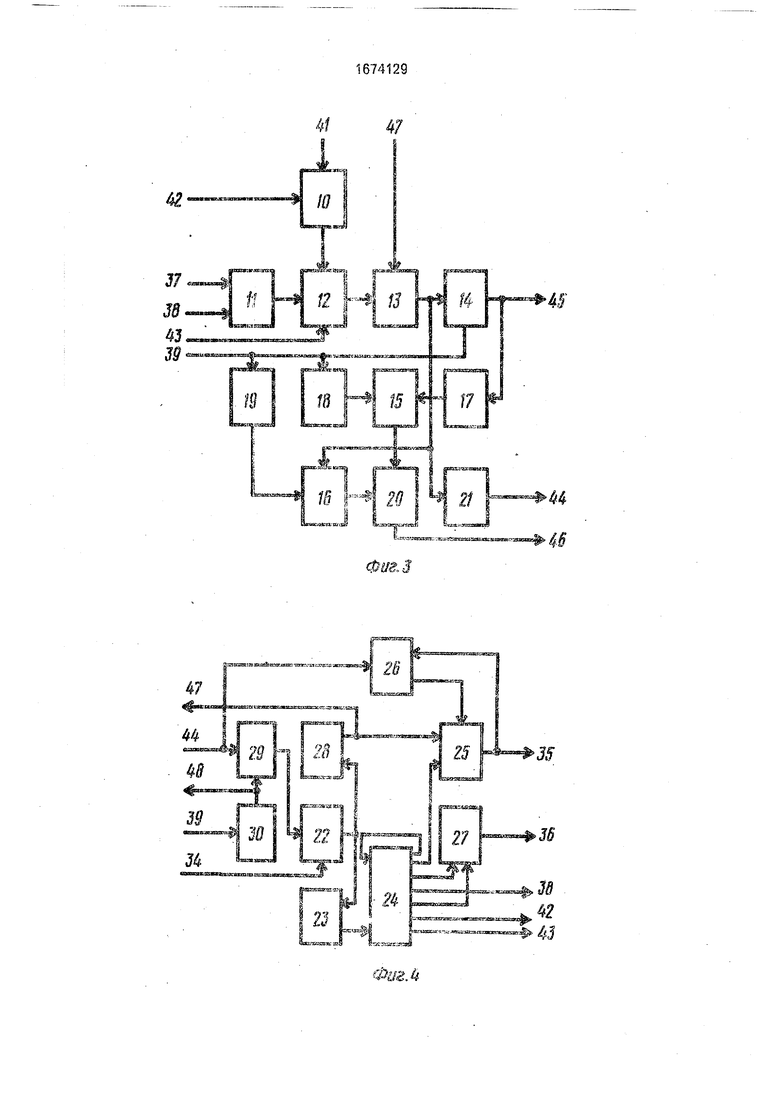

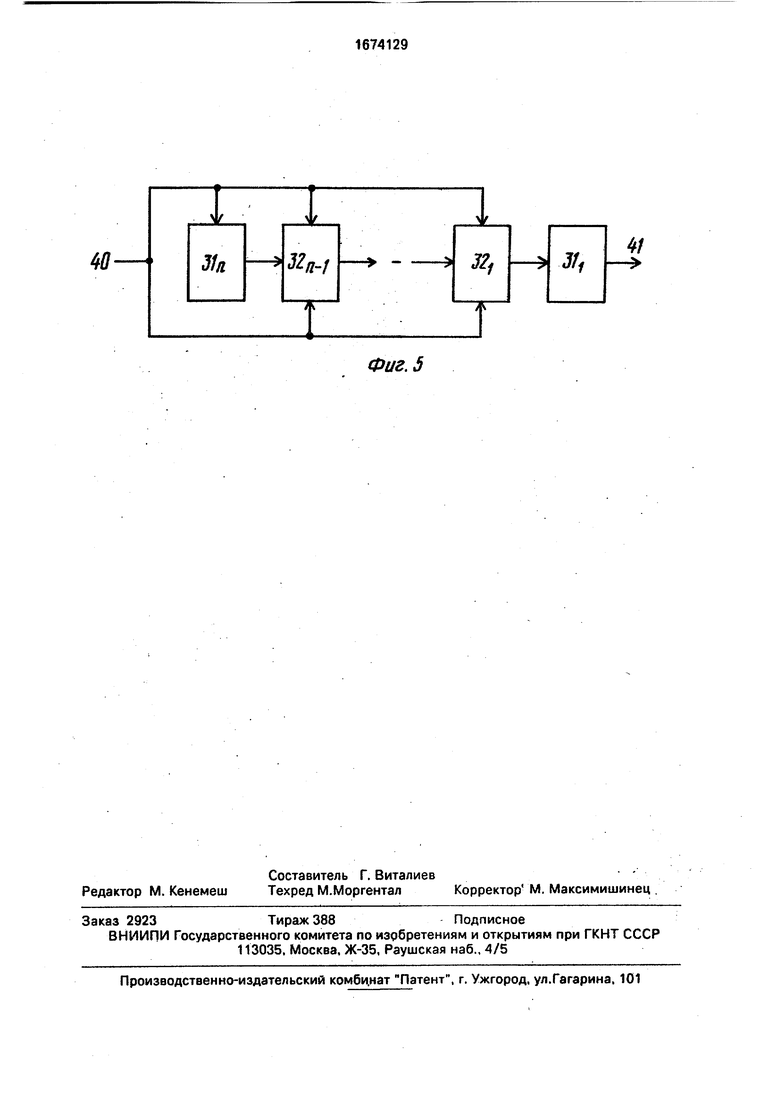

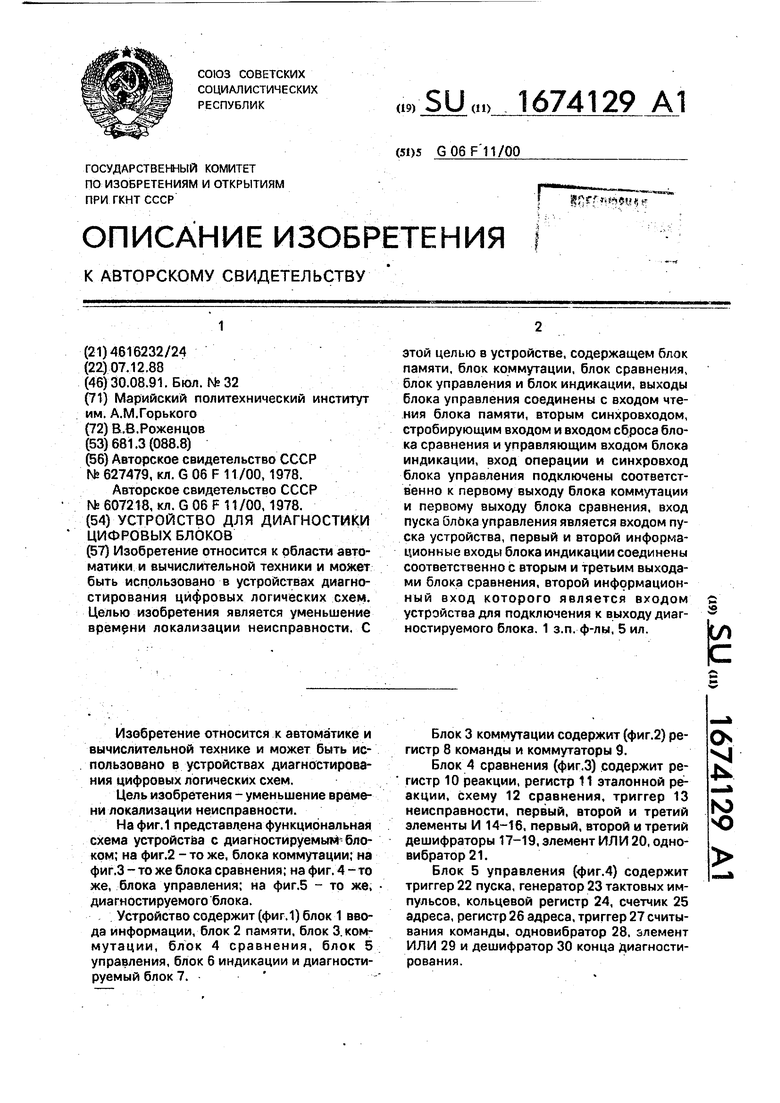

На фиг, 1 представлена функциональная схема устройства с диагностируемым блоком; на фиг.2 - то же, блока коммутации; на фиг.З - то же блока сравнения; на фиг. 4 - то же, блока управления; на фиг.5 - то же, диагностируемого блока.

Устройство содержит (фиг. 1) блок 1 ввода информации, блок 2 памяти, блок 3 коммутации, блок 4 сравнения, блок 5 управления, блок 6 индикации и диагностируемый блок 7.

Блок 3 коммутации содержит (фиг.2) регистр 8 команды и коммутаторы 9.

Блок 4 сравнения (фиг.З) содержит регистр 10 реакции, регистр 11 эталонной реакции, схему 12 сравнения, триггер 13 неисправности, первый, второй и третий элементы И 14-16, первый, второй и третий дешифраторы 17-19, элемент ИЛИ 20, одно- вибратор 21.

Блок 5 управления (фиг.4) содержит триггер 22 пуска, генератор 23 тактовых импульсов, кольцевой регистр 24, счетчик 25 адреса, регистр 26 адреса, триггер 27 считывания команды, одновибратор 28, элемент ИЛИ 29 и дешифратор 30 конца диагностирования.

2

Ю

ю

Диагностируемый блок 7 (фиг,5) содержит п последовательно соединенных функциональных узлов , между которыми включены коммутаторы 32i-32n-i.

Блок 1 ввода информации предназначен для ввода в блок 2 памяти с внешнего носителя, например перфоленты, кодов команд диагностирования блока 7, состоящих из кодов опрашиваемых коммутаторов 32, кодов опрашиваемой с них информации, кодов тестовых воздействий на диагностируемые узлы 31 блока 7 и кодов эталонных реакций на них.

Блок 2 памяти обеспечивает хранение и выдачу команд, введенных с блока 1 ввода информации.

Блок 3 коммутации предназначен для приема кодов команд из блока 2 памяти, передачи их на дешифратор 18 блока Л сравнения и дешифратор 30 блока 5 управления, передачи кодов опрашиваемых коммутаторов 32 блока 7 на элемент И 14 блока 4 сравнения, передачи кода опрашиваемой информации с выходов коммутаторов 32 блока 7 в диагностируемый блок 7, передачи кода тестового воздействия на диагностируемый узел 31 блока7, натретийдешифратор 19 блока 4 сравнения и в диагностируемый блок 7.

Блок 4 сравнения обеспечивает сравнение реакции диагностируемого узла 31 блока 7 на тестовое воздействие с эталонной реакцией, вырабатывает при их несовпадении сигнал неисправности, передает его на элемент ИЛИ 29 и регистр 26 адреса блока 5 управления, формирует коды неисправности узла и локализованной неисправности в нем и передает их в блок 6 индикации.

Блок 5 управления синхронизирует работу всего устройства, при обнаружении неисправности в диагностируемом узле 31 блока 7 запоминает адрес ячейки блока 2 памяти, по считанной команде которой обнаружена неисправность, и останавливает диагностирование, формирует сигнал Неисправность не обнаружена по окончании диагностирования всех узлов 31 блока 7 и передает его в блок 6 индикации.

Блок 6 индикации предназначен для отображения кода неисправного узла 31 диагностируемого блока 7, кода локализованной неисправности в нем, сигнала Неисправность не обнаружена.

На фиг.1-5 обозначены линии связи, предназначенные для передачи следующих сигналов: сигнала 33 - Загрузка на вход блока 1 ввода информации; сигнала 34 - Пуск на триггер 22 блока 5 управления; кода 35 адреса с выхода счетчика 25 блока 5 управления в блок 2 памяти; сигнала 36

считывания команды с выхода триггера 27 блока 5 управления в блок 2 памяти; кода 37 команды с выхода блока 2 памяти на вход регистра 8 блока 3 и кода эталонной реакции (на тестовое воздействие диагностируемого узла 31 блока 7) на вход регистра 11 блока 4 сравнения; импульса 38 записи информации с выхода кольцевого регистра 24 на вход регистра 8 блока 3 и вход регистра

11 блока 4 сравнения; кода 39 команды с выхода регистра 8 блока 3 на вход дешифратора 30 блока 5 управления и вход дешиф- ратора 18 блока 4 сравнения; кода опрашиваемого коммутатора 32 диагностируемого блока 7 на вход элемента И 14 блока 4 сравнения, кода тестового воздействия на диагностируемый узел 31 блока 7, на вход дешифратора 19 блока 4 сравнения; кодов 40 опрашиваемой информации на управляющие входы опрашиваемых коммутаторов 32 диагностируемого блока 7 и кодов тестовых воздействий н их третьи входы: кода 41 реакции диагностируемого блока 7 на вход регистра 10 блока 4; импульса 42 записи

информации с выхода кольцевого регистра 24 блока 5 управления на ьход регистра 10 блока 4; строба 43 сравнения с выхода кольцевого регистра 24 блока 5 управления на схему 12 сравнения; импульса 44 неисправности с выхода одновибратора 21 блока 4 сравнения на вход регистра 26 адреса и элемент ИЛИ 29 блока 5 управления; кода 45 неисправного узла с выхода элемента И 14 блока 4 сравнения на вход блока 6 индикации; кода 46 неисправности с выхода элемента ИЛИ 20 4 сравнения на блок 6 индикации; импульса 47 с выхода одновибратора 28 блока 5 управления на вход сброса триггера 13 неисправности блока 4

сравнения; сигнала 48 Неисправность не обнаружена с выхода дешифратора 30 блока 5 управления на вход блока 6 индикации.

Устройство работает следующим обра5 зом.

При включении питания устройство устанавливается в исходное состояние (цепи сброса не показаны), когда регистре команды, триггер 13 неисправности, триггер 22

0 пуска, регистр 26 адреса обнулены, а на выходах кольцевого регистра 24 установлен код 1000000. Первый выход регистра 24, на котором в исходном состоянии устанавливается Г, при этом не используется, сдвиг

5 состояния регистра 24 вправо осуществляется подачей импульсов с выхода генератора 18 на синхровход регистра 24.

По команде Загрузка, подаваемой по линии связи, с выхода блока 1 ввода информации в блок 2 памяти записывается

последоьательность команд диагностирования блока 7. По окончании загрузки по линии 34 скпзи подается г-оманда Пуск, триггер 22 уС|анавливяется в единичное состояние, импульс с одновибратора 28 записывает в счетчик 25 нулевой код с выхода регистра 26 и по линии 47 связи поступгет ка вход обнуления триггера 13 (но состой мне его не меняется). При этом разрешается работа генератора 23, тактовые ИМПУЛЬСЫ . выхода которого пидо-отся на регистр 2 }. Импульс с второго аыход-3 регисфа 24 поступает на вход сче..ркг 25 . увеличивает его содержимое на единицу. Код адреса с выхс/да счетчика 25 попчется на вход я регистра 26 и по линии 35 связи j блок 2 памяти. Импульсы с третьего и пятого вь-ходои реги стра 24 пост -лают на входы 27, формируя на его выходе сигнал г итыпания команды, котпргй по линии 36 м..да- чтгя на вход блока 2 памяти. По линии 3 1 гвязи код команды и код эталонной реакции гюсгупчют соответственно на реиттры 3 и 11, куда записываются имп/льгом с четвертого выхода регистра 24, подаваемым по лтми 38 с вязи.

Первые команды дизгностиропания б/,ока 7 содержит коды опрашиваемых коммутаторов 32, кидь опрашиваемой в них инфсфмации. коци j. anoHH ix реакции и предназначены для обна ухения сеисправ- ного узла 31 ( чего опрашиваются и ер- вые плоды коммутаторов 32, код на которых является тестов для наиболее типичиы HG- ислравностей последующего узла З1) Вто рне команды дополнительно содержат коды тестовых воздействий и обеспечивают локализацию неисправности в узлах 31,для чего опрашвивэклся т рртьи воды коммутаторов 32, на которые подается тестовая последовательность локализации неисправности. При отсутствии сигналов на управляющих входах коммутаторов 32, поступающих по линии 40 снязи с выходов коммутаторов 9, к выходам коммутаторов 32 подключаются их вторые входы, соединенные с выходами предыдущих узлов 3 I.

Первая команда обнаружения неисл Ј,аьносги узла 3 11 блгха 7 с выходов регистра 3 подается на входы коммутаторов 9 и по линии 39 св;гзи на дешифраторы 18 и 30. Код опрашиваемого коммутатора команды поступает на управляющие входы коммута- орсп 9 ч по линии 39 свчзи на элемент И 1-1, код опрашиваемой информации через коммутаторы ° по,,;п.тся по линии 40 связи на прльлякгч1 ИР входы коммутатора 32т. Teir г его первых чходов поступает на вхо- ,ц злаЗ) ,реакция которого на егопоздей- ствие по линии 41 связи подается на вход.

регистра 10, куда записывается импульсом с шестого выхода регисгса 24, поступающем по линии 42 связи. Реакция узла 311 блока 7 с выхода регистра 10 подается на 5 схему 12, где она сравнивается с эталонной, поступившей с регистра 11 (по стробу сравнения, подаваемому с седьмого выхода регистра 24 по линии 43 связи). При совпадении кодов схема 12 сигнал на еыхо0 } не вырабатывав с. Содержимое счетчика 25 импульсом с второго выхода регистра 24 увеличивается на единицу, вторая команда считывается i-з блока 2 памяти, опрашивается тест с первых входов коммутатора 322

5 / д. до пор, пока коды реакции с выхода диэгнос ируемо о блока 7 и эталонной реакции не совпадут. Схемг ь; сравнения выра- сигнал, опрокидывающий триггер ij в состояние I. которая поступает на

° ч оме .т И 14 и разрешает прохождение ко- д ионспрайного узпа на дешифратор 17 и по линии 45 связи в блок 6 индикации. Де- u)t фратор 17 формирует код неисправно- гг , подгибаемый на вход элемента И 15,

5 который открыт сигналом с выхода дешифратора 18. Код неисправности с выхода элемента И 15 через элемент ИЛИ 20 по линии 46 :нчзи поступает в блок 6 индикации. Од- новоемечно по сигналу с выхода триггера 13

0 одновибратор 21 вырабатывает импульс, который по линии 44 связи подается на вход регистра 26 и записывает в него код адреса ячейки блока 2 ПЭМРТИ, по считанной команде которой обнаружена неисправность.

5 Кроме того, импульс с выхода одновибрат - оа 21 проходит через элемент ИЛИ 29. опрокидывает триггер 22 в нулевое состояние, запрещая работу генератора 23 и останавливая диагностирование

0После устранения обнаруженной неисправности диагностирование блока 7 продолжается подачей по линии 34 связи игнгла Пуск, триггер 22 устанавливается в единичное состояние, импульс с выхода

5 одновибратора 28 записывает в счетчик 25 код адреса команды с выхода регистра 26, HJ которой остановилось диагностирование. Одновременно импульс с выхода одно- вибратора 28 по линии 47 связи поступает

U на вход триггера 13 и опрокидывает его в нулевое состояние. Сигналом с выхода триггера 22 разрешается работа генератора 23 ч т д до обнаружения следующего неисправного узла 31 диагностируемого блока 7.

5После окончания последовательности

первых команд диагностирования с выхода блока 2 памяти считывается последовательность вторых команд, предназначенных для тег,тового диагностирования узлов 31 блока 7 начинал с первого Процесс считывания

команд из блока 2 памяти и анализ реакций блока 7 происходит аналогичным образом. Отличие состоит в том, что у коммутатора 32, предшествующего диагностируемому узлу 31 блока 7, опрашиваются третьи входы, на которые по линии 40 связи поступает тестовая последовательность локализации неисправности, последняя одновременно с выхода регистра 8 по линии 39 связи подается на вход дешифратора 19, При обнаружении неисправности код неисправности с выхода дешифратора 17 через элемент И 15 не проходит, так как он закрыт сигналом с выхода дешифратора 18. Сигнал с выхода триггера 13 открывает элемент И 16, код неисправности с выхода дешифратора 19 через элемент И 16 и элемент 20 ИЛ И поступает по линии 46 связи в блок 6 индикации. Обнаруженная неисправность в блоке 7 устраняется, и процесс диагностирования продолжается.

Если последующие команды тесювой последовательности диагностирования узлов 3 1 блока 7 не обнаружат неисправное; ,, последняя команда с выхода блока 2 памяти сформирует на выходе дешифратора 30 сигнал, который проходит через элемент ИЛИ 29 и опрокидывает триггер 22 в нулевое состояние, прекращая диагностирование. Одновременно сигнал с выхода дешифратора 30 по линии 48 связи подается нз блок G индикации и включает сигнализацию Неисправность не обнаружена. На этом диагностирование блока 7 заканчивается, Формула изобретения 1. Устройство для диагностики цифровых блоков, содержащее блок памяти, блок коммутации, блок сравнения, блок управления и блок индикации, причем выход блока памяти соединен с информационным ьхо- дом блока коммутации и первым информационным входом блока сравнения, первый выход блока управления подключен к пдрес- ному входу блока памяти, второй выход блока управления соединен с первым синхровходом блока сравнения и управляющим входом блока коммутации, первый иы- ход которого подключен к входу режима блока сравнения, а второй выход блокп коммутации является выходом устройства для подключения к входу диагностируемого блока, отличающееся тем, что, с целью уменьшения времени локализации неисправности, третий выход блока управления

соединен с входом чтения блока памяти, четвертый выход блока управления подключен к второму синхровходу блока сравне- н,ия, вход операции блока управления

соединен с первым выходом блока коммутации, пятый и шестой выходы и синхровход бпока управления подключены соответственно к стробирующему входу, входу сброса и первому выходу бпока сравнения, вход

пуска бпока управления является входом пуска устройства, первый и второй информационные входы и управляющий вход блока индикации соединены соответственно с вторым и третьим вводами блока сраанения и седьмым выходом блока управления, а второй информационный вход блока сравнения является входом устройства для подключен1 1я к выходу диагностируемого блока

2 Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок управления содержит счетчик , реги то адреса, триггер пуска, генератор тактовых имп/льго, кольцевой ре истр, трш гер считывания команды, одновибратор, элемент ИЛИ и дешифратор кон- цл диагностирования, вход которого являс сч входом операции блока, первый вход, элемента ИЛИ и синлрогход регистра адреса образуют синхоивход блока, установо шый вход триггера пуска является входом пуска блока, выхпц дешифратора конца диагностирования соединен г, вторым входом элемента ИЛИ и седьмым выходом блока, выход элемента ИЛИ подключен к входу

сброса триггера пуска, выход которого соединен с входами однооибратора и генератора тактовых импульсов, выход которого подключен к синхровходу кольцевого регистра, выход одновибратора соединен с вхо0 дом записи счегчика адреса и шестым выходом блока, выход регистра адреса подключен к информационному входу счетчика адреса, выход которого соединен с информационным входом регистра адреса и пер5 вым вчходом блока, выходы кольцевого регистра с первого по седьмой подключены соогветС|венно к информационному входу этого же регистра, счетному входу счетчика адреса, входу сброса триггера считывания

0 команды, второму выходу блока, установочному вхоау триггера считывания команды, четвертому si пятому выходам блока, а выход триггера считывания команды является третьим выходом блока.

Фиг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Устройство для диагностирования цифровых узлов | 1986 |

|

SU1520517A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах диагностирования цифровых логических схем. Целью изобретения является уменьшение времени локализации неисправности. С этой целью в устройстве, содержащем блок памяти, блок коммутации, блок сравнения, блок управления и блок индикации, выходы блока управления соединены со входом чтения блока памяти, вторым синхровходом, стробирующим входом и входом сброса блока сравнения и управляющим входом блока индикации, вход операции и синхровход блока управления подключены соответственно к первому выходу блока коммутации и первому выходу блока сравнения, вход пуска блока управления является входом пуска устройства, первый и второй информационные входы блока индикации соединены соответственно со вторым и третьим выходами блока сравнения, второй информационный вход которого является входом устройства для подключения к выходу диагностируемого блока. 1 з.п. ф-лы, 5 ил.

Фиг.2

39

I

30

J4

Фиг.З

28

43

Фиг. U

40

41

Фиг. 5

| Устройство для диагностики дискретных блоков | 1974 |

|

SU627479A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1988-12-07—Подача