Г

Л

VJ о ел VJ

00

ю

Изобретение относится к контрольно- измерительной технике и может быть использовано для автоматизированного тестового контроля и диагностирования микропроцессорных блоков.

Цель изобретения - расширение области применения за счет обеспечения локализации неисправностей в объектах контроля, содержащих БИС, и повышение достоверности контроля за счет увеличения количества контролируемых точек объекта контроля и подачи на входы БИС объекта контроля тестовых воздействий по установленным временным диаграммам.

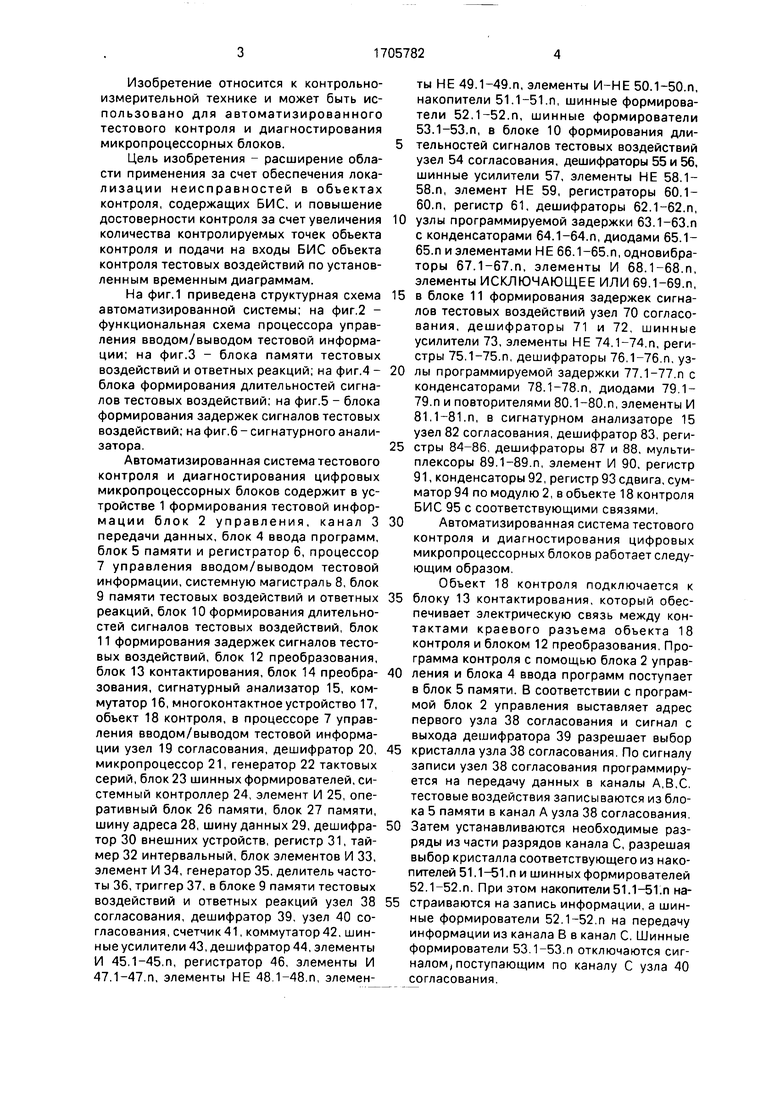

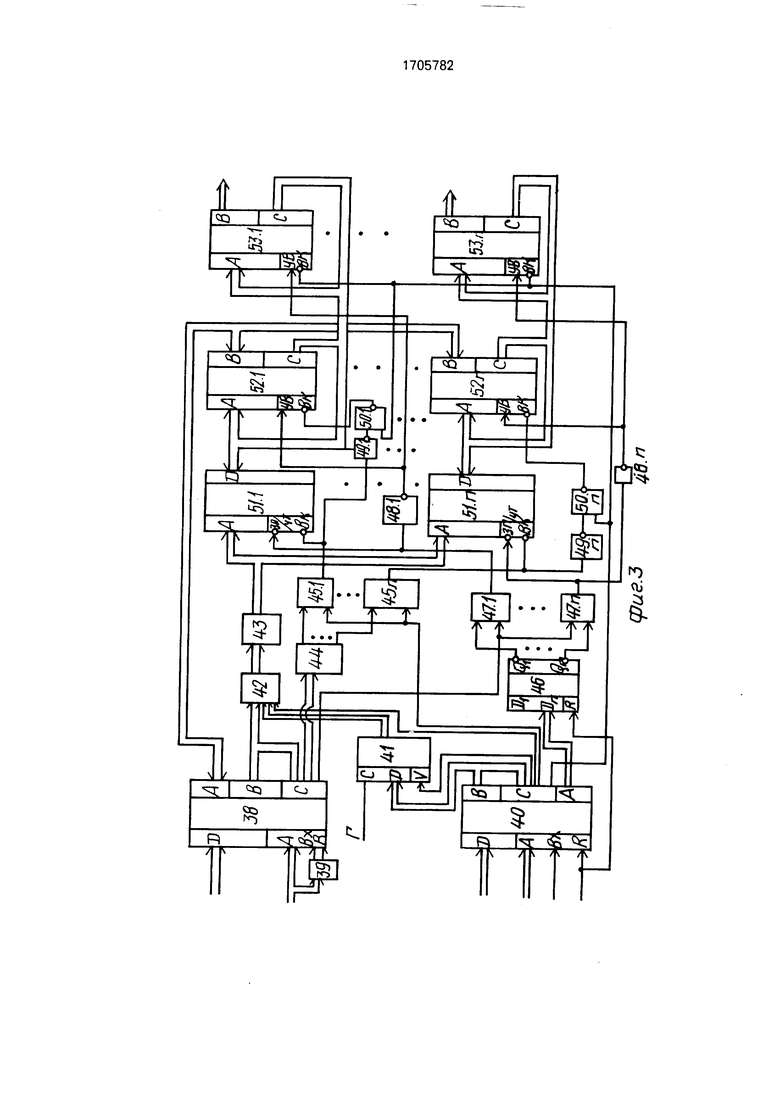

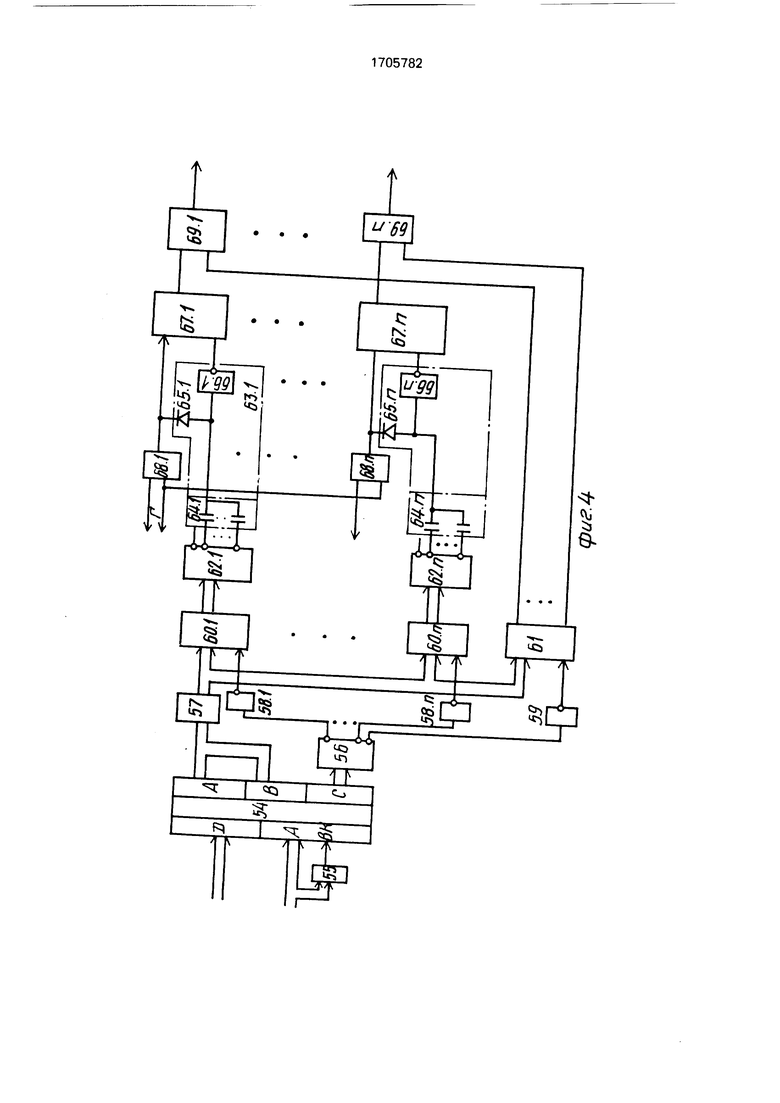

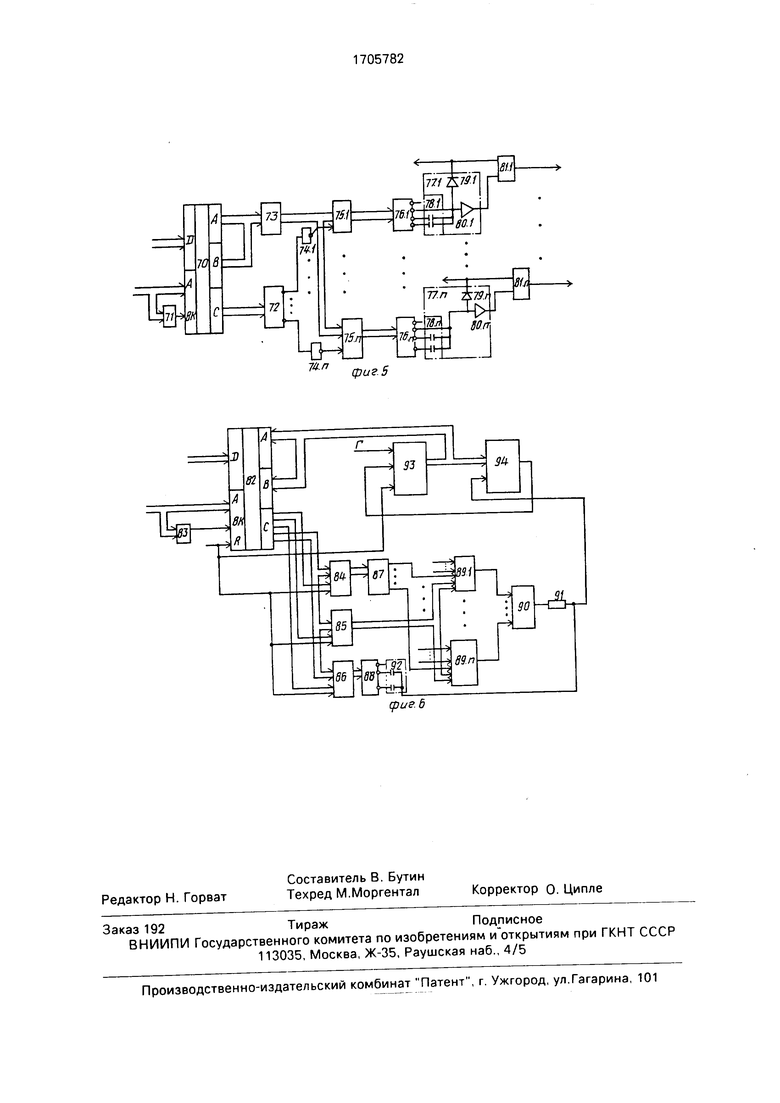

На фиг.1 приведена структурная схема автоматизированной системы; на фиг.2 - функциональная схема процессора управления вводом/выводом тестовой информации; на фиг.З - блока памяти тестовых воздействий и ответных реакций; на фиг.4 - блока формирования длительностей сигналов тестовых воздействий; на фиг.5 - блока формирования задержек сигналов тестовых воздействий; на фиг.6 - сигнатурного анализатора.

Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков содержит в устройстве 1 формирования тестовой информации блок 2 управления, канал 3 передачи данных, блок 4 ввода программ, блок 5 памяти и регистратор 6, процессор 7 управления вводом/выводом тестовой информации, системную магистраль 8, блок 9 памяти тестовых воздействий и ответных реакций, блок 10 формирования длительностей сигналов тестовых воздействий, блок 11 формирования задержек сигналов тестовых воздействий, блок 12 преобразования, блок 13 контактирования, блок 14 преобразования, сигнатурный анализатор 15, коммутатор 16, многоконтактное устройство 17, объект 18 контроля, в процессоре 7 управления вводом/выводом тестовой информации узел 19 согласования, дешифратор 20, микропроцессор 21, генератор 22 тактовых серий, блок 23 шинных формирователей, системный контроллер 24,элемент И 25, оперативный блок 26 памяти, блок 27 памяти, шину адреса 28, шину данных 29, дешифратор 30 внешних устройств, регистр 31, таймер 32 интервальный, блок элементов И 33, элемент И 34, генератор 35, делитель частоты 36, триггер 37, в блоке 9 памяти тестовых воздействий и ответных реакций узел 38 согласования, дешифратор 39, узел 40 согласования, счетчик 41, коммутатор42, шинные усилители 43, дешифратор 44, элементы И 45.1-45.п, регистратор 46, элементы И 47.1-47.п, элементы НЕ 48.1-48.п, элементы НЕ 49.1-49.п, элементы И-НЕ 50.1-50.П, накопители 51.1-51.п, шинные формирователи 52.1-52.п, шинные формирователи 53.1-53.п, в блоке 10 формирования длительностей сигналов тестовых воздействий узел 54 согласования, дешифраторы 55 и 56, шинные усилители 57, элементы НЕ 58.1- 58.п, элемент НЕ 59, регистраторы 60.1- 60.п, регистр 61, дешифраторы 62.1-62.п,

0 узлы программируемой задержки 63.1-63.п с конденсаторами 64.1-64.п, диодами 65.1- 65.п и элементами НЕ 66.1-65.п, одновибра- торы 67.1-67.п, элементы И 68.1-68.п, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 69.1-69.п,

5 в блоке 11 формирования задержек сигналов тестовых воздействий узел 70 согласования, дешифраторы 71 и 72, шинные усилители 73, элементы НЕ 74.1-74.П, регистры 75.1-75.п, дешифраторы 76.1-76.п, уз0 лы программируемой задержки 77.1-77.П с конденсаторами 78.1-78.п, диодами 79.1- 79.п и повторителями 80.1-80.п, элементы И 81.1-81.п, в сигнатурном анализаторе 15 узел 82 согласования, дешифратор 83, реги5 стры 84-86, дешифраторы 87 и 88, мультиплексоры 89.1-89.п, элемент И 90, регистр 91, конденсаторы 92, регистр 93 сдвига, сумматор 94 по модулю 2, в объекте 18 контроля БИС 95 с соответствующими связями.

0 Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков работает следующим образом.

Объект 18 контроля подключается к

5 блоку 13 контактирования, который обеспечивает электрическую связь между контактами краевого разъема объекта 18 контроля и блоком 12 преобразования. Программа контроля с помощью блока 2 управ0 ления и блока 4 ввода программ поступает в блок 5 памяти. В соответствии с программой блок 2 управления выставляет адрес первого узла 38 согласования и сигнал с выхода дешифратора 39 разрешает выбор

5 кристалла узла 38 согласования. По сигналу записи узел 38 согласования программируется на передачу данных в каналы А,В,С. тестовые воздействия записываются из блока 5 памяти в канал А узла 38 согласования.

0 Затем устанавливаются необходимые разряды из части разрядов канала С, разрешая выбор кристалла соответствующего из накопителей 51.1-51.п и шинных формирователей 52.1-52.п. При этом накопители 51.1-51.п на5 страиваются на запись информации, а шинные формирователи 52.1-52.п на передачу информации из канала В в канал С. Шинные формирователи 53.1-53.п отключаются сигналом, поступающим по каналу С узла 40 согласования.

Затем блок 9 памяти тестовых воздействий и ответных реакций настраивается на подачу тестовых воздействий через блок 12 преобразования и блок 13 контактирования, отключающих БИС 95 от соответствующих входов/выходов соседних микропроцессорных блоков объекта 18 контроля. Блок 2 управления в соответствии с диагностической программой разрешает выбор кристалла узла 19 согласования. По сигналу записи в канал В узла 19 согласования записывается адрес ячейки оперативного блока 26 памяти, в которую необходимо произвести запись данных. Данные записываются в канал А узла 19 согласования. В канал С узла 19 согласования записываются управляющие сигналы.

Информация, записанная в канал А, поступает на входы данных оперативного блока 26 памяти и записывается по необходимому адресу по сигналу записи, поступившему с одного из выходов канала С узла 19 через элемент И 25.

Блок 2 управления отключается от процессора 7, снимая сигнал Захват с микропроцессора 21, отрабатывая программу перезаписи тестовой информации из оперативного блока 26 памяти в каналы А,В,С узла 40 согласования. Программа перезаписи хранится в блоке 27 памяти. Тестовая информация поступает на соответствующие входы объекта 18 контроля и БИС 95.

Передача определенного количества слов тестовых воздействий и прием ответных реакций осуществляется следующим образом.

Количество слов, записанное в тестовой программе устройства 1 формирования, переписывается в оперативный блок 26 памяти процессора 7. Затем процессор 7 переписывает эту информацию по сигналу запись/чтение в таймер 32, который программируется на выдачу активного сигнала после отсчета программируемого количества импульсов, подаваемых с генератора 35, частота сигналов которого программируется с помощью регистра 31, в который записывается код необходимой частоты. Счетчик 41 на выходах выставляет поочередно коды адресов ячеек накопителей 51.1-51.п. После отсчета таймером 32 запрограммированного количества импульсов выходной сигнал таймера 32 взводит триггер 37, запрещая дальнейшее прохождение импульсов через элемент И 34.

Блок 10 формирования длительностей сигналов тестовых воздействий и блок 11 формирования задержек задают необходимую временную диаграмму работы БИС 95. На выходах одновибраторов 67.1-67.п образуются сигналы, длительность которых пропорциональна подключенным емкостям конденсаторов 64.1-64.п. Задержка сигналов тестовых воздействий производится с

помощью узлов программируемой задержки 77.1-77,п за счет подключения соответствующих конденсаторов 78.1-78.п.

Сигналы ответных реакций через многоконтактное устройство 17, коммутатор 16

0 могут поступать либо на сигнатурный анализатор 15 для формирования сигнатур и в дальнейшем их сравнения с помощью процессора 7 с эталонными, при этом результат сравнения дает информацию об исправно5 сти БИС 95, либо в блок 9 памяти тестовых воздействий для уточнения неисправности БИС 95 путем сравнения ответных реакций с эталонными.

Сигнатурный анализатор 16 работает

0 следующим образом.

По программе процессора 7 выбирается с помощью дешифратора 83 кристалл узла 82 согласования и тестовая информация записывается в канал С и переписывается в

5 регистр 84, регистр 85, регистр 86 по стро- бирующим сигналам, поступающим из канала С. С выходов регистра 84 информация поступает на входы дешифратора 87, активный сигнал с выхода которого поступает на

0 вход выбора кристалла одного из мультиплексоров 89.1-89.п, разрешая работу. С выходов регистра 85 информация поступает на адресные входы мультиплексоров 89.1- 89.п. Сигналы ответных реакций с выхода

5 элемента И 90 задерживаются на необходимое время относительно подачи сигналов тестовых воздействий. Программирование задержки происходит с помощью дешифратора 88 и регистра 86. Задержанные сигна0 лы ответных реакций поступают на один из входов сумматора 94 по модулю 2. Сигналы с выхода сумматора 94 поступают на информационный вход регистра 93 сдвига и записываются в него по сигналам с генератора

5 35. После прекращения подачи тактовых сигналов с выходов регистра 93 сдвига остаток считывается через каналы А и В в узел 82 согласования и передается в процессор 7.

0Сигналы ответных реакций с помощью многоконтактного устройства 17 через коммутатор 16 и блок 14 преобразования поступают на входы каналов В выбранных шинных формирователей 53.1-53.п и пере5 даются в каналы С, с выходов которых записываются по адресам, выставленным счетчиком 41, в необходимые ячейки блока 9 памяти. Затем блок 9 памяти отключается от объекта 18 диагностирования контроля и записанные ответные реакции переписываются устройством 1 формирования, где сравниваются с эталонными. Считывание ответных реакций из накопителей 51.1-51.п производится через шинные формирователи 52.1-52.п.

Использование автоматизированной системы позволяет более точно определять места возникновения неисправностей в цифровых блоках, содержащих БИС, повышает достоверность контроля и диагности- рования в связи с увеличением количества контролируемых точек диагностируемого блока и формированием тестовых сигналов согласно временной диаграмме компонентов, а также упрощает составление тестовых программ для микропроцессорных блоков за счет включения существующих тестовых программ в программы контроля и диагностирования сложных устройств.

Формулаизобретения Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков, содержащая в устройстве формирования тестовой информации блок управления, блок ввода про- грамм, блок памяти и регистратор, входы-выходы которых соединены с каналом передачи данных, блок контактирования, первая группа входов-выходов которого соединена с первой группой вхо- дов-выходов первого блока преобразования, вторая группа входов-выходов блока контактирования соединена с группой входов-выходов объекта контроля, отличающаяся тем, что, с целью расширения области применения за счет обеспечения локализации неисправностей в объектах контроля, содержащих БИС, и повышения достоверности контроля за счет увеличения количества контролируемых точек объекта контроля и подачи на входы БИС объекта контроля тестовых воздействий по установленным временным диаграммам, в систему введены процессор управления вводом-выводом тестовой информации, системная магистраль, блок памяти тестовых воздействий и ответных реакций, блок формирования длительностей сигналов тестовых воздействий, блок формирования задержек сигналов тестовых воздействий, второй блок преобразования, сигнатурный анализатор, многоконтактное устройство, коммутатор, первые группы входов-выходов процессора управления вводом-выводом тестовой информации и блока памяти тестовых воздействий и ответных реакций соединены с каналом передачи данных устройства формирования тестовой информации, вторая группа входов-выходов процессора управления вводом-выводом тестовой информации, первые группы входов блока памяти тестовых воздействий и ответных реакций, блока формирования длительностей сигналов тестовых воздействий, блока формирования задержек сигналов тестовых воздействий и входы-выходы сигнатурного анализатора соединены с системной магистралью, вторая группа входов- выходов и вторая группа входов блока памяти тестовых воздействий и ответных реакций соединены соответственно с второй группой входов-выходов первого блока преобразования и выходами второго блока преобразования, группа выходов соединена с второй группой входов блока формирования длительностей сигналов тестовых воздействий, группа выходов которого соединена с второй группой входов блока формирования задержек сигналов тестовых воздействий, группа выходов которого соединена с группой входов второго блока преобразования, первая группа входов- выходов многоконтактного устройства соединена с группой входов-выходов БИС объекта контроля, вторая группа входов-выходов соединена с первой группой входов- выходов коммутатора, вторая группа входов-выходов которого соединена с группой входов-выходов второго блока преобразования, группа выходов коммутатора соединена с группой входов сигнатурного анализатора.

CN

00 Г-

s

г74/7

фиг-5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1989 |

|

SU1691793A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1762280A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1994 |

|

RU2097827C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для автоматизированного тестового контроля и диагностирования микропроцессорных блоков. Цель изобретения - расширение области применения за счет обеспечения локализации неисправностей в объектах контроля, содержащих БИС, и повышение достоверности контроля за счет увеличения количества контролируемых точек объекта контроля подачи на входы БИС объекта контроля тестовых воздействий по установленным временным программам. Автоматизированная система содержит в устройстве 1 формирования тестовой информации блок 2 управления, канал 3 передачи данных, блок 4 ввода программ, блок 5 памяти и регистратор 6, процессор 7 управления вводом (выводом тестовой информации, системную магистраль 8, блок 9 памяти тестовых воздействий и ответных реакций, блок 10 формирования длительностей сигналов тестовых воздействий, блок 11 формирования задержек сигна- лов тестовых воздействий, блок 12 преобразования, блок 13 контактирования, блок 14 преобразования, сигнатурный анализатор 15, коммутатор 16, многоконтактное устройство 17, объект 18 контроля. 6 ил. 00 С

| Устройство для контроля и диагностирования электронных узлов | 1985 |

|

SU1415211A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автоматизированная система контроля и диагностики неисправностей электронных цифровых блоков | 1984 |

|

SU1318945A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-01-15—Публикация

1989-06-15—Подача