2. Устройство по п. 1, отличающееся тем, что-узел сжатия информации содержит триггеры, генератор импульсов, элементы И, блоки элементов И, элементы ИЛИ, элемент НЕ, элемент задержки, регистр, счетчик и дешифратор, выходы счетчика соединены с информационными входами первого блока элементов И, выходы которого соединены с входами дешифратора, первый и втррые выходы дешифратора соединены соответственно с первым входом первого элемента ИЛИ и вторыми входами второго элемента ИЛИ, третий выход - с первыми входами третьего элемента ИЛИ и первого элемента И и стробируюшими входами второго, третьего, четвертого и пятого блоков элементов И, выход второго элемента ИЛИ соединен с первым входом четвертого элемента ИЛИ и вторыми входами первого и третьего элементов ИЛИ, выход четвертого элемента ИЛИ - со стробируюшим входом шестого блока элементов И, выход третьего элемента ИЛИ - со стробируюш,им входом седьмого блока элементов И, выходы которого соединены с информационными входами шестого блока элементов И и первыми информационными входами второго, третьего и четвертого блоков элементов И, первые и вторые выходы регистра соединены с информационными входами соответственно седьмого и пятого блоков элементов И, выходы пятого блока элементов И соединены с вторыми информационными входами второго, третьего и четвертого блоков элементов И, выходы которых соединены соответственно с первыми, вторыми и третьими входами пятого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента ИЛИ, третьим входом первого элемента ИЛИ и через элемент НЕ с вторым входом первого элемента И, выход первого элемента И соединен с четвертым входом первого элемента ИЛИ, выход которого соединен с первыми входами первого триггера и счетчика, выход первого триггера соединен с первым входом второго элемента И и через элемент задержки со стробируюшим входом первого блока элементов И, выход второго элемента И соединен через генератор импульсов с первым входом второго триггера, выход второго триггера соединен с вторым входом второго элемента И, второй вход первого триггера, объединенные вход регистра и второй вход счетчика и второй вход второго триггера являются соответственно первым управляющим, информационным и вторым управляюшим входами узла сжатия информации, выходы генератора импульсов, шестого блока элементов И и первого элемента ИЛИ являются соответственно первым управляюшим, информационным и вторым управляющим выходами узла сжатия информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия и накопления графической информации | 1983 |

|

SU1096675A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для контроля систем программного управления станком | 1988 |

|

SU1580320A1 |

| Преобразователь электрического сигнала в давление жидкости или газа | 1983 |

|

SU1101600A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Устройство для управления вводом информации | 1983 |

|

SU1161949A1 |

1. УСТРОЙСТВО ДЛЯ СЖАТИЯ И НАКОПЛЕНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ по авт. св. № 1096675, отличающееся тем, что, с целью повышения информативности устройства, в него между выходом третьего регистра и первыми входами первого элемента ИЛИ введен узел сжатия информации, первый управляющий вход которого подключен к выходу второго элемента ИЛИ, первый управляющий выход - к управляющему входу третьего регистра, a второй управляющий выход подключен к входу третьего элемента задержки и является вторым выходом устройства, второй управляющий вход узла сжатия информации яа,тяется четвертым входом устройства. сл О5 4 О СО

1

Изобретение относится к автоматике и. вычислительной технике и может быть использовано в системах отображения информации.

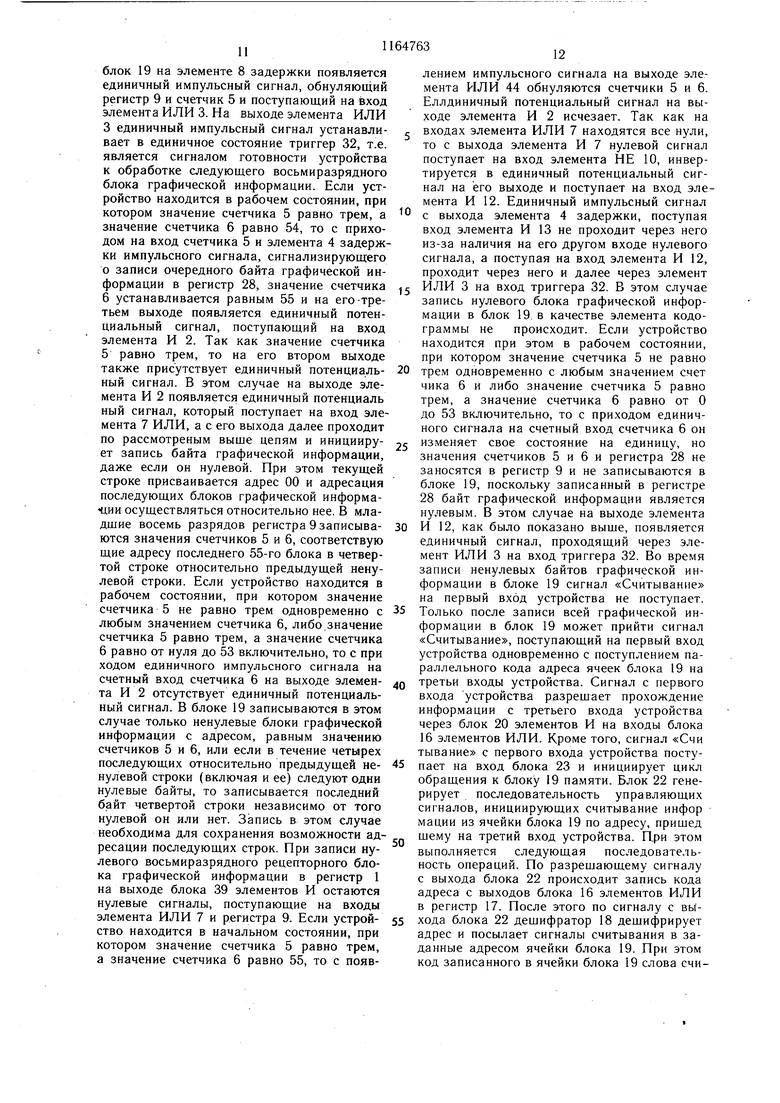

По основному авт. св. № 1096675 известно устройство для сжатия и накопления графической информации, содержащее первый регистр, выходы которого подключены к ин формационным входам дешифратора адреса, выходы дешифратора адреса соединены с первыми входами блока памяти, выходы которого подключены к информационным входам первого блока усилителей, выходы первого блока усилителей соединены с первыми входами второго регистра, выходы которого являются первыми выходами устройства, вторые выходы второго регистра подключены к информационным входам второго блока усилителей, выходы которого соединены с вторыми входами блока памяти, блок управления, первый вход которого является первым входом устройства, первый, второй, третий, четвертый, пятый и шестой выходы блока управления подключены соответственно к управляющим входам первого регистра, дешифратора адреса, второго и первого блока усилителей и первому, второму управляющим входам второго регистра, третий регистр, информационные входы которого являются вторыми входами устройства, выход третьего регистра соединен с вторыми информационными входами второго

регистра и первыми входами первого элемента ИЛИ, выход первого элемента ИЛИ подключен к первому входу первого элемента И и через элемент НЕ к первому входу второго элемента И, выход первого элемента И подключен к входам первого и второго элементов задержки и второго счетчика, выход первого элемента задержки соединен с третьим управляющим входом второго регистра, первым входом первого счетчика, управляющим входом третьего регистра и первым входом второго элемента ИЛИ, выходы второго счетчика подключены к информационным входам первого блока элементов И, выход второго элемента задержки соединен с вторым входом блока управления и стробирующим входам первого блока элементов И, информационные входы второго блока элементов И являются третьими входами устройства, стробирующий вход второго блока элементов И подключен к первому входу устройства, выходы первого и второго блоков элементов И соединены с соответствующими первыми и вторыми входами блока элементов ИЛИ, выходы которого под ключены к информационным входам первого регистра, первые выходы первого и третьего счетчиков - соответственно к третьим и четвертым информационным входам второго регистра, второй выход третьего счетчика - к второму входу первого счетчика, второй выход первого счетчика и третий выход третьего счетчика - соответственно к первому и второму входам третьего элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, входы третьего счетчика и третьего элемента задержки объединены и являются четвертым входом устройства, выход третьего элемента задержки подключен к вторым входам первого и второго элементов И, выход второго элемента И подключен к второму входу второго элемента ИЛИ, выход которого является вторым выходом устройства 1.

Недостатком известного устройства является низкий коэффициент сжатия графической информации, что снижает информативность устройства.

Цель изобретения - повышение информатичности устройства.

Указанная цель достигается тем, что в устройство для сжатия и накопления графической информации между выходом третьего регистра и первыми входами первого элемента ИЛИ введен узел сжатия информации первый управляющий вход которого подключен к выходу второго элемента ИЛИ, первый управляющий выход - управляющему входу третьего регистра, второй управляющий выход подключен к входу третьего элемента задержки и является вторым выходом устройства, второй управляющий вход узла сжатия информации является четвертым входом устройства.

Кро.ме того, узел сжатия информации содержит триггеры, генератор импульсов, элементы И, блоки элементов И, элементы ИЛИ элемент НЕ, элемент задержки, регистр, счетчик и дещифратор, выходы счетчика соединены с информационными входами первого блока элементов И, выходы котоого соединены с входами дешифратора, первый и вторые выходы дешифратора соединены соответственно с первым входом первого элемента ИЛИ и вторыми входами второго элемента ИЛИ, третий выход - с первыми

входами третьего элемента ИЛИ и первого элемента И и стробирующими входами второго, третьего, четвертого и пятого блоков элементов И, выход второго элемента ИЛИ соединен с первым входом четвертого элемента ИЛИ и вторыми выходами первого и третьего элементов ИЛИ, выход четвертого элемента ИЛИ - со стробирующими входом шестого блока элементов И, выход третьего элемента ИЛИ - со стробирующим входом

0 седьмого блока элементов И, выходы которого соединены с информационными входами шестого блока элементов И и первыми информационными входами второго, третьего и четвертого блоков элементов И, первые и вторые выходы регистра соединены с информационными входами соответственно седьмого и пятого блоков элементов И, выходы пятого блока элементов И соединены с вторыми информационными входами второго, третьего и четвертого блоков элементов И, выходы которых соединены соответственно с первыми, вторыми и третьими входами пятого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента ИЛИ, третьим входом первого элемента ИЛИ и через элемент НЕ с вторым входом первого элемента И, выход первого элемента И соединен с четвертым входом первого элемента ИЛИ, выход которого соединен с первыми входами первого триггера и счетчика, выход первого триггера соедиQ нен с первым входом второго элемента И и через элемент задержки со стробирующим входо.м первого блока элементов И, выход второго элемента И соединен через генератор импульсов с первым входом второго триггера, выход второго триггера соединен

5 с вторым входом второго элемента И, второй вход первого триггера, объединенные вход регистра и второй вход счетчика и второй вход второго триггера являются соответственно первым управляющим, информационным и вторым управляющим входами узла сжатия информации, выходы генератора импульсов, шестого блока элементов И и первого элемента ИЛИ являются соответственно первым управ.тяюшим, информационным и вторым управляющим выходами уз5 ла сжатия информации.

Увеличение коэффициента сжатия графической информации в данном случае происходит в результате реализации в устройстве метода психовизуального кодирования.

Q Сущность метода кодирования заключается в том, что восьмиразрядные блоки графической информации, содержащие единичный бит информации только в одном из разрядов, воспринимаются в устройстве как нулевые и исключаются из информационно5 го массива при дальнейшем самоадаптирующемся блочном кодирования в случае отсутствия в восьмиразрядном блоке графической информации, находящемся над рассматриваемым в предыдущей строке телевизионной развертки, комбинаций вида:

1)X X I X X X X X - блок в предыдущей строке

О О О I О О О О - рассматриваемый блок

2)XXXIXXXX- блок в предыдущей строке

00010000- рассматриваемый блок 3)ХХХХ1ХХХ- блок в предыдущей строке

00 О I О О О О - рассматриваемый блок гдеХ- безразличное состояние.

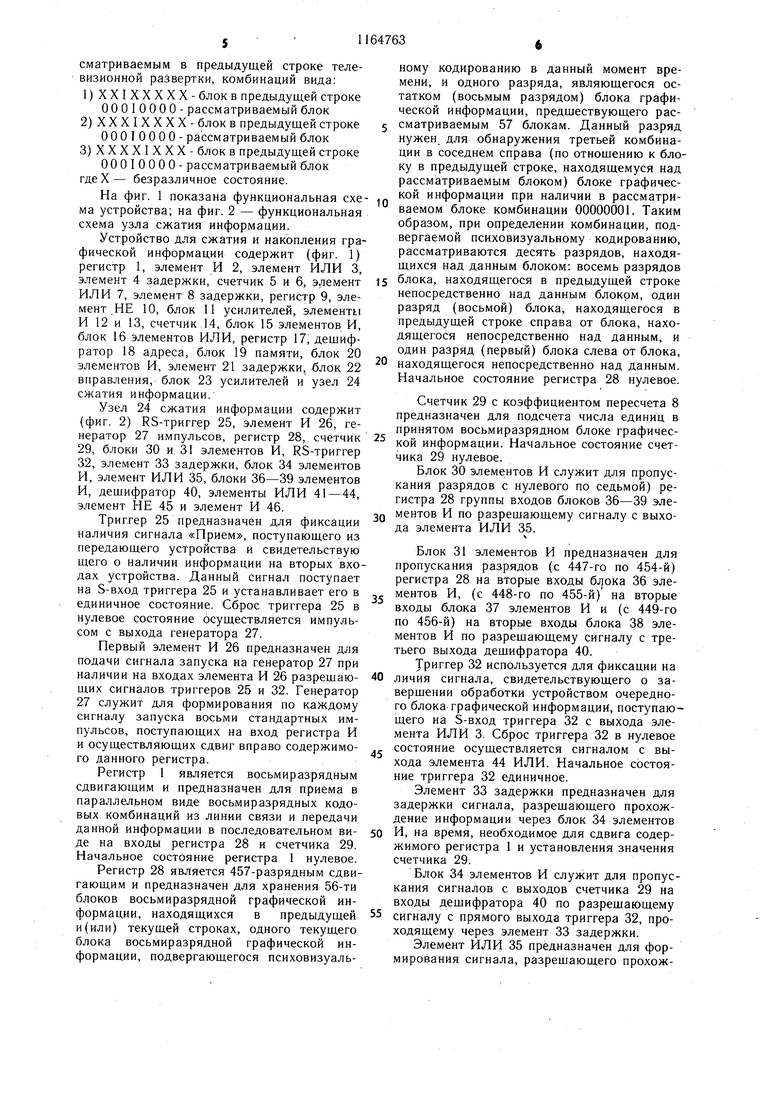

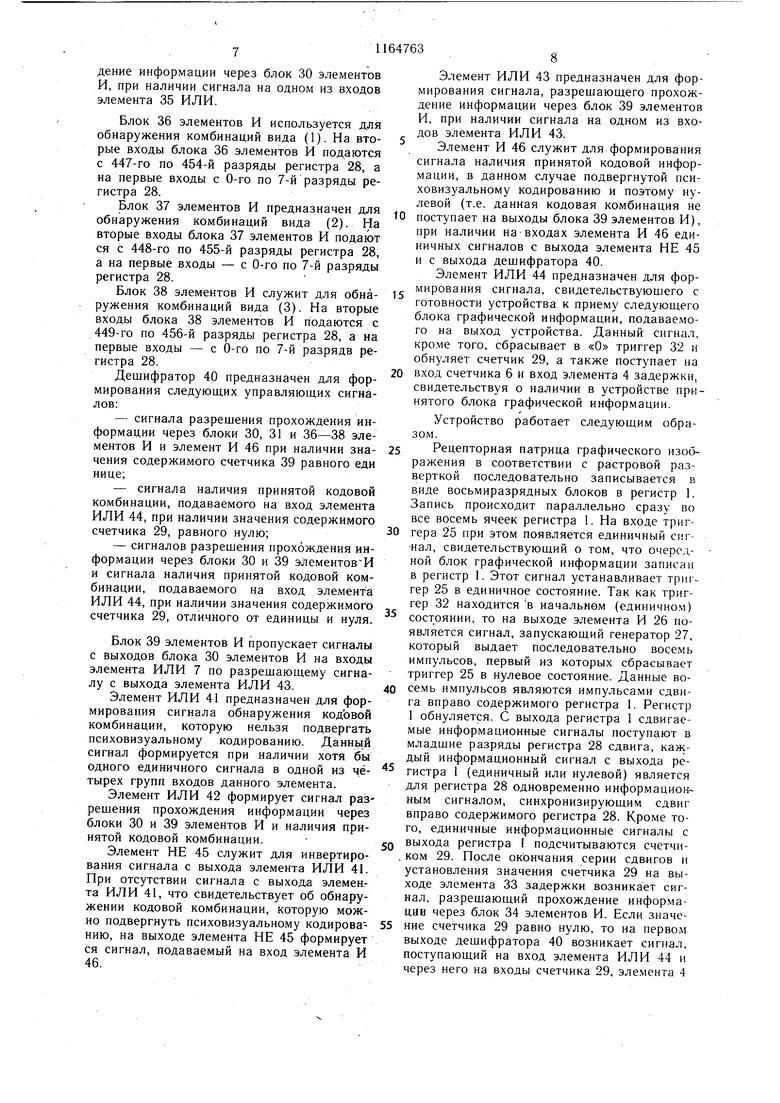

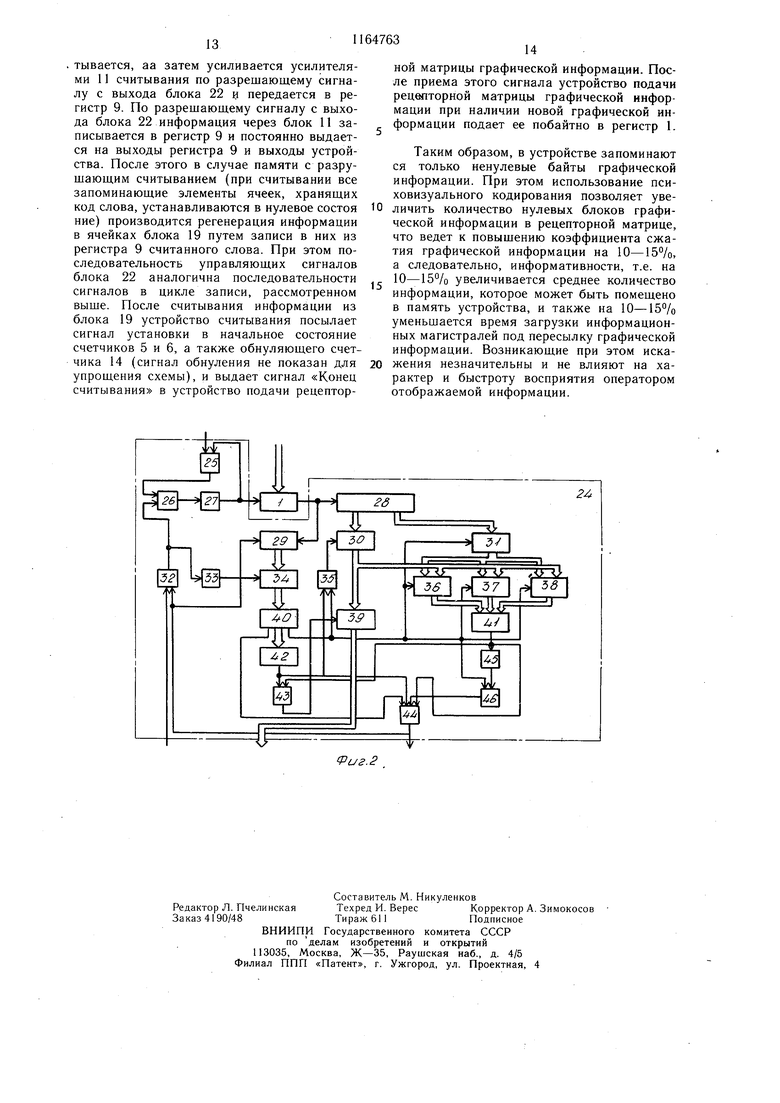

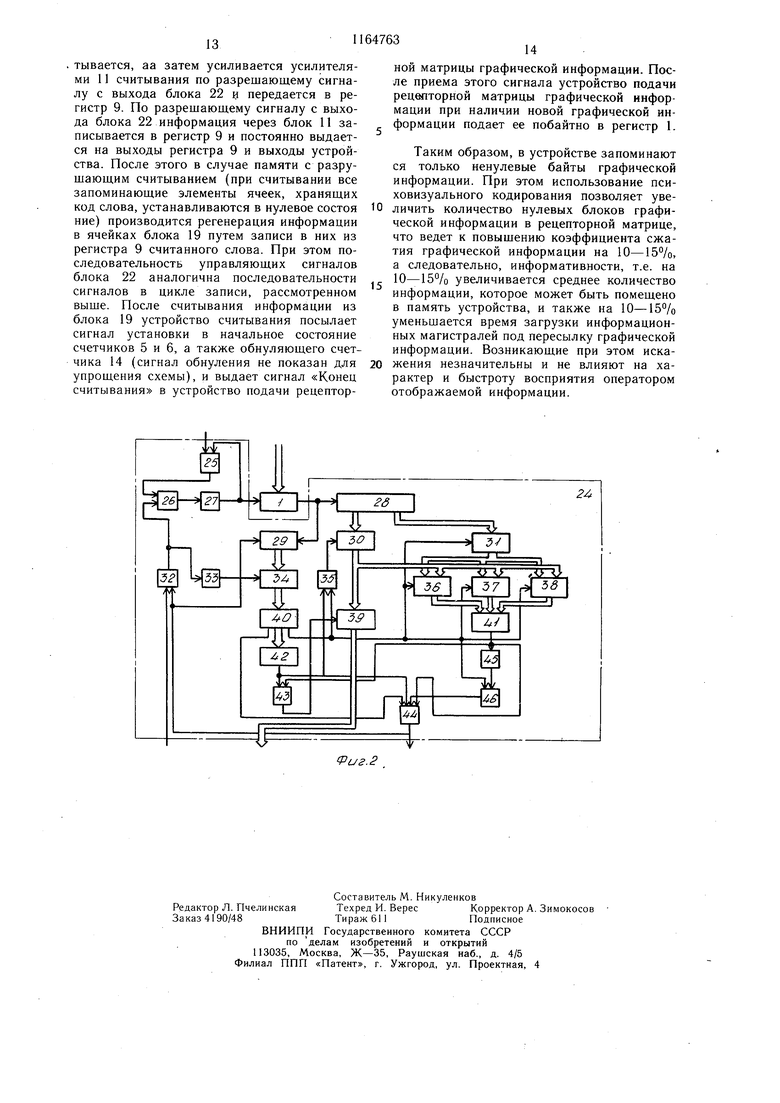

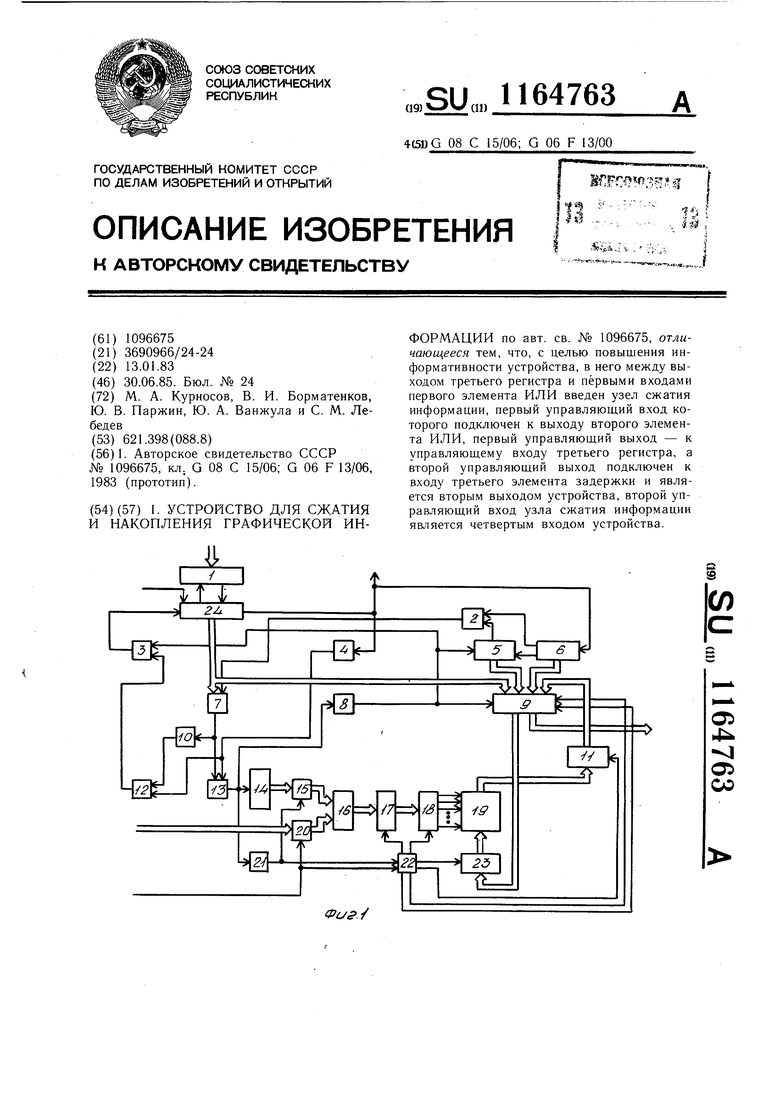

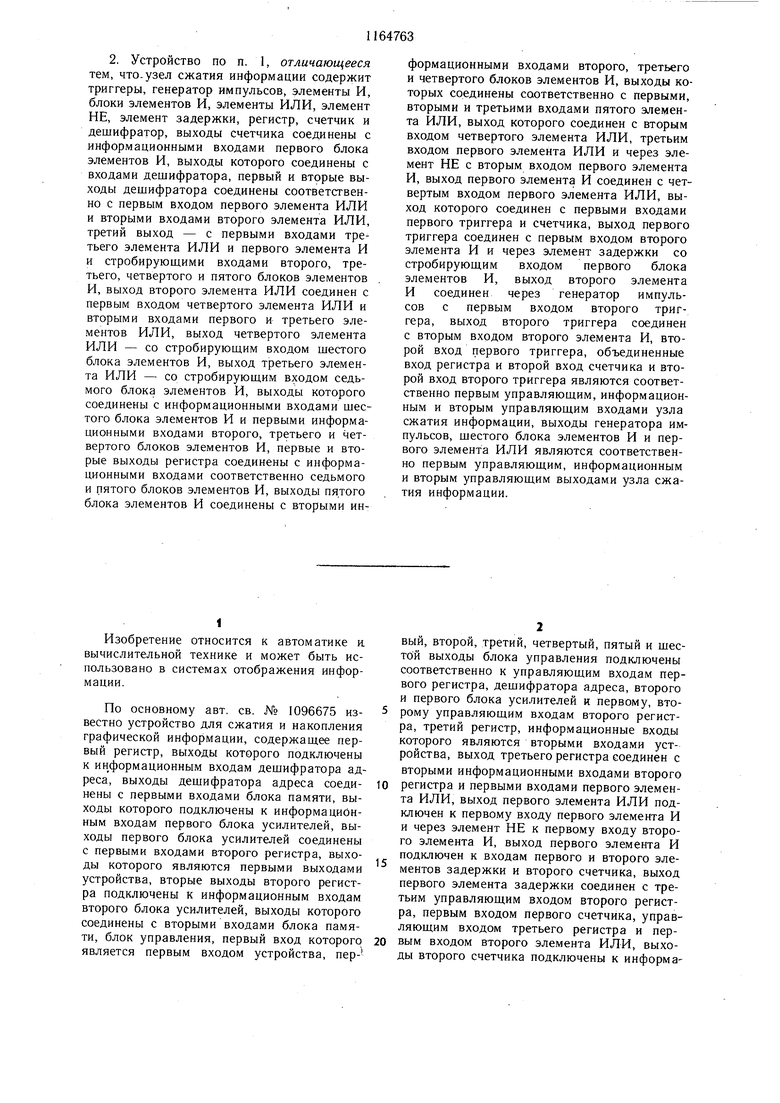

На фиг. 1 показана функциональная схема устройства; на фиг. 2 - функциональная схема узла сжатия информации.

Устройство для сжатия и накопления графической информации содержит (фиг. 1) регистр 1, элемент И 2, элемент ИЛИ 3, элемент 4 задержки, счетчик 5 и 6, элемент ИЛИ 7, элемент 8 задержки, регистр 9, элемент, НЕ 10, блок 11 усилителей, элементы И 12 и 13, счетчик 14, блок 15 элементов И, блок 16 элементов ИЛИ, регистр 17, дещифратор 18 адреса, блок 19 памяти, блок 20 элементов И, элемент 21 задержки, блок 22 вправления, блок 23 усилителей и узел 24 сжатия информации.

Узел 24 сжатия информации содержит (фиг. 2) RS-триггер 25, элемент И 26, генератор 27 импульсов, регистр 28, счетчик 29, блоки 30 и 31 элементов И, RS-триггер 32, элемент 33 задержки, блок 34 элементов И, элемент ИЛИ 35, блоки 36-39 элементов И, дешифратор 40, элементы ИЛИ 41-44, элемент НЕ 45 и элемент И 46.

Триггер 25 предназначен для фиксации наличия сигнала «Прием, поступающего из передающего устройства и свидетельствую щего о наличии информации на вторых входах устройства. Данный сигнал поступает на S-вход триггера 25 и устанавливает его в единичное состояние. Сброс триггера 25 в нулевое состояние осуществляется импульсом с выхода генератора 27.

Первый элемент И 26 предназначен для подачи сигнала запуска на генератор 27 при наличии на входах элемента И 26 разрещающих сигналов триггеров 25 и 32. Генератор 27 служит для формирования по каждому сигналу запуска восьми стандартных импульсов, поступающих на вход регистра И и осуществляющих сдвиг вправо содержимого данного регистра.

Регистр 1 является восьмиразрядным сдвигающим и предназначен для приема в параллельном виде восьмиразрядных кодовых комбинаций из линии связи и передачи данной информации в последовательном виде на входы регистра 28 и счетчика 29. Начальное состояние регистра 1 нулевое.

Регистр 28 является 457-разрядным сдвигающим и предназначен для хранения 56-ти блоков восьмиразрядной графической информации, находящихся в предыдущей и (или) текущей строках, одного текущего блока восьмиразрядной графической информации, подвергающегося психовизуальному кодированию в данный момент времени, и одного разряда, являющегося остатком (восьмым разрядом) блока графической информации, предществующего рассматриваемым 57 блокам. Данный разряд нужен для обнаружения третьей комбинации в соседнем справа (по отнощению к блоку в предыдущей строке, находящемуся над рассматриваемым блоком) блоке графической информации при наличии в рассматриваемом блоке комбинации 00000001. Таким образом, при определении комбинации, подвергаемой психовизуальному кодированию, рассматриваются десять разрядов, находящихся над данным блоком: восемь разрядов

5 блока, находящегося в предыдущей строке непосредственно над данным блоком, один разряд (восьмой) блока, находящегося в предыдущей строке справа от блока, находящегося непосредственно над данным, и один разряд (первый) блока слева от блока,

0 находящегося непосредственно над данным. Начальное состояние регистра 28 нулевое.

Счетчик 29 с коэффициентом пересчета 8 предназначен для подсчета числа единиц в принятом восьмиразрядном блоке графической информации. Начальное состояние счетчика 29 нулевое.

Блок 30 элеме нтов И служит для пропускания разрядов с нулевого по седьмой) регистра 28 группы входов блоков 36-39 элеQ ментов И по разрещающему сигналу с выхода элемента ИЛИ 35.

ч

Блок 31 элементов И предназначен для пропускания разрядов (с 447-го по 454-й) регистра 28 на вторые входы б;|ока 36 элементов И, (с 448-го по 455-й) на вторые входы блока 37 элементов И и (с 449-го по 456-й) на вторые входы блока 38 элементов И по разрещающему сигналу с третьего выхода дещифратора 40.

Триггер 32 используется для фиксации на 0 личия сигнала, свидетельствующего о заверщении обработки устройством очередного блока графической информации, поступающего на S-вход триггера 32 с выхода элемента ИЛИ 3. Сброс триггера 32 в нулевое состояние осуществляется сигналом с выхода элемента 44 ИЛИ. Начальное состояние триггера 32 единичное.

Элемент 33 задержки предназначен для задержки сигнала, разрешающего прохождение информации через блок 34 элементов 0 И, на время, необходимое для сдвига содержимого регистра 1 и установления значения счетчика 29.

Блок 34 элементов И служит для пропускания сигналов с выходов счетчика 29 на входы дешифратора 40 по разрешающему 5 сигналу с прямого выхода триггера 32, проходящему через элемент 33 задержки.

Элемент ИЛИ 35 предназначен для формирования сигнала, разрешающего прохождение информации через блок 30 элементов И, при наличии сигнала на одном из входов элемента 35 ИЛИ.

Блок 36 элементов И используется для обнаружения комбинаций вида (1). На вторые входы блока 36 элементов И подаются с 447-го по 454-й разряды регистра 28, а на первые входы с 0-го по 7-й разряды регистра 28.

Блок 37 элементов И предназначен для обнаружения комбинаций вида (2). На вторые входы блока 37 элементов И подают ся с 448-го по 455-й разряды регистра 28, а на первые входы - с 0-го по 7-й разряды регистра 28.

Блок 38 элементов И служит для обнаружения комбинаций вида (3). На вторые входы блока 38 элементов И подаются с 449-го по 456й разряды регистра 28, а на первые входы - с 0-го по 7-й разрядв регистра 28.

Дешифратор 40 предназначен для формирования следующих управляющих сигналов:

-сигнала разрещения прохождения информации через блоки 30, 31 и 36-38 элементов И и элемент И 46 при наличии значения содержимого счетчика 39 равного еди нице;

-сигнала наличия принятой кодовой комбинации, подаваемого на вход элемента ИЛИ 44, при наличии значения содержимого счетчика 29, равного нулю;

-сигналов разрешения прохождения информации через блоки 30 и 39 элементов И и сигнала наличия принятой кодовой комбинации, подаваемого на вход элемента ИЛИ 44, при наличии значения содержимого счетчика 29, отличного от единицы и нуля.

Блок 39 элементов И пропускает сигналы с выходов блока 30 элементов И на входы элемента ИЛИ 7 по разрешающему сигналу с выхода элемента ИЛИ 43.

Элемент ИЛИ 41 предназначен для формирования сигнала обнаружения кодовой комбинации, которую нельзя подвергать психовизуальному кодированию. Данный сигнал формируется при наличии хотя бы одного единичного сигнала в одной из четырех групп входов данного элемента.

Элемент ИЛИ 42 формирует сигнал разрешения прохождения информации через блоки 30 и 39 элементов И и наличия принятой кодовой комбинации.

Элемент НЕ 45 служит для инвертирования сигнала с выхода элемента ИЛИ 41. При отсутствии сигнала с выхода элемента ИЛИ 41, что свидетельствует об обнаружении кодовой комбинации, которую можно подвергнуть психовизуальному кодированию, на выходе элемента НЕ 45 формирует ся сигнал, подаваемый на вход элемента И 46.

Элемент ИЛИ 43 предназначен для формирования сигнала, разрешающего прохождение информации через блок 39 элементов И, при наличии сигнала на одном из входов элемента ИЛИ 43.

Элемент И 46 служит для формирования сигнала наличия принятой кодовой информации, в данном случае подвергнутой психовизуальному кодированию и поэтому нулевой (т.е. данная кодовая комбинация не поступает на выходы блока 39 элементов И), при наличии на входах элемента И 46 единичных сигналов с выхода элемента НЕ 45 и с выхода дешифратора 40.

Элемент ИЛИ 44 предназначен для формирования сигнала, свидетельствующего с готовности устройства к приему следующего блока графической информации, подаваемого на выход устройства. Данный сигнал, кроме того, сбрасывает в «О триггер 32 и обнуляет счетчик 29, а также поступает на вход счетчика 6 и вход элемента 4 задержки, свидетельствуя о наличии в устройстве принятого блока графической информации.

Устройство работает следующим образом.

Рецепторная патрица графического изображения в соответствии с растровой разверткой последовательно записывается в виде восьмиразрядных блоков в регистр 1. Запись происходит параллельно сразу во все восемь ячеек регистра 1. На входе триггера 25 при этом появляется единичный сигнал, свидетельствующий о том, что очередной блок графической информации записан в регистр 1. Этот сигнал устанавливает триггер 25 в единичное состояние. Так как триггер 32 находится в начальном (единичном) состоянии, то на выходе элемента И 26 появляется сигнал, запускающий генератор 27, который выдает последовательно восемь импульсов, первый из которых сбрасывает триггер 25 в нулевое состояние. Данные восемь импульсов являются импульсами сдвига вправо содержимого регистра 1. Регистр 1 обнуляется. С выхода регистра 1 сдвигаемые информационные сигналы поступают в младшие разряды регистра 28 сдвига, каждый информационный сигнал с выхода регистра 1 (единичный или нулевой) является для регистра 28 одновременно инфор.мационным сигналом, синхронизирующим сдвиг вправо содержимого регистра 28. Кроме того, единичные информационные сигналы с выхода регистра I подсчитываются счетчиком 29. После окончания серии сдвигов и установления значения счетчика 29 на выходе элемента 33 задержки возникает сигнал, разрешающий прохождение информации через блок 34 элементов И. Если значение счетчика 29 равно нулю, то на первом выходе дешифратора 40 возникает сигнал, поступающий на вход элемента ИЛИ 44 и через него на входы счетчика 29, элемента 4

задержки, на вход триггера 32 - выход устройства, свидетельствуя о готовности устройства к приему следующего блока графической информации. По этому сигналу устройство подачи рецепторной матрицы графической информации передает следующий блок графической- информации, который записывается в регистр 1 еще до окончания обработки устройством предыдущего блока. Блок 39 элементов И в данном случае, закрыт и на его выходах присутствуют нули, подаваемый на входы регистра 9. Если значение счетчика 29 равно «1, то на третьем выходе дешифратора 40 возникает сигнал, открывающий через элемент ИЛИ 35 блок 30, 31 и 36-38 элементов И и элемент И 46. На входы бло.юв 36-38 элементов И поступают, информационные сигналы из старших (447-456-й) и младщих (О-7-й) разрядов регистра 28. В случае наличия одной из трех комбинаций на выходах данных блоков возникает единичный сигнал, проходящий через элемент ИЛИ 41, открывающий через элемент ИЛИ 43 и блок 39 элементов И и поступающий через элемент ИЛИ 44 на выход устройства и на входы триггера 32, элемента 4 задержки и счетчика 6. С выходов блока 39 на входы регист ра 9 передается кодовая комбинация. Если все три комбинации отсутствуют, то на выходах блоков 36-38 элементов И присутствуют нулевые сигналы, что ведет к появлению на выходе элемента НЕ 45 единичного сигнала, проходящего через элемент 46 на вход элемента ИЛИ 44 и поступающего на элемент 4 задержки, счетчик 6, вход триггера 32 и выход устройства. В этом случае на входы регистра 9 поступают нулевые сигналы.

При всех остальных значениях счетчика 29 на вторых выходах дешифратора 40 возникают единичные сигналы, которые, пройдя через элемент 42 ИЛИ, открывают блок 30 элементов И и через элементы ИЛИ 35 и 44 поступают на выход устройства и входы триггера 32, элемента 4 задержки и счетчика 6.

Сигнал с выхода элемента ИЛИ 42, прой дя через элемент ИЛИ 43, открывает блок 39 элементов И. На вторые входы регистра 9 поступает кодовая комбинация, записанная в регистре 28.

Таким образом, сигнал с выхода элемента ИЛИ 44 поступает на вход элемента 4 задержки и на счетный вход счетчика 6, который под воздействием данного сигнала изменяет свое состояние на единицу. Если устройство находится в начальном состоянии, при котором значение счетчика 5 равно трем, а значение счетчика 29 равно 55, то под воздействием импульса с выхода элемед1та ИЛИ 44 обнуляется счетчик 6 и на его втором выходе появляется импульс переноса, который обнуляет счетчик 5. Импульсный сигнал с выхода элемента ИЛИ 44 задерживается элементом 4 задержки на время, необходимое для изменения значения счетчиков 5 и 6, поступает на входы элементов И 13 и 12.

Допустим, на выходах блока 39 элементов И содержится ненулевая информация. В этом случае, на выходе элемента ИЛИ 7 присутствует единичный сигнал, поступающий на входы элементов НЕ 10 и И 13. При наличии единичного потенциального сиг нала на входе элемента И 13 и единичного импульсного сигнала на его другом входе (с выхода элемента 4 задержки) на выходе элемента И 13 находится единичный импульс ный сигнал. В этом случае на выходе элемента НЕ 10 единичный сигнал отсутствует и импульс с выхода элемента 4 задержки не проходит через элемент И 12. Единичный импульсный сигнал с выхода элемента И 13 поступает на входы элементов 8 и 21 задержки, а также на счетный вход счетчика 14 адреса. По этому сигналу происходит увеличение значения счетчика 14 адреса на единицу. После этого на выходе элемента 21 задержки появляется единичный импульсный сигнал, разрешающий прохождение сигналов кода адреса с выхода счетчика 14 через блок 15 элементов И на входы блока 16 элементов ИЛИ и инициирующий цикл обращения к памяти 19. По этому сигналу блок 22 управления генерирует последовательность управляющих сигналов, подаваемых на отдельные ячейки блока 19 памяти. По разрешающему сигналу с выхода блока

22осуществляется прием кода адреса с груп нового выхода блока 16 элементов ИЛИ в регистр 17. По разрешающему сигналу с выхода блока 22 осуществляется занесение восьмиразрядного блока информации в стар шие разряды 16-разрядного регистра 9 и значений (в данном случае нулевых) счет-чиков 5 и 6 в младшие разряды регистра .9, что соответствует записи первого ненулевого блока в строке с адресом 00. При этом происходит выдача данной информации на выходы регистра 9. После этого по разрешающему сигналу с выхода блока 22 дешифратор 18 дешифрирует код адреса, поступаю щий с выхода регистра 17, формирует в соответствующей ячейке блока 19 сигнал считывания, по которому осуществляется считывание слова в ячейке и, следовательно, очистка данной ячейки. При этом на блок 11 не выдается сигнал с выхода блока 22, что блокирует усилители 11 считывания и в регистр 9 информация с блока 11 не посту.пает. После этого дешифратор 18.формирует сигнал записи, разрешающий запись информации в выбранную ячейку блока 19. По раз рещающему сигналу с выхода блока 22 блок

23осуществляет запись информации с первых выходов регистра 9 в выбранную ячейку блока 19. После записи информации в

блок 19 на элементе 8 задержки появляется единичный импульсный сигнал, обнуляющий регистр 9 и счетчик 5 и поступающий на вход элемента ИЛИ 3. На выходе элемента ИЛИ 3 единичный импульсный сигнал устанавливает в единичное состояние триггер 32, т.е. является сигналом готовности устройства к обработке следующего восьмиразрядного блока графической информации. Если устройство находится в рабочем состоянии, при котором значение счетчика 5 равно трем, а значение счетчика 6 равно 54, то с приходом на вход счетчика 5 и элемента 4 задержки импульсного сигнала, сигнализирующ его о записи очередного байта графической информации в регистр 28, значение счетчика 6 устанавливается равным 55 и на его-третьем выходе появляется единичный потенциальный сигнал, поступающий на вход элемента И 2. Так как значение счетчика

5равно трем, то на его втором выходе также присутствует единичный потенциальный сигнал. В этом случае на выходе элемента И 2 появляется единичный потенциаль ный сигнал, который поступает на вход элемента 7 ИЛИ, а с его выхода далее проходит по рассмотреным выще цепям и инициирует запись байта графической информации, даже если он нулевой. При этом текущей строке присваивается адрес 00 и адресация последующих блоков графической информач ии осуществляться относительно нее. В младшие восемь разрядов регистра 9 записываются значения счетчиков 5 и 6, соответствую щие адресу последнего 55-го блока в четвертой строке относительно предыдущей ненулевой строки. Если устройство находится в рабочем состоянии, при котором значение счетчика 5 не равно трем одновременно с любым значением счетчика 6, либо.значение счетчика 5 равно трем, а значение счетчика

6равно от нуля до 53 включительно, то с при ходом единичного импульсного сигнала на счетный вход счетчика 6 на выходе элемента И 2 отсутствует единичный потенциальный сигнал. В блоке 19 записываются в этом случае только ненулевые блоки графической информации с адресом, равным значению счетчиков 5 и 6, или если в течение четырех последующих относительно предыдущей ненулевой строки (включая и ее) следуют одни нулевые байты, то записывается последний байт четвертой строки независимо от того нулевой он или нет. Запись в этом случае необходима для сохранения возможности адресации последующих строк. При записи нулевого восьмиразрядного рецепторного блока графической информации в регистр 1 на выходе блока 39 элементов И остаются нулевые сигналы, поступающие на входы элемента ИЛИ 7 и регистра 9. Если устройство находится в начальном состоянии, при котором значение счетчика 5 равно трем, а значение счетчика 6 равно 55, то с появлением импульсного сигнала на выходе элемента ИЛИ 44 обнуляются счетчики 5 и 6. Еллдиничный потенциальный сигнал на выходе элемента И 2 исчезает. Так как на 5 входах элемента ИЛИ 7 находятся все нули, то с выхода элемента И 7 нулевой сигнал поступает на вход элемента НЕ 10, инвертируется в единичный потенциальный сигнал на его выходе и поступает на вход элемента И 12. Единичный импульсный сигнал

с выхода элемента 4 задержки, поступая вход элемента И 13 не проходит через него из-за наличия на его другом входе нулевого сигнала, а поступая на вход элемента И 12, проходит через него и далее через элемент

5 ИЛИ 3 на вход триггера 32. В этом случае запись нулевого блока графической информации в блок 19. в качестве элемента кодограммы не происходит. Если устройство находится при этом в рабочем состоянии, при котором значение счетчика 5 не равно

0 трем одновременно с любым значением счет чика 6 и либо значение счетчика 5 равно трем, а значение счетчика 6 равно от О до 53 включительно, то с приходом единичного сигнала на счетный вход счетчика 6 он

5 изменяет свое состояние на единицу, но значения счетчиков 5 и 6 и регистра 28 не заносятся в регистр 9 и не записываются в блоке 19, поскольку записанный в регистре 28 байт графической информации является нулевым. В этом случае на выходе элемента

0 И 12, как было показано выще, появляется единичный сигнал, проходящий через элемент ИЛИ 3 на вход триггера 32. Во время записи ненулевых байтов графической информации в блоке 19 сигнал «Считывание на первый вход устройства не поступает.

5 Только после записи всей графической информации в блок 19 может прийти сигнал «Считывание, поступающий на первый вход устройства одновременно с поступлением параллельного кода адреса ячеек блока 19 на

третьи входы устройства. Сигнал с первого входа устройства разрещает прохождение информации с третьего входа устройства через блок 20 элементов И на входы блока 16 элементов ИЛИ. Кроме того, сигнал «Счи тывание с первого входа устройства поступает на вход блока 23 и инициирует цикл обращения к блоку 19 памяти. Блок 22 генерирует последовательность управляющих сигналов, инициирующих считывание инфор мации из ячейки блока 19 по адресу, пришед шему на третий вход устройства. При этом выполняется следующая последовательность операций. По разрешающему сигналу с выхода блока 22 происходит запись кода адреса с выходов блока 16 элементов ИЛИ в регистр 17. После этого по сигналу с выхода блока 22 дешифратор 18 дешифрирует адрес и посылает сигналы считывания в заданные адресом ячейки блока 19. При этом код записанного в ячейки блока 19 слова считывается, аа затем усиливается усилителями 11 считывания по разрешающему сигналу с выхода блока 22 и передается в регистр 9. По разрешающему сигналу с выхода блока 22 информация через блок 11 записывается в регистр 9 и постоянно выдается на выходы регистра 9 и выходы устройства. После этого в случае памяти с разрушающим считыванием (при считывании все запоминающие элементы ячеек, хранящих код слова, устанавливаются в нулевое состоя ние) производится регенерация информации в ячейках блока 19 путем записи в них из регистра 9 считанного слова. При этом последовательность управляющих сигналов блока 22 аналогична последовательности сигналов в цикле записи, рассмотренном выше. После считывания информации из блока 19 устройство считывания посылает сигнал установки в начальное состояние счетчиков 5 и 6, а также обнуляющего счетчика 14 (сигнал обнуления не показан для упрощения схемы), и выдает сигнал «Конец считывания в устройство подачи рецепторной матрицы графической информации. После приема этого сигнала устройство подачи рецепторной матрицы графической информации при наличии новой графической информации подает ее побайтно в регистр 1.

Таким образом, в устройстве запоминают ся только ненулевые байты графической информации. При этом использование психовизуального кодирования позволяет увеличить количество нулевых блоков графической информации в рецепторной матрице, что ведет к повышению коэффициента сжатия графической информации на 10-15%, а следовательно, информативности, т.е. на 10-15% увеличивается среднее количество информации, которое может быть помещено в память устройства, и также на 10-15% уменьшается время загрузки информационных магистралей под пересылку графической информации. Возникающие при этом искажения незначительны и не влияют на характер и быстроту восприятия оператором отображаемой информации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сжатия и накопления графической информации | 1983 |

|

SU1096675A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-06-30—Публикация

1983-01-13—Подача