Изобретение относится к области обработки цифровых данных, поступающих из каналов свяэи и может быть использовано, в частности, в устройствах приема и обработки дискретных сообщений на базе ЭВМ.

Цель изобретения - увеличение .эффективности за счет предварительной обработки информации.

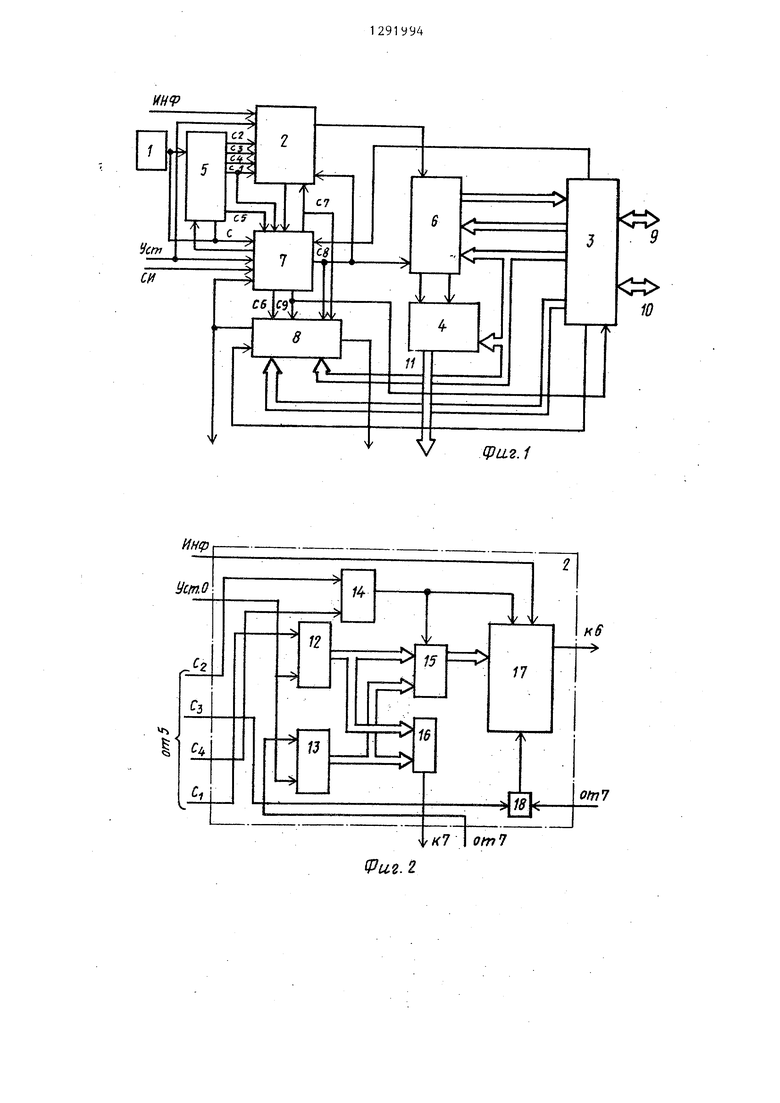

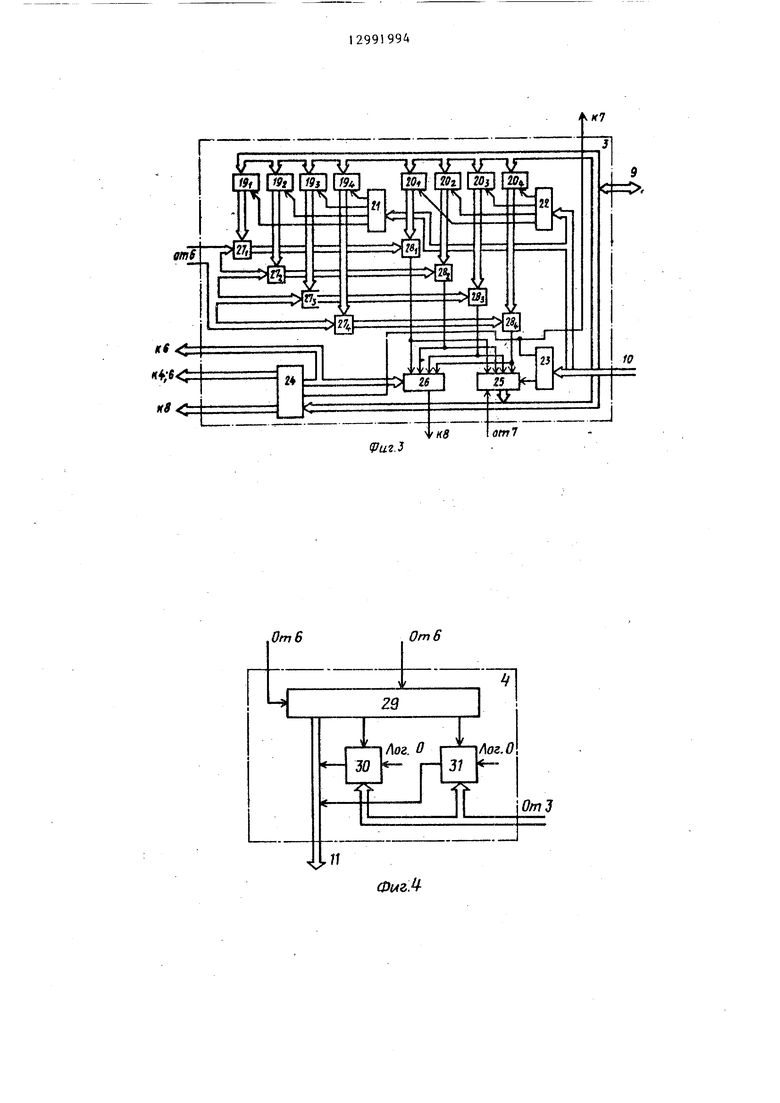

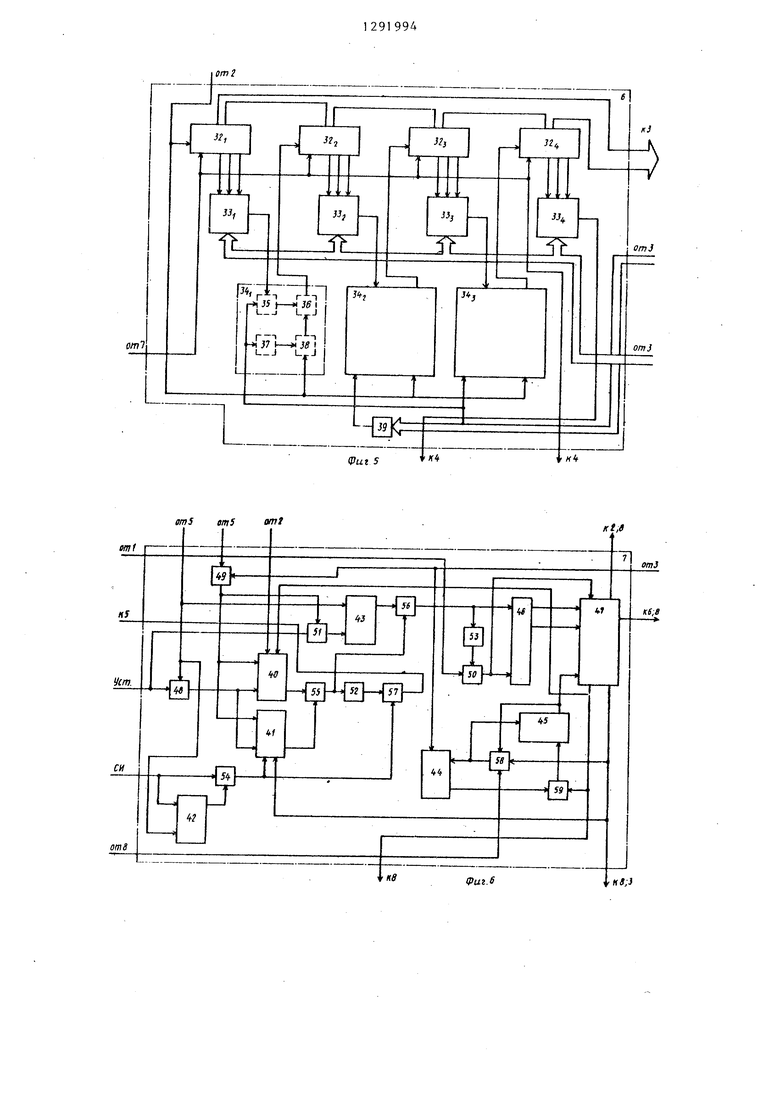

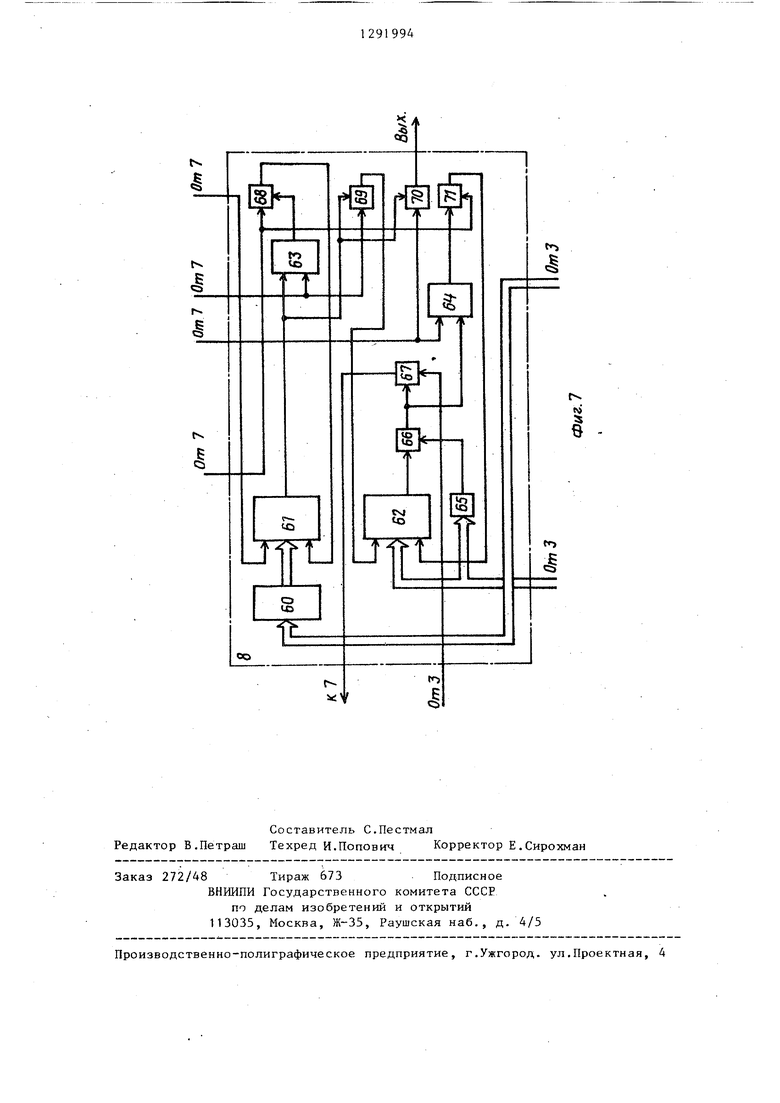

На фиг. 1 представлена блок-схема устройства; на фи г. 2 - схема блока памяти; на фиг. 3 - схема блока анализа информации; на фиг. 4 - схема блока выдачи информации; на фиг. 5 - схема блока переключения режима; на фиг. 6 - схема блока управления; на фиг. 7-схема узла прерывания.

Устройство содержит (фиг. 1) генератор 1 импульсов, блок 2 памяти, блок 3 анализа информации, блок 4 выдачи информации, распределитель 5 импульсов, блок 6 переключения режима, блок 7 управления, узел 8 прерывания, вход - выход 9 устройства, вход 10 и выход 11 устройства.

Блок 2 памяти содержит (фиг. 2) счетчик 12 адреса записи, счетчик 13 адреса считывания, триггер 14, коммутатор 15, узел 16 сравнения, оперативную память 17, элемент ИЛИ 18.

Блок 3 анализа информации содержи (фиг. 3) регистры 19 масок, регистры 20 эталонов, дешифраторы 21 - 23, регистр 24 управления, регистр 25 совпадений, дешифратор 26 совпадений, группы элементов И 27, элементы 28 сравнения.

Блок 4 выдачи информации содержит (фиг. 4) сдвиговый регистр 29 и коммутаторы 30 и 31.

Блок 6 переключения режима содержит (фиг. 5) сдвиговые регистры 32, коммутаторы 33 знака и коммутаторы 34 режима. Каждый коммутатор 34 режима содержит элементы И-НЕ 35 и 36, элемент НЕ 37 и элемент И-НЕ 38 Блок 6 содержит также элемент И 39.

Блок 7 управления содержит (фиг.6) триггеры 40-45, счетчик 46, дешифратор 47, элементы ИЛИ 48 - 51, элементы НЕ 52 и J3, элементы И 54 - 59.

Узел 8 прерывания содержит (фиг.7) дешифратор -60 кода длительности знака, реверсивные счетчики 61 знака и 62 базы анализа, триггеры 63 и 64, элементы И 65 - 71.

Устройство работает следующим образом.

0

5

0

5

ЗО

35

40

45

50

55

После общесистемного сигнала Установка в начальное состояние, приходящего извне, ЭВМ через восьмиразрядную системную шину 9 данных последовательно загружает коды в каждый из четырех регистров 19 масок и четырех регистров 20 эталонов (фиг. 2). Сигнал разрешения записи кода с системной шины данных в конкретный регистр является резуль татом дешифрации на дешифраторе 21 или 22 кода адреса, проходящего по шине 10 адреса из ЭВМ в регистр 24 кода управления (фиг. 2). Сигнал, являющийся результатом дешифрации дешифратором 23 кода адреса регистра 24 управления одновременно с сигналом разрешения записи кода в регистр 24 является также сигналом начала работы устройства Пуск, снимаемым с выхода блока 3 (фиг. 1). В ответ на сигнал Пуск, приходящий на вход блока 7 управления при наличии высокого потенциала на линии синхроимпульсов, сопровождающих биты данных, блок 7.управления выдает на выход сигнал, поступающий на вход распределителя 5 и запускающий схему формирования первичной сетки тактирующих импульсов С1-С5, формирующихся из опорной частоты генератора 1 .

По импульсу СЗ последовательно поступающая из канала связи дискретная информация побитово записывается в блок 2 памяти. Считывание непрерывно накапливаемой в блоке 2 памяти информации управляется ЭВМ. Считанный из блока 2 памяти бит информации поступает на вход блока 6 переключения режима (фиг. 5), представляющего собой цепочку сдвиговых регистров 32 с изменяемыми схемой включения и длиной анализируемого фрагмента информации. Запись на вход цепочки нового бита и сдвиг данных по цепочке осуществляются по импульсу С8, формируемому блоком 7 управления. Режим включения сдвиговых регистров 32 (последовательный, последовательно-параллельный или параллельный) задается ЭВМ посредством записи в двух разрядах регистра 24 управления соответствующей кодовой комбинации.

Сигналы, являющиеся результатом дешифраций кода режима, поступают на коммутаторы , 34 режима, которые

31

формируют каналы протекания информации по регистрам 32, Длина анализируемого фрагмента информации зависит от длительности знаков, передаваемых по каналу связи. Длительность знаков (пять, шесть или семь) известна заранее и закодирована в двух разрядах регистра 24 управления. Аппаратно длина информационного фрагмента изменяется посредством коммутации трех старших разрядов восьмиразрядных сдвиговых регистров 32 на один выход Коммутацию осуществляет соответствующий каждому регистру 32 коммутатор 33 согласно коду длительности знака; с информационных выходов сдвиговых регистров 32 постоянно снимаются четыре параллельных восьмиразрядных кода.

Таким образом, в зависимости от режима включения на входы блока 3 .анализа поступают тридцать две информационные линии, где:

все линии соответствуют различным битам информационной последователь- ности;

первые шестнадцать линий попарно идентичны вторым шестнадцати линиям;

идентичны соответствующие разряды всех четырех восьмиразрядных кодов.

В блоке 3 анализа поступающие из блока переключения режима на входы поразрядных элементов И 27 восьмиразрядные коды перемножаются с содержимым регистров 19 масок, а затем поразрядно сравниваются на элементах 28 сравнения кодов с содержимым регист- .ров 20 эталонов. Четыре сигнала, являющиеся результатом сравнений, по- cTynaJOT с элементов 28 сравнения на входы дешифратора 26 совпадений, куда поступает также код режима. Результатом дешифрации является сигнал Обнаружение или Нет обнаружения, приходящий на выход блока 3 анализа. В силу того, что сигнал Обнаружение может явиться результатом ошибочного (промежуточного) .совпадения последо- вательности информационных бит с эталонами, возникает необходимость его познакового тактирования.

Далее, так как факт обнаружения искомой комбинации информационных бит влечет за собой цикл машинной обработки полученного прерывания, необходимо избавиться от избыточности пре- Р1)1ваний, т.е. внести некоторый знаковый интервал (базу анализа), на котором в ЭВМ поступило бы не больше одно9944

го прерывания. Введение базы ана;п1за исключает обработку избыточной информации о совпадениях с эталонами и существенно повышает быстродействие системы в целом. Эти задачи решаются узлом 8 прерывания.

Код длительности знака приходит на первые управляющие входы дешифратора 60 кода длительности знака, а с его выхода - на вход реверсивного счетчика 61 знака, работающего на вычитание. Запись кода в счетчик 61 призводится импульсом С6 в том случае, если-на выходе триггера 63 высокий потенциал. Обратный счет производитс по импульсу С7, поступающему на вход счетчика, являющийся первым тактовым входом узла 8 прерывания. Когда содержимое счетчика 61 становится равным нулю, на его выходе появляется импульс, который перебрасывает триггер 64 в единичное состояние, тем самым открывая элемент И 68, и импульс С6 перезаписывает по управляющему входу код длительности знака в реверсивный счетчик 61 знака. Следующий за импульсом С7 импульс С8 перебрасывает триггер 63 в нулевое состояние и через элемент И 69 поступает на вход реверсивного счетчика 62 базы анализа, на входы которого подается через вторые управляющие входы узла прерывания код базы анализа, поступающий также и на элемент И 65. Запись кода в счетчик 61 производится импульсом С6, поступающим на его вход.

Из этого следует, что счет происходит по импульсу С8, тактированному импульсом с выхода реверсивного счетчика 61 знака. Таким образом, на выходе реверсивного счетчика 62 базы анализа импульсы будут появляться через каждые К знаков, где К определяется кодом базы анализа. Через элемент И 66 сигналы с выхода реверсивного счетчика 62 и элемента И 65 поступают на элемент И 67 и управляют сигналом, проходящим на другой вход элемента И 67 и являющимся входом узла 8 прерывания. С выхода элемента И 67, являющегося выходом узла Ь, снимается сформированный сигнал Прерывание. Сигнал на выходе элемента И 66 перебрасывает триггер 64 в единичное состояние., чем .открывает элемент И 71, пропускаю- щий импульс С6 на управляющий вход -реверсивного счетчнка 62 базы анапиза. Импульсом С 6 в счетчик 62 перезаписывается код базы анализа, приходящий на третий тактовый вход узла 8 импульс С9 сбрасывает триггер 64 и, если по второму входу элемент И 70 открыт, поступает на выход устройства сопряжения.

С выхода коммутатора 33 знака блока 6 переключения режима биты информации последовательно поступают на вход сдвигового регистра 29, являющийся входом блока 4. Сдвиг данных в регистре 29 производится по импульсу С8, приходящему на тактовый вход каскада. Восьмиразрядный параллельный код информационного знака поступает через выходы каскада на межсистемную шину, причем шестой и седьмой разряды кода заведены через коммутатор 30 шестого разряда и коммутатор 31 седьмого разряда, что позволяет обнулять лишние разряды кода при длине знака меньше восьми бит (шесть или семь). Сдвиг информации в регистре 29 происходит одновременно со сдвигом в цепочке регистров 32 блока 6 переключения режима.

Работа устройства сопряжения обеспечивается блоком 7 управления, основными функциями которого являются формирование вторичной сетки тактовых импульсов С6-С9 и управление блоком 2 памяти. Тактовые последовательности импульсов формируются с помощью счетчика 46 и дешифратора 47, стробируемого счетными импульсами со счетного входа счетчика 46. Сигнал, приходящий с входа начальной установки, через элемент ИЛИ 48 поступает на входы триггеров 40 и 41, устанавливая их в единичное состояние, а через элемент ИЛИ 51 - на вход триггера 43, устанавливая его в нулевое состояние.

Элемент И 56 закрыт по первому входу, и на вход Обнуление счетчика 46 ароходит обнуляющий потенциал, одновременно блокируя через элемент НЕ 53 его счетный вход.

Приходящий на вход блока управления сигнал Пуск вырабатываемый в блоке 3 анализа, через элемент ИЛИ 49 поступает На входы триггеров 40 и 41,

JO

триггер 42, на вход которого он приходит, находится в единичном состоянии и элемент И 54 открыт по входу. В момент прихода информационного синхроимпульса на выходе элемента И 54 появляется единичный сигнал, проходящий через элемент И 57 на выход бло- |ка. Положительная ступенька на в.ходе 1распределителя 5 означает формирова- ,ние первичной сетки тактирующих импульсов С1-С5, поступающих с распределителя 5 соответственно на входы блока 2 памяти.

15

20

25

30

Импульсом С1 показание счетчика 12 адреса записи устанавливается на единицу. Следующим импульсом С2 триггер 14 перебрасывается в нулевое состояние, и на первом управляющем входе оперативной памяти (ОП) 17 устанавливается уровень логического нуля, что соответствует режиму записи данных в ОП 17. Импульсом СЗ очередной бит данных записывается в ячейку ОП 17, адрес которой определяется счетчиком 12 адреса и выходом коммутатора 15 адреса. Следующим импульсом С4 триггер 14 перебрасывается в единичное состояние, и до прихода следующего информационного синхроимпульса блок 2 памяти находится в режиме считывания данных из ОП 17. Импульс С5, приходя на тактовый вход блока 7 управления, перебрасывает триггеры 40

35 и 41 в единичное состояние. Это приводит к тому, что инвертированный эле- jментом НЕ 52 сигнал с выхода элемента И 55 блокирует элемент И 57 и на выходе блока 7 управления (входе распределителя) устанавливается уровень логического нуля.

Сигнал на выходе элемента И 56 через элемент НЕ 53 разблокирует элемент ИЛИ 50, и через него на счетный вход начинают поступать с тактового входа импульсы опорного генератора 1 . С выходов счетчика 46, являющихся двумя.младшими его разрядами, кодовые комбинации поступают на соот50 ветствующие входы дешифратора 47. Так как счетчик 46 перебрасывается спадом положительного счетного импульса, а дешифратор 47 стробируется

40

45

передним фронтом того же импульса, обнуляя их. На выходе элемента НЕ 52 55 поступающего на его первый стробирую- и входе элемента И 57 устанавливается уровень логической единицы. К приходу синхроимпульса, сопровождающего мент времени, соответствующий ко- информационный бит в канале связи, довой комбинации 00 на выходах счет|ЩИЙ вход, первый импульс на выходе дешифратора 47 появляется в мо

триггер 42, на вход которого он приходит, находится в единичном состоянии и элемент И 54 открыт по входу. В момент прихода информационного синхроимпульса на выходе элемента И 54 появляется единичный сигнал, проходящий через элемент И 57 на выход бло- |ка. Положительная ступенька на в.ходе 1распределителя 5 означает формирова- ,ние первичной сетки тактирующих импульсов С1-С5, поступающих с распределителя 5 соответственно на входы блока 2 памяти.

5

0

5

0

Импульсом С1 показание счетчика 12 адреса записи устанавливается на единицу. Следующим импульсом С2 триггер 14 перебрасывается в нулевое состояние, и на первом управляющем входе оперативной памяти (ОП) 17 устанавливается уровень логического нуля, что соответствует режиму записи данных в ОП 17. Импульсом СЗ очередной бит данных записывается в ячейку ОП 17, адрес которой определяется счетчиком 12 адреса и выходом коммутатора 15 адреса. Следующим импульсом С4 триггер 14 перебрасывается в единичное состояние, и до прихода следующего информационного синхроимпульса блок 2 памяти находится в режиме считывания данных из ОП 17. Импульс С5, приходя на тактовый вход блока 7 управления, перебрасывает триггеры 40

5 и 41 в единичное состояние. Это приводит к тому, что инвертированный эле- jментом НЕ 52 сигнал с выхода элемента И 55 блокирует элемент И 57 и на выходе блока 7 управления (входе распределителя) устанавливается уровень логического нуля.

Сигнал на выходе элемента И 56 через элемент НЕ 53 разблокирует элемент ИЛИ 50, и через него на счетный вход начинают поступать с тактового входа импульсы опорного генератора 1 . С выходов счетчика 46, являющихся двумя.младшими его разрядами, кодовые комбинации поступают на соот0 ветствующие входы дешифратора 47. Так как счетчик 46 перебрасывается спадом положительного счетного импульса, а дешифратор 47 стробируется

0

5

передним фронтом того же импульса, поступающего на его первый стробиру мент времени, соответствующий ко- довой комбинации 00 на выходах счет

|ЩИЙ вход, первый импульс на выходе дешифратора 47 появляется в мочика 46. Продолжающие поступать на счетчик 46 импульсы опорной частоты формируют поступающие импульсы С7 - С9, соответствующие кодовьм комбинациям на входах дешифратора 47 соответственно 01, 10, 11. Импульс С9 стробирует по синхровходу тригге- :ра 41 сигнал, приходящий на его информационный вход. Этот сигнал соответствует появлению на тактовом входе устройства сопряжения синхроимпульса, сопровождающего новый бит информации. До тех пор триггер 41 на ходится в единичном состоянии и дешифратор 47 продолжает формировать импульсы С6-С9.

При появлении на входе устройства нового бита информации по сопровождающему его синхроимпульсу на выходе элемента И 54 появляется сигнал, который стробируется импульсом С9 и перебрасывает триггер 41 в нулевое состояние, что ведет к обнулению счетчика 46 и блокированию его счетного входа. Одновременно открывается элемент И 57, и на входе распределителя устанавливается положитель- ный потенциал, что означает разре- щение формирования импульсов С1-С5 и начало нового цикла Запись-считывание. Импульс С7 поступает на вход счетчика 13 адреса считывания и увеличивает адрес считывания бита из блока 2 памяти на единицу. Следующий за ним импульс С8 приходит на другой вход. Через элемент ИЛИ 18 он поступает на второй управляющий вход ОП 17 и по этому импульсу происходит считывание очередного бита информации на цепочку регистров 32 блока 6 переключения режима.

Опорная частота генератора 1 много

больше частоты следования информационных синхроимпульсов, в результате на один импульс записи СЗ приходится несколько импульсов считывания С8. Это связано с необходимостью согласования записи и считывания информации из блока 2 памяти, так как после обнаружения искомого кадра информации считывание информации из ОП 17 прекращается и устройство сопряжения находится в режиме ожида- ния, гфодолжая накапливать информацию При одинаковых скоростях записи и считывания это неизбежно приводит к переполнению ОП и потере информации

5

0

5

В блоке 2 памяти постоянно происхо---.. дит сравнение содержимого счетчика 12 адреса записи и счетчика 13 адреса считывания на элементе 16 сравнения адресов. Из-за различия в скоростях наступает момент, когда счетчик 13 адреса считывания догонит счетчик 12 адреса записи. В этом случае на выходе элемента 16 сравнения адресов, являющемся выходом перепол нения блока 2 памяти, появляется сигнал совпадения адресов, который поступает на вход блока 7 управления (на вход триггера 40), стробируется импульсом С6, поступающим с выхода дешифратора 47 и перебрасывает триггер 40 в нулевое состояние, что, в свою очередь, ведет к обнулению счетчика 46 и блокировке его счетного входа. До прихода нового бита информации из канала импульсы С6-С9 генерироваться не будут, следовательно, не будет происходить и считывание информации из ОП 17.

0

0

5

0

5

С приходом следующего информационного синхроимпульса начинает новый цикл. После -появления на входе блока 7 управления, сигнала разрешения, формируемого в узле 8 прерывания, импульс С9 проходит через элемент И 58 и устанавливает триггеры 44 и 45 в нулевое состояние. Так как потенциал на выходе триггера 45 ответственен j за формирование сигналов С7 и С8, после прихода сигнала разрешения с выходов дешифратора снимаются лишь сигналы С6 и СУ. В это время ЭВМ считывает из блока 3 анализа содержимое регистра 25 совпадений, анализирует состояние устройства сопряжения и принимает решение о дальнейшем режиме функционирования.

Для устройства сопряжения результатом анализа является перезагрузка регистра 24 управления, входящего в состав блока 3 анализа. Сигнал Пуск сбрасывает триггер 44 в единичное состояние и открывает элемент И 59. Импульс С6 через элемент И 59 перебрасывает триггер 45 в единичное состояние, что разблокирует дешифратор 47 на формирование импульсов С7 и С8.

Формула изобретения

Устройство для сопряжения вычислительной машины с каналом связи, содержащее блок анализа информации, блок выдачи информации, блок памяти, генератор импульсов, причем информационный вход блока памяти является информационным входом устройства для подключения к каналу связи, группа входов-выходов логических условий блока анализа информации является группой входов-выходов логических условий устройства для подключения к группе управляющих входов-выходов вычислительной машины, первая группа информационных входов блока анализа информации является группой информационных входов устройства для под- к:ж1чения к группе информационных выходов вычислительной машины-, вход начальной установки блока памяти является входом начальной установки устройства для подключения к выходу начальной установки вычислительной машины, группа информационных выххэ- дов блока выдачи информации соединена с группой информационных входов вычислительной машины, отличающееся тем, что, с целью увеличения эффективности за счет предварительной обработки информации, в него введены блок управления, блок переключения режима, распределитель импульсов, узел прерывания, причем вход начальной установки блока управления подключен к выходу начальной установки вычислительной машины, синхровход блока управления подключен к синхровходу вычислительной машины, выход прерывания узла прерывания соединен с разрешающим входом блока управления и. является выходом прерывания устройства для подключения кАвходу прерывания вычислительной машины, стробирующий выход узла прерывания является синхровыходом устройства подключения к синхровходу вычислительной машины, при этом выход генератора импульсов соединен с тактовым входом распределителя импульсов и первым тактовым входом блока управления, первый выход которого соединен с запускающим входом распределителя импульсов, первый, второй, третий тактовые выходы кото- рого соединены с входами записи, считывания и первым синхровходом блока памяти соответственно, первый адресный вход которого соединен с вторым тактовым входом блока управления и с четвертым тактовым выходом распределителя импульсов, пятый такто

выи выход которого соединен с третьим тактовым входом блока управления, вход логического условия которого соединен с выходом переполнения бло- ка памяти, информационный выход которого соединен с информационным входом блока переключения режима, так- товый вход которого соединен с первым установочным входом узла прерыва- ния, с вторым синхровходом блоки памяти и с вторым выходом блока управления, третий выход которого соединен с вторым адресным входом блока памяти и со счетным входом узла прерывания, стробирующий вход которого соединен с четвертым выходом блока управления, пятый выход которого соединен с вторым установочным входом узла прерывания и с тактовым входом блока анализа информации, выход обнаружения которого соединен с разрешающим входом узла прерывания, первая группа входов логических условий которого соединена с первой группой выходов логических условий блока анализа информации, вторая группа выходов логических условий соединена с первой группой вхо- дов логических условий блока переключения режима, с второй группой входов логичес ких условий узла прерывания и с группой входов логических условий блока выдачи информации, тактовый и информационный входы которого соединены с тактовым и информационным вы- ходами блока переключения режима соответственно, вторая группа входов логических условий и группа информационных выходов которого соединены с третьей группой выходов логических условий и с второй группой информационных входов блока анализа информации соответственно, выход пуска которого соединен с входом пуска блока управления, причем блок управления содержит .счетчик, дешифратор, шесть триггеров, шесть элементов И, четыре элемента ИЛИ, два элемента НЕ, причем первый вход первого элемента ИЛИ соединен с первым входом второго эле- мента ИЛИ и является входом начальной установки блока управления, первый вход первого элемента И соединен с единичным входом первого триггера и является синхровходом блока управ- ления, первый вход второго элемента И является разрешающим входом блока управления, первый вход третьего элемента ИЛИ является первым тактовым входом блока управления, первый вход

11

четвертого элемента ИЛИ является вторым тактовым входом блока управления, второй вход первого элемента ИЛИ соединен с нулевым входом пер- вого триггера, с единичным входом второго триггера и является третьим тактовым входом блока управления, информационный вход третьего триггера является входом логического условия блока управления, второй вход четвертого элемента ИЛИ соединен с единичным входом четвертого триггера и является входом пуска блока управления,

выход третьего элемента И является первым выходом блока управления,

первый и второй выходы дешифратора являются вторым и третьим выходами блока управления соответственно, третий выход дешифратора соединен с синхро- входом третьего триггера, с первым входом четвертого элемента И и является четвертым выходом блока управления, четвертый выход дешифратора соединен с вторым входом второго элемента И, с синхровходом пятого триг- гера и является пятым выходом блока управления, при этом в блоке управления выход первого триггера соединен с вторым входом первого элемента И,

1

выход которого соединен с информацион-30 второго, третьего коммутаторов режиным входом пятого триггера и с первым входом третьего элемента И, второ выход которого соединен с выходом первого элемента НЕ, вход которого соединен с первым входом пятого эле- MeH Va И и с выходом шестого элемента И, первый и второй входы которого соединены с выходами третьего и пятого триггеров соответственно, единичные входы которых соединены с выходами первого элемента ИЛИ, нулевой вход пятого триггера соединен с нулевым входом третьего триггера, с выходом четвертого элемента ИЛИ, с втррым входом второго элемента ИЛИ, вы- 45 с первым, вторым, третьим информационными входами первого, второго, третьего и четвертого .коммутаторов знака соответственно, информационные выходы первого, второго, третьего коммутаторов знаков соединены с вторыми информационными входами первого, второго, третьего коммутаторов режима соответственно, информационные выходы которых соединены с информа- 55 ционнЕ1ми входами второго, третьего, четвертого сдвиговых регистров соход которого соединен с вторым входом пятого элемента И, выход которого соединен с нулевым входом счетчика и с входом второго элемента НЕ, выход которого соединен с вторым входом50

третьего элемента ИЛИ, выход которого соединен со стробирующим входом дешифратора и счетным входом счетчика, первый и второй разрядные выходы которого соединены с первым и вторым информационными входами дешифратора

соответственно, разрешающий вход кото- ответственно, управляющий вход второ- рого соединен с выходом шестого триг- го коммутатора режима соединен с вы- гера и с вторым входом второго элемен- ходом элемента И, соответствующий

tO

15

209199412

та И, выход которого соединен с нулевым входом четвертого триггера и с нулевым входом шестого триггера, единичный вход шестого триггера соединен с выходом четвертого элемента И, второй вход которого соединен с выходом четвертого триггера, выход второго элемента ИЛИ соединен с нулевым входом второго триггера, блок переключения режима содержит четыре сдвиговых регистра, четыре коммутатора знака, три коммутатора режима, элемент И, при этом каждый коммутатор режима содержит три элемента И-НЕ и элемент НЕ, причем группы информационных выходов первого, второго, третьего и четвертого сдвиговых регистров образуют группу информационных выходов блока переключения режима, группа входов элемента И образует первую группу Iвходов логических условий блока переключения режима, группы управляющих входов первого, второго, третьего и четвертого коммутаторов энака образуют вторую группу входов логических условий блока переключения режима, информационный вход первого сдвигового регистра соединен с первыми информационными входами первого.

ма и является информационным входом блока переключения режима, тактовый вход первого сдвигового регистра соединен с тактовыми входами второго, третьего, четвертого сдвиговых регистров и является тактовым входом и тактовым выходом блока переключения режима, информационный выход четвертого коммутатора знака является информационным выходом блока пере- -ключения режима, а при этом первые, вторые, третьи информационные выходы первого, второго, третьего и четвертого сдвиговых регистров соединены

13

вход группы входов которого соединен с управляющими входами первого и третьего коммутаторов режима, при этом в каждом коммутаторе режима первые входы первого и второго элементов И-НЕ являются первым и вторым информационными входами коммутатора режима, выход третьего элемента И-НЕ является информационным выходом коммутатора режима, вход элемента НЕ соединен с вторым входом второго элемента И-НЕ и является управляющим входом коммутатора режима, причем в коммутаторе режима выход элемента НЕ соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, блок анализа информации содержит четыре регистра масок, четыре регистра эталонов, три дешифратора, четыре элемента сравнения, четыре группы элементов И, регистр совпадений, дешифратор совпадений, регистр управления, причем группы информационных входов первого, второго, третьего, четвертого регистров масок первого, второго, третьего, четвертого регистров эталонов, регистра управления и группа информационных выходов регистра совпадения образуют группу входов-выходов логических условий блока анализа информации, груп пы информационных входов первого, второго и третьего дешифраторов об- разуют первую группу информационных входов блока анализа информации, первые входы элементов И первой, второй, третьей и четвертой групп образуют вторую группу информационных входов блока анализа информации, первая и вторая группы информационных выходов регистра управления образуют первую и вторую группы выхо , --

9199Д14

дов логических условий соответствен- третья группа информационных выШ

15

20

25

30

35

40

45

но,

ходов регистра управления соединена с группой управляющих входов дешифратора управления и образует третью группу выходов логических условий блока анализа информации, выход дешифратора совпадения и вход чтения регистра совпадения являются выходом обнаружения и тактовым входом блока анализа информации соответственно, первый выход первого дешифратора соединен с входом записи регистра управления и является выходом пуска блока анализа информации, при этом в блоке анализа информации второй выход первого дешифратора соединен с входом записи регистра совпадений, первый, второй, третий и четвертый информационные входы которого соединены с первым, вторым, третьим и четвертым информационными входами дешифратора совпадений и с выходами первого, второго, третьего и четвертого элементов сравнения соответственно, первые группы входов которых соединены с выходами элементов И первой, второй, третьей и четвертой групп соответственно, вторые входы которых соединены с группами информационных выходов первого, второго, третьего и четвертого регистров масок соответственно, входы записи которых соединены с первым, вторым, третьим, четвертым выходами второго дешифратора соответственно, вторые группы входов первого, второго, третьего, четвертого элементов сравнения соединены с группами информационных выходов первого, второго, третьего, четвертого регистров эталонов соответст-, венно, входы записи соедине- ,ны с первым, вторым, третьим, четвертым выходами третьего дешифратора ,

U2.2

Г

ОЯ}$

Kt

чв

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для контроля и диагностики радиоэлектронной аппаратуры | 1986 |

|

SU1432463A1 |

| Многоканальный временной коммутатор | 1988 |

|

SU1647922A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения двух электронных вычислительных машин (ЭВМ) | 1983 |

|

SU1265781A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

Изобретение относится к области обработки цифровых данных, поступающих из каналов связи, и может быть использовано, в частности, в устройствах приема и обработки дискрет ных сообщений на базе ЭВМ. Целью изобретения является увеличение эффективности за счет предварительной обработки информации. Устройство содержит генератор импульсов, блок памяти, блок анализа информации, блок выдачи информации, распределитель импульсов, блок переключения режима, блок управления, узел прерывания. 7 ил. с S со to со ;о со 4

От 6

От 6

Фиг.

mS emS ofnJ

Kt,S

от}

HS;i

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения цифровой вычис-лиТЕльНОй МАшиНы C КАНАлАМи СВязи | 1979 |

|

SU840876A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-07-08—Подача