счетчика подключены соответственно к первому и второму входам третьего элемента И, выход которого подключен к второму входу первого элемента ИЛИ, вторые входьг первого и второго элементов И объединены и подключены к выходу третьего элемента задержки, вход которого объединен е входом третьего счетчика и подключен к четвертому входу устройства, выход второго элемента И подключен к второму входу второго элемента ИЛИ, выход которого является вторым выходом устройства,

2. Устройство по п. 1, о т л и чаюп;ееся тем, что блок управления содержит триггер, элементы задержки, элементы И и элементы ИЛИ, выход первого элемента ИЛИ через последовательно соединенные первый, второй и элементы задержки подключены к первым входам первого и второго элементов И, выход первого элемента И непосредственно, а выход второго элемента И через четвертый элемент задержки подключены соответственно к первому и второму входам второго элемента ИЛИ, выходы триггера подключены к вторым входам первого и второго элементов И, первые и вторые входы первого элемента РШИ и триггера объединены и подключены соответственно к первому и второму входам блока управления, выход первого элемента задержки, выход второго элемента задержки, выход второго элемента ИЛИ, выход второго элемента И, ,первый выход триггера и второй вхо первого элемента ИЛИ являются соответственно первым - шестым выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия и накопления графической информации | 1983 |

|

SU1164763A2 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1241281A1 |

| Устройство для регистрации информации | 1989 |

|

SU1603412A1 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1988 |

|

RU1637638C |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для формирования графической информации | 1982 |

|

SU1068982A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

1. УСТРОЙСТВО ДЛЯ СЖАТИЯ И НАКОПЛЕНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ, содержащее первый регистр, выходы которого подключены к информационньт входам дешифратора адреса, выходы которого подключены к первьт входам блока памяти, выходы которого подключены к информационным входам первого блока усилителей, выходы которого подключены к первым входам второго регистра, первые вькоды которого подключены к первым выходам устройства, вторые выходы второго регистра подключены к первым информационным входам второго блока усилителей, выходы которого подключены к вторым входам блока памяти, блок управления, первый, второй, третий, четвертый, пятый и шестой выходы которого подключены соответственно к управляющие входам первого регистра, дешифратора адреса, второго и первого блока усилителей и второго регистра, первый вход блока управления подключен к первому входу устройства, отличающееся тем, что, с целью упрощения устройства, в него введены элементы И, элементы ИЛИ, элемент НЕ, элементы задержки, счетчики, блокА, элементов И, блок элементов ИЛИ, третий регистр, входы которого являются входами устройства, выходы третьего регистра подключены к вторым информационным входам второго регистра и первым входам первого элемента ИЛИ, выход которого подключен к первому входу первого элемента И и через эле,мент НЕ к первому входу второго элемента И, выход первого элемента И 8 подключен через первый элемент задержки к третьему управляющему входу Г второго регистра, первому входу первого счетчика, управляющему входу третьего регистра и первому входу второго элемента ИЛИ и через второй счетчик к информационным входам первого блока элементов И и через второй со элемент задержки к второму входу блоО) ка управления и стробирующему входу О) первого блока элементов И, выходы первого и второго блоков элементов И СП через блок элементов ИЛИ подключены, к информационным входам первого регистра, стробирующий и информационные входы второго блока элементов И подключены соответственно к первому и третьему входам устройства, первые выходы первого и третьего счетчика подключены соответственно к третьим и четвертым информ 1ционным входам второго регистра, второй выход третьего счетчика подключен к второму входу, первого счетчика, второй выход первого счетчика и третий вход третьего

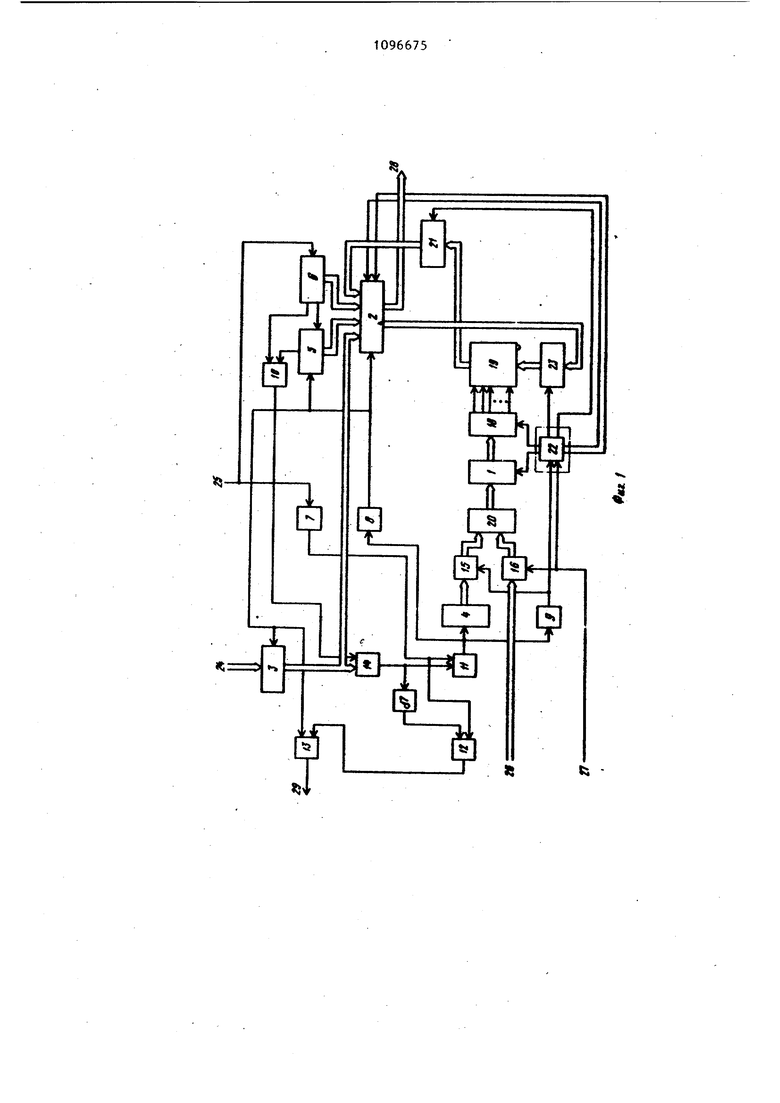

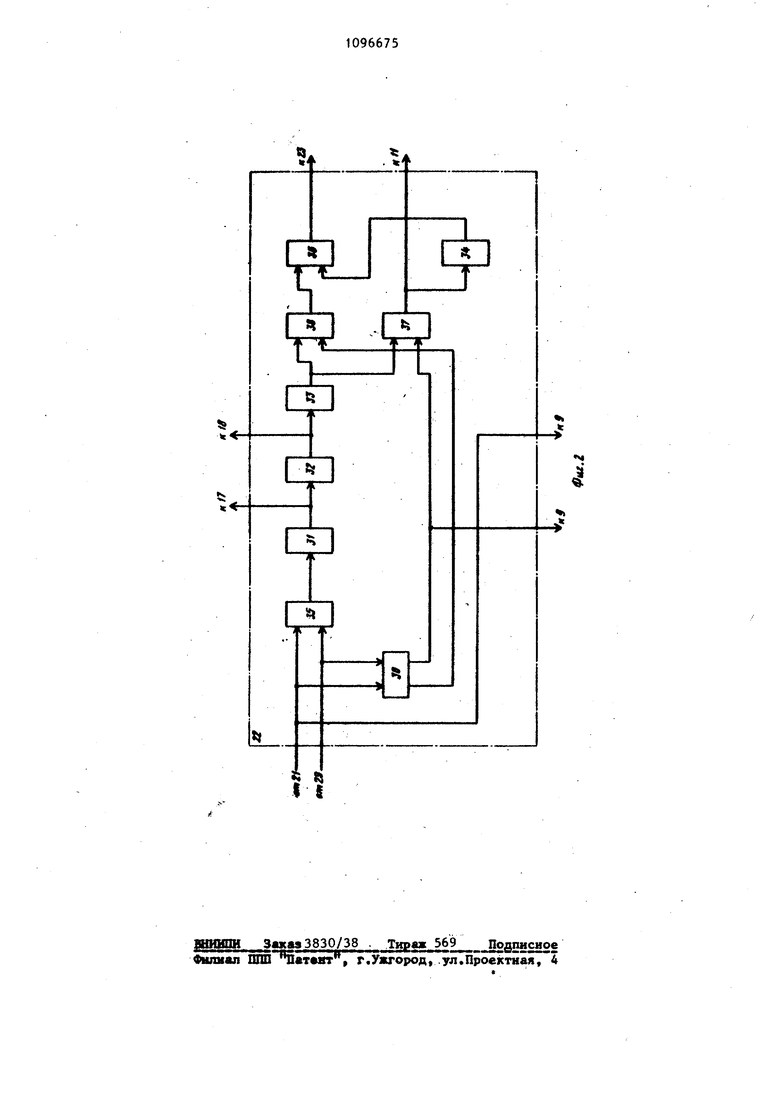

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах отображения информации. Известно устройство для отображеНИН графической информации на экране электроннолучевой трубки, содержащее три блока памяти, четыре многоразряд ных сдвигающих регистра, три элемент И, три счетчика и тактовый генератор Устройство воспроизводит графическую информацию, сжатую предварительно с помощью четырехкаскадного самоадап тирующего одномерного блочного кодирования f 1. Недостатком устройства является слабая защита от ошибок, обусловленная применяемым методом сжатия графической информации. Так при случайном искажении даже одного бита, записанного в четвертом, третьем, втором регистрах или третьем, втором блоках памяти, все графическое изображение может неузнаваемо исказиться Кроме того, недостатком устройства является его сложность, обусловле ная необходимостью использования для запоминания графической информации трех блоков памяти и четырех многоразрядных сдвигающих регистров. Наиболее близким к изобретению по технической сущности является устройство для хранения информации, содержащее последовательно соединенные регистр адреса, блок адресной выборки с дешифратором кода адреса, запоминающий массив, блок усилителей считывания (БУС), информационный регистр, блок усилителей записи (БУЗ), соединенный с вторым входом запоминающего массива, блок управления памятью 2 3КаХдому элементу разложенная графического изображения на экране ЭЛТ в оперативном запоминающем устройстве (ОЗУ) однозначно соответствует одна ячейка ДJIя хранения одного бита 3 . В то же время известно из статистических измерений, что в любом графическом изображении фон, кодируемый одними нулями и не несущий никакой информации, составляет обычно не менее 90%, а элементы изображений имеют корреляционную зависимость, т.е. сгруппированы обычно, а не разбросаны хаотично Г ЗНедостатком известного устройства является большой объем ОЗУ, необходимый для записи информационного рельефа экрана ЭЛТ, имеющего большую избыточность. 31 Цель изобретения - упрощение устройства путем сокращения объема памя ти. Поставленная цель достигается тем, что в устройство для сжатия и накопления графической информации, содержащее первый регистр, выходы которого подключены к информационным входам дешифратора адреса, выходы ко торого подключены к первьп входам блока памяти, выходы которого подклю чены к информационным входам первого блока усилителей, выходы которого подключены к первым входам второго регистра, первые выходы которого под ключены к первым выходам устройства, вторые выходы второго регистра подключены к первым информационным входам второго блока усилителей, выходы которого подключены к вторым входам блока памяти, блок управления, первый, второй, третий, четвертый , пятый и шестой выходы которого подключены соответственно к управляющим входам первого регистра, дешифратора адреса, второго и первого блока усилителей и второго регистра, первый вход блока управления подключен к первому входу устройства, введены элементы И, элементы ИЛИ, элемент НЕ 1, блоки элементы задержки, счетчики, блоки элементов И, блок элементов ИЛИ, третий регистр, входы которого являются входами устройства, выходы третьего регистра подключены к вторым информационным входам второго регистра и первым входам первого элемента ИЛИ, выход которого подключен к первому входу первого элемента И и череэ элемент НЕ к первому входу второго элемента И, выход первого элемента РГ подключен через первый элемент задержки к третьему управляющему входу второго регистра, первому, входу первого счетчика, управляющему входу третьего регистра и первому входу, второго элемента ИЛИ и через второй счетчик к информационным входам первого блока элементов И и через второй элемент задержки к второму входу блока управления и стробирующему входу первого блока элементов И, вькодьр первого и второго блоков элементов И через блок элементов ИЛИ подключены , к информационным входам первого регистра, стробирующий и информационные входы второго блока элементов И подключены соответственно к первому и 5 третьему входам устройства, первые выходы первого и третьего счетчика подключены соответственно к третьим и четвертым информационным входам второго регистра, йторой выход третьего счетчика подключен к второму входу первого счетчика, второй выход первого счетчика и третий выход третьего счетчика подключены соответственно к первому и второму входам третьего элемента И, выход которого подключен к второму входу первого элемента ИЛИ, вторые входы первого и второго элементов И объединены и подключены к выходу третьего элемента задержки, вход которого объединен с входом третьего счетчика и подключен к четвертому входу устройства, выход второ го элемента И подключен к второму входу второго элемента ИЛИ, выход которого является .вторым выходом устройства. Кроме того, блок управления содержит триггер, элементы задержки, элементы И и элементы ИЛИ, выход первого элемента ИЛИ через последовательно соединенные первый, второй и третий элементы задержки подключены к первым входам первого и второго элементов И, выход первого элемента И непосредственно, а выход второго элемента И через четвертый элемент задержки подключены соответственно к первому и второму входам второго элемента ИЛИ, выходы триггера подключены к вторым входам первого и второго элементов И, первые и вторые входы первого элемента ИЛИ и триггера объединены и под-/ ключены соответственно к первому и второму входам блока управления, выход первого элемента задержки, выход второго элемента задержки, выход второго элемента ИЛИ, выход второго элемента И, первый выход триггера и второй вхэд первого элемента ИЛИ являются соответственно первым - шестым выходами блока управления. За счет введения указанных элементов и связей между ними устройство позволяет уменьшить в среднем в 3 раза требуемый объем ОЗУ. Информация формируется и хранится в ОЗУ по каждому адресу в виде 16-разрядных кодограмм. Их этих 16 разрядов 8 разрядов несут информацию о коде подсвета ненулевых (нефоновых) участков строк длиной в 8 элементов разложения изображения . В каждой телевизионной строке при растровом методе разввертки обычно можно получить 400-500 элемен тов разложения изображения. Для удоб ства выберем число элементов разложения равным 448i В этом случае на одной строке уместится 56,8-разрядны кодов подсвета. Дпя того, чтобы можн было адресовать любой из этих 56 участков, необходимо минимум 6 двоич ных разрядов, поскольку число различ ных комбинаций из 6 двоичных разрядо равно 2 - 64. Поэтому 6 разрядов в 16-разрядных кодограммах отводится на адресацию ненулевого 8-разрядного кода подсвета в строке. Два оставших ся разряда кодограммы предназначены для адресации строки, в которой находится отображаемый 8-разрядный ненулевой блок информации, относительн текущей отображаемой строки. С помощью 2-х разрядов возможно адресовать 2 4 строки относительно текущей строки. Для определенности в устройстве принята следующая адресация строк относительно текущей строки: комбинация 00 означает, что соответствующий 8-разрядный код подсве та находится в текущей строке, комбинация 01 означает, что ненулевой 8-разрядный блок информации находится в следующей строке, комбинация 10 означает, что соответствующий 8-разрядный блок информации находится во второй относительно текущей строке, комбинация 11 означает, что соответствующий 8-разрядный ненулевой блок информации находится в последующей третьей по счету строке относительно текущей строки. Таким образом, по каждому адресу в ОЗУ хранится 8-битовой ненулевой информационный код подсвета и 8-разрядный адрес этого кода подсвета в любом из 56x4 мест очередных 4-х строк. При этом 6 разрядов из 8 разр дов адреса указывает положение 8разрядного блока в строке, а 2 разря да адресуют одну из 4-х очередных строк относительно строки, которая адресовалась предыдущей 16-разрядной кодограммой. Допустим, в первых 4-х строках одна нулевая информация (фон а ненулевая информация только в 5-й строке. В этом случае в виде исключения адресуется и записываетс г в память в 4-й строке последний .нулевой 8-разрядный блок информации, а следующая 16-разрядная кодограмма будет уже адресовать первый ненулевой 8разрядный блок информации в 5-й строке относительно 4-й. В этом случае 5-я строка будет второй относительно четвертой и адресация,, следовательно, ее возможна. Вероятность того, что 8-разрядный блок графической информации будет состоять из одних нулей, равна (0).Р (0/0)7, (О Р (Oj 8,1) Р где Р (0) вероятность того, первый элемент 8-разрядного блока нулевой-, Р(0/0) - условная вероятность того, что текущий элемент 8-разрядного блока графической информации является нулевым при предыдущем нулевом элементе. Тогда вероятность того, что 8-разрядный блок графической информации является, ненулевым равна Р (0; 8,1) 1 -Р (0)-Р (0/0).(2) Если эта вероятность равна к примеру 1/10, то это означает, что 9/10 графического изображения составляет фон, который в ОЗУ в предлагаемом устройстве не записьгоается. Следовательно, требуемьгй объем ОЗУ для записи ненулевых блоков будет в этом случае в 10 раз меньше, т.е. коэффициент выигрыша в объеме памяти вычисляется по следующей формуле: - Р (0) Р (0/0). Сомножитель 2 добавлен вследствие того, что на каждые 8 информационных разрядов в устройстве приходится 8 адресных разрядов. Для типичньк графических изображений, п реденных в C4jj приведены вероятности Р (0) и Р (6/0) Несмотря на то, что в 4 на с. 22 изображен печатный и прописной текст, а также довольно насыщенные различного рода линиями географические ландшафты, средние значения вероятностей получились Р (0) 0,933; Р (ОД)) 0,983 и, соответственно, средний коэффициент выигрыша в объеме памяти, полученный для этих изображений по формуле (3), равен 3. Путем машинного моделирования были опробованы различные длины информационных блоков с адресами и определено, что наибольший коэффициент выигрыша в объеме памяти получается в случае,, описанном выше, когда длина информационного блока равна 8 разрядам и соответственно 8 разрядам равен адрес блока. При этом адресация 8-разрядного кода плдсвета в 4-х текущих строках вполне достаточна, поскольку вероятность того, что в очередных 4-х текущих строках графической информации будут одни нули, равна :Р{01448-4,-1) Р(0)Р( (1 Для вьшеуказанных значений Р (0) 0,933 и Р (О/О) 0,983 эта вероятность к примеру равна 0,2 103 т.е. пренебрежимо мала. На фиг. 1 представлена функционал ная схема предлагаемого устройства; на фиг. 2 - функциональная схема бло ка управления. Устройство содержит регистры 1, 2 и 3, счетчики 4-6, элементы задержки 7-9, элементы И 10-12, элементы ИЛИ и 14, блоки 15 и 16 элементов И, элемент НЕ 17, дешифратор 18 адреса, блок 19 памяти, блок 20 элементов ИЛИ, блок 21 усилителей считьтания (БУС), блок 22 управления, блок 23 усилителей записи (БУЗ), входы 24-27 выходы 28 и 29. Блок управления содержит триггер 30, элементы 31-34 задержки, элементы ИЛИ 35 и 36, элементы И 37 и 38. Устройство pa6oTaet следующим образом. Рецепторная матрица графического изображения в соответствии с растровой разверткой последовательно записывается в виде 8-разрядных блоков через первую группу входов 24 устрой ства в регистр 2. Запись происходит параллельно во все 8 ячеек регистра 3. На входе 25 при этом появляется единичный сигнал, свидетельствующий о том, что очередной блок графической информации записан в регистр 3. Этот сигнал поступает на вход элемен та 7 задержки и на счетный вход счет чика 6, который под воздействием данного сигнала изменяет свое значение на единицу. Если устройство находится в начальном состоянии, при котором значение счетчика 5 равно 3, а значение счетчика 6 равно 55., то под воздейст вием импульса с входа 25 обнуляется счетчик 6 и на его втором одиночном выходе появляется импульс переноса, KOTOpbM обнуляет счетчик 5. Импульсный сигнал приема информации с входа 25 задерживается элементом 7 задержки на время, необходимое для изменения значений счетчика 5 и счетчика 6 и после этого поступает на второй вход элемента И 11 и второй вход второго элемента И 12. Допустим первый же записанный блок графической информации в регистре 3 содержит ненулевую информацию. В этом случае на выходе элемента ИЛИ 14 будет единичный сигнал, поступающий на вход элемента НЕ 17 и на первый вход элемента И 11. При наличии единичного потенциального сигнала на первом входе элемента И 11 и единичного импульсного сигнала на втором его входе (с выхода элемента 7 задержки) на выходе элемента И 11 будет единичный импульсный сигнал. В этом случае .на выходе элемента НЕ 17 единичный сигнал будет отсутствовать и импульс с -выхода элемента 7 держки не пройдет через элемент И 12 Единичный импульсный сигнал с выхода элемента И 11 поступает на входы элемента 8 задержки и элемента 9 задержки, а также на счетный, вход счетчика 4 адреса. По этому сигналу происходит увеличение значения счетчика 4 адреса на единицу. После этого, на выходе элемента 9 задержки появляется единичный импульсный сигнал, разрешаю щий прохождение сигналов кода адреса с выхода счетчика 4 через первый блок 15 элементов И на первую группу входов блока 20 элементов ИЛИ и инициирующий цикл обращения к памяти. По этому сигналу, поступающему на ход блока 22 управления (БУП), генерируется последовательность управляющих сигналов, подаваемых на отдельные уэлы памяти. При этом, сигнал Запись с выхода элемента 9 задержки поступает на первый вход БУИ 22, устанавливает R -5 -триггер 30 в нулевое состояние, поступает на пятый выход БУП, соединенный с вторым одиночным входом регистра 2, через элемент ИЛИ 35 и элемент 31 задержки поступает на первый выход БУП, соединенный с одиночным входом регистра 1, через элемент 32 задержки поступает на второй выход БУП, соединенный с одиночным входом дешифратора 18 адреса, через элемент 33 задержки, первый элемент И 38 и элемент ИЛИ 36 поступает на третий выход БУП, соединенный с одиночным входом ВУЗ 23. По разрешающему сигналу с первого выхода БУП 22 осуществляется прием кода адреса с группового -выхода блока 20 элементов ИЛИ в регистр 1. По разрешающему сигналу с пятого выхода БУП 22 осуществляется занесение 8разрядного блока графической информа ции в старшие разряды 16-разрядного регистра 2 и значений (в данном случае нулевых) счётчика5 и счетчика 6 в младшие разряды регистра 2, что соответствует записи первого ненулев го блока в строке с адресом 00. При этом происходит вьщача данной информ ции на первую группу выходов регистра 2. После этого по разрешающему сигналу с второго выхода БУП 22 дешифратор 18 адреса дешифрирует код адреса, поступающий с группового вы|хода регистра 1, формирует в соответ ствующей ячейке блока 19 памяти сиг. нал считывания, по которому осуществ ляется считывание слова в ячейке и, следовательно, очистка данной ячейки При этом на БУС 21 не вьщается сигнал с четвертого выхода БУП 22, что блокирует усилители считывания, и в регистр 2 информация с БУС 21 не пос тупает. По разрешающему сигналу с Третьего выхода БУП 22 БУЗ 23 осуществляет запись информации с первой группы выходов регистра 2 в выбранну ячейку запоминакндего массива (ЗМ) блока 19 памяти. После записи информации в ЗМ на вькоде элемента 8 задержки появляется единичный импульсный сигнал, обнулякнций регистр 2, регистр 3, счетчик 5 и поступающий на первый вход элемента ИЛИ 13. На выходе данного элемента, являющемся выходом 29 устройства, единичный импульсный сигнал воспримется как сигнал готовности устройства к приему следунмцего 8-раз рядного блока графической информации Если устройство находится в рабочем состоянии, при котором значение счетчика 5 равно 3, а значение счетчика 6 равно 54, то с приходом на вход 25 устройства импульсного сигнала, сигнализирующего о записи оче ;редного байта графической информации в регистр 3, значение счетчика 6 устанавливается равным 55 и на его одиночном выходе появляется единичный пртенциапьный сигнал, поступающий на перв вход элемента И tO. Так как значение счетчика 5 равно 3, то на его одиночном выходе также убудет eдиничньD потенциальный сигнал. В этом случае на выходе элемента И 10 появляется единичный потенциальный сигнал, который поступает на одиночный вход элемента ИЛИ 14, ас его выхода далее проходит по тем же цепям, как было рассмотрено выше, и инициирует запись байта графической информации, даже если он нулевой. В младшие 8 разрядов регистра 2 будут записаны значения счетчика 5 и счетчика 6, соответствующие адресу последнего 56-го блока в четвертой строке относительно предьщущей ненулевой строки. После этого Текущей .строке присваивается адрес 00 и адресация последующих блоков графической информации будет осуществляться относительно её. Если устройство находится в рабочем состоянии, при котором значение счетчика 5 не равно 3 одновременно с любым значением счетчика 6, либо значение счетчика 5 равно 3, а значение счетчика 6 равно от нуля до 53-х включительно, то с приходом единичного импульсного сигнала с входа 25 устройства на счетный вход счетчика 6, на выходе элемента И 10 отсутствует единичный потен1Ц альный сигнал. В ЗМ блока 19 памяти записываются в этом случае только ненулевые блоки графической информации с ад ресом, paiBHbiM значению счетчика 5 и счетчика 6, либо если в течение 4-х последукяцих относительно предыдущей ненулевой строки (включая ее) следуют одни нулевые байты, то записьгеается последний байт четвертой строки независимо от того нулевой он или нет. Запись в этом случае необходима для сохранения возможности адресации последующих строк. При записи нулевого 8-раэрядного рецепторного блока графической информации в регистр 3 с группы входов 24 устройства, на выходе регистра 3 останутся нулевые сигналы, поступающие на входь элемента ИЛИ 14 и на первую группу входов регистра 2. Если устройство находится в начальном состоянии, при котором значение счетчика 5 равно 3, а значение счетчика 6 равно 55, то с появлением нютульсного сигнала приема информации на входе 25 устройства обнуляются счетчика 5 и 6. Единичный потенциальный сигнал 111 на выходе элемента (1 10 исче: ает. Та как па входах элемента ИЛИ 14 находятся все нули, то на выходе данного элемента - нулевой сигнал, который поступает на вход элемента НЕ 17, ин вертируется в единичньй потенциальны сигнал на его выходе и поступает на первый вход элемента И 12. Единичньй импульсный сигнал с выхода элемента 7 задержки, поступая на второй вход элемента И 11, не проходит через данный элемент из-за наличия на первом его входе нулевого сигнала, а, поступая на второй вход элемента И 12, проходит через этот элемент и далее проходит через элемент ИЛИ 13 на выход 29 устройства. Появление единичного импульсного сигнала на выходе 29 устройства свидетельствует о готовности устройства к приему сле дующей очередной графической информации. В этом случае запись нулевого блока графической информации в ЗМ в качестве элемента кодограммы не происходит. Если устройство находится при этом в рабочем состоянии, при ко тором значение счетчика 5 не равно 3 одновременно с любым значением сче чика 6 либо значение счетчика 5 равно 3, а значение счетчика 6 равно от нуля до 53 включительно, то с приходом единичного импульсного сигнала с входа 25 устройства на счетный вход счетчика 6, данный счетчик изменяет свое Состояние на единицу, но значения счетчика 5, счетчика 6 и регистра 3 не заносятся в регистр 2 и не записываются в ЗМ, поскольку за писанньй в регистр 3 байт графической информации является нулевым. Н этом случае на выходе элемента И 12, как было показано выше, появляется единичны1Т импульспьй сигнал, проходящий через элемент ИЛИ 13 на выход 23 устройства и свидетельствующий о готовности устройства к приему следующего байта графической информации. Во время записи ненулевых байтов графической информации в ЗМ сигнал Считывание на одиночный вход 27 устройства не поступает. Только после записи всей графической информации в ЗМ может прийти сигнал Считывание, поступающий на одиночный вход 27 одновременно с поступлением параллельного кодя адреса ячеек ЗМ на группу пхсдоп 26 устройства. Сигнал с пхода 21 устройства разрешает прохождоинг Т11 фпрмлии 1 с пхода 26 S устройства через второй блок элем ;нтов И 16 на второй групповой вход блока 20 элементов ИЛИ. Кроме того , сигнал Считывание с входа 27 поступает на второй вход БУП 22 и инициирует цикл обращения к памяти. БЛТ 22 генерирует последовательность управляющих сигналов, ини циирующих считывание информации из ячейки ЗМ по коду адреса,пришедшему на вход 26 устройства. При. этом, сигнал Считывание устанавливаетR-5триггер 30 в единичное состояние, через элемент ИЛИ 35 и элемент 31 задержки поступает на первый выход БУП, соединенный с одиночным входом регистра 1, через элемент 32 задержки поступает на второй вькод БУП, соединенный с одиночным входом дешифратора 18 адреса, через элемент 33 задержки и элемент И 37 поступает на четвертый выход БУП, соединенный с одиночным входом БУС 21, через элемент ЗА задержки и элемент ИЛИ 36 поступает на третий выход БУП, соединенный с одиночным входом БУЗ 23. С прямого выхода R -5-триггера потенциальный единичньш сигнал поступает на шестой выход БУП, соединенный с третьим одиночным входом регистра 2, и разрешает прохождение импульсного сигнала через элемент И 37. По разрушающему сигналу с первого выхода БУП 22 происходит запись кода адреса с группового выхода блока 20 элементов ИЛИ в регистр 1. После этого, по сигналу с второго выхода БУП 22, дешифратор 18 адреса дешифрирует адрес, посыпает сигналы, разрешающие считывание в заданные адресом ячейки ЗМ. При этом код записанного в ячейки слова считывается, а затем усиливается усилителями считывания БУС 21, по разрешающему сигналу с четвертого выхода БУП 22, и передается в регистр 2. Информацию с БУС 21 записывается в регистр 2 и постоянно выдается на первую группу выходов регистра 2, а также на группу выходов, являющуюся группой выходов 28 устройства, по разрешающему сигналу с шестого выхода БУП 22. После этого, в случае памяти с разрушающим считыванием ( при считывании все запоминающие элементы ячеек, хранящих код слова, устанавливАются в нулевое состояние), производится регенерация информации в ячейках путем записи в них из регистра

считанного слова. При этом на одиночньй вход БУЗ 23 подается сигнал с третьего выхода БУП 22, разрешающий запись информации в выбранную ранее ячейку ЗМ. После считывания всей информации из ЗМи устройство считьшайия видеосигналов посьшает сигнал установки в начальное состояние счетчиков 5 и 6, а также обнуления счетчика 4 (сигнал обнуления не показан для упрощения схемы), и вьщает сигнал Конец считывания в устройство пода чи рецепторной матрицы графической информации в регистр 3. После приема этого сигнала устройство подачи рецепторной матрицы.графической информации при наличии новой графической инфррмахщи подает ее по-байтно в регистр 3.

Таким образом, в устройстве запоминаются только ненулевые байты графической информации. Эти байты запоминаются вместе с адресом. Адресация блоков абсолютно-относительная, т.е. щесть разрядов .адресуют абсолютный адрес 8-разрядного блока в строке, а два разряда адресуют адрес строки относительно строки, в которой был предьщущий (ненулевой) блок графической информации, запомненной в устройстве Таким образом, связь между последовательными 16-разрядными кодограммами в устройстве минимальна. При искажении любых битов графической информации искажения минимальны по сравнению с блочным кодированием и общая конфигурация изображения сохраняется. Возможны искажения отдель ых битов в отдельных строках, что на общем фоне обычно из нескольких сот строк, будет сказываться незначительно. При искажении 2-х битов из 16-ти с относительным адресом строки возможен лишь одновременный незначительный сдвиг части изображения по вертикали, что также не нарущит возможность распознавания изображения.

о ....

Эффект от использования изобретения по сравнению с базовым объектом состоит в том, что в среднем в три раза экономится объем памяти для хранения графической информации и время загрузки информационных магистралей под пересылку графической информации .

«ч;

Авторы

Даты

1984-06-07—Публикация

1983-03-24—Подача