Изобретение относится к автоматике, вычислительной технике и может быть использовано в цифровых системах управления, регулирования, контроля для ввода в управляющую ЭВМ информации от двухпозиционных (диcкретных) датчиков, преобразователей информации, характеризующих состояние объекта управления, контроля, а также вывода из ЭВМ информации, определяющей состояния двухпозиционных исполнительных устройств (реле, бесконтактных коммутационных элементов и т.п.), преобразователей информации, с помощью которых осуществляется воздействие на объект управления, регулирования.

Известно устройство для ввода информации [1] содержащее однотипные модули ввода, каждый из которых связан с группой дикретных датчиков. Модуль содержит регистр управляющей информации, которая заносится из ЭВМ, регистр хранения текущих состояний датчиков (эти регистры входят в состав узла маскирования), регистр хранения предшествующих состояний датчиков, анализатор, содержащий схему сравнения, элемент задержки, триггер, логические элементы И и фиксирующий факт изменения состояний датчиков.

Основным недостатком известного устройства является его высокая аппаратная сложность при большом числе датчиков, обусловленная наличием отдельного модуля ввода для каждой группы датчиков. Кроме того, ограничены функциональные возможности устройства: отсутствуют возможность задания длительности "дребезга" контактов, ввода сигналов от датчиков без отстройки от "дребезга", возможность фиксации изменения состояния датчика одного заданного типа (например, перехода из разомкнутого состояния в замкнутое).

Высокоэффективная, с точки зрения затрат оборудования, реализация устройств, требующих выполнения одних и тех же операций по отношению к разным элементам данных (такими элементами данных являются группы сигналов, снимаемые с дискретных датчиков в устройствах ввода информации), может быть получена в результате использования принципа групповой обработки. В соответствии с этим принципом по отношению к отдельным элементам данных в режиме разделения времени циклически выполняется операция обработки, соответствующая фиксированному алгоритму. Для всех элементов данных используются общие аппаратные средства обработки. При использовании этого принципа к аппаратуре предъявляются высокие требования в части быстродействия с целью минимизации временного интервала между последовательными обращениями к одному и тому же элементу данных.

Принцип групповой обработки можно успешно реализовать на основе типовой микропроцессорной системы, состоящей из микропроцессора и подключенных к нему микросхем, реализующих функции хранения информации, сопряжения с управляющей ЭВМ и с объектом управления. В памяти системы хранятся программа обработки, исходные и рабочие данные, результаты обработки. Отдельную микропроцессорную систему можно рассматривать как контроллер, реализующий определенную функцию сопряжения управляющей ЭВМ с объектом управления. Обеспечен доступ управляющей ЭВМ в память контроллера. Присущая микропроцессорным средствам функциональная гибкость позволяет эффективно строить на их основе не только контроллер ввода информации с дискретных датчиков, обладающий широкими функциональными возможностями, но и контроллеры, реализующие функции вывода информации из ЭВМ на исполнительные устройства объекта управления.

Из известных устройств наиболее близка по технической сущности к изобретению однокристальная микроЭВМ 8048 фирмы Intel [2] основными частями которой являются блоки памяти команд и данных и процессор, включающий в себя рабочие (информационные) регистры, арифметико-логический узел (его ядром является интервал кодов), таймер-счетчик (узел отсчета временных интервалов), а также регистр и дешифратор команд, логическая схема условных переходов, схема управления и синхронизации, образующие в целом блок управления. Информационные входы таймера-счетчика, рабочих регистров, блока управления соединены с двунаправленным информационным входом-выходом ЭВМ и информационным входом-выходом блоков памяти. Выходы рабочих регистров соединены с информационными входами арифметико-логического узла, выходы признаков состояния которого подключены к входам блока управления. Выходы блока управления соединены с управляющими входами рабочих регистров, арифметико-логического узла, таймера-счетчика, блока памяти и с выходом устройства.

Недостатком известного устройства является низкое быстродействие, которое обусловлено наличием затрат времени на передачу по информационной шине кодов команд из памяти в блок управления и арифметико-логического узла, реализующего ограниченный набор типовых операций по отношению к восьмиразрядным кодам, что требует выполнения определенных последовательностей команд для реализации специфических операций по отношению к отдельным двоичным разрядам и полям, предусмотренных алгоритмами операций ввода-вывода информации, наличием затрат времени на организацию ветвлений (переходов) в алгоритмах ввода-вывода программными средствами, необходимостью выполнения подпрограммы формирования кода, предназначенного для передачи в управляющую ЭВМ для информирования ее о причине возбуждения инициативного сигнала.

Изобретение направлено на повышение быстродействия процессора устройства за счет эффективной реализации алгоритмов операций ввода-вывода микропрограммными средствами, специализации арифметико-логического узла и обеспечения минимальных временных затрат на формирование кода, информирующего управляющую ЭВМ о причинах возбуждения инициативного сигнала (сигналов).

При использовании изобретения может быть увеличено быстродействие контроллеров, реализующих функции ввода-вывода информации с использованием принципа групповой обработки. Следствием увеличения быстродействия является уменьшение временного интервала между последовательными обращениями к отдельному элементу вводимых-выводимых данных при его обработке, т.е. уменьшение временной задержки при передаче информации от объекта управления к ЭВМ и в обратном направлении. Увеличение быстродействия обусловливает также уменьшение времени реакции управляющей системы на инициативный сигнал от объекта управления. Увеличение быстродействия достигается за счет введения в состав микропроцессора контроллера узла регистрации запросов прерывания, что обусловливает минимизацию временных затрат на формирование кода, информирующего управляющую ЭВМ о причинах возбуждения инициативного сигнала (сигналов), первого и второго формирователей кодов, группы элементов ИЛИ, формирователя кода адреса памяти, первого и второго блоков ключей, первого и второго счетчиков адресов массивов, коммутатора, регистра номера адреса массива, что обеспечивает высокую эффективность реализации алгоритмов операций ввода-вывода.

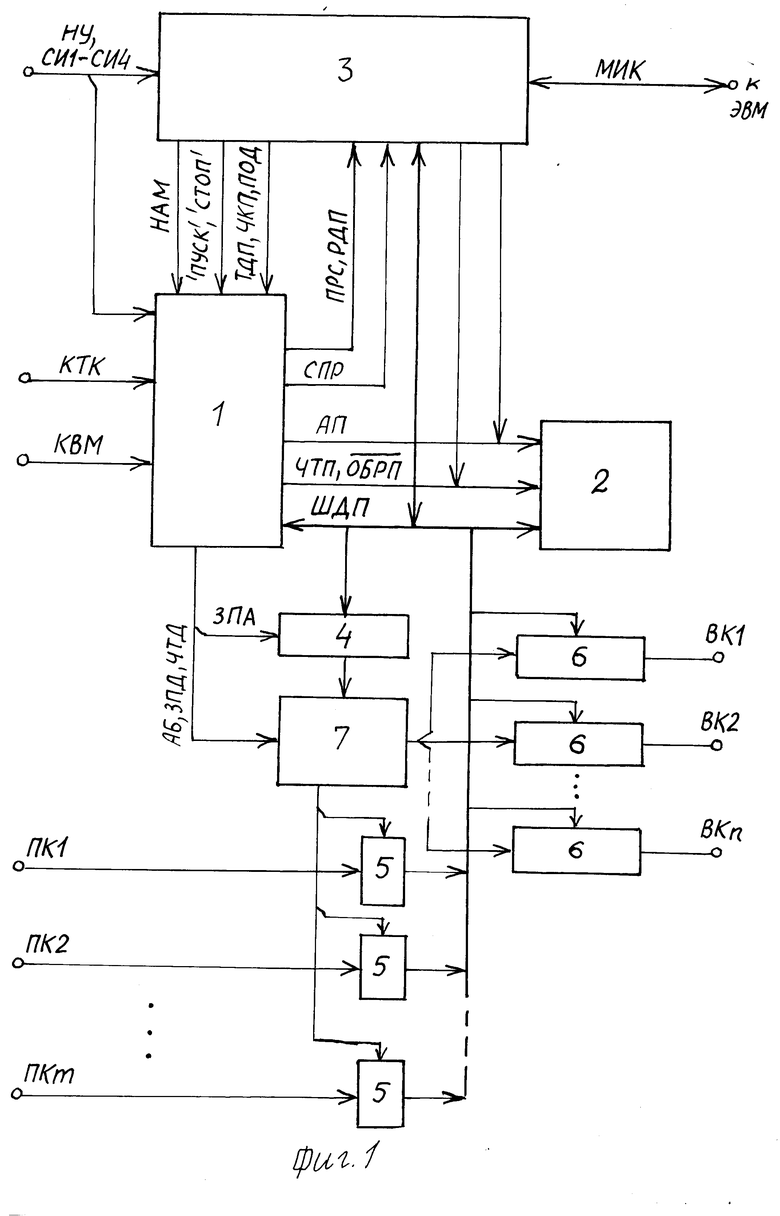

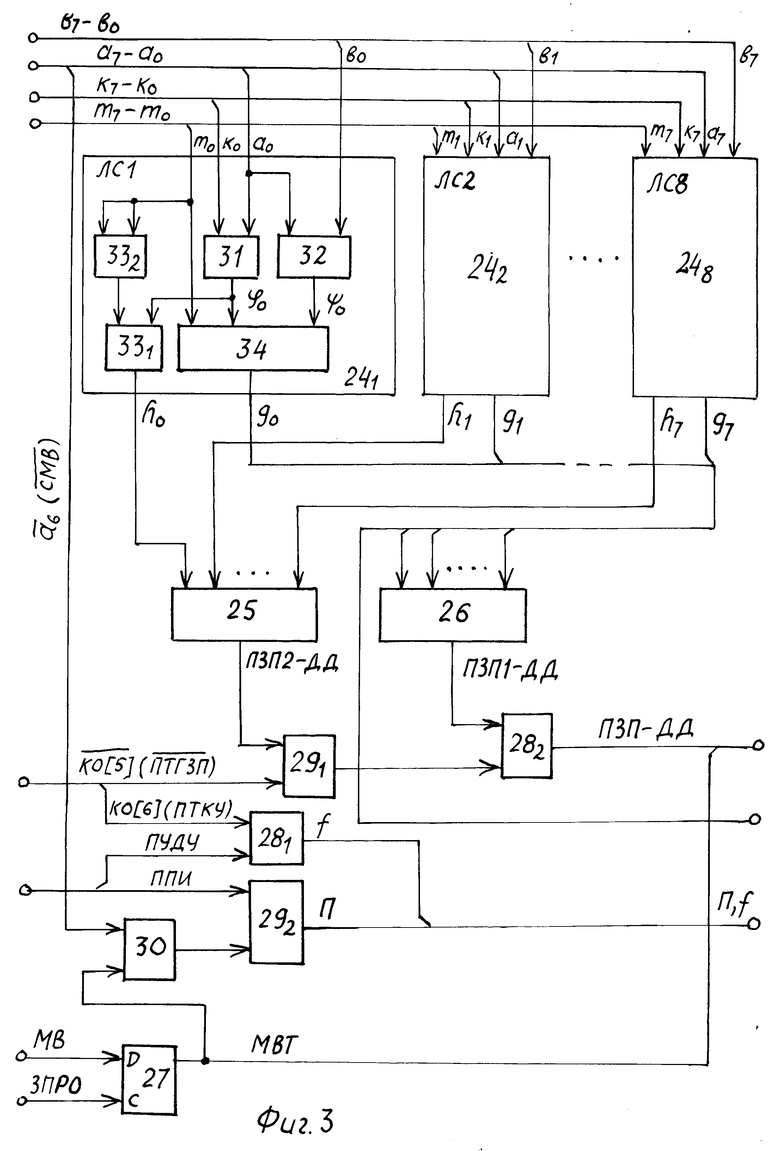

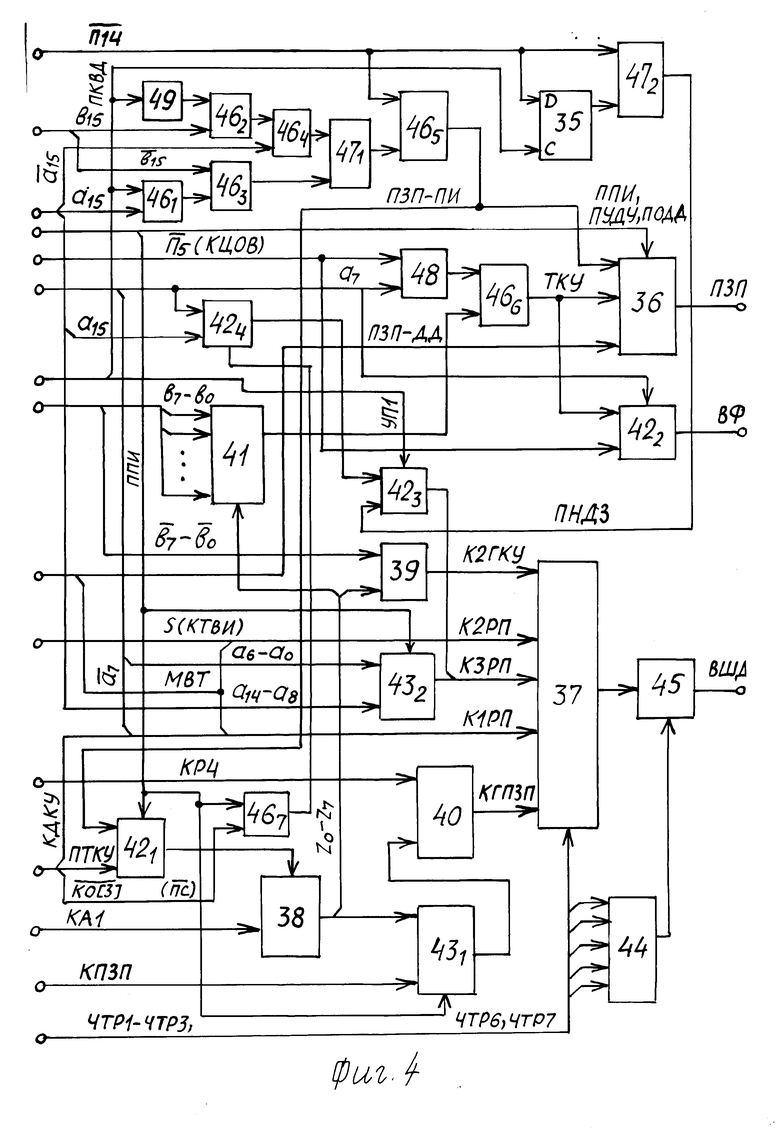

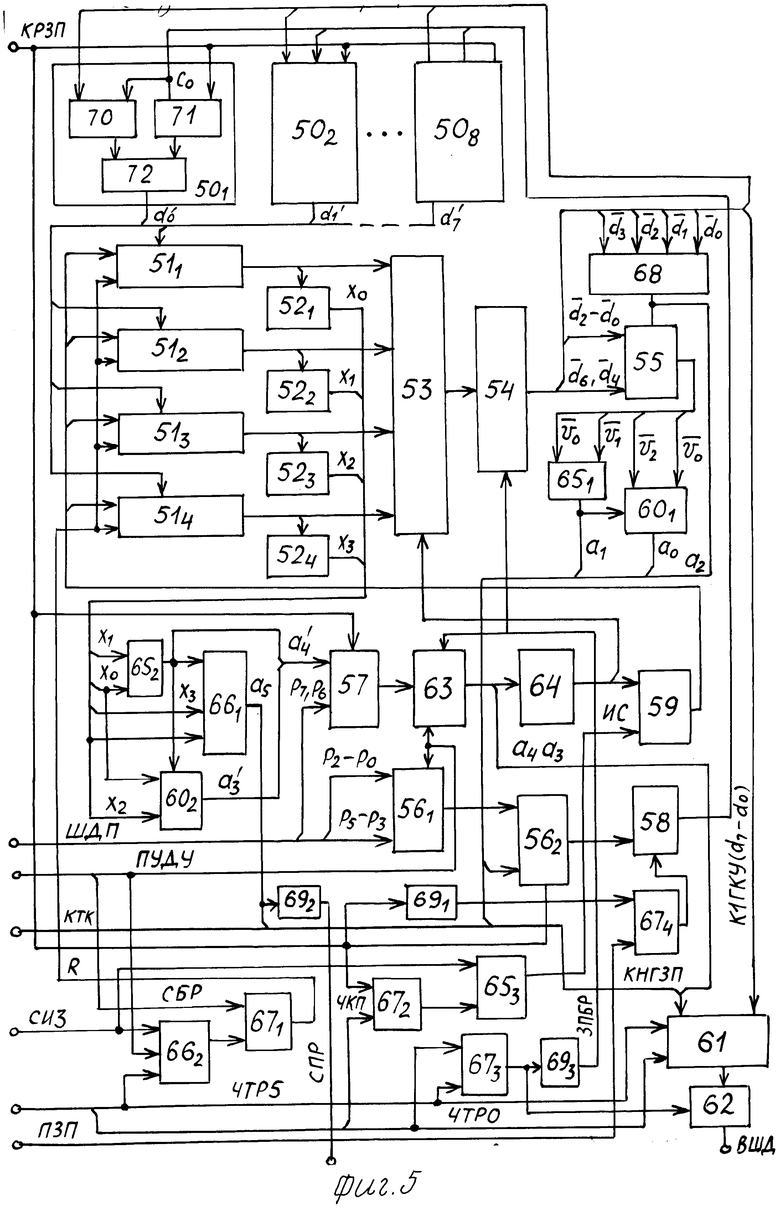

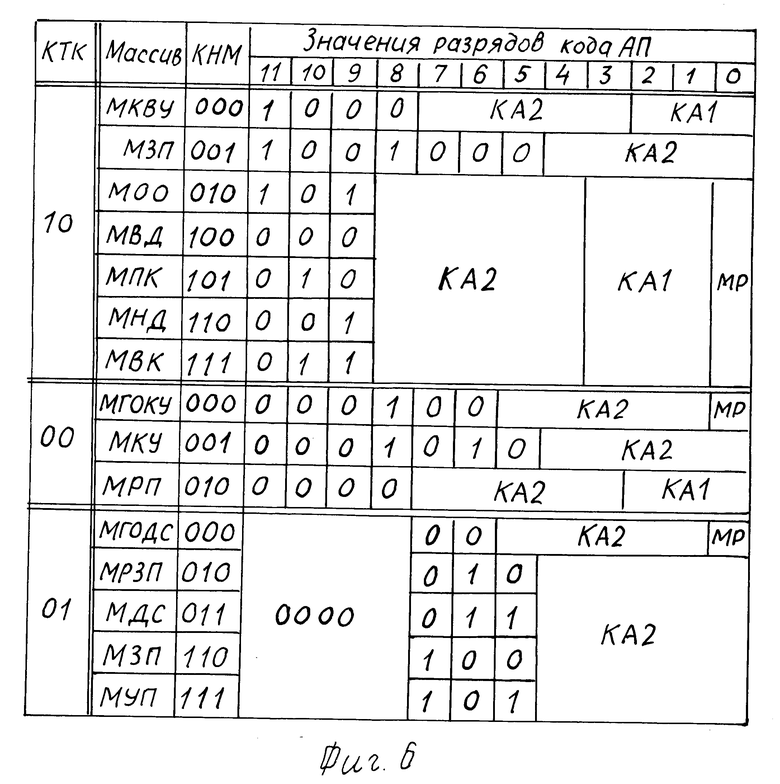

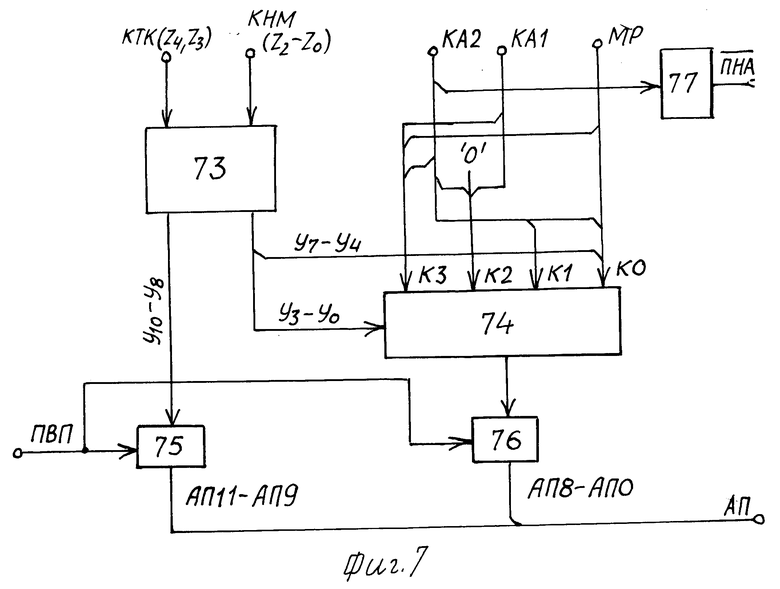

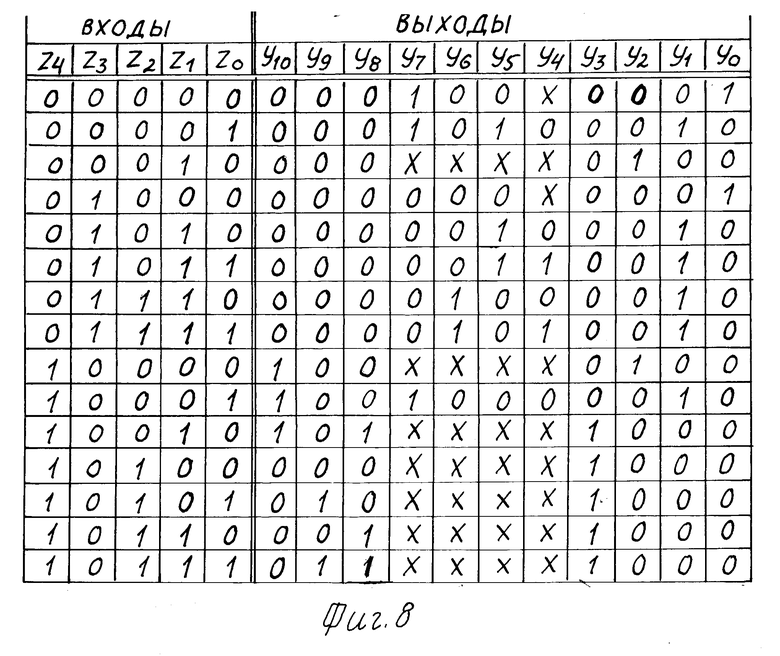

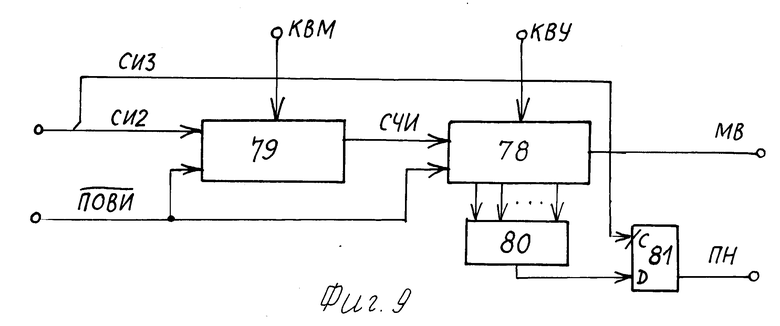

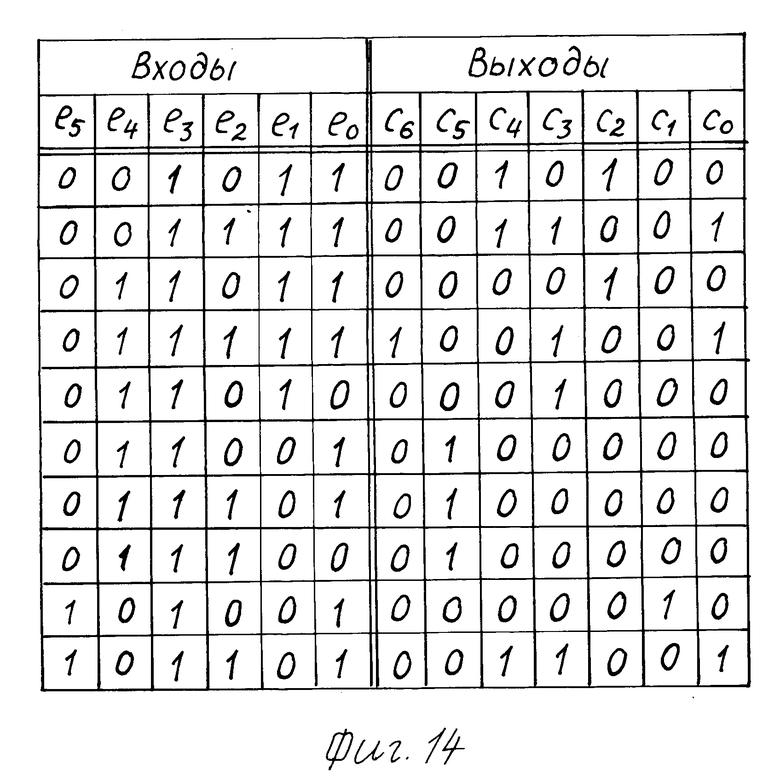

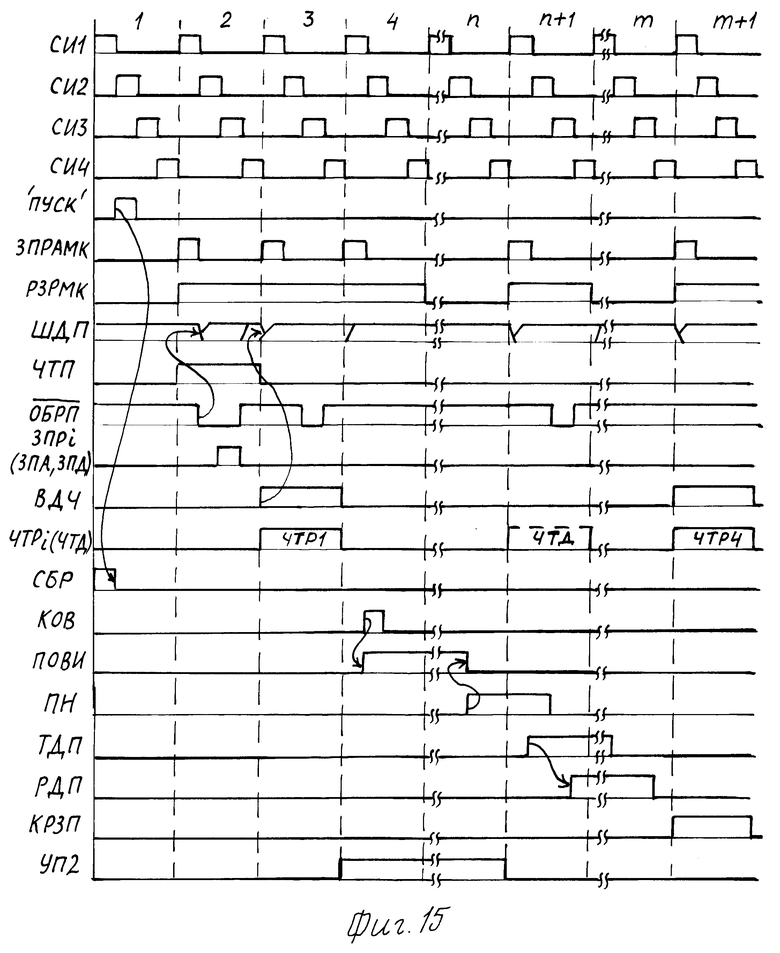

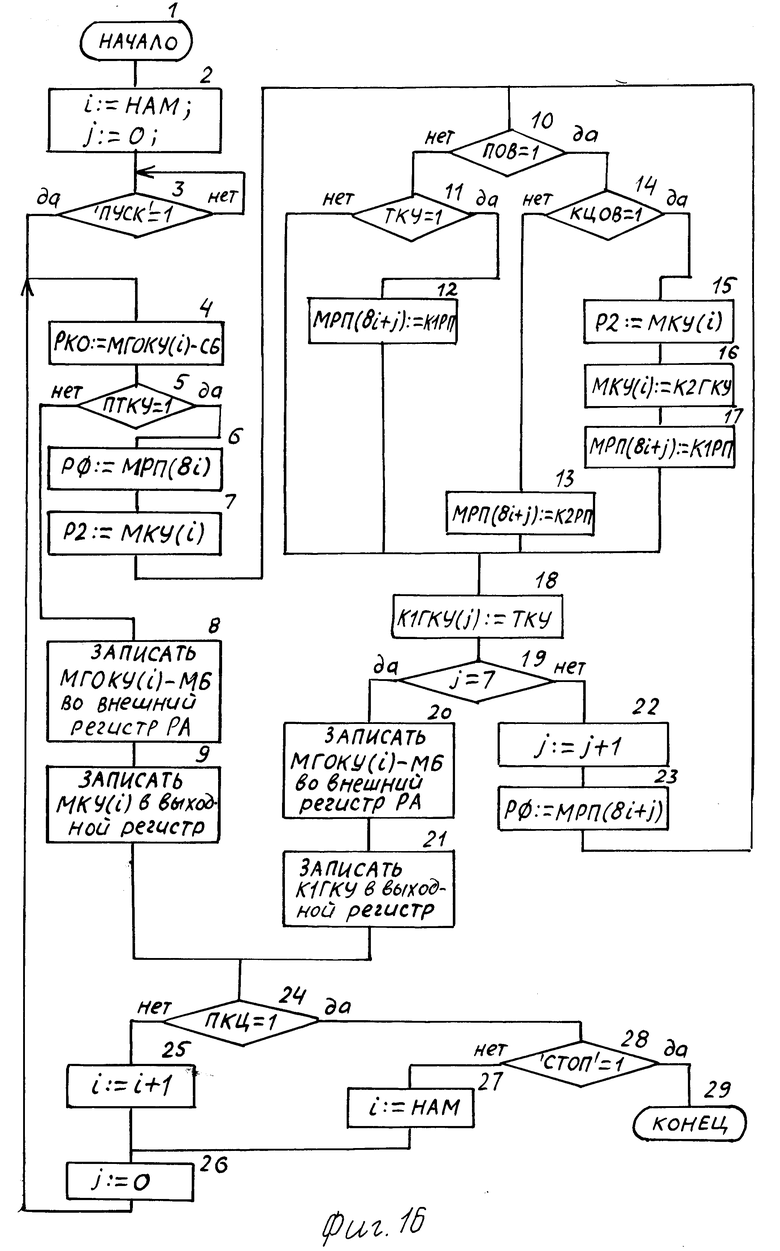

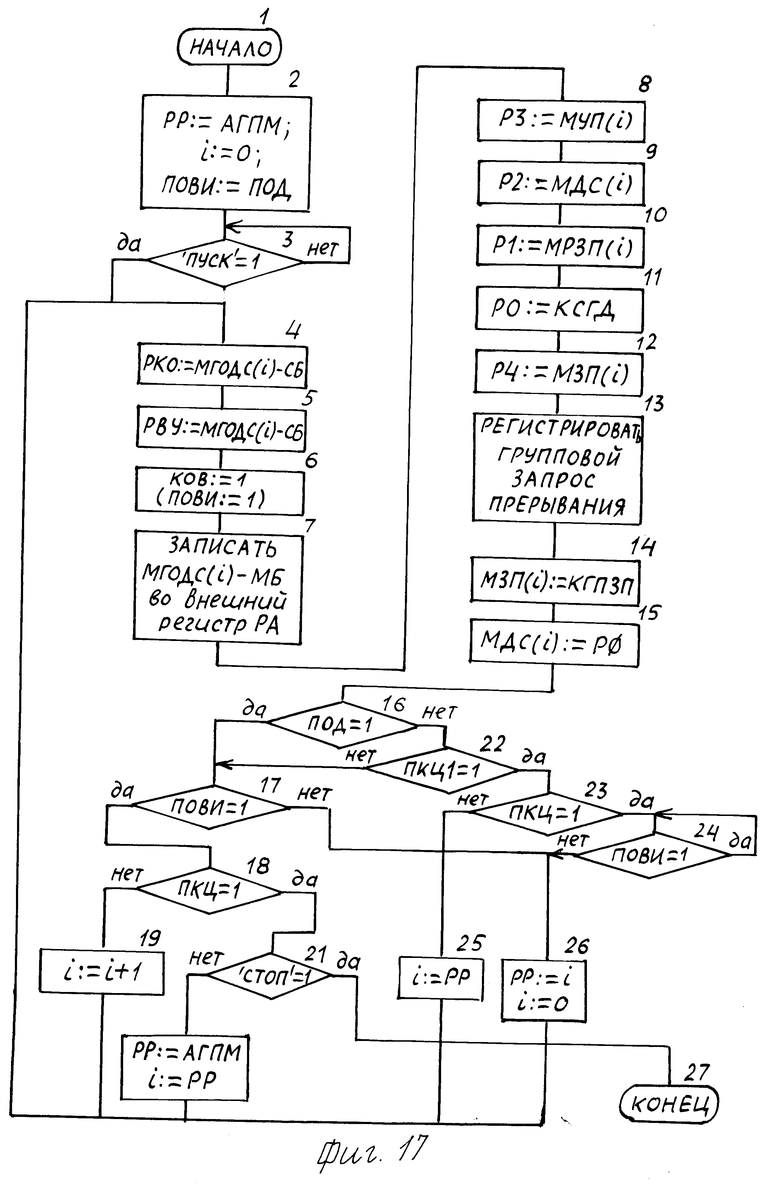

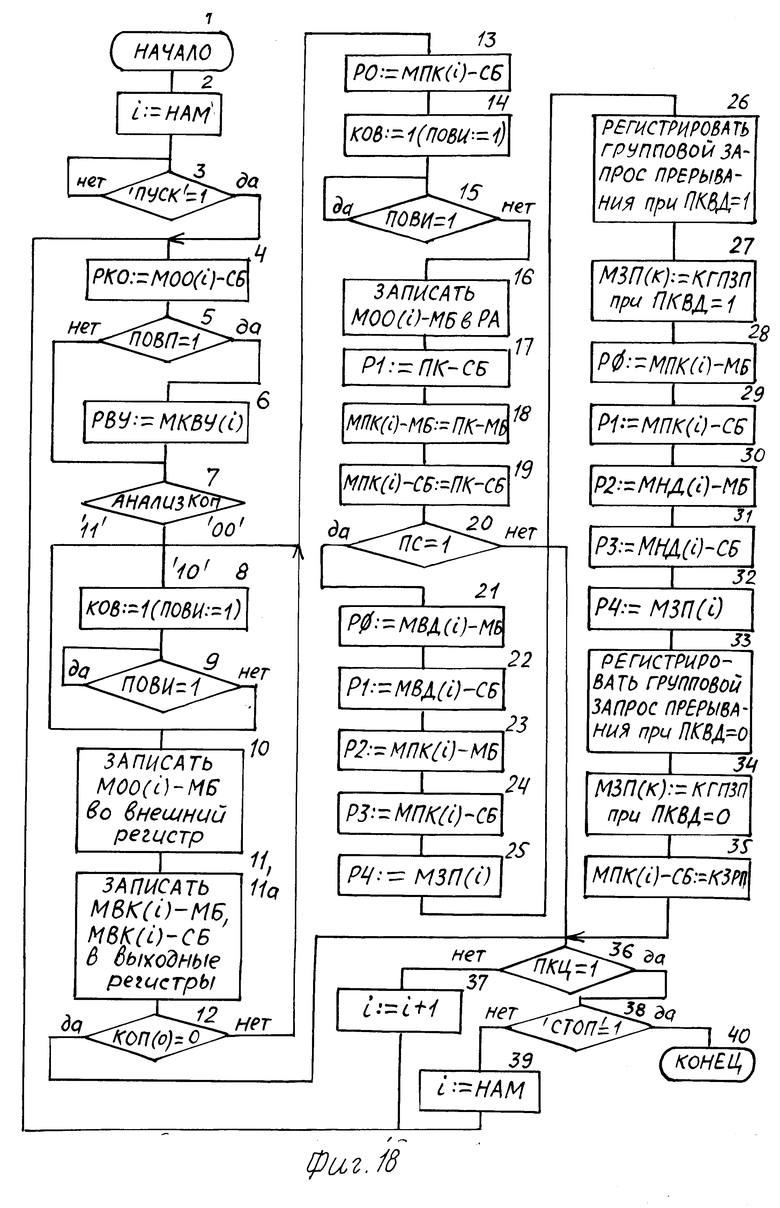

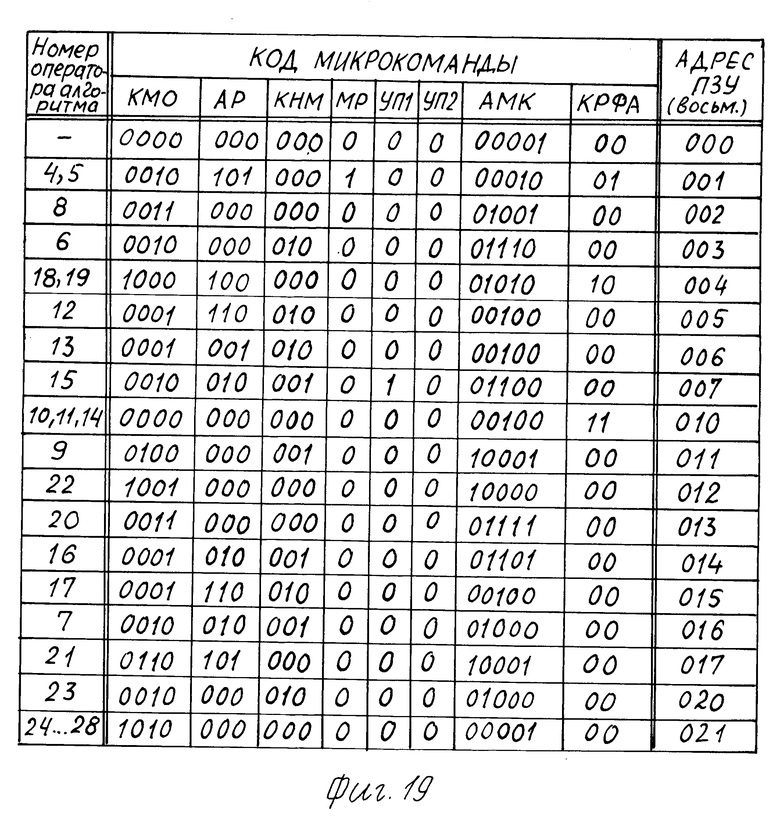

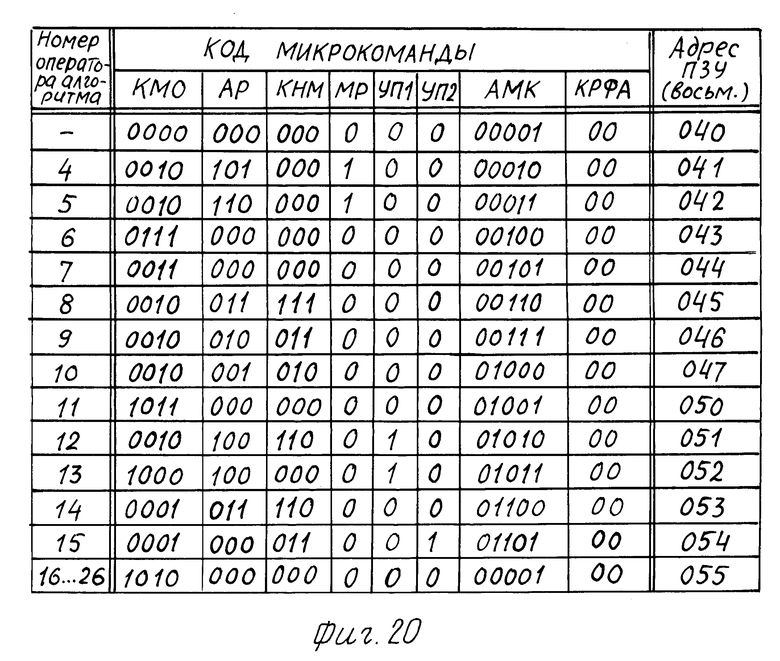

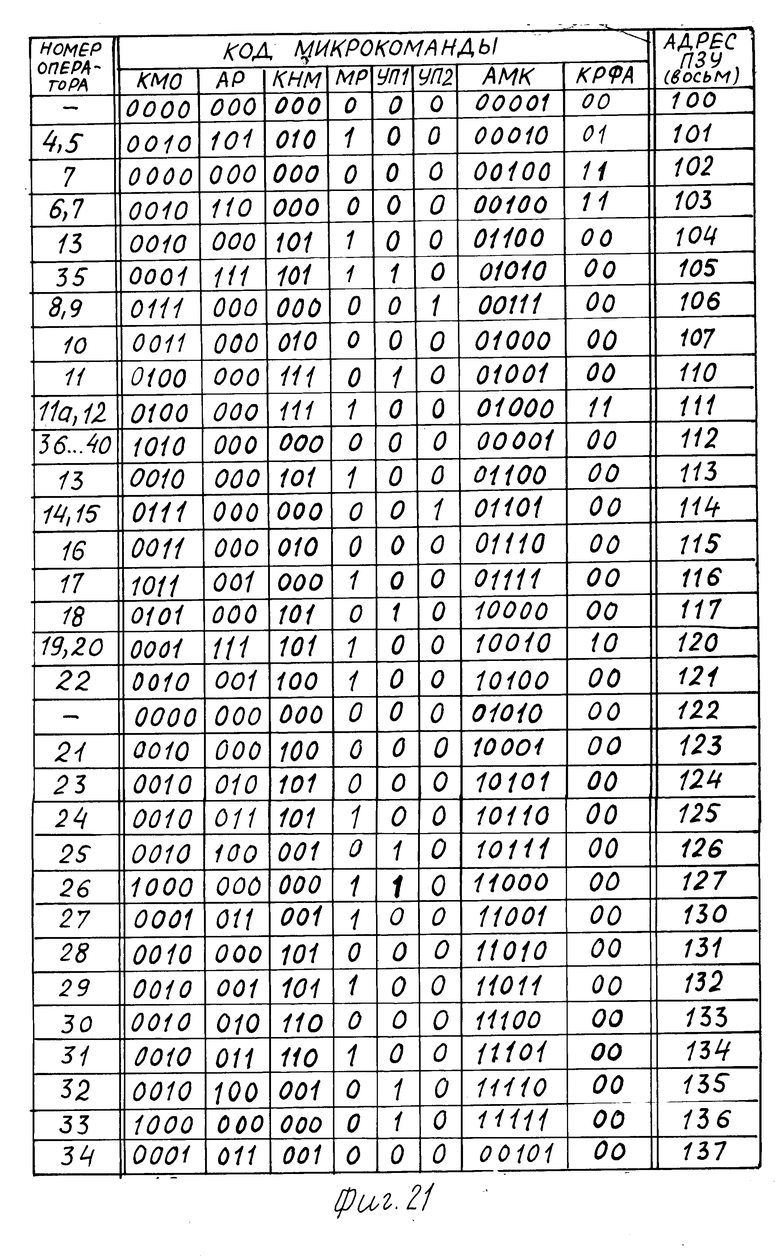

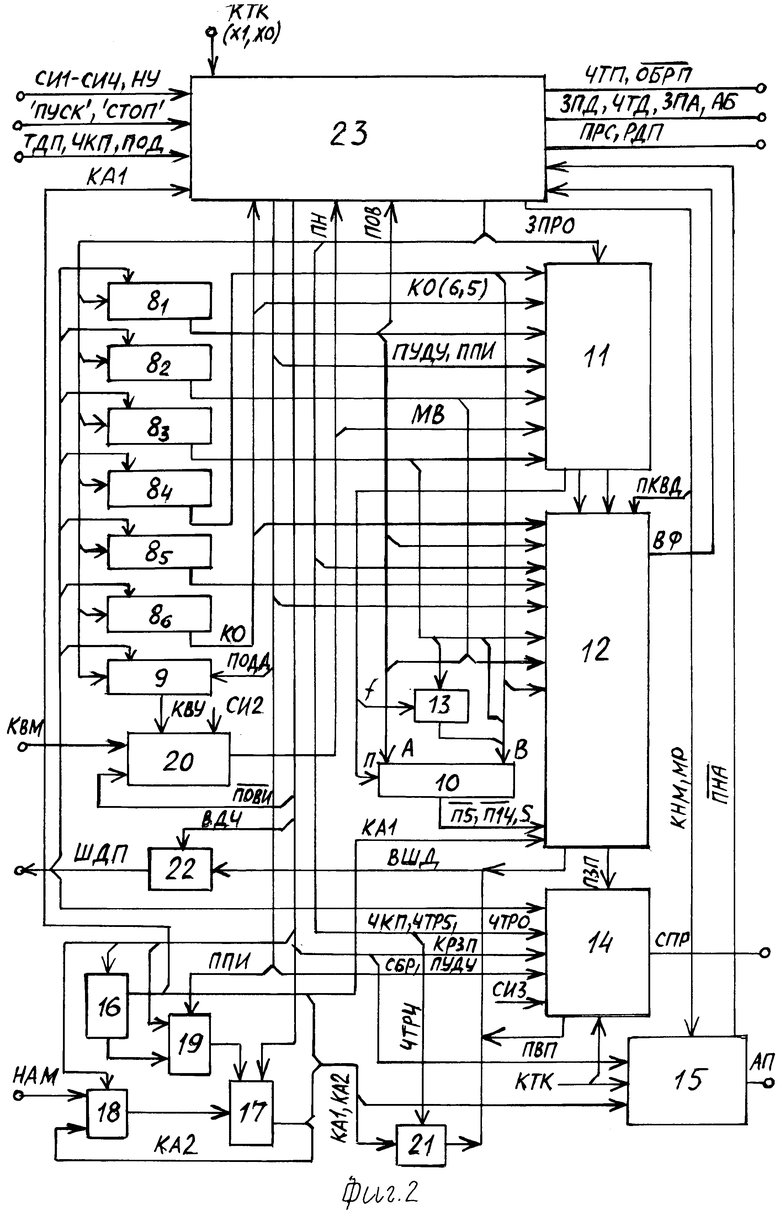

На фиг. 1 изображена структурная схема контроллера ввода-вывода информации; на фиг. 2 структурная схема микропроцессора ввода-вывода информации; на фиг. 3 функциональная схема первого формирователя кодов; на фиг. 4 функциональная схема второго формирователя кодов; на фиг. 5 функциональная схема узла регистрации запросов прерывания; на фиг. 6 таблица форматов адресов при обращении к блоку памяти; на фиг. 7 функциональная схема формирователя кода адреса памяти; на фиг. 8 таблица кодов постоянного запоминающего устройства (ЗУ), входящего в состав формирования кода адреса; на фиг. 9 функциональная схема узла отсчета времени; на фиг. 10 структурная схема микропрограммного блока управления; на фиг. 11 формат микрокоманд блока управления; на фиг. 12 функциональная схема узла управления; на фиг. 13 функциональная схема формирователя управляющих сигналов; на фиг. 14 таблица кодов постоянного ЗУ, входящего в состав формирователя управляющих сигналов; на фиг. 15 временная диаграмма, поясняющая работу микропроцессора; на фиг. 16 блок-схема алгоритма работы контроллера управления двухпозиционными исполнительными устройствами; на фиг. 17 блок-схема алгоритма работы контроллера опроса двухпозиционных датчиков; на фиг. 18 блок-схема алгоритма работы контроллера сопряжения с преобразователями информации; на фиг. 19 микропрограмма контроллера управления двухпозиционными исполнительными устройствами; на фиг. 20 микропрограмма контроллера опроса двухпозиционных датчиков; на фиг. 21 микропрограмма контроллера сопряжения с преобразователями информации.

Контроллер ввода-вывода информации содержит (фиг. 1) микропроцессор 1 ввода-вывода информации, блок 2 памяти, блок 3 сопряжения с машинным информационным каналом, регистр 4 адреса, блоки 5 ключей, выходные регистры 6, формирователь 7 управляющих сигналов.

В состав микропроцессора входят (фиг. 2) информационные регистры 81-86, регистр 9 временной уставки, сумматор 10, первый формирователь 11 кодов, второй формирователь 12 кодов, группа 13 элементов ИЛИ, узел 14 регистрации запросов прерывания, формирователь 15 кода адреса памяти, первый счетчик 16 адресов массивов, второй счетчик 17 адресов массивов, регистр 18 номера адреса массива, коммутатор 19, узел 20 отсчета времени, первый блок 21 ключей, второй блок 22 ключей, микропрограммный блок 23 управления.

Первый формирователь 11 кодов содержит (фиг. 3) восемь блоков 241-248 логического преобразования, первый элемент И 25, первый элемент ИЛИ 26, триггерт 27, третий и второй элементы И 281 и 282, второй и третий элементы ИЛИ 291 и 292, элемент И-НЕ 30. В состав блока логического преобразования входят элемент 31 равнозначности, элемент 32 неравнозначности, элементы ИЛИ 331, 332, элемент И 34.

В состав второго формирователя 12 кодов (фиг. 4) входят триггер 35, восьмой коммутатор 36, второй коммутатор 37, управляемый дешифратор 38, группа 39 элементов ИЛИ-НЕ, группа 40 элементов ИЛИ, седьмой коммутатор 41, первый, четвертый, девятый и третий коммутаторы 421, 422, 423 и 424, шестой и пятый коммутаторы 431 и 432, первый элемент ИЛИ 44, блок 45 ключей, с первого по седьмой элементы И 461-467, третий и второй элементы ИЛИ 471 и 472, элемент И-НЕ 48, элемент НЕ 49.

Узел 14 регистрации запросов прерывания 14 (фиг. 5) содержит восемь блоков 501-508 логического преобразования, регистры 511-514, элементы ИЛИ-НЕ 521-524, третий коммутатор 53, первый буферный регистр 54, пятый коммутатор 55, шестой и второй коммутаторы 561 и 562, первый коммутатор 57, первый дешифратор 58, группу 59 элементов И, седьмой и третий коммутаторы 601 и 602, четвертый коммутатор 61, блок 62 ключей, второй буферный регистр 63, второй дешифратор 64, шестой, второй и четвертый элементы И 651, 652 и 653, первый и третий элементы И 661 и 662, элементы ИЛИ 671-673, пятый элемент И 68, элементы НЕ 691-693. Блок логического преобразования узла регистрации запросов прерывания образован элементом ИЛИ-НЕ 70, элементом И 71, элементом ИЛИ 72.

Формирователь 15 кода адреса памяти образован (фиг. 7) постоянным ЗУ 73, коммутатором 74, первым блоком 75 ключей, вторым блоком 76 ключей, элементом ИЛИ 77.

Узел 20 отсчета времени (фиг. 9) содержит вычитающий счетчик 78, делитель 79 частоты, элемент И 80, динамический триггер 81.

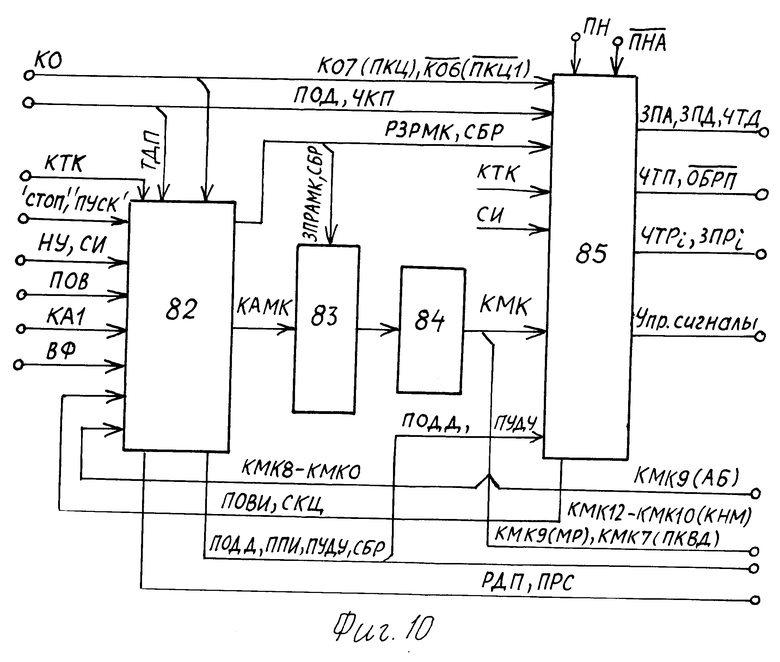

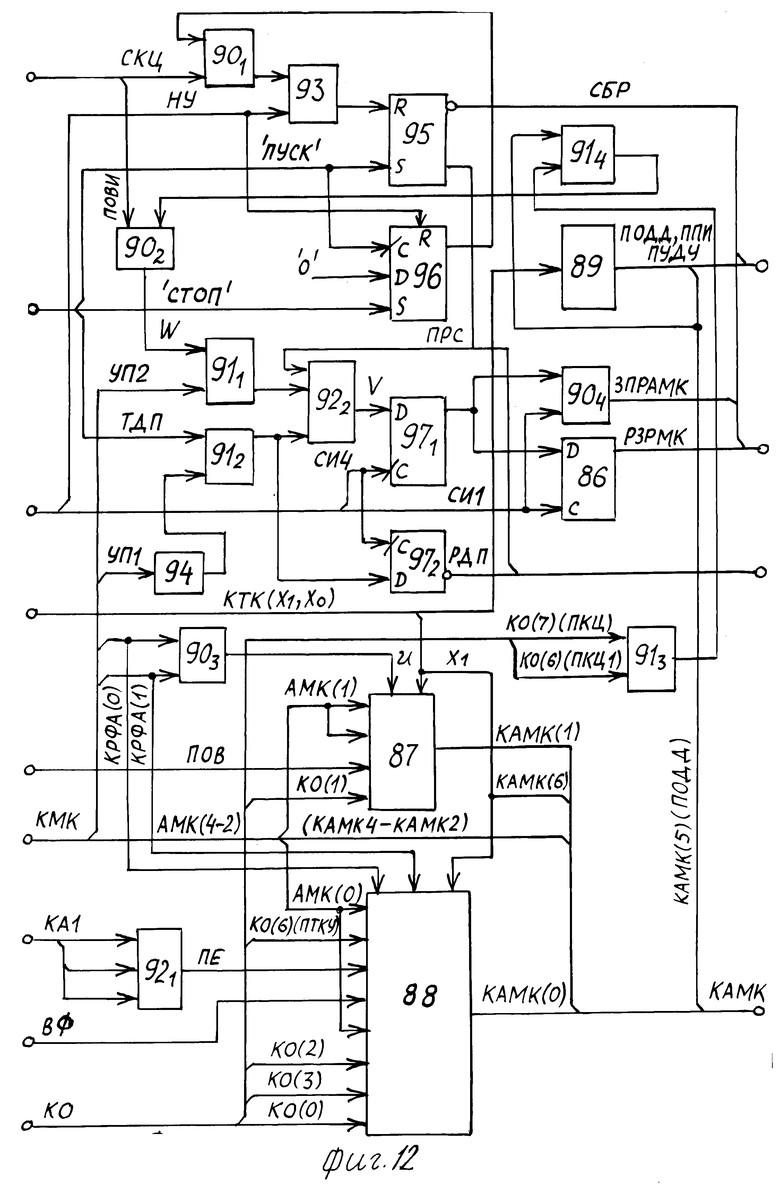

Микропрограммный блок 23 управления включает (фиг. 10) узел 82 управления, регистр 83 адресов микрокоманд, постоянное ЗУ 84у микрокоманд, формирователь 85 управляющих сигналов. Узел 82 управления содержит (фиг. 12) триггер 86, первый мультиплексор 87, второй мультиплексор 88, дешифратор 89, элементы И 901-904, элементы И-НЕ 911-914, элементы И 921, 922, элемент ИЛИ 93, элемент НЕ 94, триггер 95 RS-типа, динамический триггер 96 с установочным входом, динамические триггеры 971, 972.

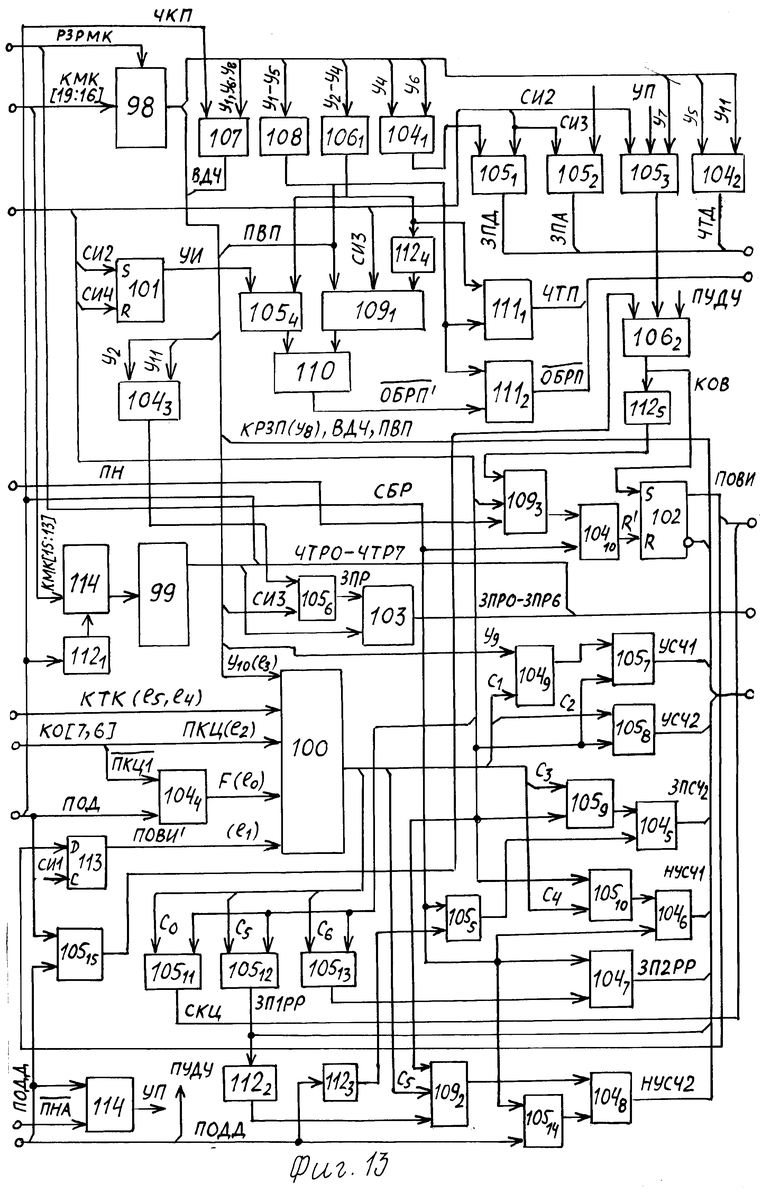

Формирователь 85 управляющих сигналов содержит (фиг. 13) управляемый дешифратор 98, дешифратор 99, постоянное ЗУ 100 микроопераций, триггеры 101, 102 RS-типа, группу 103 элементов И, элементы ИЛИ 1041-10410, элементы И 1051-10515, элементы ИЛИ 1061, 1062, элемент ИЛИ 107, элемент ИЛИ 108, элементы И 1091-1093, элемент ИЛИ-НЕ 110, управляемые элементы 1111, 1112 с тремя состояниями, элементы НЕ 1121-1125, триггер 113, двувходовый элемент 114.

Микропроцессор ввода-вывода информации позволяет построить следующие специализированные контроллеры, которые обеспечивают ввод и обработку информации о состоянии объекта управления, контроля (результаты обработки используются управляющей ЭВМ), а также вывод из ЭВМ и преобразование информации, определяющей значения сигналов, которые подаются на исполнительные устройства объекта: контроллер управления двухпозиционными исполнительными устройствами (КУДУ), контроллер опроса двухпозиционных датчиков (КОДД), контроллер сопряжения с преобразователями информации (КСПИ).

Общая структура контроллера ввода-вывода информации, представленная на фиг. 1, поясняет взаимодействие микропроцессора с другими структурными элементами контроллера.

Микропроцессор 1 и блок 3 сопряжения с машинным информационным каналом (МИК) взаимодействуют с блоком 2 памяти в режиме разделения времени. В блок 2 подаются код адреса памяти АП, управляющие сигналы ЧТП (признак типа операции) и ОБРП (сигнал активизации блока 2). По шине ШДП обеспечена двухнаправленная передача восьмиразрядных кодов данных. Под управлением микропроцессора 1 обеспечена возможность передачи через блоки 5 ключей в блок 2 и микропроцессор принимаемых в контроллер кодов ПК1-ПКm, а также выдачи из блока 2 и микропроцессора 1 кодов в выходные регистры 6. Сигналы, обеспечивающие управление блоками 5 и регистрами 6, вырабатываются формирователем 7 на основе кода адреса, содержащегося в регистре 4, сигналов ЗПД, ЧТД и признака АБ (адрес байта в 16-разрядном слове), дополняющего кода адреса. В регистр 4 код заносится из блока 2 с помощью сигнала ЗПА.

В контроллере с помощью блока 3 обеспечено информационное взаимодействие ЭВМ и блока 2 с целью передачи из ЭВМ параметров и приема в ЭВМ результатов обработки. При необходимости доступа к блоку 2 блок 3 активизирует сигнал ТДП требования доступа к памяти и начинает обмен только после перехода в соответствующее состояние сигнала разрешения доступа (РДП).

В состав блока 3 входит регистр управления и состояния (программно доступен для ЭВМ), обеспечивающий возможность подачи в микропроцессор 1 команд "Пуск", "Стоп" (в виде импульсов), других управляющих сигналов. Для отображения в ЭВМ состояния микропроцессора в блок 3 подается признак ПРС его рабочего состояния. Аппаратные средства блока 3 организуют также передачу в ЭВМ сигнала запроса прерывания (СПР), формируемого микропроцессором, выполнение операции чтения из микропроцессора кода причины прерывания (этой операции соответствует сигнал ЧКП). Из регистра управления и состояния в микропроцессор передаются управляющие код НАМ и признак ПОД.

Синхронизация схем контроллера производится четырьмя импульсными последовательностями СИ1-СИ4, которые характеризуются одинаковой частотой и длительностью импульсов. Последовательности образуют циклически повторяющиеся серии из четырех импульсов, непосредственно следующих друг за другом.

Структура фиг. 1 соответствует контроллеру КСПИ. Структуры контроллеров КУДУ и КОДД аналогичны вышеописанной с той разницей, что в КУДУ отсутствуют блоки 5 ключей, а в КОДД выходные регистры 6.

Двухразрядный код КТК, подаваемый на вход микропроцессора, определяет его режим работы, значение "00" этого кода соответствует использованию микропроцессора в составе КУДУ, значение "01" использование в составе КОДД, "10" использованию в составе КСПИ. В микропроцессор подается также код КВМ временного масштабирования, используемый для отсчета временных интервалов. Ниже приводятся общие характеристики контроллеров.

Контроллер КУДУ обеспечивает на основе информации, поступающей из ЭВМ, формирование состояний триггеров выходных регистров, которым соответствуют двухпозиционные исполнительные устройства. Состояние отдельного триггера определяет команду управления для соответствующего исполнительного устройства. Отдельному выходному регистру, следовательно, соответствует восьмикомандная группа. Для каждой группы в памяти контроллера хранится описатель, который содержит информацию, характеризующую команды группы, в том числе признак типа команды. К одному типу отнесены команды, активизация и дезактивизация которых производится путем задания их состояния из ЭВМ (команды программного управления), к другому типу команды, активизация которых производится из ЭВМ, а заданная длительность формируется микропроцессором (команды с аппаратно формируемой длительностью). Максимальное число команд управления, формируемых контролером, 256 (32 группы).

В блоке памяти контроллера хранится три информационных массива. Массив групповых описателей команд управления (МГОКУ) образован упорядочненной последовательностью описателей, имеющих двухбайтовый формат. Младший байт описателя содержит код адреса выходного регистра, который соответствует группе. Старший байт содержит шестиразрядный код КДКУ длительности команды (занимает разряды 5 0 байта), признак ПТКУ типа команды (занимает разряд 6), состояние "0" признака соответствует командам программного управления, признак ПКЦ конца массива (занимает разряд 7), имеет единичное значение в последнем описателе массива. МГОКУ размещен в области адресов (0400-0477)8 памяти контроллера.

Массив команд управления (МКУ) отражает состояние команд. Установка единичных состояний разрядов массива (активизация команд) производится ЭВМ, а сброс в "0" микропроцессором либо ЭВМ. МКУ имеет байтовую организацию, отдельному байту соответствует определенная группа команд. МКУ занимает область адресов (0500-0537)8.

Массив рабочих переменных (МРП) может содержать до 256 байт. Каждой команде с аппаратно формируемой длительностью соответствует байт МРП, который содержит шестиразрядный код ТВИ текущего временного интервала, используемый для формирования требуемой длительности команды (занимает разряды 5 0), признак СМВ состояния метки времени (разряд 6), признак ПОВ отсчета времени (разряд 7): признак устанавливается в "1" при активизации команды, сбрасывается в "0" после отсчета интервала, соответствующего длительности команды. Группе команд программного управления соответствует один байт МРП, который содержит текущее состояние команд группы. МРП занимает область адресов (0000-0377)8.

Контроллер КОДД обеспечивает прием, хранение и анализ состояний двухпозиционных датчиков, отражающих состояние объекта управления. Указанные операции выполняются одновременно для группы из восьми датчиков. Информация о состоянии датчиков в произвольный момент времени доступна для ЭВМ. Прием состояний датчиков в контроллер производится как с учетом необходимости отсройки от "дребезга" контактов, так и без нее. Значение длительности "дребезга" задается и является одинаковым для всех датчиков.

В КОДД обеспечена возможность формирования инициативного сигнала (запроса прерывания) по изменению состояния любого датчика. С этой целью для отдельного датчика задаются значение признака разрешения прерывания и вид изменения его состояния, обусловливающий возбуждение запроса. Может быть сформирован запрос прерывания при установке заданных состояний в группе датчиков. Для каждой группы датчиков в памяти контроллера хранится описатель, содержащий информацию о характеристиках группы. Максимальное число датчиков, обслуживаемых контроллером, 256 (32 группы).

В памяти контроллера хранится пять информационных массивов. Массив групповых описателей дискретных сигналов, соответствующих датчикам (МГОДС), образован упорядоченной последовательностью описателей, имеющих двухбайтовый формат. Если контроллер опрашивает датчики, часть которых требует отстройки от "дребезга", то в области младших адресов МГОДС помещены описатели для датчиков, требующих отстройки (эти описатели образуют первый подмассив), а затем описатели для остальных датчиков (они образуют второй подмассив). Младший байт каждого описателя содержит код адреса узла ключей, соответствующего группе датчиков. Старший байт содержит код КВИ временного интервала, соответствующего продолжительности "дребезга" контактов (занимает разряды 4 0 байта), признак ПТГЗП типа группового запроса прерывания (разряд 5), при нулевом состоянии разряда групповой запрос прерывания (обобщенный запрос прерывания для группы датчиков) активизируется, если активен хотя бы один индивидуальный запрос прерывания, при единичном состоянии разряда групповой запрос активизируется, если все датчики группы, для которых разрешено формирование запроса, устанавливаются в заданные состояния, признак ПКЦ1 конца первого подмассива описателей (разряд 6) имеет единичное состояние в последнем описателе подмассива, признак ПКД конца массива имеет единичное состояние в последнем описателе массива МГОДС. МГОДС размещен в области адресов (0000-0077)8 памяти контроллера.

Массив признаков разрешения формирования запросов прерывания (МРЗП) имеет байтовую организацию, причем отдельный байт соответствует определенной группе датчиков. Единичное состояние разряда в массиве разрешает формирование запроса прерывания для соответствующего датчика. Этому массиву соответствует область памяти (0100-0137)8.

Массив зарегистрированных значений дискретных сигналов (МДС) отражает состояние опрашиваемых датчиков. Байты массива соответствуют группам датчиков. Массиву соответствует область памяти (0140-0177)8.

Массив запросов прерывания (МЗП) хранит сформированные для отдельных датчиков запросы прерывания (возбужденному запросу соответствует состояние "1" определенного разряда массива). Байты массива соответствуют группам датчиков. Массиву соответствует область памяти (0200-0237)8.

Массив управляющих признаков (МУП) определяет условие формирования запроса прерывания для каждого датчика. Нулевое состояние разряда массива определяет, что запрос прерывания возбуждается при установке нулевого значения сигнала, соответствующего датчику, единичное значение разряда определяет, что запрос прерывания формируется при установке единичного значения сигнала от датчика. Байты МУП соответствуют группам датчиков. МУП размещен в области адресов (0240-0277)8 памяти контроллера.

Одноименные разряды массивов МРЗП, МДС, МЗП, МУП соответствуют одному и тому же датчику. Байты этих массивов и описатели МГОДС имеют одинаковую упорядоченность относительно групп датчиков.

Контроллер КСПИ обеспечивает выдачу кодов, являющихся входной информацией для преобразователей, которые формируют управляющие воздействия в выходные регистры контроллера, а также прием, анализ и хранение кодов от преобразователей информации, отражающей состояние объекта управления (прием кодов производится через узлы ключей контроллера).

Коды, передаваемые в преобразователи и принимаемые из преобразователей, хранятся в памяти контроллера. Первые заносятся в эту память из ЭВМ, вторые через узлы ключей. Принятые в контроллер коды доступны для чтения со стороны ЭВМ в произвольный момент времени. В памяти контроллера обеспечено также хранение кодов, поступивших из ЭВМ и соответствующих верхнему и нижнему предельным значениям для каждого принимаемого кода. Каждый из указанных кодов сопровождается признаком разрешения прерывания при фиксации выхода значения соответствующего принятого кода за данный допустимый предел. При выходе хотя бы одного принятого кода за предельное значение при активном состоянии соответствующего признака разрешения прерывания обеспечивается формирование инициативного сигнала (сигнала запроса прерывания) со стороны контроллера. Признаки запросов прерывания, соответствующие отдельным принятым кодам, объединены в восьмиразрядные группы. В контроллере предусмотрена возможность реализации заданного временного интервала между следующими друг за другом операциями информационного обмена с преобразователями.

В памяти контроллера хранится семь информационных массивов. Массив описателей обменных операций (МОО) образован упорядоченной последовательностью описателей, имеющих двухбайтовый формат. Младший байт описателя содержит код адреса выходного регистра, узла ключей. Старший байт содержит двухразрядный код операции (занимает разряды 1,0 байта), значение кода "00" определяет операцию приема в память контроллера кода от преобразователя через заданный узел ключей с заданной временной задержкой, значение "10" операцию записи кода из памяти контроллера в выходной регистр с заданной временной задержкой, значение "11" операцию безусловной записи кода из памяти в выходной регистр и последующего приема в память кода от преобразователя с заданной временной задержкой через соответствующий узел ключей, признак ПОВП обновления временного параметра (занимает разряд 2): при единичном состоянии признака производится изменение кода, определяющего величину временной задержки для обменных операций, признак ПС сравнения кодов (занимает разряд 3), при единичном состоянии признака производися допусковый контроль принятого из преобразователя кода, признак ПКЦ конца массива (занимает разряд 7): признак имеет единичное значение в последнем используемом описателе МОО. МОО может содержать до 256 описателей и занимает область адресов (5000-5777)8 в памяти контроллера.

Массив МВК кодов, выдаваемых из контроллера в преобразователи, может содержать до 256 двухбайтных кодов. Этому массиву соответствует область памяти с адресами (3000-3777)8.

Массив МПК кодов, принимаемых в память контроллера из преобразователей, может содержать до 256 двухбайтовных кодов. Если не проводится допусковый контроль принятого кода, он может иметь 16-разрядный формат. Если указанный контроль проводится, код имеет 15-разрядный формат, старший разряд соответствует признаку, фиксирующему выход значения принятого кода за пределы допустимых значений. МПК занимает область памяти с адресами (2000-2777)8.

Массив МВД верхних допустимых значений может содержать до 256 двухбайтовых кодов. Старший разряд старшего байта содержит признак разрешения формирования запроса прерывания при выходе принятого из преобразователя кода за верхнее допустимое значение (при единичном состоянии разряда прерывания разрешено). Остальные семь разрядов старшего байта и разряды младшего байта образуют код допустимого значения. МВД расположен в области памяти с адресами (0000-0777)8.

Массив МНД нижних допустимых значений может содержать до 256 двухбайтовых кодов. Формат каждого из этих кодов такой же, как и для МВД. Он включает в себя 15-разрядный код нижнего допустимого значения и соответствующий признак разрешения формирования, запроса прерывания. МНД соответствует область памяти с адресами (1000-1777)8.

Массив МЗП запросов прерывания хранит признаки запросов прерывания, соответствующие отдельным принимаемым в контроллер кодам. МЗП может содержать до 32 байтов, причем отдельный байт содержит признаки запросов для группы из восьми последовательных кодов в массиве МПК (выделение групп производится в направлении возрастания номеров элементов МРК). МЗП размещен в области памяти с адресами (4400-4437)8.

Массив МКВУ кодов временной установки может содержать до 256 байтов, каждый из которых содержит код, определяющий значение временной задержки запуска соответствующей обменной операции. МКВУ соответствует область памяти с адресами 4000-4377)8.

Элементы всех массивов КСПИ упорядочены в направлении возрастания адресов памяти таким образом, что элементы с одинаковыми номерами соответствуют одной и той же обменной операции (для МЗП элементом является отдельный разряд).

Регистры 81-86 и 9, входящие в состав операционного блока микропроцессора (фиг. 2), обеспечивают хранение восьмиразрядных кодов, используемых при обработке информации. При этом регистр 86 содержит код, соответствующий старшему байту описателя и определяющий режимы обработки (код КО), в регистрах 81-85 содержатся операнды, регистр 9 предназначен для хранения кодов временной уставки, которые используются при отсчете временных интервалов. При использовании микропроцессора в составе контроллера КАДД на входы сброса в "0" триггеров, соответствующих трем старшим разрядам регистра 9, подается единичное значение сигнала ПОДД, что обеспечивает нулевое состояние этих разрядов. Информационные входы указанных регистров подключены к информационной шине ШДП, на управляющие входы регистров подаются стробы записи, которые формируются блоком 23 на основе кодов адресов регистров. Регистрам 81-86 и 9 соответствуют коды адреса (000) (110).

Информационное содержимое регистров 81-86 определяет работу 15-разрядного сумматора 10, первого и второго формирователей 11 и 12 кодов, группы 13 элементов ИЛИ. Операнд А для сумматора 10 образован содержимым регистров 81 (оно определяет значение восьми младших разрядов А) и 82 (определяет значение семи старших разрядов). Шесть младших разрядов операнда В образованы значениями сигналов с выхода группы 13, следующие два разряда соответствуют обратному коду операнда, содержащегося в старших разрядах регистра 83, остальные семь разрядов операнда обратному коду операнда, содержащегося в старших разрядах регистра 83, остальные семь разрядов операнда обратному коду операнда, содержащегося в младших разрядах регистра 84. Группа 13 образована шестью двухвходовыми элементами ИЛИ, на один из входов которых подан сигнал f, а на другой сигнал, соответствующий разряду обратного кода, снимаемого с регистра 83. Таким образом, сумматор 10 фактически производит вычитание кодов, хранящихся в регистрах 81, 82 и 83, 84, с учетом значения сигнала П переноса, подаваемого в младший разряд сумматора. С выходов сумматора в формирователь 12 выдаются шестиразрядный код S, соответствующий младшим разрядам суммы, сигналы  и

и  переноса из разрядов сумматора (нумерация разрядов сумматора начинается с младшего, нулевого, разряда).

переноса из разрядов сумматора (нумерация разрядов сумматора начинается с младшего, нулевого, разряда).

Узел 14 регистрации запросов прерывания на основе признака ПЗП запроса прерывания, поступающего из формирователей 12 кодов, кода номера группы источников прерывания, подаваемого по шине ШДП, и сигналов управления из блока 23 обеспечивает установку (в накопительном режиме) соответствующего триггера при единичном значении признака ПЗП. При выполнении операции чтения кода номера группового признака запроса прерывания из узла 14 выдается код, соответствующий минимальному номеру триггера, установленного в "1", по завершении выдачи кода этот триггер сбрасывается в "0". Если в узле зарегистрирован хотя бы один групповой запрос, сигнал СПР на выходе узла имеет единичное значение.

Трехразрядный код КА1 и пятиразрядный код КА2, формируемые на выходах соответственно счетчиков 16 и 17, определяют номера элементов информационных массивов, содержимое которых используется для выполнения типовой операции обработки, предусмотренной алгоритмом работы соответствующего контроллера. За счет работы счетчиков в режиме увеличения своего состояния последовательно выполняется операция обработки по отношению ко всей информации, содержащейся в информационных массивах. Из блока 28 на управляющие входы счетчика 16 подаются сигнал НУСЧ1 сброса в ноль и сигнал УСЧ1, а на входы счетчика 17 сигнал НУСЧ2 сброса в ноль и сигнал ЗПСЧ2 записи в счетчик содержимого рабочего регистра 18. Сигнал счета для счетчика 17 формируется на выходе коммутатора 19, на один из входов которого подан сигнал УСЧ2 из блока 23 (этот сигнал подается на соответствующий управляющий вход счетчика 17, если ППИ 0), а на другой сигнал переноса с выхода счетчика 16, так что при ППИ 1 счетчики 16, 17 образуют единый восьмиразрядный счетчик.

Регистр 18 обеспечивает запоминание состояния счетчика 17 (для записи в регистр кода из счетчика используется управляющий сигнал ЗП1РР) и его последующий возврат в счетчик. Предусмотрена также возможность записи в регистр 18 кода НАМ с помощью управляющего сигнала ЗП2РР.

На основе кодов КА1 и КА2, признака МР младшего разряда адреса памяти, кода номера массива (КНМ) формирователь 15 вырабатывает 12-разрядный код адреса памяти (АП). Выдача этого кода из формирователя производится при единичном значении признака ПВП.

Узел 20 отсчета времени обеспечивает формирование временного интервала, величина которого задается содержимым регистра 9, на основе синхроимпульса МИ2 и кода КВМ, подаваемого в узел и определяющего временной масштаб при отсчете времени. При единичном значении сигнала ПОВИ отсчет не производится, схемы узла 20 в исходном состоянии. Отсчет начинается с момента перехода сигнала ПОВИ в нулевое состояние и завершается формированием единичного состояния признака ПН. При реализации контроллера КУДУ узел 20 формирует последовательность импульсов МВ типа меандр с частотой, которая задается кодом КВМ.

Микропроцессор характеризуется восемью восьмиразрядными адресуемыми элементами данных, значения которых могут быть выданы в шину ШДП. Пять элементов данных формируются во втором формирователе 12 кодов. К их числу относятся первый код рабочих переменных К1РП (адресуется кодом "110"), второй код рабочих переменных К2РП (адрес "001"), третий код рабочих переменных К3РП (адрес "111"), код КГПЗП группы признаков запросов прерывания (адрес "011"), второй код группы команд управления К2ГКУ (адрес "010"). Два адресуемых элемента данных формируются в узле 14. К ним относятся первый код группы команд управления К1ГКУ (адресуется кодом "101"), код КНГПЗП номера группового признака запроса прерывания (адрес "000"). Еще один адресуемый элемент данных образуют коды КА2, КА1 с выходов счетчиков 16, 17 (этому элементу соответствует адрес "100").

Выдача кодов адресуемых элементов данных в мультиплексную внутреннюю шину данных ВШД производится с помощью управляющих сигналов чтения, формируемых блоком 23 и подаваемых в формирователь 12 (сигналы ЧТР1-ЧТР3, ЧТР6, ЧТР7), узел 14 (сигналы ЧТР0, ЧТР5), на управляющий вход первого блока 21 ключей (сигнал ЧТР4). Через второй блок 22 ключей при значении управляющего сигнала ВДЧ=1 код с шины ВШД передается в двунаправленную внешнюю шину ШДП.

На основе значения кода КТК блок 23 формирует единичное значение одного из признаков ПУДУ, ПОДД, ППИ, которые определяют режимы работы микропроцессора в составе контроллеров КУДУ, КОДД, КСПИ.

Первый формирователь 11 кодов (фиг. 3) обеспечивает формирование признака ПЗП-ДД, который фиксирует возбуждение запроса прерывания в группе двухпозиционных датчиков, и кода КПЗП признаков запросов прерывания для этой группы (признак и код используются в контроллере КОДД). Признаку ПЗП-ДД соответствуют логические выражения

ПЗП-ДД ПЗП1-ДД( ПЗП2-ДД)

ПЗП2-ДД)

ПЗП1-ДД  gi; ПЗП2-ДД

gi; ПЗП2-ДД  hi

hi

gi= mi∧ϕi∧Ψi; hi=

ϕi= (ai∧Ki)∨( )

)

ϕi= (ai∧Ki)∨( )

)

Ψi= ( bi)∨(a

bi)∨(a )

)

i  где а7-а0 значения разрядов регистра 81 микропроцессора; b7-b0 значения разрядов регистра 83; m7-m0 значения разрядов регистра 84, К7-К0 значения разрядов регистра 82. Признак ПТГЗП соответствует состоянию пятого разряда регистра 86. Приведенные логические выражения реализуются однотипными логическими блоками 241-248, элементами И 25, ИЛИ 26, 291, И 282. Логические блоки формируют сигналы h7-h0 и g7-g0, причем последние образуют код КПЗП.

где а7-а0 значения разрядов регистра 81 микропроцессора; b7-b0 значения разрядов регистра 83; m7-m0 значения разрядов регистра 84, К7-К0 значения разрядов регистра 82. Признак ПТГЗП соответствует состоянию пятого разряда регистра 86. Приведенные логические выражения реализуются однотипными логическими блоками 241-248, элементами И 25, ИЛИ 26, 291, И 282. Логические блоки формируют сигналы h7-h0 и g7-g0, причем последние образуют код КПЗП.

Для использования в контроллерах КУДУ и КСПИ формирователей 11 формируются сигналы f, П в соответствии с логическими выражениями

f ПУДУ∧ПТКУ; П ППИ

Значение текущей метки времени МВТ определяется состоянием триггера 27, в котором "защелкивается" состояние метки МВ сигналом ЗПРО. Значение признака ПТКУ соответствует состоянию шестого разряда регистра 86, а сигнал  состоянию шестого разряда регистра 81. Реализация сигналов f, П производится с помощью элементов И 281, ИЛИ 292, И-НЕ 30.

состоянию шестого разряда регистра 81. Реализация сигналов f, П производится с помощью элементов И 281, ИЛИ 292, И-НЕ 30.

Во втором формирователе 12 кодов (фиг. 4) формируются адресуемые элементы данных К2ГКУ, КГПЗП, КГРП, К2РП, К3РП. Состояния разрядов К2ГКУ определяются значениями сигналов на выходах логических элементов ИЛИ-НЕ, образующих группу 39. Этим сигналам соответствуют логические выражения

К2ГКУ(i)  = b

= b ; i

; i  где Z0-Z7 сигналы с выходов управляемого дешифратора 38.

где Z0-Z7 сигналы с выходов управляемого дешифратора 38.

К2ГКУ используется в контроллере КУДУ. В этом режиме использования микропроцессора на управляющий вход дешифратора 38 через коммутатор 421подается значение признака ПТКУ.

Элемент данных К2РП характеризуется следующим форматом: старший (седьмой) разряд имеет контактное единичное значение, состояние шестого разряда определяется значением метки времени МВТ, остальные разряды отображают значение кода S с выхода сумматора 10 (он является кодом КТВИ текущего временного интервала).

Формат К1РП содержит значение  старшего разряда регистра 81(седьмой разряд), значение метки времени МВТ (шестой разряд), код КДКУ, определяемый состоянием шести младших разрядов регистра 86 (разряды 5 0).

старшего разряда регистра 81(седьмой разряд), значение метки времени МВТ (шестой разряд), код КДКУ, определяемый состоянием шести младших разрядов регистра 86 (разряды 5 0).

Семь младших разрядов кода КЗРП определяются состоянием выходов коммутатора 432, а старший разряд значением сигнала с выхода одноразрядного коммутатора 423. Для контролера КОДД значение К3РП а7а6. а0. Для контроллера КСПИ младшие разряды кода К3РП соответствуют а14-а8, а старший разряд имеет значение а7 (при УП1 0 и ПС 1), а17(при УП1 0 и ПС= 0) либо значение признака ПНДЗ нарушения допустимых значений (при УП1 ПС1). Код а15а14 а8 соответствует информационному содержимому регистра 82. Признак ПНДЗ формируется путем дизъюнктивного объединения элементом ИЛИ 472 текущего и буферизированного с помощью триггера 35 значений сигнала переноса  . Коммутатор 424 подает на один из входов коммутатора 423 значение а7 (при нулевом значении сигнала на выходе элемента И 467) либо а15 (в противном случае).

. Коммутатор 424 подает на один из входов коммутатора 423 значение а7 (при нулевом значении сигнала на выходе элемента И 467) либо а15 (в противном случае).

Значение восьмиразрядного кода КГПЗП зависит от режима использования микропроцессора, в контроллера КСПИ (ППИ 1) обеспечивает с помощью группы 40, поразрядное дизъюнктивное объединение кода КР4 с выхода регистра 85 и кода "1" из 8", формируемого дешифратором 38, на управляющий вход которого подано значение признака ПЗП-ПИ через одноразрядный коммутатор 421, в контроллере КОДД группа 40 дизъюнктивно объединяет код КР4 и код КПЗП. На информационный вход дешифратора 38 подается код КА1 со счетчика 16. Через коммутатор 431 обеспечена подача разных кодов на один из входов группы 40.

Коммутатор 37 обеспечивает передачу на вход блока 45 ключей кода любого из рассмотренных элементов данных при активном состоянии соответствующего сигнала на его управляющем входе. Элемент ИЛИ 44 формирует для блока 45 сигнал, управляющий выдачей значения элемента данных в шину ВШД.

Второй формирователь 12 кодов обеспечивает также формирование признака ПЗП-ПИ, который фиксирует возбуждение запроса прерывания при анализе кодов, принимаемых от преобразователей информации (при использовании микропроцессора в составе КСПИ). Указанный признак определяется логическим выражением

ПЗП-ПИ  ((a

((a ПКВД)∨(a

ПКВД)∨(a )) где П14 сигнал переноса из сумматора 10; а15 и b15 значения старших разрядов регистров 82 и 84; ПКВД управляющий признак, формируемый блоком 23. Для выработки признака ПЗП-ПИ используются логические элементы И 461-465, ИЛИ 47, НЕ 49.

)) где П14 сигнал переноса из сумматора 10; а15 и b15 значения старших разрядов регистров 82 и 84; ПКВД управляющий признак, формируемый блоком 23. Для выработки признака ПЗП-ПИ используются логические элементы И 461-465, ИЛИ 47, НЕ 49.

При использовании микропроцессора в составе КУДУ формирователь 12 формирует сигналы ТКУ и ВФ в соответствии с логическими выражениями

ТКУ ( )∧

)∧  (bi∧Zi)

(bi∧Zi)

ВФ ( a7)∨(ТКУ

a7)∨(ТКУ )

)

Для реализации этих выражений использованы коммутаторы 41 и 422, логические элементы И 466, И-НЕ 48. Значение сигнала ПЗП на выходе формирователя 12 зависит от режима использования микропроцессора, для КСПИ оно определяется значением признака ПЗП-ПИ, для КУДУ значением ТКУ, для КОДД значением ПЗП-ДД. Формирование требуемых значений ПЗП осуществляется с помощью коммутатора 36.

Узел 14 обеспечивает регистрацию до 32 групповых запросов прерывания при использовании микропроцессора в составе контроллеров КСПИ и КОДД. Этим запросам в узле соответствуют триггеры, которые образуют четыре восьмиразрядных регистра 511-514 (фиг. 5). Пятиразрядный код, определяющий номер группы, для которой регистрируется запрос, задается старшими разрядами кода, поступающего по шине ШДП (этим разрядам кода соответствуют сигналы p7-p3). С помощью старших разрядов кода номера группы (сигналы p7, p6) производится адресация регистров, младшими разрядами (сигналы p5, p4, p3) адресуются разряды регистров. Регистрируемое значение группового запроса прерывания определяется состоянием признака ПЗП.

Восьмиразрядный код d7'd6'. d0', подаваемый на информационные входы регистров, формируется однотипными логическими блоками 501-508, причем

d (ci∧КРЗП)

(ci∧КРЗП) i

i  где сигналы с0-с7 соответствуют разрядам кода "1" из 8", вырабатываемого управляемым дешифратором 58; d0-d7 сигналы с выхода буферного регистра 54; КРЗП управляющий сигнал из блока 23, принимающий единичное значение при регистрации группового запроса. На информационный вход регистра 54 подается код с выхода одного из регистров 511-514 через коммутатор 53, который управляется сигналами с выхода дешифратора 64. Работа этого дешифратора определяется содержимым буферного регистра 63, на вход сброса в ноль которого подан сигнал ПУДУ (в режиме регистрации запросов он имеет нулевое значение), а на вход сигнала записи сигнал ЗПБР, определяемый выражением

где сигналы с0-с7 соответствуют разрядам кода "1" из 8", вырабатываемого управляемым дешифратором 58; d0-d7 сигналы с выхода буферного регистра 54; КРЗП управляющий сигнал из блока 23, принимающий единичное значение при регистрации группового запроса. На информационный вход регистра 54 подается код с выхода одного из регистров 511-514 через коммутатор 53, который управляется сигналами с выхода дешифратора 64. Работа этого дешифратора определяется содержимым буферного регистра 63, на вход сброса в ноль которого подан сигнал ПУДУ (в режиме регистрации запросов он имеет нулевое значение), а на вход сигнала записи сигнал ЗПБР, определяемый выражением

3ПБР ( ).

).

Сигнал ЗПБР формируется элементами ИЛИ 673, НЕ 693. Через коммутатор 57 на информационный вход регистра 63 при КРЗП 1 подается код p7p6.

Значение кода на информационном входе дешифратора 58 определяется значениями сигналов на управляющих входах коммутаторов 561 и 562. При ПУДУ 0 через коммутатор 562 передается код p5p4p3, который устанавливается на выходе коммутатора 562 при КРЗП 1. На управляющий вход дешифратора 58 сигнал подается с выхода элемента ИЛИ 674 и определяется значениями сигналов ПЗП и КРЗП.

Сигнал R, подаваемый на входы сброса в ноль регистров 511-514, формируется элементами И 662 и ИЛИ 671 в соответствии с логическим выражением

R СБР∨(ПУДУ∧4TP5∧СИ3).

Сигналы записи информации в регистры 511-514 вырабатываются группой 59 двухвходовых элементов И, на один из входов которых подан соответствующий выходной сигнал дешифратора 64, а на другой импульсный сигнал ИС, определяемый выражением

ИС СИ3∧(4КП∨КР3П).

Сигнал ИС формируется элементами ИЛИ 672, И 653.

Таким образом, если ПУДУ 0, КРЗП1, то при подаче СИЗ вырабатывается активное значение сигнала записи в тот из регистров 511-514, который задается значением кода p7p6. Разряд кода d7'd6' d0', номер которого задается значением кода p5p4p3 (модифицируемый разряд), имеет единичное значение при ПЗП 1. Остальные разряды кода d7'd6' d0', а также модифицируемый разряд при ПЗП 0 имеют значения, определяемые состоянием соответствующих разрядов регистра, в который производится запись.

В узле 14 обеспечено формирование кода a4а3а2а1а0, соответствующего минимальному номеру зарегистрированных в регистрах 511-514 запросов прерывания. Разряды а4а3 определяют минимальный номер регистра (регистру 511 соответствует номер "00" регистру 514 номер "11"), в котором установлен в единицу хотя бы один разряд, а разряды а2а1а0 минимальный номер разряда указанного регистра, установленного в "1". Нумерация разрядов регистров определяется их соответствием значениям кода p5p4p3.

При КРЗП 0 значения разрядов а4а3 устанавливаются на выходе буферного регистра 63 и соответствуют значениям сигналов a4' и a3', которые формируются элементами ИЛИ-НЕ 521-523, 602 и И 652 в соответствии с логическими выражениями

a xo∧xi; a

xo∧xi; a (a

(a x2)∨(

x2)∨( xo).

xo).

Признак а5, фиксирующий факт отсутствия единиц во всех регистрах, вырабатывается элементом И 661 и определяется выражением

a5= a x2∧x3.

x2∧x3.

В приведенных выражениях

xi=  i

i  где rij выход j-го разряда регистра с номером i.

где rij выход j-го разряда регистра с номером i.

С помощью коммутаторов 55, 601 и логических элементов И 651, 68 формируются значения разрядов а2, а1, а0 на основе обратного кода  .

. , снимаемого с выхода буферного регистра 54 и соответствующего информационному содержимому регистра с запросами прерывания, который имеет номер а4а3 (на основе кода а4а3 дешифратор 64 формирует соответствующие управляющие сигналы для коммутатора 53). При этом используются следующие логические выражения:

, снимаемого с выхода буферного регистра 54 и соответствующего информационному содержимому регистра с запросами прерывания, который имеет номер а4а3 (на основе кода а4а3 дешифратор 64 формирует соответствующие управляющие сигналы для коммутатора 53). При этом используются следующие логические выражения:

a2=  ; a1=

; a1=  ; ao= (a

; ao= (a )∨(

)∨( );

); = (

= ( )∨a

)∨a ); i

); i  .

.

В узле 14 формируется адресуемый элемент данных КНГПЗП, имеющий следующий формат: старшему (седьмому) разряду соответствует признак а5, в шестом и пятом разрядах содержится код КТК, в остальных разрядах код а4а3а2а1а0. Выдача КНГПЗП в шину ВШД производится через коммутатор 61 и блок 62 ключей при ЧТРО 1. В этом режиме сигнал КРЗП 0, что обусловливает "защелкивание" в буферном регистре 63 кода а4а3, в буферном регистре 54 кода с выхода регистра, имеющего номер а4а3. На информационный вход дешифратора 58 через коммутатор 562 подан код а2а1а0, на управляющий вход сигнал логической "1". Вследствие этого код  .

.  характеризуется нулевым значением разряда с номером а2а1а0, остальные семь разрядов этого кода имеют значения соответствующих разрядов буферного регистра 54. При подаче импульса СИЗ производится запись кода в регистр с номером а4а3, что приведет к сбросу в ноль группового запроса прерывания с наименьшим номером.

характеризуется нулевым значением разряда с номером а2а1а0, остальные семь разрядов этого кода имеют значения соответствующих разрядов буферного регистра 54. При подаче импульса СИЗ производится запись кода в регистр с номером а4а3, что приведет к сбросу в ноль группового запроса прерывания с наименьшим номером.

При использовании микропроцессора в составе контроллера КУДУ признак ПУДУ 1. Следствием этого является то, что на выходе буферного регистра 63 установлено нулевое значение кода, буферный регистр 54 отображает содержимое регистра 511, на вход дешифратора 58 при КРЗП 1 подается код p2p1p0 с шины ШДП. Следовательно, в данном случае регистрация значений сигнала ПЗП при КРЗП 1 производится только в разрядах регистра 511, причем номер разряда, значение которого может быть изменено, определяется значением кода p2p1p0. Прямой код буферного регистра соответствует адресуемому элементу данных КПКУ, который выдается в шину ВШД при значении сигнала ЧТР5 1. Если при выдаче КПКУ активизируется сигнал СИЗ, то сбрасываются в ноль все триггеры регистра 511.

Сигнал СПР формируется путем инвертирования элементов НЕ 692сигнала а5.

Фиг. 6 отображает форматы кодов адресов, которые используются при обращении к различным информационным массивам, хранящимся в памяти контроллера. Организация формирователя 15 кода адреса памяти определяется вышеуказанными форматами. Основными узлами этого формирователя являются (фиг. 6) постоянное ЗУ73 и коммутатор 74, на входы которого поданы девятиразрядные коды К3-К0. Код К0 образован признаком МР (младший разряд кода), кодом адреса КА2 (занимает разряды 5-1 кода), значениями сигналов y7-y5 с выхода ЗУ 73 (им соответствуют старшие разряды). В состав кода К1 входят код КА2 (занимает младшие разряды), значения сигналов y7-y5 (занимают старшие разряды), в состав кода К2 коды КА1 (занимают младшие разряды) и КА2 (занимают разряды 7-3), константа "0" (содержится в старшем разряде), в состав кода К3 признак МР (занимает младший разряд), код КА2 (занимает старшие разряды), код КА1 (занимает остальные разряды). Управление коммутатором 74 осуществляется сигналами y3-y0 с выхода ЗУ 73, причем активизация сигнала yj обусловливает передачу на выход коммутатора 74 кода Kj. Код с выхода этого коммутатора определяет значение разрядов 8-0 адреса памяти АП, формируемых на выходе второго блока 76 ключей. Разряды 11, 10, 9 адреса АП вырабатываются на основе выходных сигналов y10, y9, y8 ЗУ 73, подаваемых на вход первого блока 75 ключей. Элемент ИЛИ 77 формирует инверсное значение признака ПНА, фиксирующего нулевое состояние разрядов кода КА2.

На фиг. 8 приведено соответствие между значениями входных сигналов (адресов) ЗУ 73 и его выходными сигналами, которые отображают информационное содержимое ячеек памяти.

Узел 20 отсчета времени (фиг. 9) включает в свой состав делитель 79 частоты, импульсный сигнал СЧИ с выхода которого подается на счетный вход восьмиразрядного вычитающего счетчика 78. Предусмотрена возможность записи кода КВУ временной уставки в счетчик. Сигнал МВ снимается с выхода триггера, соответствующего старшему разряду счетчика. Работа делителя 79 определяется последовательностью импульсов СИ2 и кодом КВМ временного масштаба, задающего коэффициент деления. На вход начальной установки делителя подан сигнал ПОВИ, что обусловливает его работу только при ПОВИ 0. ПОВИ является также сигналом записи кода КВУ в счетчик 78 (запись производится при ПОВИ1). Восьмивходовый элемент И 80 формирует единичное значение признака ПН при нулевом состоянии всех разрядов счетчика 78.

Блок 23 построен в соответствии с микропрограммным принципом управления, вследствие чего включает в себя (фиг. 10), постоянное ЗУ 84 микрокоманд, регистр 83 адресов микрокоманд, формирователь 85 управляющих сигналов, который вырабатывает сигналы, обеспечивающие реализацию микроопераций в операционном блоке микропроцессора, и узел 82 управления, организующий выполнение требуемых последовательностей микрокоманд путем формирования кода КАМК адреса микрокоманд. Узел 82 вырабатывает также сигнал СБР начальной установки схем микропроцессора, сигнал ЗПРАМК записи информации в регистр 83, сигнал РЗРМК, при единичном значении которого вырабатываются управляющие сигналы формирователем 85, признаки ПОДД, ППИ, ПУДУ, определяющие в составе какого контроллера используется микропроцессор. Сигналы, определяемые состоянием разрядов 7, 9, 10-12 кода КМК микрокоманд выдаются в операционный блок непосредственного использования.

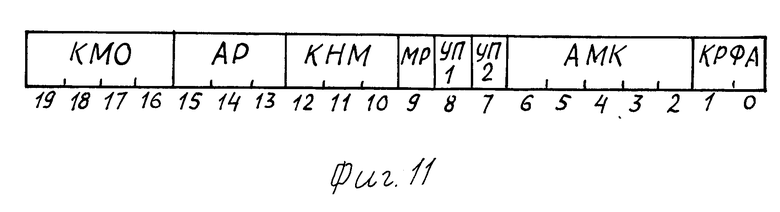

Формат микрокоманд представлен на фиг. 11.

Коды поля микроопераций (КМО) предусматривают возможность выполнения следующих микрокоманд: "записать содержимое адресуемого элемента данных в заданный массив, хранящийся в памяти" (код 0001 в поле КМО), "записать код в адресуемый регистр из заданного массива, хранящегося в памяти" (код 0010), "записать код во внешний адресный регистр из заданного массива, хранящегося в памяти" (код 0011), "записать код в выходной регистр данных из заданного массива, хранящегося в памяти" (код 0100), "записать код внешних данных в заданный массив, хранящийся в памяти" (код 0101), "записать содержимое адресуемого элемента данных в выходной регистр данных" (код 0110), "записать отсчет времени (формировать единичное значение сигнала КОВ") (код 0111), "регистрировать групповой запрос прерывания (регистрировать значение заданной команды управления в группе)" (код 1000), "увеличить на единицу содержимое первого счетчика адресов массивов" (код 1001), "формировать управляющие сигналы по завершении цикла обработки" (код 1010), "записать код внешних данных в адресуемый регистр" (код 1011). Код 0000 в поле КМО соответствует отсутствию операций.

В поле АР микрокоманды задают адреса регистров и элементов данных для микрокоманд типа 1, 2, 6, 11. Поле КНМ содержит код номера массива, хранящегося в памяти, и используется микрокомандами типа 1, 2, 3, 4, 5. Признак МР задает номер байта при обращении к массивам с двухбайтовыми элементами (МР 0 для младшего байта).

При единичном состоянии признака УП1 запрещена приостановка выполнения микропрограмм при обращении к памяти контроллера со стороны ЭВМ. При УП2 1 выполнение очередной микрокоманды может быть начато только по завершении отсчета временного интервала.

Поле АМК и код КРФА режима формирования адреса используются для задания адреса очередной микрокоманды. При КРФА 00 этот адрес определяется всеми разрядами поля АМК, если КРФА имеет значение 01 и 10, то очередной адрес образуется путем объединения четырех старших разрядов поля АМК и соответствующего признака, отражающего состояние операционного блока, при КРФА 11 адрес состоит из трех старших разрядов поля АМК и двух признаков из операционного блока.

Формирование значений младших разрядов адреса очередной микрокоманды в узле 82 (фиг. 12) производится первым и вторым мультиплексорами 87 и 88. Код, подаваемый на управляющие входы мультиплексора 88, который формирует значения сигнала КАМК (0), образован старшим разрядом кода КТК (х1) (он соответствует старшему разряду кода адреса на входе мультиплексора) и разрядами кода КРФА. На информационные входы этого мультиплексора поданы следующие сигналы (в порядке возрастания номеров информационных входов, определяемых состоянием кода на управляющих входах): АМК (0) (соответствует нулевому информационному входу), КО (6) ПЕ, ВФ, АМК (0), КО (2), КО (3), КР (0). Признак ПЕ 1 при единичном значении всех разрядов кода КА1.

Код, поданный на управляющие входы мультиплексора 87, образован сигналом х1 (младший разряд кода) и сигналом U с выхода элемента И 903. На информационные входы мультиплексора с номерами 0 и 1 подан сигнал АМК (1), на остальные входы признак ПОВ (информационный вход 2) и сигнал КО (1).

Единичное состояние триггера 971 определяет возможность выполнения микрокоманд. Сигнал U, значение которого отображается состоянием этого триггера, формируется в соответствии с логическими выражениями

U ПРС∧( )∧(

)∧( );

);

W ПОВИ∧( (ПКЦ∧ПКЦ1) ПОВИ∧(

(ПКЦ∧ПКЦ1) ПОВИ∧( ).

).

Признак ПРС рабочего состояния микропроцессора формируется триггером 95, установка которого в "1" производится сигналом "Пуск", а сброс в "0" сигналом НУ или сигналом СКЦ при единичном состоянии триггера 96. Управление последним осуществляется сигналами "Пуск" и "Стоп". Состояние признака РДП формируется триггером 972. Дешифратор 89 на основе кода КТК вырабатывает признаки ПОДД, ППИ, ПУДУ, определяющие работу микропроцессора в составе контроллеров КОДД, КСПИ, КУДУ.

Формирователь 85 управляющих сигналов включает в свой состав (фиг. 13) дешифратор 98 кодов микроопераций, на выходе которого вырабатываются сигналы y1-y11, соответствующие используемым кодам микроопераций (номера сигналов соответствуют десятичным эквивалентам значений кодов). Сигналы на выходе дешифратора 98 активизируются только при значении сигнала РЗРМК 1. Выходные сигналы данного дешифратора используются для формирования управляющих сигналов в соответствии со следующими выражениями:

3ПА y3∧СИ3; 4ТД y5∨y11; 3ПД (y4∨y6)∧СИ3;

3ПР (y2∨y11)∧СИ3; ВД4 y1∨y6∨y8∨4ПК;

ПВП y1∨y2∨y3∨y4∨y5; 4ТП′= y2∨y3∨y4;

КОВ (y7∧УП∧СИ2)∨ПУДУ∨(ПОДД∧ПОД);

УП ПНА

;

;

Управляющий импульс УИ формируется триггером 101 и определяет продолжительность активизации сигнала  ; при обращении к памяти контроллера в режиме чтения. Сигналы ЧТП и ОБРП формируются на выходах ключей 1111, 1112, на информационные входы которых поданы сигналы

; при обращении к памяти контроллера в режиме чтения. Сигналы ЧТП и ОБРП формируются на выходах ключей 1111, 1112, на информационные входы которых поданы сигналы  и

и  ,а на управляющие признак ПВП взаимодействия с памятью.

,а на управляющие признак ПВП взаимодействия с памятью.

Сигнал ЗПР используется для формирования сигналов ЗПР0-ЗПР6 записи и поступает на один из входов элементов И, образующих группу 103. На второй вход этих элементов поданы сигналы с выходов дешифратора 99, формируемые на основе значений разрядов поля АР микрокоманды. Выходные сигналы этого дешифратора используются также в качестве сигналов ЧТР0-ЧТР7. Разряды АР подаются на входы дешифратора 99 через элемент 114, на один из входов которого подан сигнал  с выхода элемента НЕ 1121.

с выхода элемента НЕ 1121.

Сигнал КОВ производит установку в "1" триггера 102, обеспечивающего формирование признака ПОВИ отсчета временного интервала. Сброс этого триггера в "0" производится сигналом R', формируемым в соответствии с выражением

R′= (ПН СИ3)∨СБР.

СИ3)∨СБР.

При y10 1 производится формирование управляющих сигналов на этапе завершения типового цикла обработки, предусмотренного алгоритмом работы соответствующего контроллера. К числу этих сигналов относятся сигналы управления работой счетчиков 16, 17, рабочего регистра 18, сигнал СКЦ конца цикла, обеспечивающий останов микопроцессора. Для выработки управляющих сигналов используется постоянное ЗУ 100 микроопераций, значение кода l5-l0 адреса для которого определяется состоянием разрядов кода КТК (l5, l4), признаков ПКЦ (l2), ПОВИ' (l1), значением сигнала y10(l3) и сигнала F, определяемого выражением F ПОД V  (l0). Соответствие кодов адресов информационному содержимому ячеек ЗУ 100 приведено на фиг. 14 (остальные ячейки памяти имеют нулевое содержимое). Формирование управляющих сигналов производится в соответствии с выражениями

(l0). Соответствие кодов адресов информационному содержимому ячеек ЗУ 100 приведено на фиг. 14 (остальные ячейки памяти имеют нулевое содержимое). Формирование управляющих сигналов производится в соответствии с выражениями

УСЧ1 (C1∨Y9)∧СИ3; НУСЧ1 СБР∨(C4∧CB3);

УСЧ2 C2∧СИ3; 3ПС42 (СБР )∨(C3∧СИ3);

)∨(C3∧СИ3);

НУСЧ2 (СБР∧ПОДД)∨(c СИ3);

СИ3);

3П1РР C5∧СИ2; 3П2РР СБР∨(C6∧СИ2);

СКЦ Co∧СИ2.

Каждая микрокоманда выполняется в течение одного цикла синхронизации, образованного однократной последовательностью импульсов СИ1-СИ4. На фиг. 15 представлена временная диаграмма, поясняющая работу микропроцессора при выполнении типовых микрокоманд. Начало диаграммы соответствует исходному состоянию схемы микропроцессора, характеризующемуся единичным значением сигнала СБР (и соответственно сигналов НУСЧ1, ЗПСЧ2 (или НУСЧ2, ЗП2РР), нулевым состоянием регистра 83 микрокоманд, отсутствием управляющих сигналов на выходах формирователя 85. Сигнал "Пуск", подаваемый в цикле 1 синхронизации, обусловливает формирование единичных значений сигналов ЗПРАМК и РЗРАМК в начале цикла 2. Предполагается, что в цикле 2 выполняется микрокоманда записи кода в адресуемый регистр из массива, хранящегося в памяти, за счет формирования активного состояния сигналов ЧТП, ЗПР ОБРП. В шину ШДП выдается код из памяти. Аналогично выполняются микрокоманды записи кода в выходной регистр данных из массива (в этих случаях активизируются сигналы ЗПА либо ЗПД).

В цикле 3 выполняется микрокоманда записи содержимого адресуемого элемента данных К2РП в массив, хранящийся в памяти. При этом в ШДП за счет активизации сигналов ЧТР1 и ВДЧ выдается код элемента данных, запись которого в память производится сигналом ОБРП. В цикле 4 выполняется микрокоманда запуска отсчета времени, характеризующаяся единичным состоянием признака УП2. В данном цикле вырабатывается единичное значение сигнала КОВ, активизирующее сигнал ПОВИ, что приводит к запрету выполнения очередной микрокоманды (прекращается формирование импульсов ЗПРАМК, устанавливается значение РЗРМК 0). По окончании отсчета заданного временного интервала узлом 20 в n-м цикле вырабатывается единичное значение признака ПН, обусловливающее снятие запрета на выполнение очередной микрокоманды. В (n + 1)-м цикле выполняется микрокоманда записи кода внешних данных в массив памяти за счет формирования сигнала ЧТД, обеспечивающего выдачу в ШДП кода данных, который записывается в память сигналом ОБРП. В этой микрокоманде признак УП1 имеет нулевое значение, вследствие чего формирование в (n + 1)-м цикле единичного значения сигнала ТДП приводит к активизации сигнала РДП разрешения доступа к памяти со стороны ЭВМ и запрету выполнения очередной микрокоманды. Сброс в ноль сигнала ТДП в m-м цикле обеспечивает возможность выполнения в (m + 1)-м цикле микрокоманды регистрации группового запроса прерывания за счет активизации сигналов ЧТР4, ВДЧ. На шину ШДП через блок 21 ключей выдаются коды КА1, КА2, которые отсюда подаются в узел 14.

Работа микропроцессора в разных режимах его использования поясняется с помощью блок-схем алгоритмов, реализуемых контроллерами КУДУ, КОДД, КСПИ.

Контроллер КУДУ. Переменным j, i, которые используются в блок-схеме алгоритма (фиг. 16), соответствуют коды КА1 и КА2, определяемые состояниями счетчиков 16 и 17. Операции, входящие в состав оператора 2, обеспечивают установку контроллера в исходное состояние и реализуются за счет активизации сигналов НУСЧ1, ЗПРР, ЗПСЧ2. После подачи сигнала "Пуск" в регистр 86 (РКО) заносится старший байт группового описателя (оператор 4), содержащий информацию о режиме обработки группы команд. Если разряд 6 этого регистра имеет состояние "0" (признак ПТКУ 0), то производится запись значения группы команд в выходной регистр 6 с адресом, код которого предварительно занесен в регистр 4 адреса (за счет выполнения операторов 8, 9). На этом завершается обработка группы и в результате анализа состояния признака ПКЦ, соответствующего старшему разряду регистра РКО, активизируется один из сигналов УСЧ2 (соответствует оператору 25), ЗПСЧ2 (соответствует оператору 27), формируется импульсный сигнал НУСЧ1 (оператор 26).

Если ПТКУ 1, то производится индивидуальная обработка каждой из восьми команд управления, входящих в состав группы. Номер команды в группе задается переменной j. Команда характеризуется индивидуальным описателем, являющимся элементом массива МРП. Описатель команды содержит признак ПОВ, который имеет единичное значение, если команда автивизирована, пятиразрядное поле, содержащее код КТВИ, который используется для отсчета временного интервала, определяющего продолжительность команды, признак СМВ, отражающий состояние текущей метки времени в момент обработки команды. Исходной информацией для обработки команды являются код описателя, хранящийся в регистре 81 (РО), текущее состояние команды (ТКУ), соответствующее состоянию i-го разряда регистра 83 (Р2), в котором хранится код группы команд управления (ТКУ формируется на выходе элемента И 466 с помощью коммутатора 41 и дешифратора 38 при условии, что ПОВ 0), шестиразрядный код S с выхода сумматора 10, который соответствует значению КТВИ, уменьшенному на единицу, если СМВ 0 и текущая метка времени МВТ 1 (это условие фиксирует окончание периода следования метки времени) либо повторяет значение КТВИ, если вышеприведенное условие не выполняется, признак КЦОВ конца отсчета временного интервала, соответствующий сигналу  переноса из старшего разряда при формировании суммы S.

переноса из старшего разряда при формировании суммы S.

Алгоритм отражает четыре режима обработки команды управления, определяемые состоянием признаков ПОВ, КЦОВ и сигнала ТКУ. Анализ признаков производится операторами 10, 11, 14. На схемотехническом уровне при реализации этих операторов используется вспомогательная функция ВФ, формируемая коммутатором 422.

Первый режим соответствует случаю, когда обрабатываемая команда ранее не активизировалась (ПОВ 0) и не активизируется в текущий момент времени, о чем свидетельствует значение ТКУ (ВФ) 0.

Второй режим имеет место, если команда ранее не активизировалась (ПОВ 0), но активизируется в текущий момент времени (ТКУ 1). В данном случае формируется значение кода К1РП, соответствующее исходному состоянию описателя команды: признак ПОВ устанавливается в "1", коду КТВИ присваивается значение кода КДКУ, заданное в групповом описателе, СМВ воспроизводит состояние текущей метки времени МВТ. Сформированный код заносится в память (оператор 12).

Третий режим соответствует случаю, когда команда активизирована (ПОВ 1), но не закончен отсчет заданного временного интервала, т.е. КЦОВ (ВФ) 0. В этом случае формируется значение кода К2РП, соответствующее обновленному значению описателя команды, который содержит признак ПОВ 1, значение кода КТВИ S, значение СМВ МВТ. Сформированный код заносится в память (оператор 13).

Четвертый режим имеет место, если ПОВ 1 и зафиксирован конец отсчета временного интервала, соответствующего длительности команды, т.е. КЦОВ (ВФ) 1. В данном режиме команда деактивизируется, что обусловливает следующие действия: формируется значение ТКУ 0; записывается нулевое значение этой команды в массив МКУ путем записи в него кода К2ГКУ, в котором один из разрядов имеет состояние "0", а остальные разряды отображают состояния соответствующих команд группы (действия реализуются операторами 15, 16 алгоритма); в описателе данной команды устанавливается значение признака ПОВ 0 за счет записи кода К1РП в соответствующую ячейку массива МРП.

В микрокоманде, соответствующей оператору 15, задано значение УП1 1, что исключает возможность активизации команд со стороны ЭВМ в интервале между выполнением операторов 15 и 16.

Независимо от режима обработки команды управления производится ее регистрация в j-м разряде кода К1ГКУ, который соответствует состоянию разрядов регистра 54 узла 14, отображающих разряды регистра 511(регистрация выполняется оператором 18).

Обработке последовательно подвергаются все команды группы путем реализации алгоритмического цикла с помощью операторов 19, 22, 23. По завершении обработки всех команд группы производится запись кода К1ГКУ во внешний регистр с заданным адресом (операторы 20, 21), после чего анализируется состояние признака ПКЦ и активизируются соответствующие управляющие сигналы. Если признак "СТОП" 1, то триггер 95 сбрасывается в ноль, что обусловливает активизацию сигнала СБР и останов контроллера.

Таким образом, при многократной обработке отдельной команды в соответствии с приведенным алгоритмом обеспечены ее активизация после задания из ЭВМ единичного значения соответствующего разряда массива МКУ, установка единичного значения соответствующего разряда внешнего регистра, сохранение этого значения в течение заданного времени интервала, а после окончания отсчета этого интервала сброс в "0" соответствующего разряда как массива МКУ, так и внешнего регистра.

Микропрограмма контроллера приведена на фиг. 19.

Контроллер КОДД. Алгоритм работы контроллера (фиг. 17) предусматривает в общем случае обработку восьмиразрядных кодов, отражающих состояние группы двухпозиционных датчиков, как требующих отстройки от "дребезга", так и свободных от него. Используемая в алгоритме переменная j соответствует коду КА2 с выхода счетчика 17 и задает номер группы.

Информация, относящаяся к группам датчиков, организована в виде массивов, хранящихся в памяти, причем информация для групп датчиков с отстройкой от "дребезга" содержится в начальных элементах массивов. Элементы массивов, начиная с номера, соответствующего значению кода АГПМ (АГПМ НАМ), содержат информацию, которая относится к датчикам, свободным от "дребезга". Независимо от типа датчиков для каждого кода, отражающего состояния датчиков, выполняется типовая процедура обработки, включающая в себя запись в регистр 86 (РКО) старшего байта соответствующего группового описателя (оператор 4 алгоритма); запись в регистр 9 кода временного интервала, содержащегося в старшем байте группового описателя и определяющего продолжительность "дребезга" (оператор 5); прием в регистр 81 (РО) кода КСГД, отражающего текущее состояние датчиков в группе с заданным адресом (операторы 7, 11); занесение в регистры 82-84 (Р1-Р3) кодов с параметрами, которые используются для формирования признаков запросов прерывания (операторы 8-10); регистрацию в накопительном режиме группового запроса прерывания в узле 14 (оператор 13) и признаков прерывания для отдельных датчиков группы в массиве МЗП (операторы 12, 14); обновление текущего состояния датчиков в массиве МДС (оператор 15).

После выполнения оператора 12 в формирователе 11 кодов сформированы значения группового признака прерывания ПЗП-ДД (элементом И 282) и кода КПЗП (логическими блоками 241-248) на основе значений разрядов регистров 81-84 и пятого разряда регистра 86 (ему соответствует признак ПТГЗП). При ПТГЗП 0 значение ПЗП-ДД ПЗП1-ДД 1, если хотя бы для одного датчика в группе сформирован запрос прерывания. Если ПТГЗП 1, то ПЗП-ДД 1 при условии, что сформировались запросы прерывания для всех датчиков группы, для которых это разрешено.

В микрокомандах, соответствующих операторам 12, 13, задано значение признака УП1 1, что исключает возможность считывания в ЭВМ информации о запросах прерывания в процессе их регистрации. Оператор 6 выполняется только для группы с номером i 0.

Алгоритм предусматривает следующий порядок обработки кодов, отражающих состояние групп датчиков. Коды, соответствующие датчикам с отстройкой от "дребезга", обрабатываются с периодичностью, которая соответствует продолжительности "дребезга" (заданному временному интервалу). Коды групп датчиков, не требующих отстройки, обрабатываются в течение всего времени, свободного от обработки кодов датчиков другого типа. После подачи команды "Пуск" начинается обработка группы с номером i 0, предусматривающая запуск отсчета временного интервала. Затем коды обрабатываются в порядке возрастания номеров групп.

После обработки кода группы, описатель которой характеризуется значением признака ПКЦ 1, обрабатываются коды групп, начиная с номера, определяемого значением АГПМ. Такой режим работы продолжается до тех пор, пока не будет завершен отсчет заданного временного интервала (завершение фиксируется путем установки значения ПОВИ 0). Если такое событие зафиксировано, что по завершении обработки кода очередной группы ее номер заносится в рабочий регистр 18, устанавливается значение i 0 и начинается обработка кодов групп датчиков, требующих отстройки от "дребезга". После обработки кода группы, описатель которой характеризуется значением признака ПКЦ1 1, обрабатывается код группы, номер которой был сохранен в регистре 18. В дальнейшем обрабатываются коды датчиков, не требующих отстройки от "дребезга", до момента окончания очередного временного интервала и т.д.

Требуемый порядок обработки кодов реализуется с помощью операторов 16-26 алгоритма. Здесь учтены два частных случая обработки кода группы, описатель которой характеризуется значением признака ПКЦ1 1, обрабатывается код группы, номер которой был сохранен в регистре 18. В дальнейшем обрабатываются коды датчиков, не требующих отстройки от "дребезга", до момента окончания очередного временного интервала и т.д.

Требуемый порядок обработки кодов реализуется с помощью операторов 16-26 алгоритма. Здесь учтены два частных случаях обработки кодов групп. Первый случай характеризуется отсутствием датчиков, требующих отстройки от "дребезга", в микропроцессор подается постоянное значение признака ПОД 1, что обусловливает аналогичное значение признака ПОВИ (он формируется триггером 102) и, следовательно, исключает возможность отсчета временного интервала, которая не требуется (в этом случае операторы 5, 6 алгоритма являются избыточными). Второй частный случай имеет место, когда все опрашиваемые контроллером датчики требуют отстройки от "дребезга". Он характеризуется групповым описателем, в котором задано единичное значение признаков ПКЦ и ПКЦ1 (это последний описатель массива МГОДС). Если заканчивается обработка кода группы, соответствующей этому описателю, то процесс обработки приостанавливается до окончания отсчета временного интервала (такой режим работы обеспечивается с помощью оператора 24 алгоритма).

Активное значение сигнала прерывания СПР, который формируется узлом 14 микропроцессора и отражает факт наличия запросов (запроса) перерывания, обусловленных изменением состояния двухпозиционных датчиков, подается в блок 3 сопряжения контроллера и, в конечном счете, воспринимается управляющей ЭВМ. Реакция ЭВМ на этот инициативный сигнал проявляется в возбуждении операции чтения из контроллера по каналу МИК, когда нет запросов прерывания. При выполнении этой операции блок 3 активизирует сигнал ТДП и после установки единичного значения сигнала РДП формирует значение ЧКП 1 в течение одного цикла синхронизации. Под действием сигнала ЧКП из узла 14 в шину ШДП будет выдан код КНГПЗП (за счет формирования значения сигнала ЧТР0 1 с помощью элемента 114 и дешифратора 99) и сброшен признак группового запроса с номером, содержащимся в коде КНГПЗП (сброс реализуется с помощью логических элементов ИЛИ 672, И 652, группы 59 элементов И, которые формируют сигнал записи в соответствующий регистр из множества 511-514). Этот код принимается в блок 3 и используется вслед за этим для обращения к блоку 2 памяти с целью чтения элемента массива МЗП с вышеуказанным номером. Затем блок 3 выполняет операцию записи в блок 2 нулевого содержимого этого элемента МЗП и сбрасывает в ноль сигнал ТДП. Шестнадцатиразрядное слово, которое содержит информацию о запросах (запросе) прерывания, считанную из микропроцессора из памяти, блоком 3 выдается в МИК. Если по завершении операции чтения кода запросов прерывания сигнал СПР сохраняет активное состояние, аналогичная операция повторно возбуждается ЭВМ.

Микропрограмма контроллера приведена на фиг. 20.

Контроллер КСПИ. Алгоритм работы контроллера (фиг. 18) предусматривает выполнение трех типов операций информационного обмена между блоком памяти контроллера и адресуемыми регистрами, элементами данных, которые относятся к преобразователям информации. Переменная, используемая в алгоритме, соответствует порядковому номеру обменной операции и определяется состоянием счетчиков 16 и 17 (счетчик 16 вырабатывает младшие разряды переменной).

Выполнение любой обменной операции начинается с приема в регистр 86старшего байта описателя операции (оператор 4), содержащего код подлежащей выполнению операции и признаки режимов выполнения. Если признак ПОВП обновления временного интервала имеет единичное значение, то производится запись в регистр 9 из массива МКВУ кода, определяющего продолжительность используемого обменной операцией временного интервала (операторы 5, 6). Если ПОВП 0, то при выполнении обменной операции используется код временной уставки, ранее занесенный в регистр 9.

Оператор 7 соответствует анализу состояния двух младших разрядов регистра 86, содержащих код обменной операции. Если этот код имеет значение 10, то выполняется операция записи кода данных из памяти контроллера в выходные регистры с заданной временной задержкой. При этом с помощью операторов 8, 9 реализуется требуемая временная задержка, а операторы 10, 11, 11а обеспечивают выдачу 16-разрядного кода в выходные регистры с заданными адресами. Вслед за этим производится переход к выполнению очередной обменной операции (операторы 36-39).

Если код операции имеет значение 00, то выполняется операция приема в память контроллера 16-разрядного кода через соответствующие блоки 5 ключей с заданной временной задержкой. В данном случае временная задержка реализуется операторами 14, 15, прием кода операторами 16 19. Если признак ПС 1, то операторы 17, 19 совместно с оператором 13 обеспечивают занесение в массив МПК старшего байта принятого кода, в котором старший разряд имеет значение старшего разряда байта, до этого хранившегося в памяти. Коду старшего байта соответствует код КЗРП, формируемый коммутаторами 424, 423 и 432 (в данном случае УП1 0, ПС 1 и через коммутаторы 423, 424 передается значение а7). Если ПС 0, старший байт принятого кода заносится в массив МПК без изменений.

Дальнейшая последовательность операторов зависит от значения признака ПС. Если ПС 0, то выполнение данной операции завершается и производится переход к выполнению очередной обменной операции. Если ПС 1, то выполняется последовательность операторов, обеспечивающих анализ принятого кода данных. Этот анализ сводится к сравнению значения принятого кода с верхним и нижним допустимыми значениями и регистрации активного состояния признака запроса прерывания, которое формируется, если значение принятого кода выходит за установленные пределы. Сравнение с верхним допустимым значением осуществляется с помощью операторов 21 27, первые четыре из которых производят занесение операндов в регистры 81, 82 (Р0, Р1), операнд А, и 83, 84 (Р2, Р3), операнд В.

Сумматор 10 формирует значение сигнала переноса из старшего разряда  1, если А < В (в данном режиме сигнал переноса П 1 на выходе элемента ИЛИ 292). На основе значений сигналов

1, если А < В (в данном режиме сигнал переноса П 1 на выходе элемента ИЛИ 292). На основе значений сигналов  , ПКВД и а15, b15,

, ПКВД и а15, b15,  (значения старших разрядов регистров 82, 84) логические элементы И 461-465, ИЛИ 471, НЕ 49 формируют значение признака ПЗП-ПИ прерывания, которое регистрируется в узле 14 с помощью в рассматриваемом случае оператора 26. Операторы 26, 27 обеспечивают занесение в байт массива МЗП с номером k, определяемым значением кода КА2 восьмиразрядного кода КГПЗП группы признаков запроса прерывания. Код КГПЗП формируется управляемым дешифратором 38, коммутатором 431, группой 40 дизъюнктивных элементов ИЛИ и характеризуется тем, что значение разряда с номером, определяемым значением кода КА1, соответствует значению ПЗП-ПИ, а остальные разряды сохраняют значения разрядов байта массива МЗП, вчитанного в регистр 85, оператором 25 (байту соответствует код КРЧ).

(значения старших разрядов регистров 82, 84) логические элементы И 461-465, ИЛИ 471, НЕ 49 формируют значение признака ПЗП-ПИ прерывания, которое регистрируется в узле 14 с помощью в рассматриваемом случае оператора 26. Операторы 26, 27 обеспечивают занесение в байт массива МЗП с номером k, определяемым значением кода КА2 восьмиразрядного кода КГПЗП группы признаков запроса прерывания. Код КГПЗП формируется управляемым дешифратором 38, коммутатором 431, группой 40 дизъюнктивных элементов ИЛИ и характеризуется тем, что значение разряда с номером, определяемым значением кода КА1, соответствует значению ПЗП-ПИ, а остальные разряды сохраняют значения разрядов байта массива МЗП, вчитанного в регистр 85, оператором 25 (байту соответствует код КРЧ).