Изобретение относится к множительным устройствам на логических элементах и может использоваться в вычислительных устройствах и системах автоматического управления для преобразования данных в частотно-импульсном коде.

Известно устройство для умножения частоты на код, содержащее делитель, управляемьш кодом, счетчик, регистр и управляемый счетчик, выход которото соединен с выходом устройства для умножения частоты на код, вход которого соединен,через формирователь с входами сброса делителя управляемого кодом, счетчшса и входом записи регистра, выходы которого соединены с управляющими входами управляемого счетчика, счетный вход которого соединен с выходом генератора тактовых импульсов,, который соединен со счетным входом делителя, управляемого кодом,ВЫХОД которого соединен со счетным входом счетчика, а управляющие входы делителя, управляемого кодом, соединены с управляющими входами устройства для умноже.ния частоты на код 01.

Недостатком этого устройства является отсутствие контроля за выходом частоты входных диг}шлов за допустимые пределы.

Наиболее близким к пpeдлaгaef;. является устройство для умножения .частоты на код, содержащее генератор тактовых импульсов, управляемый делитель, счетчик, регистр и управляемый счетчик, выход которого соединен .с выходом устройства для умножения частоты на код, вход которого соединен с тактовым входом регистра и входом сброса счетчика, счетный вход которого соединен с выходом управляемого делителя, управляющие входы которого соединены с управляющими входами устройства для умножения частоты на код, а вход управляемого делителя соединен с выходом генератора тактовых импульсов, который соединен со счетным входом управляемого счетчика, управляющие входы которог.о соединены с выходами регистра, входы которого соединены с выходами счетчика 2j .

Недостатками этого устройства является возможность появления погрешностей в формируемом частотно- импульсном сигнале, что связано с

ограниченностью его частотного диапазона, а следовательно, низкая достоверность функционирования.

Целью изобретения является расширение частотного диапазона при повышер{ии достоверности функционирования.

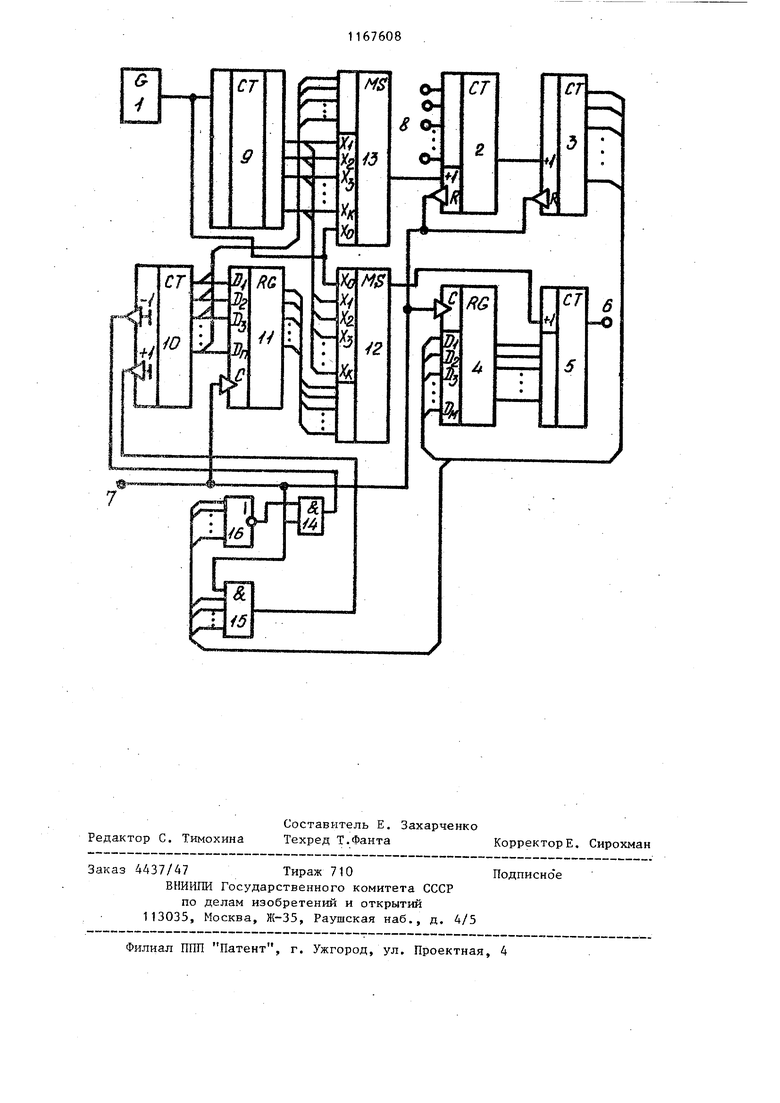

Поставленная цель достигается тем, что в устройство для умножения частоты на код, содержащее генератор тактовых импульсов, делитель частоты, счетчик, регистр и управляющий делитель, выход которого соединен с выходом устройства, информационный вход которого соединен со входами сброса делителя частоты и счетчика и тактовым входом регистра, информационные входы которого соединены с выходами счетчика, счетный вход которого соединен с выходом делителя частоты, информационные входы которого соединены со входами кода устройства, информационные входы управляющего делителя соединены с выходами регистра, введены многоразрядный делитель частоты, два мультиплексора, дополнительный регистр, реверсивный счет.чик, два элемента И и элемент ИЛИ-НЕ, причем выход генератора тактовых импульсов соединен с тактовыми входами первого и второго мультиплексоров и многоразрядного делителя частоты, выходы которого соединены с информационными входами первого и второго мультиплексоров, выходы которых соединены со счетными входами делителя частоты и управляющего делителя соответственно, адресные входы первого мультиплексора соединены с выходами реверсивного счетчика и информационными входами дополнительного регистра, выходы которого соединены с адресными входами второго мультиплексора, вход вычитания реверсивного счетчика соединен с выходом первого элемента И, первый вход которого соединен с выходом элемента ИЛИ-НЕ, входы которого соединены с выходами счетчика, и входами, кроме первого, второго элемента И, выход которого соединен со входом сложения реверсивного счетчика, первый вход второго элеменta И,второй вход первого элемента И,тактовые входы дополнительного регистра и регистра соединены с частотным информационным входом устройства. На чертеже представлена структурная схема предлагаемого устройства. Устройство для умножения частоты на код содержит генератор 1 тактовых импульсов, делитель-2 частоты, счетчик 3, регистр 4,управляющий делитель 5, выход 6 устройства, вход 7 устройства, входы кода 8 .устройства многоразрядный делитель 9 частоты, реверсивный счетчик 10, дополнительный регистр 11, первый 12 и второй мультиплексоры, первый 14 и второй 15 элементы И и элемент ИЛИ-НЕ 16. Устройство работает следующим образом. Опорный сигнал с частотой f подается на вход 7. На вход 8 подается код, определяющий коэффициент умноже ния частоты , . Если „ не изменя ется, в реверсивном счетчике 10 фиксируется код, совпадающий с кодом на выходе регистра 11, в соответстви с которым; на выходах мультиплексоров 12 и 13 формируются последовательности импульсов с частотой f, удовлетворяющих допустимым пределам Эти импульсы проходят через делитель 2 и фиксируются счетчиком 3, в котором за время l/fg накапливается код N , где К - коэффициент деления делителя 2, определяемый кодом на входах 8. Код N при поступлении следующего импульса переписывается в регистр 4, который обеспечивает управление делителем 5, на выходе которого формируется сигнал с частотой f-b,,, тг- K-f . При поступлении каждого опорного импульса на вход 7 с помощью элементов 15 и , 16 осуществляется контроль кода N. Если он недопустимо мал, все его старшие разряды нулевые и на выходе элемента 16 появляется логическая единица, благодаря чему импульс опорной частоты проводит через элемент 14 на реверсивный счетчик, состояние которого изменяется, что выэьгеает изменение тактовой частоты на выходе мультиплексора 13, которьй переключается. При поступлении следующего импульса опорной частоты состояние реверсивного счетчика 10 переписывается в регистр 11, что вы- зьюает аналогичное переключение мультиплексора 12. Таким образом, обеспечивается задержка изменения частоты тактовых импульсов, поступающих с делителя 9 на один период, что исключает ошибки при переходе от одного, диапазона к другому. При превьпиении кодом N максималоного значения аналогичньм образом опорный сигнал проходит через элемент 15, вызывая обратное изменение тактовой частоты f-f . Таким образом, обеспечивается расширение частотного диапазона при повышении достоверности функционирования, что позволяет работать в более широком частотном диапазоне значений f j, при повьшении достоверности функционирования. Это позволяет расширить частотньй диапазон и повысить надежность аппаратуры, использующей устройство для умножения частоты на код.

G- У

СТ

/

fo

СТ

СП д

о- о От

/

raL

&

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель элементов матрицы спектральной плотности мощности двух сигналов | 1989 |

|

SU1661667A2 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Перемножающее устройство | 1984 |

|

SU1220007A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2018977C1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367035A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ НА КОД, содержащее генератор тактовых импульсов, делитель частоты, счетчик, регистр, управляющий делитель, выход которого соединен с выходом устройства, информационный вход которого соединен с входами сброса делителя частоты и счетчика и тактовым входом регистра, информационные входы которого соединены с выходами счетчика, -счетньй вход которого соединен с выходом делителя частоты, информационные входы которого соединены с входами кода устройства, информационные входы управляющего делителя соединены с выходами регистра, отличающееся тем, что, с целью расширения частотного диапазона при повышении достоверности функционирования, в него введены многоразрядный делитель частоты, два мультиплексора, дополнительный регистр, реверсивньй счетчик, два элемента И и элемент ИЛИ-НЕ, причем выход генератора тактовых импульсов соединен с тактовыми входами первого и второго мультиплексоров и многоразрядного делителя частоты, выходы которого соединены с информационными входами первого и второго мультиплексоров, выходы которых соединены с счетными входами делителя частоты и управляющего делителя соответственно, адресные входы первого мультиплексора соединены с выходами реверсивного счетчика и информационными (Л входами дополнительного регистра, выходы которого соединены с адресными входами второго мультиплексора, вход вычитания реверсивного счетчика соединен с выходом первого элемента И, первый вход которого соединен с выходом элементаИЛИ-НЕ, входы которого соединены с выходами счетчика а и с входами, кроме первого, второго элемента И, выход которого соединен 05 с входом сложения реверсивного счетО 00 чика, первый вход второго элемента И, второй вход первого элемента И, тактовые входы дополнительного регистра и регистра соединены с частотным информационньм входом устройства.

т

/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство умножения частоты на код | 1976 |

|

SU580555A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой следящий умножитель частоты | 1977 |

|

SU634277A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип). | |||

Авторы

Даты

1985-07-15—Публикация

1984-01-02—Подача