т т

сриг 1

г т

Изобретение относится к области энергетики, может быть использовано для определения частотных характеристик объектов автоматического управления и является усовершенствованием известного устройства по основному авт„ св. № 1307375,

Цель изобретения - расширение функциональных возможностей путем измерения временного сдвига двух iсигналов, измерения элементов матрицы спектральной плотности мощности двух сигналов.

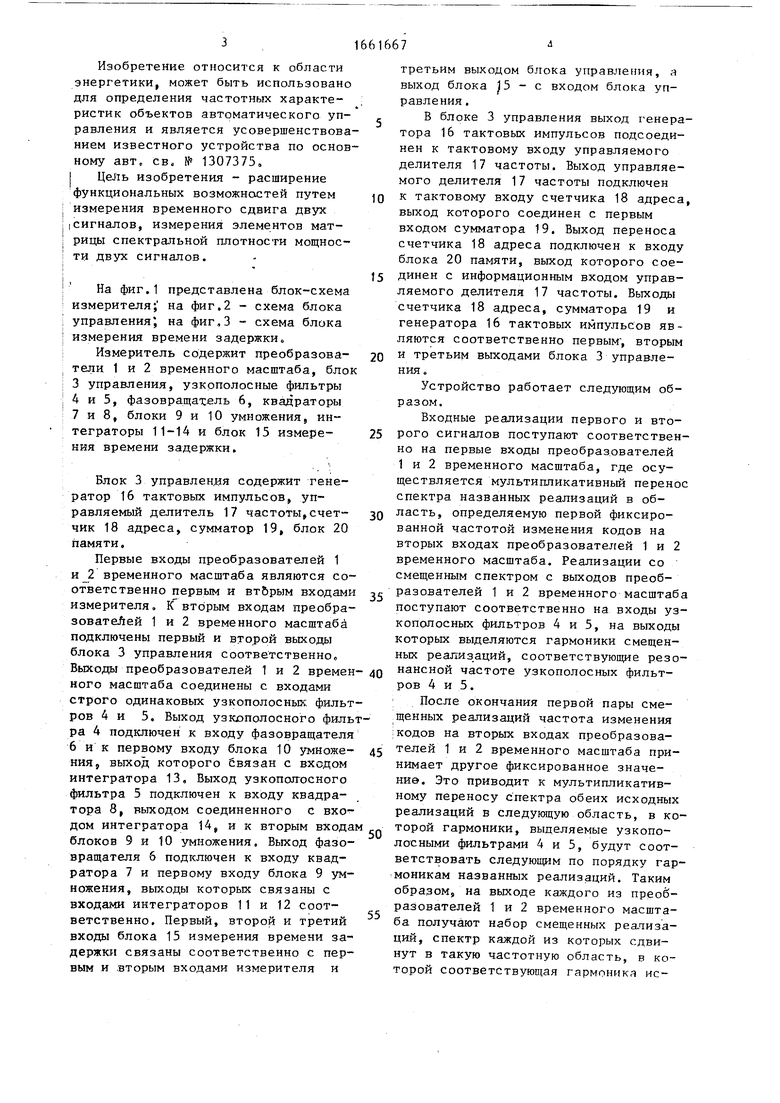

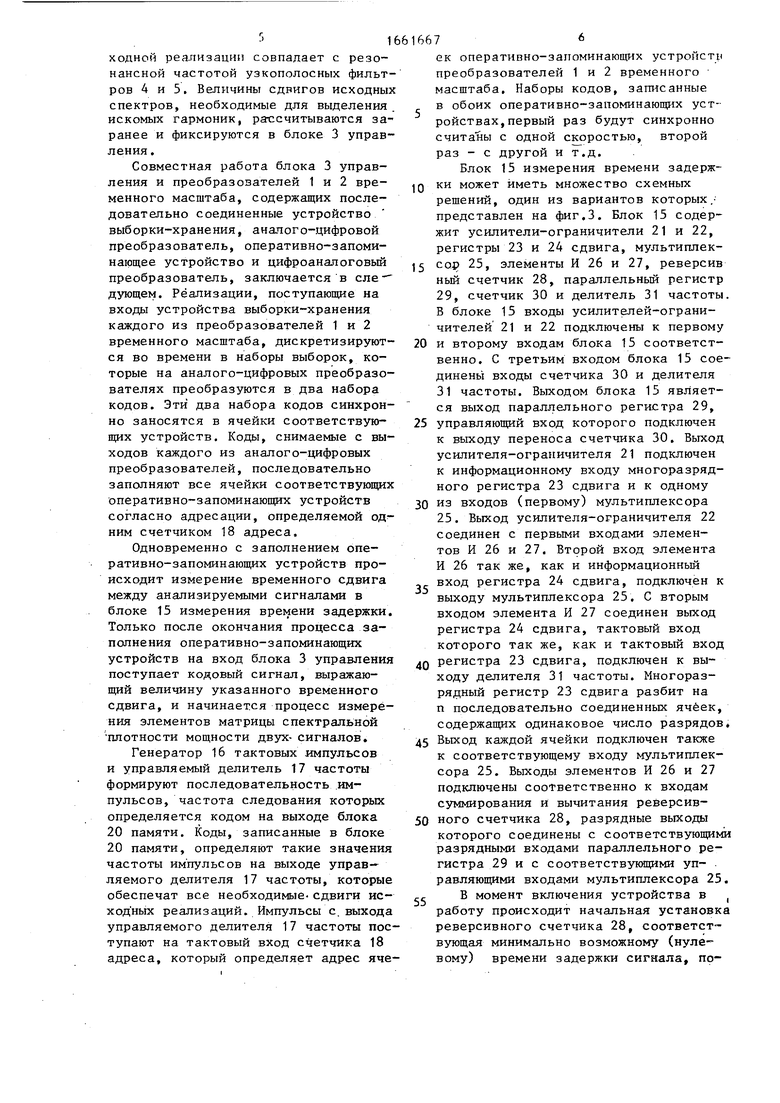

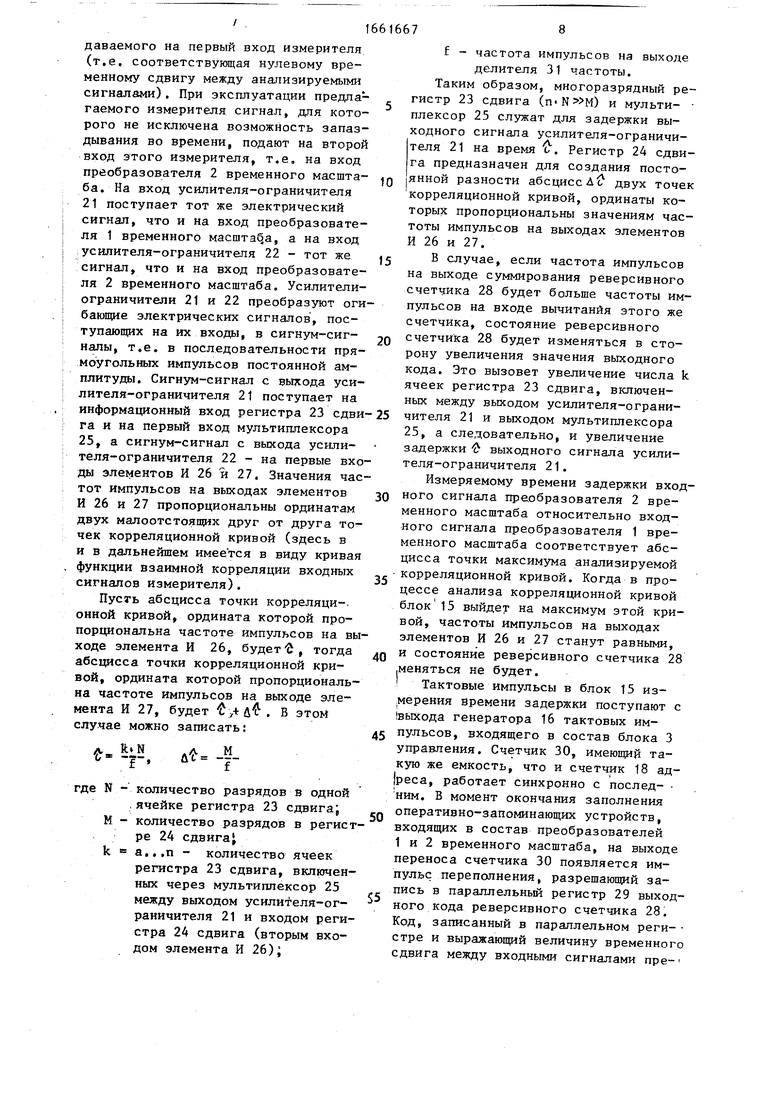

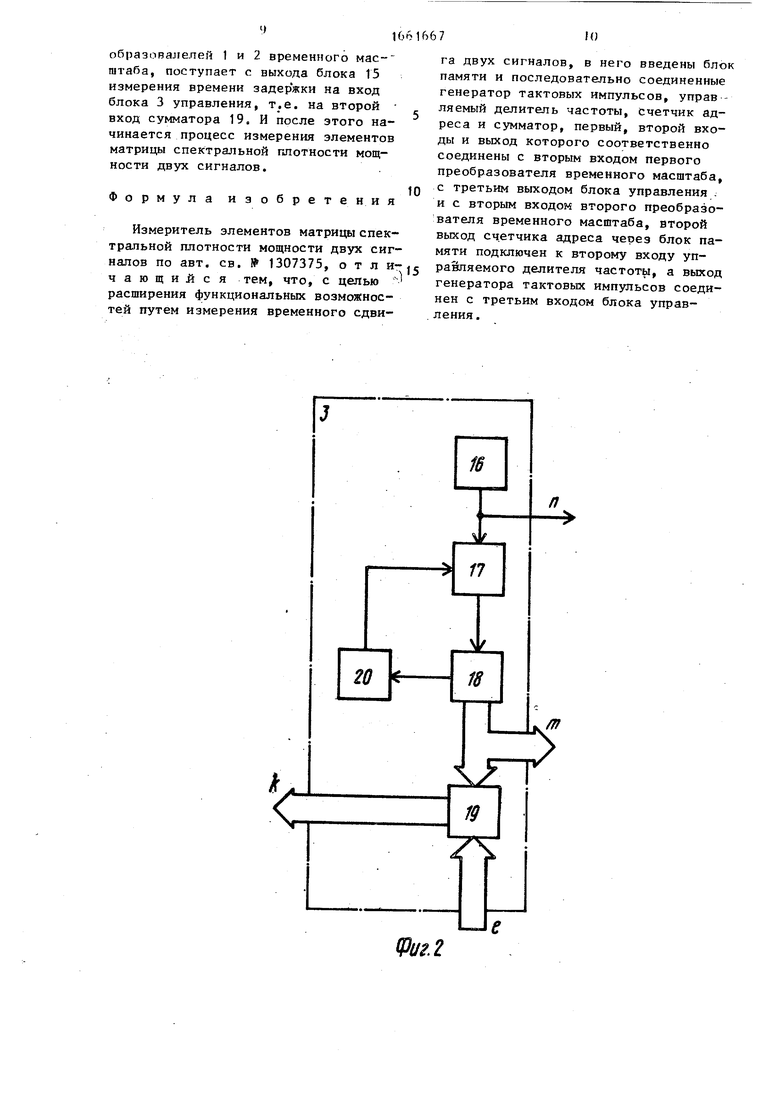

На фиг.1 представлена блок-схема измерителя; на фиг,2 - схема блока управления , на фиг,3 - схема блока измерения времени задержки.

Измеритель содержит преобразова- тели 1 и 2 временного масштаба, блок

3управления, узкополосные фильтры

4и 5, фазовращатель 6, квадраторы 7 и 8, блоки 9 и 10 умножения, интеграторы 11-14 и блок 15 измере- ния времени задержки.

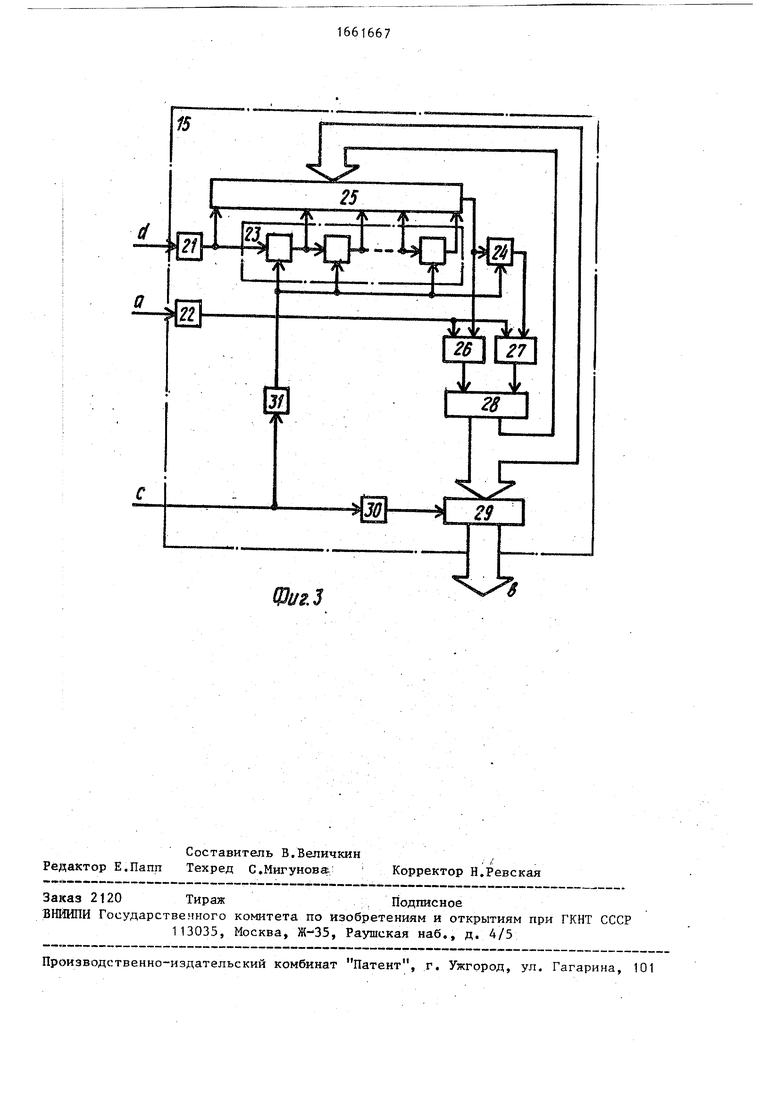

Блок 3 управления содержит генератор 16 тактовых импульсов, управляемый делитель 17 частоты,счет- чик 18 адреса, сумматор 19, блок 20 памяти.

Первые входы преобразователей 1 временного масштаба являются соответственно первым и втбрым входами измерителя. if вторым входам преобразователей 1 и 2 временного масштаба подключены первый и второй выходы блока 3 управления соответственно. Выходы преобразователей 1 и 2 времен ного масштаба соединены с входами строго одинаковых узкополосных фильтров 4 и 5. Выход узюэполосного фильра 4 подключен к входу фазовращателя 6 и к первому входу блока 10 умноже- ния, выход которого бвязан с входом интегратора 13, Выход узкопоггосного фильтра 5 подключен к входу квадратора 8, выходом соединенного с входом интегратора 14, и к вторым входа блоков 9 и 10 умножения. Выход фазовращателя 6 подключен к входу квадратора 7 и первому входу блока 9 умножения, выходы которых связаны с входами интеграторов 11 и 12 соответственно. Первый, второй и третий входы блока 15 измерения времени задержки связаны соответственно с первым и вторым входами измерителя и

третьим выходом блока управления, я выход блока J5 - с входом блока управления .

В блоке 3 управления выход генератора 16 тактовых импульсов подсоединен к тактовому входу управляемого делителя 17 частоты. Выход управляемого делителя 17 частоты подключен к тактовому входу счетчика 18 адреса выход которого соединен с первым входом сумматора 19. Выход переноса счетчика 18 адреса подключен к входу блока 20 памяти, выход которого соединен с информационным входом управляемого делителя 17 частоты. Выходы счетчика 18 адреса, сумматора 19 и генератора 16 тактовых импульсов являются соответственно первым, вторым и третьим выходами блока 3 управления.

Устройство работает следующим образом.

Входные реализации первого и второго сигналов поступают соответственно на первые входы преобразователей 1 и 2 временного масштаба, где осуществляется мультипликативный перено спектра названных реализаций в область, определяемую первой фиксированной частотой изменения кодов на вторых входах преобразователей 1 и 2 временного масштаба. Реализации со смещенным спектром с выходов преобразователей 1 и 2 временного масштаб поступают соответственно на входы узкополосных фильтров 4 и 5, на выходы которых выделяются гармоники смещенных реализаций, соответствующие резонансной частоте узкополосных фильтров 4 и 5.

После окончания первой пары смещенных реализаций частота изменения кодов на вторых входах преобразователей 1 и 2 временного масштаба принимает другое фиксированное значение. Это приводит к мультипликативному переносу спектра обеих исходных реализаций в следующую область, в которой гармоники, выделяемые узкополосными фильтрами 4 и 5, будут соответствовать следующим по порядку гармоникам названных реализаций. Таким образом9 на выходе каждого из преобразователей 1 и 2 временного масштаба получают набор смещенных реализаций, спектр каждой из которых сдвинут в такую частотную область, в которой соответствующая гармлникл ис1

ходной реализации совпадает с резонансной частотой узкополосных фильтров 4 и 5. Величины сдвигов исходных спектров, необходимые для выделения искомых гармоник, рассчитываются заранее и фиксируются в блоке 3 управления.

Совместная работа блока 3 управления и преобразователей 1 и 2 временного масштаба, содержащих последовательно соединенные устройство выборки-хранения, анач ого-цифровой преобразователь, оперативно-запоминающее устройство и цифроаналоговый преобразователь, заключается в еле дующем. Реализации, поступающие на входы устройства выборки-хранения каждого из преобразователей 1 и 2 временного масштаба, дискретизируют- ся во времени в наборы выборок, которые на аналого-цифровых преобразователях преобразуются в два набора кодов. Эти два набора кодов синхронно заносятся в ячейки соответствующих устройств. Коды, снимаемые с выходов каждого из аналого-цифровых преобразователей, последовательно заполняют все ячейки соответствующих оперативно-запоминающих устройств согласно адресации, определяемой одним счетчиком 18 адреса.

Одновременно с заполнением оперативно-запоминающих устройств происходит измерение временного сдвига между анализируемыми сигналами в блоке 15 измерения времени задержки. Только после окончания процесса заполнения оперативно-запоминающих устройств на вход блока 3 управления поступает кодовый сигнал, выражающий величину указанного временного сдвига, и начинается процесс измерения элементов матрицы спектральной плотности мощности двух- сигналов.

Генератор 16 тактовых импульсов и управляемый делитель 17 частоты формируют последовательность импульсов, частота следования которых определяется кодом на выходе блока 20 памяти. Коды, записанные в блоке 20 памяти, определяют такие значения частоты импульсов на выходе управляемого делителя 17 частоты, которые обеспечат все необходимые- сдвиги исходных реализаций. Импульсы с выхода управляемого делителя 17 частоты поступают на тактовый вход счетчика 18 адреса, который определяет адрес яче667й

ек оперативно-запоминающих устройств преобразователей 1 и 2 временного масштаба. Наборы кодов, записанные в обоих оперативно-запоминающих устройствах, первый раз будут синхронно считаны с одной скоростью, второй раз - с другой и т.д.

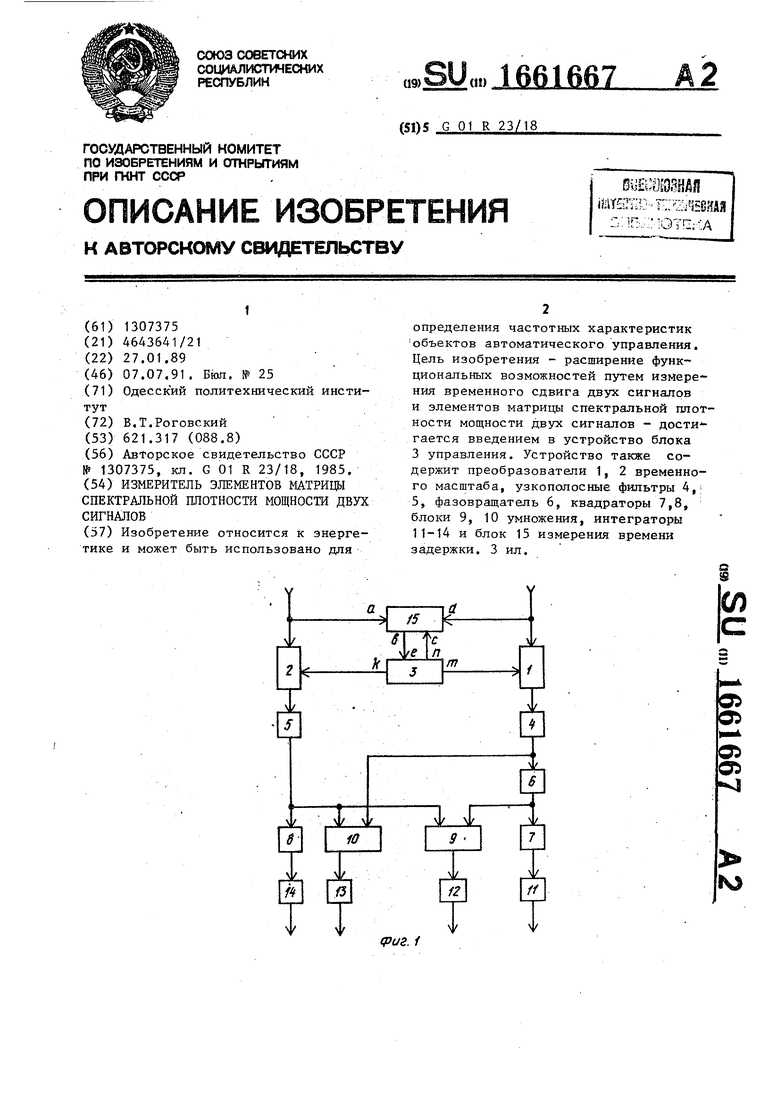

Блок 15 измерения времени задержки может иметь множество схемных решений, один из вариантов которых.- представлен на фиг.З. Блок 15 содержит усилители-ограничители 21 и 22, регистры 23 и 24 сдвига, мультиплек5 сор 25, элементы И 26 и 27, реверсив ный счетчик 28, параллельный регистр 29, счетчик 30 и делитель 31 частоты. В блоке 15 входы усилителей-ограничителей 21 и 22 подключены к первому

0 и второму входам блока 15 соответственно. С третьим входом блока 15 соединены входы счетчика 30 и делителя 31 частоты. Выходом блока 15 является выход параллельного регистра 29,

5 управляющий вход которого подключен к выходу переноса счетчика 30. Выход усилителя-ограничителя 21 подключен к информационному входу многоразрядного регистра 23 сдвига и к одному

0 из входов (первому) мультиплексора 25. Выход усилителя-ограничителя 22 соединен с первыми входами элементов И 26 и 27. Второй вход элемента И 26 так же, как и информационный вход регистра 24 сдвига, подключен к выходу мультиплексора 25. С вторым входом элемента И 27 соединен выход регистра 24 сдвига, тактовый вход которого так же, как и тактовый вход

Q регистра 23 сдвига, подключен к выходу делителя 31 частоты. Многоразрядный регистр 23 сдвига разбит на п последовательно соединенных ячеек, содержащих одинаковое число разрядов

5 Выход каждой ячейки подключен также к соответствующему входу мультиплексора 25. Выходы элементов И 26 и 27 подключены соответственно к входам суммирования и вычитания реверсив0 ного счетчика 28, разрядные выходы которого соединены с соответствующими разрядными входами параллельного регистра 29 и с соответствующими управляющими входами мультиплексора 25. В момент включения устройства в ( работу происходит начальная установка реверсивного счетчика 28, соответствующая минимально возможному (нулевому) времени задержки сигнала, по-

5

5

даваемого на первый вход измерителя (т.е. соответствующая нулевому временному сдвигу между анализируемыми сигналами). При эксплуатации предлагаемого измерителя сигнал, для которого не исключена возможность запаздывания во времени, подают на второй вход этого измерителя, т.е. на вход преобразователя 2 временного масштаба. На вход усилителя-ограничителя 21 поступает тот же электрический сигнал, что и на вход преобразователя 1 временного масштаба, а на вход усилителя-ограничителя 22 - тот же сигнал, что и на вход преобразователя 2 временного масштаба. Усилители- ограничители 21 и 22 преобразуют огибающие электрических сигналов, поступающих на их входы, в сигнум-сигналы, т.е. в последовательности прямоугольных импульсов постоянной амплитуды. Сигнум-сигнал с выхода усилителя-ограничителя 21 поступает на информационный вход регистра 23 сдви га и на первый вход мультиплексора 25, а сигнум-сигнал с выхода усилителя-ограничителя 22 - на первые входы элементов И 26 и 27. Значения частот импульсов на выходах элементов И 26 и 27 пропорциональны ординатам двух малоотстоящих друг от друга точек корреляционной кривой (здесь в и в дальнейшем имеется в виду кривая функции взаимной корреляции входных сигналов измерителя).

Пусть абсцисса точки корреляци-. онной кривой, ордината которой пропорциональна частоте импульсов на выходе элемента И 26, будет Ј, тогда абсцисса точки корреляционной кривой, ордината которой пропорциональна частоте импульсов на выходе элемента И 27, будет . В этом случае можно записать:

е-Ц2

Г

At- -fде N - количество разрядов в одной ячейке регистра 23 сдвига;

М - количество разрядов в регистре 24 сдвига

k e а,,.п - количество ячеек

регистра 23 сдвига, включенных через мультиплексор 25 между выходом усилителя-ограничителя 21 и входом регистра 24 сдвига (вторым входом элемента И 26)J

f - частота импульсов на выходе

делителя 31 частоты. Таким образом, многоразрядный регистр 23 сдвига () и мульти- плексор 25 служат для задержки выходного сигнала усилителя-ограничителя 21 на время Ј. Регистр 24 сдви

0

5 о

5

0

5

0

5

га предназначен для создания янной разности абсцисс Д с двух

постоточек

корреляционной кривой, ординаты которых пропорциональны значениям частоты импульсов на выходах элементов И 26 и 27.

В случае, если частота импульсов на выходе суммирования реверсивного счетчика 28 будет больше частоты импульсов на входе вычитания этого же счетчика, состояние реверсивного счетчика 28 будет изменяться в сторону увеличения значения выходного кода. Это вызовет увеличение числа k ячеек регистра 23 сдвига, включенных между выходом усилителя-ограничителя 21 и выходом мультиплексора 25, а следовательно, и увеличение задержки Ј выходного сигнала усилителя-ограничителя 21.

Измеряемому времени задержки входного сигнала преобразователя 2 временного масштаба относительно входного сигнала преобразователя 1 временного масштаба соответствует абсцисса точки максимума анализируемой корреляционной кривой. Когда в процессе анализа корреляционной кривой блок 15 выйдет на максимум этой кривой, частоты импульсов на выходах элементов И 26 и 27 станут равными, и состояние реверсивного счетчика 28 .меняться не будет. Тактовые импульсы в блок 15 измерения времени задержки поступают с 1выхода генератора 16 тактовых импульсов, входящего в состав блока 3 управления. Счетчик 30, имеющий такую же емкость, что и счетчик 18 ад- |реса, работает синхронно с послед- ним. В момент окончания заполнения оперативно-запоминающих устройств, входящих в состав преобразователей 1 и 2 временного масштаба, на выходе переноса счетчика 30 появляется импульс переполнения, разрешающий запись в параллельный регистр 29 выходного кода реверсивного счетчика 28. Код, записанный в параллельном реги- стре и выражающий величину временного сдвига между входными сигналами преобразовалелей 1 и 2 временного мае-- штаба, поступает с выхода блока 15 измерения времени задержки на вход блока 3 управления, т.е. на второй вход сумматора 19. И после этого начинается процесс измерения элементов матрицы спектральной плотности мощности двух сигналов.

Формула изобретения

Измеритель элементов матрицы спектральной плотности мощности двух сигналов по авт. св. 9 1307375, отличающийся тем, что, с целью расширения функциональных возможностей путем измерения временного сдви

га двух сигналов, в него введены блок памяти и последовательно соединенные генератор тактовых импульсов, управ - ляемый делитель частоты, счетчик адреса и сумматор, первый, второй входы и выход которого соответственно соединены с вторым входом первого преобразователя временного масштаба,

я с третьим выходом блока управления - и с вторым входом второго преобразователя временного масштаба, второй выход счетчика адреса через блок памяти подключен к второму входу упje равляемого делителя частоты, а выход генератора тактовых импульсов соединен с третьим входом блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Коррелятор | 1981 |

|

SU1024933A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1995 |

|

RU2096801C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

Изобретение относится к энергетике и может быть использовано для определения частотных характеристик объектов автоматического управления. Цель изобретения - расширение функциональных возможностей путем измерения временного сдвига двух сигналов и элементов матрицы спектральной плотности мощности двух сигналов - достигается введением в устройство блока 3 управления. Устройство также содержит преобразователи 1, 2 временного масштаба, узкополосные фильтры 4, 5, фазовращатель 6, квадраторы 7, 8, блоки 9, 10 умножения, интеграторы 11 - 14 и блок 15 измерения времени задержки. 3 ил.

(Риг. 2

feJ

| Измеритель элементов матрицы спектральной плотности мощности двух сигналов | 1985 |

|

SU1307375A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-07-07—Публикация

1989-01-27—Подача