К5 00

о

о

4

ГО

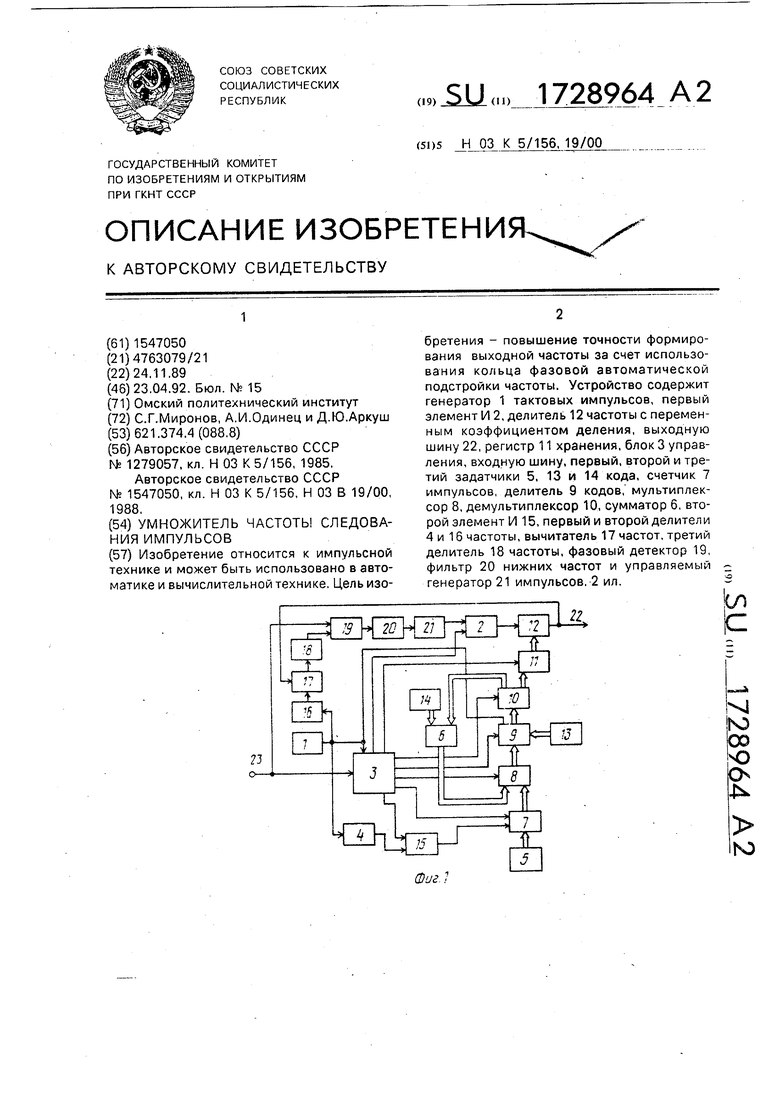

Изобретение относится к импульсной технике, может быть использовано в устройствах автоматики, вычислительной техники, в преобразователях частоты и измерительной технике и является усовершенствованием известного умножителя по авт.св. № 1547050,

Известен цифровой умножитель частоты следования периодических импульсов, содержащий генератор тактовых импульсов (ГТИ), делитель частоты с переменным коэффициентом деления (ДПКД), запоминающий регистр, делитель частоты, счетчик импульсов и формирователь импульсов сброса.

Однако такой умножитель обладает недостаточной надежностью из-за возможности сбоев в работе в момент его запуска.

Известен умножитель частоты следования периодических импульсов, содержащий ГТИ, ДПКД, запоминающий регистр, делитель частоты, счетчик импульсов, формирователь импульсов сброса, элемент И и формирователь управляющих импульсов. ГТИ подключен к первому входу элемента И и к входу делителя частоты, выход которого соединен с входом счетчика импульсов. Импульсы входной частоты поступают на входы формирователя импульсов сброса и формирователя управляющих импульсов, на вход записи запоминающего регистра. Выход формирователя импульсов сброса подключен к входам обнуления счетчика импульсов и делителя частоты. Выход формирователя управляющих импульсов соединен с вторым входом элемента И, а выход элемента И - со счетным входом ДПКД, выход которого соединен с выходной шиной. Выходы счетчика импульсов подключены через запоминающий регистр к информационным входам ДПКД. На выходе умножителя частоты формируется последовательность импульсов с частотой

Рвых П FBX,

где п - коэффициент умножения;

FBX - входная частота.

Недостатком умножителя частоты является невозможность использования его в качестве следящего гетеродина в цифровом следящем анализаторе спектра, в канале фильтрации которого используются узкополосные прецизионные кварцевые или электромеханические фильтры с центральной частотой 8 или 128 кГц из-за невозможности добавления к выходной частоте постоянной частотной подставки.

Наиболее близким к предлагаемому является умножитель частоты следования импульсов, содержащий ГТИ, первый элемент И, блок управления, делитель частоты, первый задатчик кода, сумматор, счетчик импульсов, мультиплексор, делитель кодов, де- мультиплексор, регистр хранения, ДПКД, второй задатчик кода, второй элемент И.

ГТИ через первый элемент И соединен

с тактовым входом ДПКД, выход которого соединен с выходной шиной, а информационные входы соединены с выходами регистра хранения. Первый вход блока управления

0 соединен с входной шиной, второй вход - с выходом ГТИ, с тактовым входом делителя кодов и с входом делителя частоты, выход которого соединен с первым входом второго элемента И, выход которого соединен со

5 счетным входом счетчика импульсов, информационные входы которого соединены с выходами первого задатчика кода, выходы - с первой группой входов мультиплексора, выходы которого с первой группой входов

0 делителя кодов, вторая группа входов которого соединена с выходами второго задатчика кода, выходы - с выходами демульгиплексора, первая группа выходов которого соединена с информационными

5 входами регистра хранения, вторая группа выходов - с первой группой входов сумматора, вторая группа входов которого соединена с выходами третьего задатчика кода, выходы - с второй группой входов мульти0 плексора. Первый и второй выходы блока управления соединены с вторыми входами соответственно первого и второго элементов И, третий выход соединен с установочным входом счетчика импульсов, четвертый

5 выход - с входом управления мультиплексора, пятый выход - с входом запуска делителя кодов, шестой выход - с входом управления мультиплексора и седьмой выход - с входом записи регистра хранения.

0 Блок управления содержит первый элемент И, первый вход которого соединен с первым входом блока управления и с вторым входом сброса счетчика импульсов, выход - с тактовыми входами первого и

5 второго триггеров, инверсный выход первого из которых соединен с его информацион- ным входом, прямой выход - с информационным входом второго триггера, инверсный выход которого соединен со вто0 рым входом первого элемента И, прямой выход - с информационным входом третьего триггера, прямой выход которого соединен с первым выходом второго элемента И, выход которого соединен со счетным вхо5 дом счетчика импульсов, выходы которого соединены с адресными входами запоминающего устройства, первый - пятый выходы которого соединены соответственно с вторым - шестым выходами блока управления, седьмой выход которого соединен с тактовым входом третьего триггера и с шестым выходом постоянного запоминающего устройства, седьмой выход которого соединен с вторым входом второго элемента И.

На выходе устройства получается последовательность импульсов с частотой

М

вх

n +Fr

т.е. в выходной сигнал введена постоянная частотная подставка с возможностью ее изменения в широких пределах путем изменения кода, подаваемого на вторую группу входов сумматора с выходов первого задат- чика кода.

Недостатком известного умножителя является низкая точность формирования частоты выходных импульсов, обусловленная ограниченной разрядностью ДПКД и погрешностью измерения входной частоты. Такой умножитель невозможно использовать в качестве следящего гетеродина анализатора спектра, в канале фильтрации которого используются узкополосные (с полосой пропускания от единиц до десятков герц) фильтры с центральной частотой 8 или 128 кГц.

Цель изобретения - повышение точности формирования выходной частоты.

Указанная цель достигается тем, что в умножителе частоты следования импульсов, содержащем ГТИ, первый элемент И, выход которого соединен с выходной шиной, а информационные входы подключены к выходам регистра хранения, блок управления, первые вход и выход которого соединены соответственно с входной шиной и с первым входом первого элемента И, первый, второй и третий задатчики кодов, счетчик импульсов, информационные входы которого соединены с выходами первого задатчика кода, делитель кодов, мультиплексор, сумматор, второй элемент И и делитель частоты, вход и выход которого соединены соответственно с выходом ГТИ и первым входом второго элемента И, второй вход которого соединен с вторым выходом блока управления, третий выход которого соединен с установочным входом счетчика импульсов, счетный вход которого соединен с выходом второго элемента И, выходы - с первой группой входов мультиплексора, выходы которого соединены с первой группой входов делителя кодов, вторая группа входов которого соединена с выходами второго задатчика кодов, тактовый вход - с выходом ГТИ, выходы - с входами мультиплексора, первая группа выходов которого соединена с информационными входами регистра хранения, вторая группа выходов - с первой

группой входов сумматоров, вторая группа входов которого соединена с выходами третьего задатчика кода, выходы - с второй группой входов мультиплексора, управляющий вход которого соединен с четвертым выходом блока управления, пятый, шестой, седьмой выходы которого соединены с выходами соответственно запуска делителя кодов, управления демультиплексора и за0 писи регистра хранения, введена между выходом ГТИ и вторым входом первого элемента И цепь из последовательно соединенных второго делителя частоты, вычитате- ля частот, второй вход которого соединен с

5 выходной шиной, третьего делителя частоты, фазового детектора, второй вход которого соединен с входной шиной, фильтра нижних частот, управляемого ГТИ.

Сравнение предлагаемого технического

0 решения с другими показывает, что делители и вычитатели частот, а также системы ФАПЧ, содержащие фазовый детектор, фильтр нижних частот, управляющий элемент и перестраиваемый генератор, извест5 ны.

Однако при использовании этих блоков в цифровом умножителе частоты следования импульсов для компенсации в выходном сигнале ошибки rio частоте они проявляют

0 новые свойства, что приводит к повышению точности формирования выходного сигнала. При этом выходной сигнал умножителя частоты синтезируется с точностью до фазы в соответствии с выражением

5Рвых П F ex + Fn

Таким образом, становится возможным использование предлагаемого множителя в качестве цифрового гетеродина следящего анализатора спектра, который содержит уз- О кополосные полосовые фильтры,

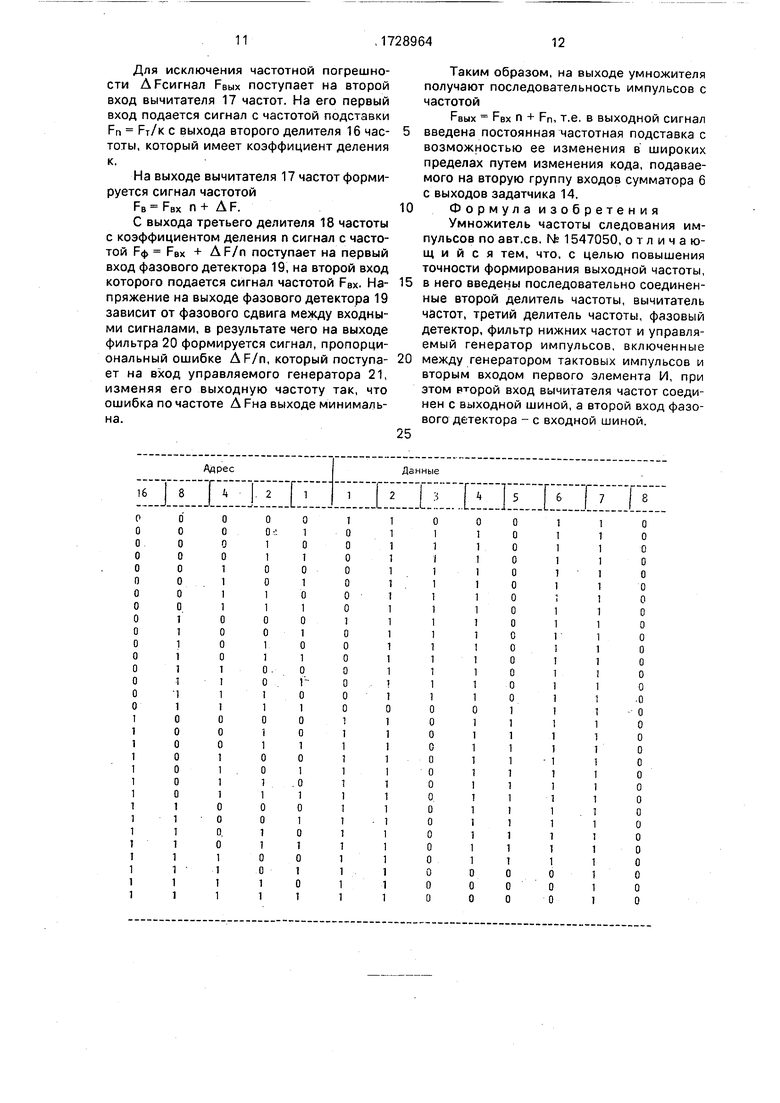

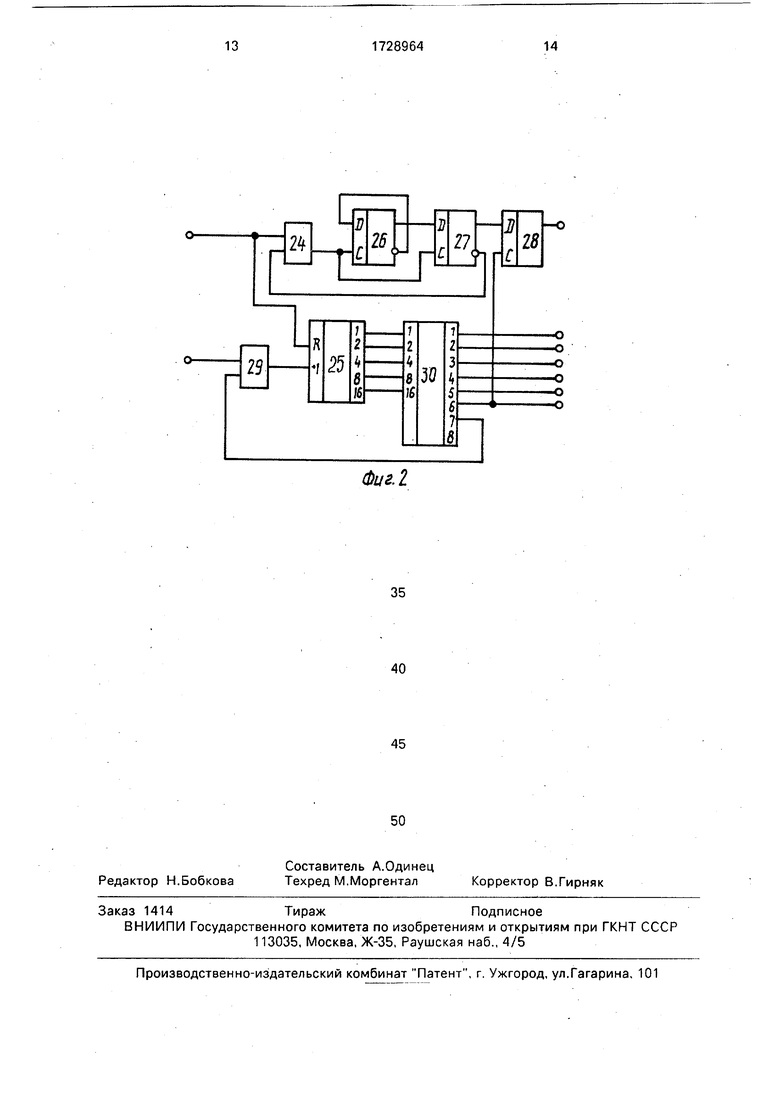

На фиг.1 изображена электрическая структурная схема предлагаемого умножителя; на фиг.2 - блок управления.

Умножитель содержит генератор 1 так- 5 товых импульсов, первый элемент И 2, блок 3 управления, первый делитель 4 частоты, первый задатчик5 кода, сумматор 6, счетчик 7 импульсов, мультиплексор 8, делитель 9 кодов, демультиплексор 10, регистр 11 хра- 0 нения, ДПКД 12, второй задатчик 13 кода, третий задатчик 14 кода, второй элемент И 15, второй делитель 16 частоты, вычитате ь 17 частот, третий делитель 18 частоты, фазовый детектор 19, фильтр 20 нижних частот и 5 управляемый генератор 21 импульсов. Генератор 1 тактовых импульсов через второй делитель 16 частоты, вычитатель 17 частот, третий делитель 18 частоты, фазовый детектор 19, фильтр 20 нижних частот, управляемый генератор 21 импульсов и первый

элемент И 2 соединены с тактовым входом делителя 12 с переменным коэффициентом деления, выход которого соединен с выходной шиной 22 и с вторым входом вычитателя 17 частот, а информационные входы соединены с выходами регистра 11 хранения.

Персый вход блока 3 управления соединен с входной шиной 23 и с вторым входом фазового детектора 19, второй вход с выходом генератора 1 тактовых импульсов, с тактовым входом делителя 9 кодов и с входом делителя 4 частоты, выход которого соединен с первым входом второго элемента И 15, выход которого соединен со счетным входом счетчика 7 импульсов, информационные входы которого соединены с выходами первого задатчика 5 кода, выходы - с первой группой входов мультиплексора 8, выходы которого соединены с первой группой входов делителя 9 кодов, вторая группа входов которого соединена с выходами второго задатчика 13 кода, выходы - с входами демуль- типлексора 10, первая группа выходов которого соединена с информационными входами регистра 11 хранения, вторая группа выходов - с первой группой выходов сумматора 6, вторая группа входов которого соединена с выходами третьего задатчика 14 кода, выходы - с второй группой входов мультиплексора 8. Первый и второй выходы блока 3 управления соединены.с вторыми выходами соответственно первого 2 и второго 15 элементов И, третий выход которого соединен с установочным входом счетчика 7 импульсов, четвертый выход - с входом управления мультиплексора 8, пятый выход - с входом запуска делителя 9 кодов, шестой выход-с входом управления демультиплек- сора 10 и седьмой - с входом записи регистра 11 хранения.

Блок 3 управления содержит первый элемент И 24, первый вход которого соединен с первым входом блока 3 управления и с входом сброса счетчика 25 импульсов, выход - с тактовыми входами первого 26 и второго 27 триггеров, инверсный выход первого из которых соединен с его информаци- онным входом, прямой выход - с информационным входом второго триггера 27, инверсный выход которого соединен с вторым выходом первого элемента И 24, прямой выход - с информационным входом третьего триггера 28, прямой выход которого соединен с первым выходом блока 3 управления, второй выход которого соединен с первым выходом второго элемента И 29, выход которого соединен со счетным входом счетчика 25 импульсов, выходы которого соединены с адресными входами постоянного запоминающего устройства

30, первый - пятый выходы которого соединены соответственно с вторым - шестым выходами блока 3 управления, седьмой выход которого соединены с тактовыми входами третьего триггера 28 и с шестым входом постоянного запоминающего устройства 30, седьмой вход которого соединен с вторым входом второго элемента И 29.

Генератор 1 тактовых импульсов по0 строен по схеме мультивибратора на инверторах ТЛЛ с кварцевой стабилизацией частоты. Первый элемент И 2, второй элемент И 15, первый 5, второй 13 и третий 14 задатчики кода построены на микросхемах

5 К155ЛАЗ. Задатчики 5, 13 и 14 кода построено так, что на их выходах после включения питания устанавливается двоичное число, причем значения напряжений для нулей и единиц этого двоичного числа соответст0 вует ТТЛ уровням.

Блок 3 управления построен на микросхемах К155ТМ7, К155ЛАЗ, К155ИЕ7 и К155РЕ:3.

Первый 4, второй 16, третий 18 делители

5 частоты, счетчик 7 импульсов, ДПКД 12 выполнены на базе счетчиков К155ЕИ7, сумматор 6 - на микросхеме АЛУ К155ИПЗ.

Мультиплексор 8 выполнен на базе микросхем К155ЛАЗ таким образом, что при

0 подаче управляющего сигнала на вход управления на выходе мультиплексора 8 появляется информация, присутствующая на одной из выходных шин, в зависимости от уровня логического сигнала на управляю5 щем входе мультиплексора 8.

Демультиплексор 10 выполнен на базе микросхем К155ЛАЗ так, что при подаче сигнала на вход управления информация, присутствующая на входе коммутатора,

0 передается на одну из выходных шин, в зависимости от уровня логического сигнала на управляющем входе демультиплексора 10. Делитель 9 кодов выполнен на базе последовательно умножителя-делителя

5 КР1802ВР2.

Регистр 11 хранения выполнен на микросхемах К155ИР13 (универсальных 8-разрядных регистрах сдвига).

Управляемый генератор 21 импульсов и

0 фазовый детектор 19 выполнены на базе микросхем ФАПЧ 564ГП, фильтр 20 нижних частот - пропорционально интегрирующая цепь, состоящая из двух резисторов и конденсатора.

5 Вычитатель 17 частот построен на известной схеме.

Умножитель работает следующим образом.

В исходном состоянии на первом выходе блока 3 установлен низкий уровень (на

структурной схеме цепи начальной установки условно не показаны), в результате чего элемент И 2 закрыт по второму входу, импульсы с выхода генератора 21 на тактовый вход делителя 12 не поступают, счетчик 25 обнулен и на выходе запоминающего устройства 30 установлен код, соответствующий нулевому адресу. По приходу второго импульса на шину 23 триггер 27 переключается в единичное состояние и сигнал низко- го уровня с инверсного выхода триггера 27 запрещает прохождение входного сигнала на тактовые входы триггеров 26 и 27. По приходу тридцать второго импульса тактовой частоты с выхода генератора 1 положи- тельный перепад сигнала на шестом выходе запоминающего устройства 30 переключает триггер 28 в единичное состояние. Этим сигналом на первом выходе блока 3 открывается по второму входу элемент И 2 и им- пульсы с выхода генератора 21 поступают на вход делителя 12, в результате чего на шине 22 появляется сигнал с частотой Рвых. Задержка после включения необходима для предотвращения появления ложной часто- ты на выходе умножителя в первый момент после включения питания.

Таким образом, после первых двух импульсов входной частоты и тридцати двух импульсов тактовой частоты в регистре 11 хранится верное число, определяющее входную частоту деления, а следовательно, верна и частота на выходе умножителя.

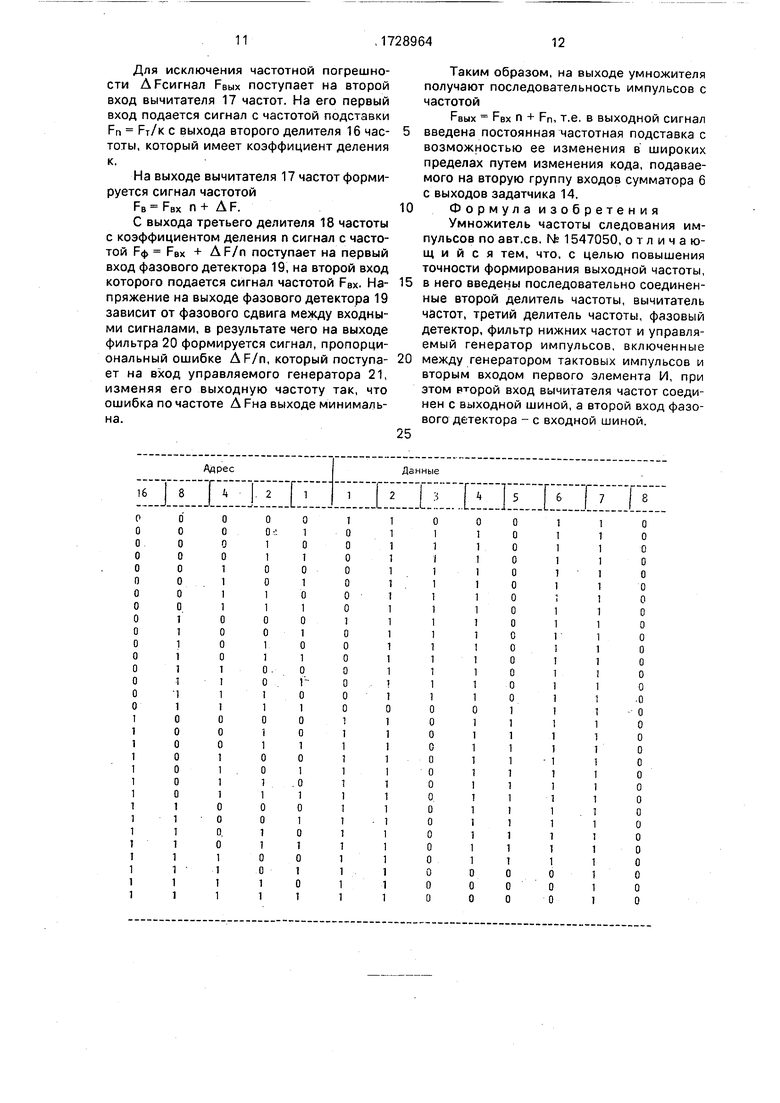

Карта программирования запоминающего устройства 30 приведена в таблице.

Рассмотрим работу умножителя после прихода i-ro импульса входной частоты на шину 23. На вход делителя 4 частоты с коэффициентом деления, равным п, поступают импульсы с выхода генератора 1. С прихо- дом первого импульса тактовой частоты после фронта i-ro импульса входной частоты на втором выходе блока 3 появляется низкий уровень, закрывающий элемент И 15. Импульсы делителя 4 частоты на счетный вход счетчика 7 не поступают, в результате чего в счетчике хранится число, равное

г вх П

где Рт-тактовая частота на выходе генератора;

FBX - входная частота на шине 23;

п - коэффициент деления делителя 4 частоты.

В этот же момент на четвертом выходе блока 3 появляется высокий уровень, что соответствует подключению мультиплексором 8 выходов счетчика 7 к первой группе входов делителя 9 кодов. Положительный перепад

сигнала на пятом выходе блока 3 запускает делитель 9 кодов, который тактируется импульсами генератора 1 и осуществляет деление двоичного кода числа 1 подаваемого с выходов за датчика 13 кода на вторую группу входов делителя 9 кодов, на число N, т.е. через четырнадцать тактов на выходе делителя 9 имеет код, равный N 1/N.

Демультиплексор 10 сигналом с шестого выхода блока 3 включен так, что выходы делителя 9 подключены к первой группе входов сумматора 6, на вторую группу входов которого подается код числа а с выходов задатчика 14, причем а Fn/FT.

Таким образом, на выходах сумматора 6 получают код, равный 1/N + а.

По приходу последнего тактового импульса первого цикла деления мультиплексор 8 переключается так, что выходы сумматора 6 оказывается подключенными к первой группе входов делителя 9. В этот же момент на третьем входе блока 3 появляется низкий уровень, по которому происходит запись кода с выхода задатчика 5 в счетчик 7. Эта предварительная запись необходима для учета в изменении периода входной частоты того времени, когда счетчик 7 остановлен. По приходу следующего тактового импульса на втором выходе блока 3 появляется высокий уровень и счетные импульсы через элемент И 15 начинают поступать на счетный вход счетчика 7, В этот же момент начинается второй цикл деления, по окончании которого на выходах делителя 9 получается код

1 1FT

М

А+а

F вх п F п FTFT

n F n

В момент прихода последнего тактового импульса второго цикла деления низкий уровень на шестом выходе блока 3 переключает демультиплексор 10 так, что выходы делителя 9 оказываются подключенными к информационным входам регистра 11, запись в который происходит по приходу следующего сигнала тактового импульса положительным перепадом сигнала на седьмом выходе блока 3. Делитель 12 делит частоту на код М. Таким образом, на выходе умножителя получают последовательность импульсов с частотой

Рвых ппг п + Fn.

В связи с ограниченной разрядностью делителя 12 и погрешностью измерения входной частоты выходной сигнал умножителя формируется с ошибкой ДР

Рвых FBX П + Fn + A F.

Для исключения частотной погрешности ДРсигнал Рвых поступает на второй вход вычитателя 17 частот. На его первый вход подается сигнал с частотой подставки Fn FT/K с выхода второго делителя 16 частоты, который имеет коэффициент деления к.

На выходе вычитателя 17 частот формируется сигнал частотой

Рв FBX п + А Р.

С выхода третьего делителя 18 частоты с коэффициентом деления п сигнал с частотой Рф Рвх + AF/n поступает на первый вход фазового детектора 19, на второй вход которого подается сигнал частотой FBx. Напряжение на выходе фазового детектора 19 зависит от фазового сдвига между входными сигналами, в результате чего на выходе фильтра 20 формируется сигнал, пропорциональный ошибке AF/n, который поступает на вход управляемого генератора 21, изменяя его выходную частоту так, что ошибка по частоте А Рна выходе минимальна.

0

5

0

5

Таким образом, на выходе умножителя получают последовательность импульсов с частотой

Рвых Рвх п + рп, т.е. в выходной сигнал введена постоянная частотная подставка с возможностью ее изменения в широких пределах путем изменения кода, подаваемого на вторую группу входов сумматора 6 с выходов задатчика 14.

Ф о р м у л а и з о б р е т е н и я

Умножитель частоты следования импульсов по авт.св. № 1547050, отличающийся тем, что, с целью повышения точности формирования выходной частоты, в него введены последовательно соединенные второй делитель частоты, вычитатель частот, третий делитель частоты, фазовый детектор, фильтр нижних частот и управляемый генератор импульсов, включенные между генератором тактовых импульсов и вторым входом первого элемента И, при этом второй вход вычитателя частот соединен с выходной шиной, а второй вход фазового детектора - с входной шиной.

Фиг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1547050A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

| Умножитель частоты | 1988 |

|

SU1626315A1 |

| ЦИФРОВАЯ РЕГУЛИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2108659C1 |

| Цифровой умножитель частоты следования периодических импульсов | 1987 |

|

SU1554124A1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2004 |

|

RU2269866C2 |

| Умножитель частоты следования импульсов | 1987 |

|

SU1636983A1 |

Изобретение относится к импульсной технике и может быть использовано в автоматике и вычислительной технике. Цель изобретения - повышение точности формирования выходной частоты за счет использования кольца фазовой автоматической подстройки частоты. Устройство содержит генератор 1 тактовых импульсов, первый элемент И 2, делитель 12 частоты с переменным коэффициентом деления, выходную шину 22, регистр 11 хранения, блок 3 управления, входную шину, первый, второй и третий задатчики 5, 13 и 14 кода, счетчик 7 импульсов, делитель 9 кодов, мультиплексор 8, демультиплексор 10, сумматор 6, второй элемент И 15, первый и второй делители 4 и 16 частоты, вычитатель 17 частот, третий делитель 18 частоты, фазовый детектор 19, фильтр 20 нижних частот и управляемый генератор 21 импульсов, 2 ил. ы t

| Устройство задержки импульсов | 1985 |

|

SU1279057A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1547050A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-23—Публикация

1989-11-24—Подача