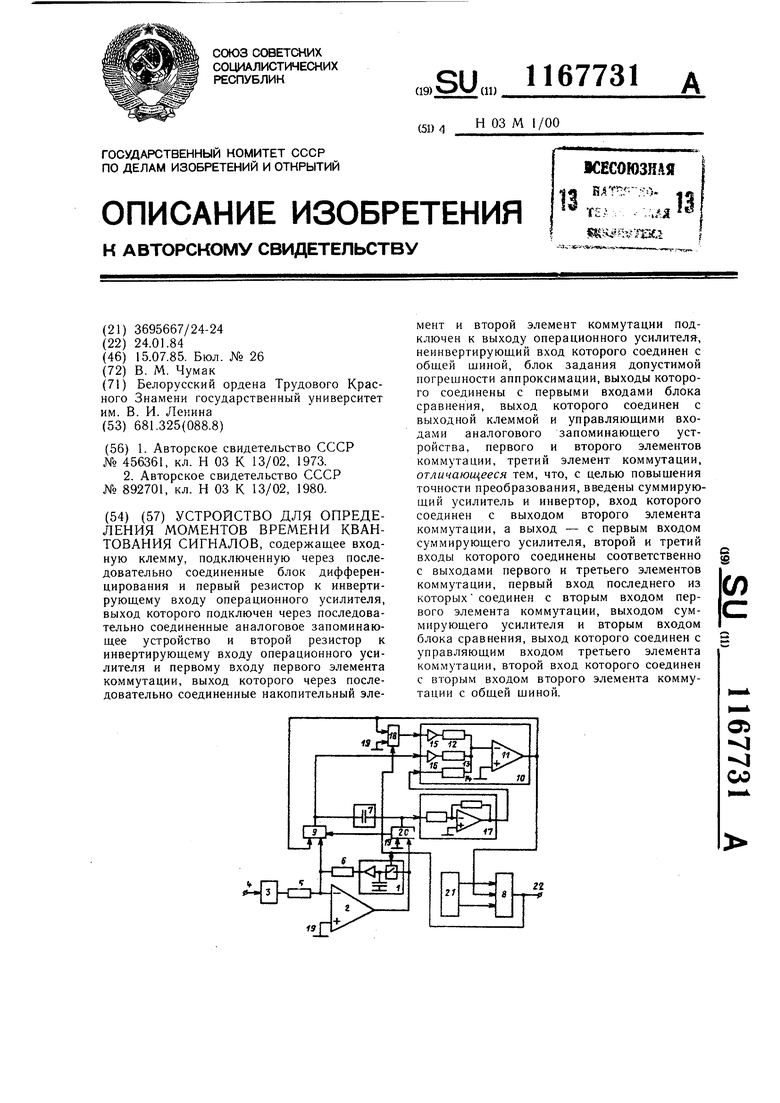

Изобретение относится к информационной измерительной технике и может быть использовано для адаптивной временной дискретизации аналоговых сигналов при заданной точности их восстановления. Известно устройство для определения моментов времени квантования сигналов, содержащее последовательно соединенные входную клемму, блок дифференцирования, блок запоминания и вычитания, интегратор, блок сравнения, второй вход которого соединен с блоком задания допустимой погрещности аппроксимации, причем выход блока сравнения соединен с выходной клеммой и управляющими входами интегратора и блока запоминания и вычитания 1. К недостаткам этого устройства еледует отнести низкую точность и малый частотный диапазон обрабатываемых аналоговых сигналов, что обусловлено наличием аддитивной погрешности, вносимой интеграторомНаиболее близким к предлагаемому по технической сущности является устройство для определения моментов времени квантования сигналов, содержащее входную клемму, подключенную через последовательно соединенные блок дифференцирования и первый резистор к первому входу первого ключевого элемента и инвертирующему входу операционного усилителя, выход которого соединен с первым входом блока сравнения и входом аналогового запоминающего устройства, выход которого через второй резистор подключен к первому входу первого ключевого элемента, выход которого через последовательно соединенные накопительный элемент, параллельно которому подключен второй ключевой элемент и третий ключевой элемент, соединен с выходом операционного усилителя, неинвертирующий вход которого через третий резистор соединен с общей щиной, блок задания допустимой погрешности аппроксимации, выходы которого соединены с вторыми входами блока сравнения, выход которого соединен с выходной клеммой и управляющими входами первого и третьего ключевых элементов, а инверсный выход - с управляющими входами второго ключевого элемента аналогового запоминающего устройства 2. Недостаток устройства - также низкая точность, обусловленная неполным устра нением аддитивной погрешности,, вносимой интегратором. Известные способы устранения этой погрешности с помощью МДМ усилителей мало приемлемы, так как интегратор в данном типе устройства работает не периодически в ключевом режиме разряд - интегрирование. Использование же суммирующей точки (инвертирующего входа операционного усилителя) приводит к возникновению большой погрешности из-за несимметричности выбросов (токов переключения) ключевых элементов. имеющихся по входу МДМ усилителя (модуляторов), которые накапливаются на накопительном элементе во время интегрирования. Кроме того, наличие аддитивной погрешности блока сравнения также приводит к неточному определению длины адаптивного временного интервала. Цель изобретения - повышение точности преобразования. Указанная цель достигается тем, что в устройство для определения моментов времени квантования сигналов, содержащем входную клемму, подключенную через последовательно соединенные блок дифференцирования и первый резистор к инвертирующему входу операционного усилителя, выход которого подключен через последовательно соединенные аналоговое запоминающее устройство и второй резистор к инвертирующему входу операционного усилителя и первому входу первого элемента коммутации, выход которого через последовательно соединенные накопительный элемент и второй элемент коммутации подключен к выходу операционного усилителя. неинвертирующии вход которого соединен с общей шиной, блок задания допустимой погрешности аппроксимации, выходы которого соединены с первыми входами блока сравнения, выход которого соединен с выходной клеммой и управляющими входами аналогового запоминающего устройства, первого и второго элементов коммутации, третий элемент коммутации, введены суммирующий усилитель и инвертор, вход которого соединен с выходом второго элемента коммутации, а выход - с первым входом суммирующего усилителя, второй и третий входы которого соединены соответственно с выходами первого и третьего элементов коммутации, первый вход последнего из которых соединен с вторым входом первого элемента коммутации, выходом суммирующего усилителя и вторым входом блока сравнения, выход которого соединен с управляющим входом третьего элемента коммутации, второй вход которого соединен с вторым входом второго элемента коммутации и общей шиной. Структурная электрическая схема устройства приведена на чертеже. Устройство содержит аналоговые запоминающее устройство 1, вход которого соединен с выходом операционного усилителя 2, блок 3 дифференцирования. вход которого соединен с входной клеммой 4, а выход через резистор 5 с инвертирующим входом операционного усилителя 2 и через резистор 6 - с выходом аналогового запоминающего устройства 1, накопительный элемент 7, блок 8 сравнения, первый вход элемента 9 коммутации соединен с инвертирующим входом операционного усилителя 2, второй вход элемента 9 соединен с выходом суммирующего усилителя 10, состоящего из соединенного с выходом операционного усилителя 11, первый вход которого соединен с первыми выводами резисторов 12-14, вторые выводы резисторов 12 и 13 соединены с выходами повторителей 15 и 16, второй вывод резистора 14 соединен с выходом инвертора 17, вход повторителя 15 соединен с выходом элемента 18 коммутации, первый вход которого соединен с вторым входом элемента 9 и выходом суммирующего усилителя 10, второй вход - с общей щиной 19. Первый вход элемента 20 коммутации, выход которого соединен с входом инвертора 17 и через накопительный элемент 7 - с выходом элемента 9 и входом повторителя 16, соединен с выходом операционного усилителя 2, неинвертирующий вход которого соединен с общей щиной, второй вход аналогового запоминающего устройства 1 соединен с выходом блока 8, первые входы которого соединены с выходами блока 21 задания допустимой погрещности аппроксимации, второй вход - с выходом суммирующего усилителя 10, а выход - с выходной клеммой 22 и управляющими входами элементов 9, 18 и 20, второй вход последнего соединен с общей шиной. Устройство работает в режиме отслеживания производной входной сигнала и разряда накопительного элемента и режиме определения длины адаптивного временного интервала. При работе устройства в первом режиме в течение времени At аналоговое запоминающее устройство 1 включается на отслеживание, замыкая обратную отрицательную связь операционного усилителя 2. Значение, которое фиксируется аналоговым запоминающим устройством 1, по окончании отслеживания в момент времени ti равно Uc (1 +1) Uo- (tc) + Ug) -Ud, (1) где A- параметр блока 3; x(ti) - значение первой производной аналогового сигнала x(t), поступающего на входную клемму 4. Значение х (f формируется блоком 3, имеющим аддитивную погрещность по выходу Ug; напряжение смещения по входу one рационного усилителя 2; Ua - аддитивная погрещность на выходе аналогового запоминающего устройства 1. RiMBj-сопротивление соответственно резисторов 5 и 6. Одновременно с процедурой отслеживания производной входного аналогового сигнала x(t) осуществляется операция разряда накопительного элемента 7. При этом под действием управляющего сигнала с выхода блока 8 элемент 9 отключает накопительный элемент 7 от инвертирующего входа операционного усилителя 2 и подключает его к выходу суммирующего усилителя 10, который построен на базе операционного усилителя 11 и содержит резисторы 12-14 и повторители 15 и 16, предназначенные для повыщения входного сопротивления. Подключение одного входа накопительного элемента 7 к выходу суммирующего усилителя 10 через элемент 9, а другого его входа через инвертор 17 к первому входу суммирующего усилителя 10 приводит к разряду накопительного элемента 7. Требуемая точность разряда обеспечивается наличием глубокой отрицательной связи, которая осуществляется через последовательно соединенные элемент 9, повторитель 16 и резистор 13. На данном этапе элемент 18 подключает общую шину19 к входу суммирующего усилителя 10, а второй элемент 20 соединяет вход инвертора 17 и второй вход накопительного элемента 7 с общей щиной 19. По окончании разряда накопительного элемента 7 значение дифференциального напряжения на нем (разность потенциалов между обкладками конденсатора) равно Up(2+)Uc«o- ,-Uc«,-и«,, (2) r UcMrUci f Ц ыГ-н а п7яжени7 смещения Р, выходу соответственно повторителей 15, 16 и инвертора 17; напряжение смещения по входу операционного усилителя 11; R - сопротивление резисторов 13 и 14; Rs - сопротивление резистора 12. Применение инвертирующих схем, таких как инвертор 17 и суммирующий усилитель 10, позволяет не учитывать синфазиую ощибку, так как она для указанных схем отсутствует. Повторители 15 и 16 могут быть выполнены на базе полевого транзистора. На этапе определения адаптивного временного интервала, аналоговое запоминающее устройство 1 включается на хранение значения Uc, а цепь обратной отрицательной связи суммирующего усилителя 10 замыкается через элемент 18, при этом элементы 9 и 20 включают накопительный элемент 7 в цепь обратной отрицательной связи операционного усилителя 2. Дифференциальное напряжение на накопнтельном элементе 7 равно: и„ ир+-1 j«dT CJ) где JH - ток, протекающий через накопительный элемент 7; т - текущее время адаптивного временного интервала; С| - емкость накопительного элемента 7. JoK JH, протекающий через накопительный элемент 7 с высокой степенью точности равен сумме токов i и 2, протекающих через резисторы 5 и 6, т. е. Jn s

:,,+-з,,,;,е-з,,

с учетом выражения (1) имеем 1и -4(x(tc-х), т. е. дифференциальное напряжение на накопительном элементе 7 с учетом соотношений (3) и (4) равно

U,Ug-(x/ti -T-x/T).

Суммирующий усилитель 10 в сочетании с инвертором 17 осуществляет дифференциальный съем значения UH и его усиление так, что напряжение на выходе суммирующего усилителя 10 в момент времени € равно

5() 1 RT-crf / i )1:-Х(Я -f UP+ + ( l)Uo,,-UcH,- f UcM, или с учетом выражения (2) имеем

5(t) (ti)€-3t(),

значение коэффициента К равно

Кз

А К RjCr

И

Текущее значение погрешности аппроксимации (t) сравнивается блоком 8 со значением tc ±k ц. (например, с использованием сдвоенного компаратора напряжения), где .- заданная погрешность аппроксимации, определяемая блоком допустимой погрешности аппроксимации. При превышении значения li(C)l величины поиск очередного адаптивного временного интервала заканчивается.

Для уменьшения погрешности, возникающей при сравнении величины е. и

блоком 8, желательно иметь достаточно большое значение коэффициента К. Причем во сколько раз увеличивается значение К, во столько же раз уменьшается погрешность, возникающая при сравнении.

Анализ выражения для коэффициента К показывает следующие пути для его увеличения.

Увеличение значения величины А ограничивается верхней граничной частотой ujg

обрабатываемых сигналов, его максимальным значением АН и максимально допустимой величиной выходного напряжения UM блока 3. При заданных (, АЛ и Уд значение А определяется однозначно. Для идеального дифференциатора при Aju. U«ti. имеем А К. f.2 , где R j и С - параметры дифференциатора.

Уменьшая значение R iC i при заданном А, необходимо выполнить условие Ri;Ci- RaCa что приводит к увеличению восприимчивости устройства к частота.м выше граничной частоты входного сигнала, поэтому следует выполнять условие ., что при , приводит к требованию К.1 (для прототипа -R 1).

Желаемый эффект можно получить лишь

путем увеличения значения - Максимально допустимое при этом значение К определяется максимально допустимым рабочим напряжением операционных усилителей

2, 11, элементов 9, 18, 20 и блоков 8 сравнения, входящих в состав устройства, и равно К .

Таким образом, аддитивная погрешность, вносимая блоком сравнения 8, может быть уменьшена в К раз, где .

В предлагаемом изобретении погрешности, вносимые операционными усилителями, не влияют на точностные характеристики устройства, что позволяет не менее, чем в два раза повысить его точность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1978 |

|

SU781838A1 |

| Устройство для определения моментов времени квантования сигналов | 1980 |

|

SU892701A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1691895A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Интегратор | 1984 |

|

SU1161963A1 |

| Аналоговое запоминающееуСТРОйСТВО | 1979 |

|

SU801104A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868839A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU842971A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОМЕНТОВ ВРЕМЕНИ КВАНТОВАНИЯ СИГНАЛОВ, содержащее входную клемму, подключенную через последовательно соединенные блок дифференцирования и первый резистор к инвертирующему входу операционного усилителя, выход которого подключен через последовательно соединенные аналоговое запоминающее устройство и второй резистор к инвертирующему входу операционного усилителя и первому входу первого элемента коммутации, выход которого через последовательно соединенные накопительный элемент и второй элемент коммутации подключен к выходу операционного усилителя, неинвертирующий вход которого соединен с общей шиной, блок задания допустимой погрешности аппроксимации, выходы которого соединены с первыми входами блока сравнения, выход которого соединен с выходной клеммой и управляющими входами аналогового запоминающего устройства, первого и второго элементов коммутации, третий элемент коммутации, отличающееся тем, что, с целью повыщения точности преобразования, введены суммирующий усилитель и инвертор, вход которого соединен с выходом второго элемента коммутации, а выход - с первым входом суммирующего усилителя, второй и третий i входы которого соединены соответственно с выходами первого и третьего элементов (Л коммутации, первый вход последнего из которых соединен с вторым входом первого элемента коммутации, выходом суммирующего усилителя и вторым входом блока сравнения, выход которого соединен с управляющим входом третьего элемента коммутации, второй вход которого соединен с вторым входом второго элемента коммутации с общей щиной. 05 | со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения моментов времени квантования сигнала | 1973 |

|

SU456361A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения моментов времени квантования сигналов | 1980 |

|

SU892701A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-15—Публикация

1984-01-24—Подача