(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОМЕНТОВ ВРЕМЕНИ КВАНТОВАНИЯ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения моментов времени квантования сигналов | 1984 |

|

SU1167731A1 |

| Устройство для определения моментов времени квантования сигналов | 1979 |

|

SU782146A1 |

| Устройство для определения моментов времени квантования сигнала | 1975 |

|

SU714642A1 |

| Устройство для определения моментов времени квантования сигнала | 1982 |

|

SU1069154A2 |

| Адаптивный временной дискретизатор | 1977 |

|

SU680015A1 |

| Устройство для определения моментов времени квантования сигнала | 1973 |

|

SU456361A1 |

| Устройство для определения моментов времени квантования сигнала | 1980 |

|

SU855991A2 |

| Устройство для определения моментов времени квантования | 1976 |

|

SU588625A1 |

| Устройство для определения моментов времени квантования сигнала | 1986 |

|

SU1325695A2 |

| Адаптивное телеметрическое устройство | 1979 |

|

SU769595A1 |

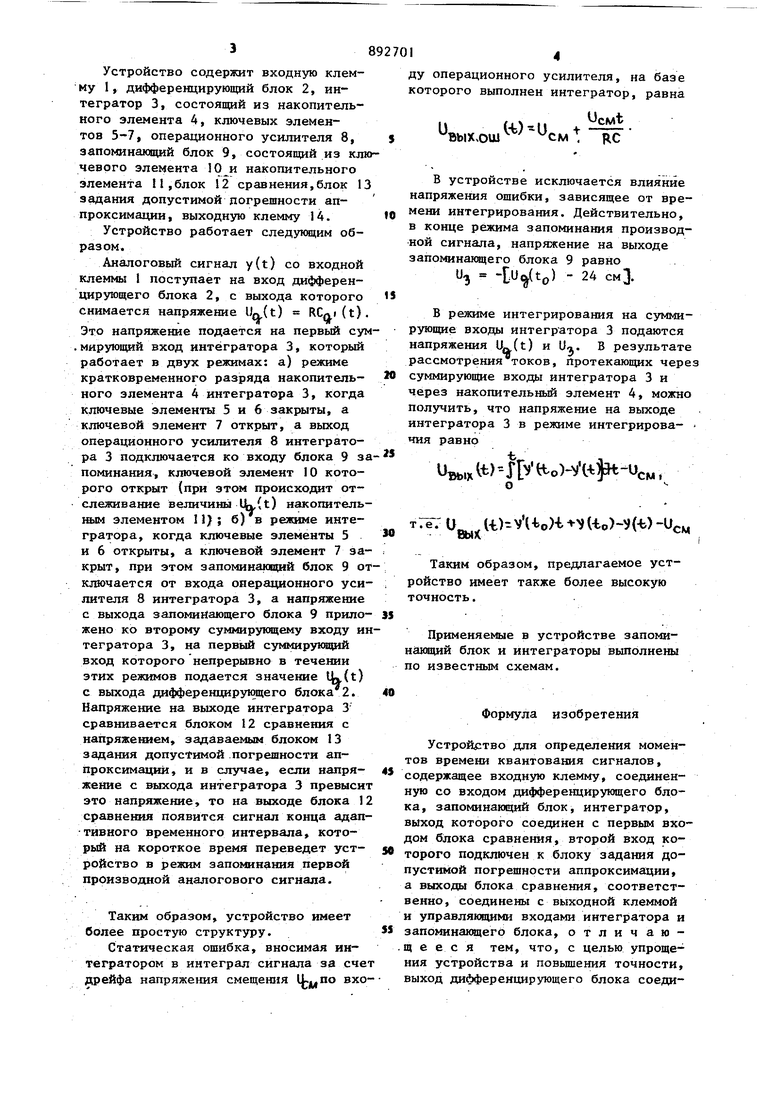

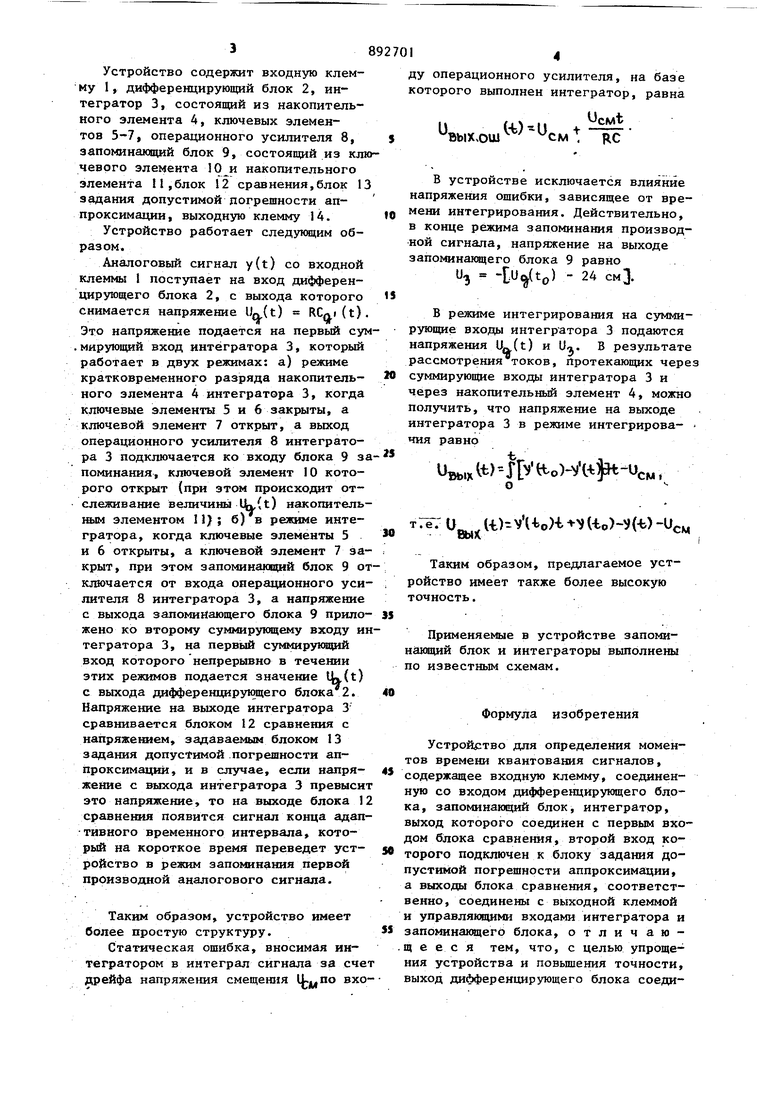

Изобретение относится к измеритель ной информационной технике и может быть использовано для дискретизации аналоговых сигналов при требуемой точности восстановления. Известно устройство дл1Я определения моментов времени квантования сигналов , содержащее последовательно соединенные входную клемму, дифференцирующий блок, запоминающе-вычитающий блок, интегратор, блок сравнения, вто рой вход которого соединен с блоком задания допустимой погрешности аппроксимации, а выход блока сравнения соединен с выходной клеммой и управля ющими входами интегратора и запоминанчце-вычитающего блока 1. Недостатком известного устройства является избыточность схемного построения и низкая точность, обусловленная последовательным соединением запоминающе-вычитающего блока и интегратора, которые вносят свои погрршности. Цель изобретения - упрощение устройства и повышение точности. Указанная цель достигается тек, что в устройстве, содержащем входную клемму, соединенную со входом дифференцирующего блока, запоминающий блок, интегратор, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к блоку задания допустимой погрешности аппроксимации, а выходы блока сравнения, соответственно, соединены с выходной клеммой и управляющими входами интегратора и запоминающего блока, выход дифференцирующего блока соединен с первым суммирующим входом интегратора, выход которого подключен ко входу запоминающего блока, выход которого соединен со вторым суммирующим входом интегратора. На чертеже представлена структурная электрическая схема предлагаемого устройства. 3 Устройство содержит входную клемму 1, дифференцирующий блок 2, интегратор 3, состоящий из накопительного элемента 4, ключевых элементов 5-7, операционного усилителя 8, запоминающий блок 9, состоящий из клю чевого элемента накопительного элемента И,блок 12 сравнения,блок 13 задания допустимой погрешности аппроксимации, выходную клемму 14. Устройство работает следующим образом. Аналоговый сигнал y(t) со входной клеммы I поступает на вход дифференцирующего блока 2, с выхода которого снимается напряжение lW(t) RCrti(t). Это напряжение подается на первый сум ,мирующий вход интегратора 3, который работает в двух режимах: а) режиме кратковременного разряда накопительного элемента 4 интегратора 3, когда ключевые элементы 5 и 6 закрыты, а ключевой элемент 7 открыт, а выход операционного усилителя 8 интеграто3 подключается ко входу блока 9 за поминания, ключевой элемент 10 которого открыт {при этом происходит отслеживание величины lU,(t) накопительгадм элементом П); б) в режиме интегратора, когда ключевые элементы 5 и 6 открыты, а ключевой элемент 7 закрыт, при этом запоминающий блок 9 от ключается от входа операционного усилителя 8 интегратора 3, а напряжение с выхода запоминающего блока 9 приложено ко второму суммирующему входу ин тегратора 3, на первый суммирующий вход которого непрерывно в течении этих режимов подается значение t|.(t) с выхода дифференциругмдего блока 2. Напряжение на выходе интегратора 3 сравнивается блоком 12 сравнения с напряжением, задаваемым блоком 13 задания допустимой погрешности аппроксимации, и в случае, если напряжение с выхода интегратора 3 превысит это напряжение V то на выходе блока 1 сравнения появится сигнал конца адаптивного временного интервала, который на короткое время переведет устройство в режим запоминания первой производной аналогового сигнала. Таким образом, устройство имеет более простую структуру. Статическая ошибка, вносимая интегратором в интеграл сигнала за сче дрейфа напряжения смещения вхо 1 ду операционного усилителя, на базе которого выполнен интегратор, равна вь,х. в устройстве исключается влияние напряжения ошибки, зависящее от времени интегрирования. Действительно, в конце режима запоминания Производной сигнала, напряжение на выходе запоминакяцего блока 9 равно -tUi(to) 24 см. В режиме интегрирования на суммирующие входы интегратора 3 подаются напряжения f(t) и U-j. В результате рассмотрения токов, протекающих через суммирующие входы интегратора 3 и через накопительный элемент 4, можно получить, что напряжение на выходе интегратора 3 в режиме интегрирова- чия равно .х -№ H.o)-V0t -Uc xju. Ч .4air-ii ц, а)-vHoH vHo)-v{-b) -UCM Таким образом, предлагаемое устройство имеет также более высокую точность. Применяемые в устройстве запоминающий блок и интеграторы выполнены по известным схемам. Формула изобретения Устройство для определения моментов времени квантования сигналов, содержащее входную клемму, соединенную со входом дифференцирующего блока, запоминающий блок, интегратор, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к блоку задания допустимой погрешности аппроксимации, а выходы блока сравнения, соответственно, соединены с выходной клеммой и управляющими входами интегратора и запоминакяцего блока, отличающ е ее я тем, что, с целью упрощения устройства и повьш1ения точности, выход дифференцирующего блока соединен с первым суммирующим входом интегратора, выход которого подключен ко входу запоминающего блока, выход которого соединен со вторым суммирующим входом интегратора. О

892701 ,t .

Источникиинформации, принятые во внимание при экспертизе

Авторы

Даты

1981-12-23—Публикация

1980-04-02—Подача