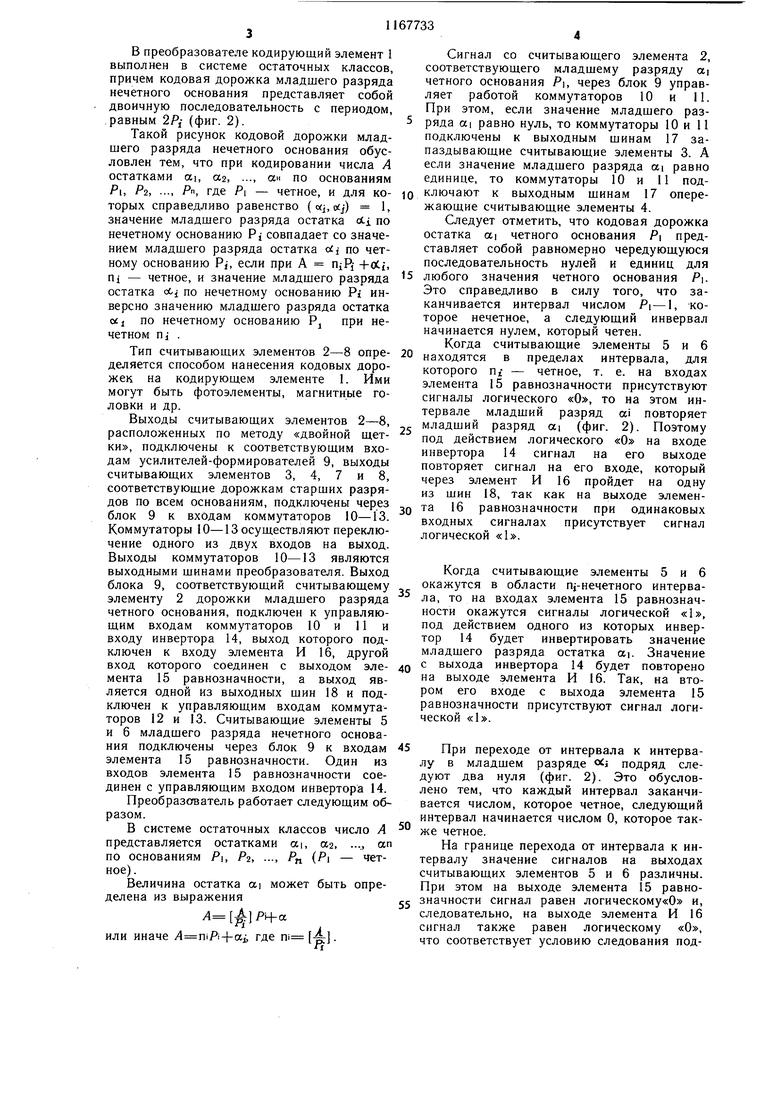

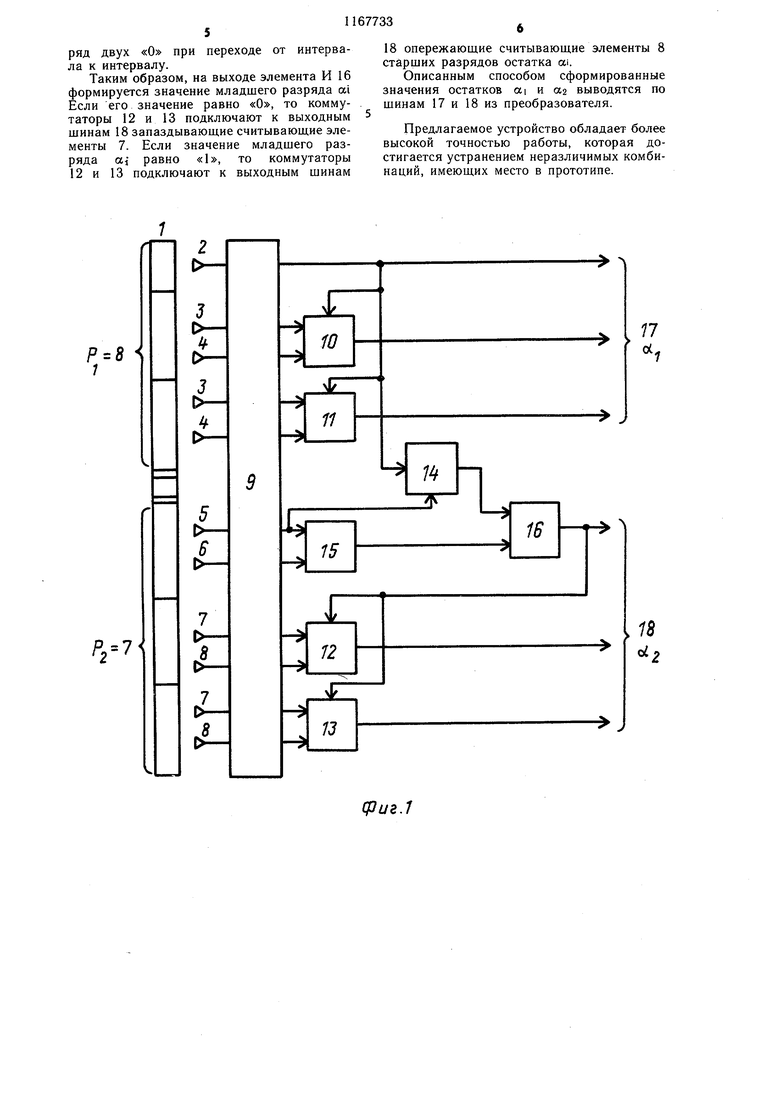

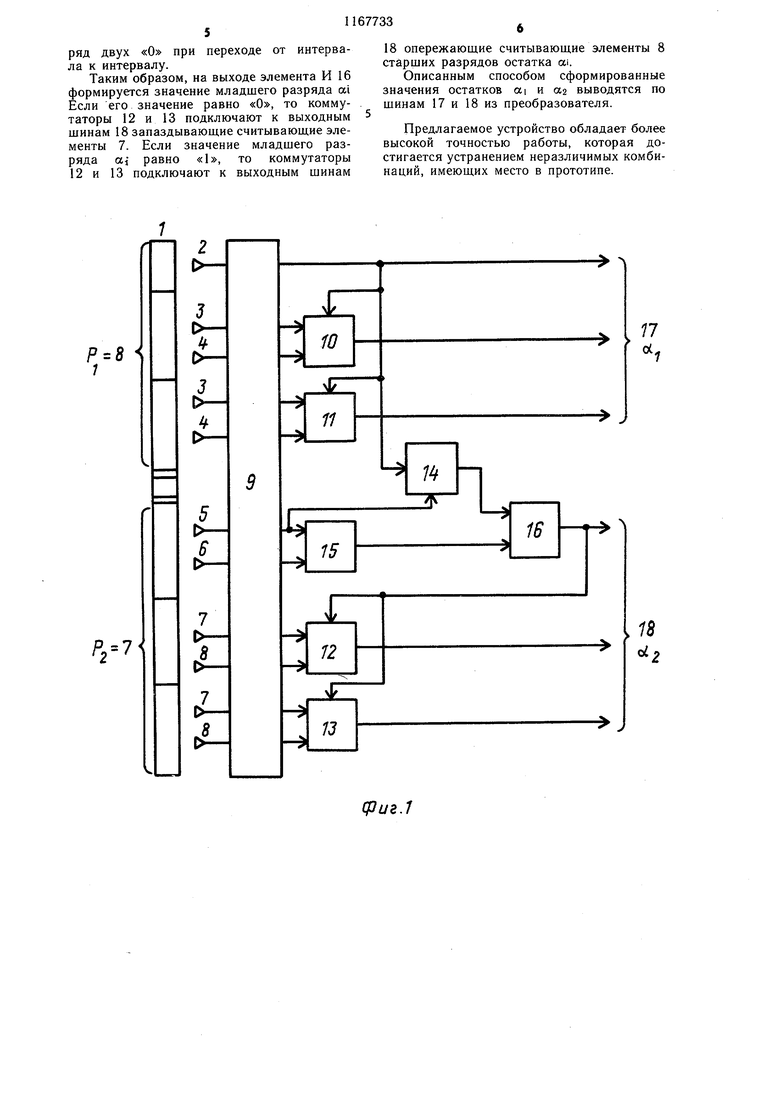

Изобретение относится к вычислительной технике и может быть использовано для преобразования угла поворота вала в цифровой код системы остаточных классов (СОК), для ввода информации о перемещениях в цифровые вычислительные устройства, в устройства автоматического управления и радиотехнические устройства. Известен преобразователь угла поворота вала в код, содержащий источник света, щелевую диафрагму, считывающие элементы кодовую щкалу, выполненную в системе остаточных классов и установленную неподвижно, щелевая диаграмма выполнена с прозрачными окнами, расположенными для каждого основания на расстоянии, равном величине этого основания и закреплена на валу кодирующего диска 1. Однако этот преобразователь обладает недостаточной точностью, обусловленной неоднозначностью считывания при переходе от одного считывающего элемента к другому. Это проявляется наиболее сильно, если считывающие элементы смещены относительно своего требуемого расположения. Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому является преобразователь угла по-2 ворота вала в код, содержащий кодирующий элемент с дорожками, выполненными в системе остаточных классов, считывающие элементы, расположенные по методу «двоиной щетки, выходы считывающих элементов соединены с соответствующими входамиз блока усилителей-формирователей, выход младщего разряда четного основания которого является одноименным выходом преобразователя, а выходы старших разрядов четного основания соединены с информационными входами первого и второго3 коммутаторов, управляющие входы которых соединены с выходом младщего разряда четного основания блока усилителей-формирователей, а выходы являются выходами старших разрядов нечетного основания преобразователя, выходы старших разрядов4 нечетного основания блока усилителейформирователей соединены с информационными входами третьего и четвертого коммутаторов, управляющие входы которых соединены с выходом элемента И, первый вход которого соединен с выходом инвертора, выходы третьего, четвертого коммутаторов и выход элемента И являются выходами разрядов нечетного основания преобразователя 2. Недостатком этого преобразователя является низкая точность, обусловленная тем, что при переходе от одного периода остатков нечетного основания к другому периоду существуют два повторения нулевого значения. При этом возможно множество различных ситуаций сигналов, комбинации которых могут быть неразличными, что ведет к ощибкам в преобразовании информации. Цель изобретения - повышение точности преобразователя угла поворота вала в код. Поставленная цель достигается тем, что в преобразователь угла поворота вала и одГ содержащий кодирующий элемент с дорожками, выполненными в системе остаточных классов, считывающие элементы, расположенные по методу «двойной щетки выходы считывающих элементов соединень с .соответствующими входами блока усилителей-формирователей, выход младшего разряда четного основания которого является одноименным выходом преобразователя, а выходы старщих разрядов четного основания соединены с информационными входами первого и второго коммутаторов, управляющие входы которых соединены с выходами младшего разряда четного основания блока усилителей-формирователей, а выходы являются выходами старших разрядов четного основания преобразователя, выходы старших разрядов нечетного основания блока усилителей-формирователей соединены с информационными входами третьего и четвертого коммутаторов, управляющие выходы которых соединены с выходами элемента И, первый вход которого соединен с выходом инвертора, выходы третьего, четвертого коммутаторов и выход элемента И являются выходами разрядов нечетного основания преобразователя, введен элемент равнозначности, а дорожка младшего разряда нечетного основания кодирующего элемента выполнена в виде двоичной последовательности прозрачных и непрозрачных участков с периодом 2 Pi, где Р - величина кванта дорожки нечетного основания, выходы младшего разряда нечетного основания блока усилителей - формирователей соединены с входами элемента равнозначности, выход которого соединен с вторым входом элемента И, первый вход инвертора соединен с выходом младшего разряда четного основания блока усилителей - формирователей, а второй вход - с первым выходом младшего разряда нечетного основания блока усилителейформирователей, На фиг. 1 представлена структурная схема преобразователя; на фиг. 2 - фрагмент кодирующего элемента дорожек младшего разряда четного и нечетного основания; на фиг. 3 - возможные варианты расположения считывающих элемен дорожках младших разрядов четного и нечетного оснований, Преобразователь содержит кодирующий элемент 1, считывающие элементы 2-8, блок 9 усилителей-формирователей, коммутаторы 10-13, инвертор 14, элемент 15 равнозначности, элемент И 16, а также шины 17 и 18 выхода преобразователя разрядов четного и нечетного оснований соответственно. В преобразователе кодирующий элемент I выполнен в системе остаточных классов, причем кодовая дорожка младшего разряда нечетного основания представляет собой двоичную последовательность с периодом, равным 2Pi (фиг. 2). Такой рисунок кодовой дорожки младшего разряда нечетного основания обусловлен тем, что при кодировании числа А остатками oci, 0,2, ..., а по основаниям PI, Ра, .... Р, где Р| - четное, и для которых справедливо равенство («i,otj) 1, значение младшего разряда остатка oCi по нечетному основанию Pj совпадает со значением младщего разряда остатка ctj по четному основанию Pi, если при А niPf +(Хь ni - четное, и значение младшего разряда остатка л по нечетному основанию Pi инверсно значению младшего разряда остатка ocj по нечетному основанию Pj при нечетном ni . „ „ Тип считывающих элементов 2-8 определяется способом нанесения кодовых дррожек на кодирующем элементе 1. Ими могут быть фотоэлементы, магнитные головки и др. Выходы считывающих элементов 2-8, расположенных по методу «двойной щетки, подключены к соответствующим входам усилителей-формирователей 9, выходы считывающих элементов 3, 4, 7 и 8, соответствующие дорожкам старщих разрядов по всем основаниям, подключены через блок 9 к входам коммутаторов 10-13. Коммутаторы 10-13 осуществляют переключение одного из двух входов на выход. Выходы коммутаторов 10-13 являются выходными шинами преобразователя. Выход блока 9, соответствующий считывающему элементу 2 дорожки младщего разряда четного основания, подключен к управляющим входам коммутаторов 10 и 11 и входу инвертора 14, выход которого подключен к входу элемента И 16, другой вход которого соединен с выходом элемента 15 равнозначности, а выход является одной из выходных шин 18 и подключен к управляющим входам коммутаторов 12 и 13. Считывающие элементы 5 и 6 младшего разряда нечетного основания подключены через блок 9 к входам элемента 15 равнозначности. Один из входов элемента 15 равнозначности соединен с управляющим входом инвертора 14. Преобразователь работает следующим образом. В системе остаточных классов число А представляется остатками cxi, 0,2, ...., «п по основаниям Р, Ра, ..., РП (Pi - тетное). Величина остатка ai может быть определена из выражения или иначе niPi+ai где П1 4: Сигнал со считывающего элемента 2, соответствующего младщему разряду «i четного основания Р, через блок 9 управляет работой коммутаторов 10 и 11. При этом, если значение младщего разряда ai равно нуль, то коммутаторы 10 и 11 подключены к выходным шинам 17 запаздывающие считывающие элементы 3. А если значение младшего разряда «i равно единице, то коммутаторы 10 и II под«лючают к выходным шинам 17 опережающие считывающие элементы 4. Следует отметить, что кодовая дорожка остатка ai четного основания Pi представляет собой равномерно чередующуюся последовательность нулей и единиц для любого значения четного основания Рь Это справедливо в силу того, что заканчивается интервал числом PI-1, которое нечетное, а следующий инвервал начинается нулем, который четен. Когда считывающие элементы 5 и 6 находятся в пределах интервала, для которого П - четное, т. е. на входах элемента 15 равнозначности присутствуют сигналы логического «О, то на этом интервале младший разряд ai повторяет младщий разряд а, (фиг. 2) Поэтому под действием логического «О на входе инвертора 14 сигнал на его выходе повторяет сигнал на его входе, который через элемент И 16 пройдет на одну „з щин 18, так как на выходе элемен а 16 равнозначности при одинаковых входных сигналах присутствует сигнал логической «1. Когда считывающие элементы 5 и 6 окажутся в области ni-нечетного интервала, то на входах элемента 15 равнозначности окажутся сигналы логической «1, под действием одного из которых инвертор 14 будет инвертировать значение младщего разряда остатка «ь Значение выхода инвертора М будет повторено на выходе элемента И 16. Так, на втором его входе с выхода элемента 15 равнозначности присутствуют сигнал логической «1. При переходе от интервала к интервалу в младщем разряде oi подряд следуют два нуля (фиг. 2). Это обусловлено тем, что каждый интервал заканчивается числом, которое четное, следующий интервал начинается числом О, которое так же четное, На границе перехода от интервала к интервалу значение сигналов на выходах считывающих элементов 5 и 6 различны. При этом на выходе элемента 15 равнозначности сигнал равен логическому«0 и, следовательно, на выходе элемента И 16 сигнал также равен логическому «О, что соответствует условию следования подряд двух «о при переходе от интервала к интервалу.

Таким образом, на выходе элемента И 16 формируется значение младшего разряда ai Если его значение равно «О, то коммутаторы 12 и 13 подключают к выходным шинам 18 запаздываюшие считываюшие элементы 7. Если значение младшего разряда «t равно «1, то коммутаторы 12 и 13 подключают к выходным шинам

18 опережающие считывающие элементы 8 старших разрядов остатка ai.

Описанным способом сформированные значения остатков ai и «2 выводятся по шинам 17 и 18 из преобразователя.

Предлагаемое устройство обладает более высокой точностью работы, которая достигается устранением неразличимых комбинаций, имеющих место в прототипе.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОТОЭЛЕКТРИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЕ—КОД | 1973 |

|

SU384118A1 |

| ВСЕСОЮЗНАЯ ПАТЕйТно-Т1Х11г;Е:йдя | 1973 |

|

SU374647A1 |

| Преобразователь перемещения в код | 1986 |

|

SU1403371A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ — КОД | 1971 |

|

SU429446A1 |

| Преобразователь угол-код | 1973 |

|

SU444232A1 |

| Преобразователь угол-код | 1973 |

|

SU517035A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Многоотсчетный фотоэлектрический преобразователь перемещения в код | 1980 |

|

SU997065A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312735A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1259485A1 |

ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД, содержащий кодирующий элемент с дорожками, выполненный в системе остаточных классов, считывающие элементы, расположенные по методу «двойной щетки, выходы считывающих элементов соединены с соответствующими входами, блока усилителейформирователей, выход младщего разряда четного основания которого является одноименным выходом преобразователя, а выходы старщих разрядов четного основания соединены с информационными входами первого и второго коммутаторов, управляющие входы которых соединены с выходом младщего разряда четного основания блока усилителей-формирователей, а выходы являются выходами старщих разрядов четного основания преобразователя, выходы старших разрядов нечетного основания блока усилителей-формирователей соединены с информационными входами третьего и четвертого коммутаторов, управляющие выходы которых соединены с выходом элемента И, первый вход которого соединен с выходом инвертора, выходы третьего, четвертого коммутаторов и выход элемента И являются выходами разрядов нечетного основания преобразователя, отличающийся тем, что, с целью повыщения точности преобразователя, в него введен элемент равнозначности, а дорожка младщего разряда нечетного основания кодирующего элемента выполнена в виде двоичной последовательности прозрачных и неi прозрачных участков с периодом Pi - величина кванта дорожки не(Л четного основания, выходы младщего разряда нечетного основания блока усилителейформирователей соединены со входами элемента равнозначности, выход которого соединен со вторым входом элемента И, первый вход инвертора соединен с выходом младшего разряда четного основания блока, усилителей-формирователей, а второй вход с первым выходом младщего разряда нечетного основания блока усилителей-форО5 мирователей. оо

Р 8

(puz.1

Младший разряд четного основания

Считывающие головки

1 2 3 5В7 8 д W1112imf57S17

Четное

Нечетное

сриг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU312289A1 | |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ФОТОЭЛЕКТРИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЕ—КОД | 0 |

|

SU384118A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-07-15—Публикация

1984-01-13—Подача