(А С

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Генератор двоичных чисел | 1984 |

|

SU1201827A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

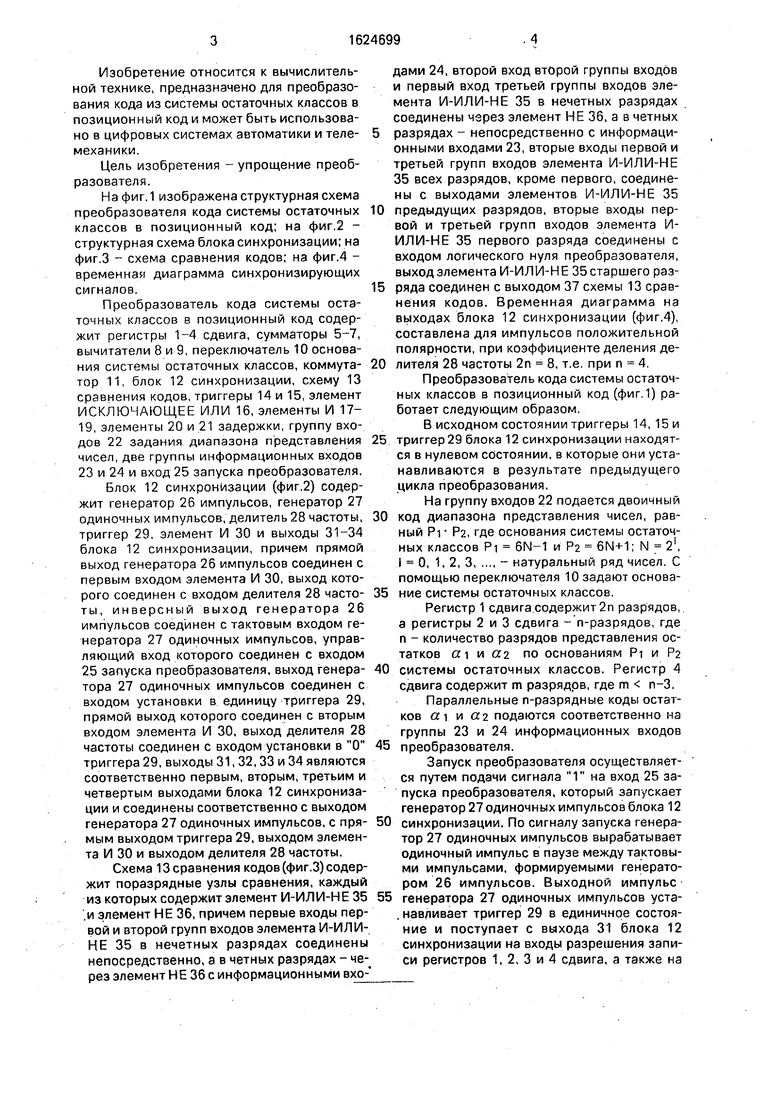

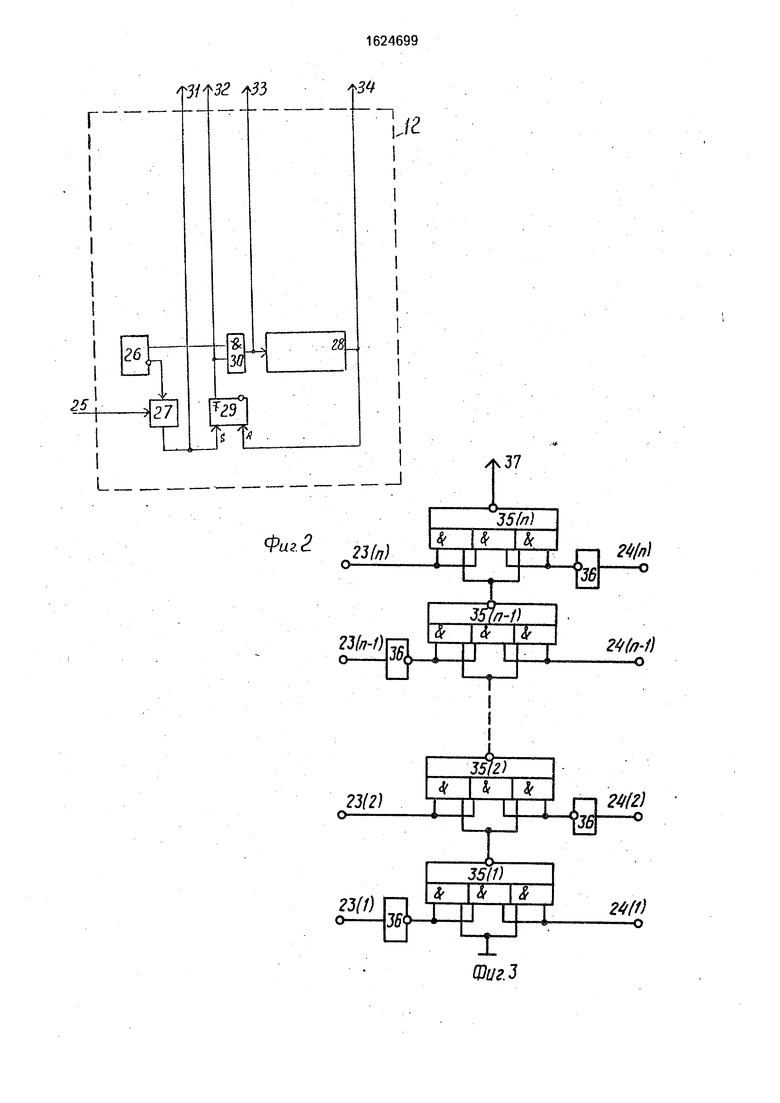

Изобретение относится к вычислительной технике и предназначено для преобразования кода из системы остаточных классов в позиционный код. Цель изобретения состоит в упрощении преобразователя. Преобразователь кода системы остаточных классов в позиционный код содержит четыре регистра 1-4 сдвига, два вычитателя 8 и 9, три сумматора 5-7, переключатель Ю основания системы остаточных классов, коммутатор 11, блок 12 синхронизации, схему 13 сравнения кодов, два триггера 14 и 15, три элемента И 17-19, элемент ИСКЛЮЧАЮЩЕЕ ИПИ 16, два элемента 20 и 21 задержки. 4 ил.

гз гз гз

Фиг.1

О

Ю

U

Os

Ю Ю

г гь lit

Изобретение относится к вычислительной технике, предназначено для преобразования кода из системы остаточных классов в позиционный код и может быть использовано в цифровых системах автоматики и телемеханики.

Цель изобретения - упрощение преобразователя.

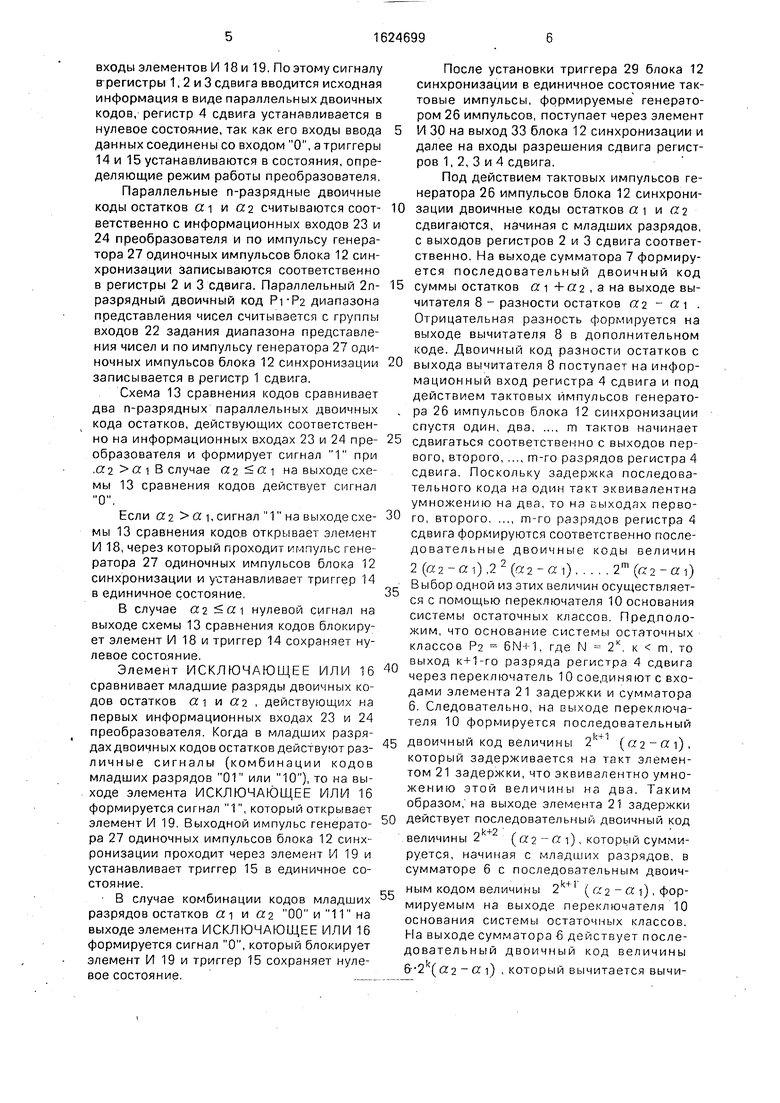

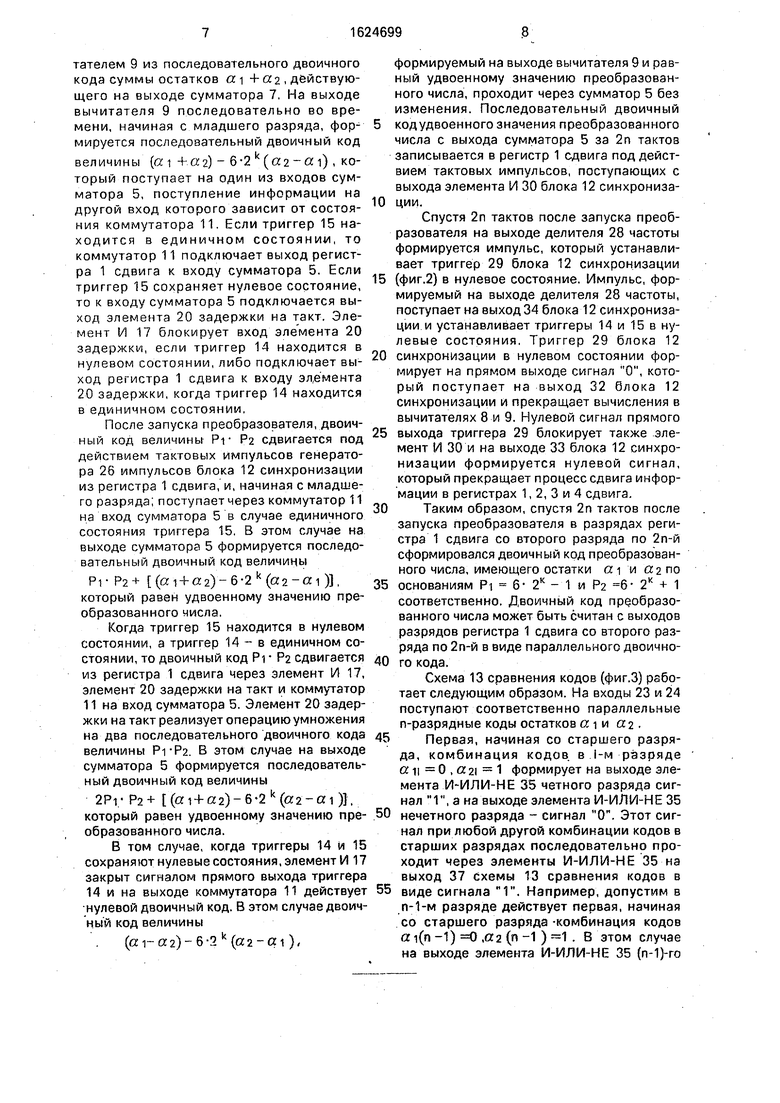

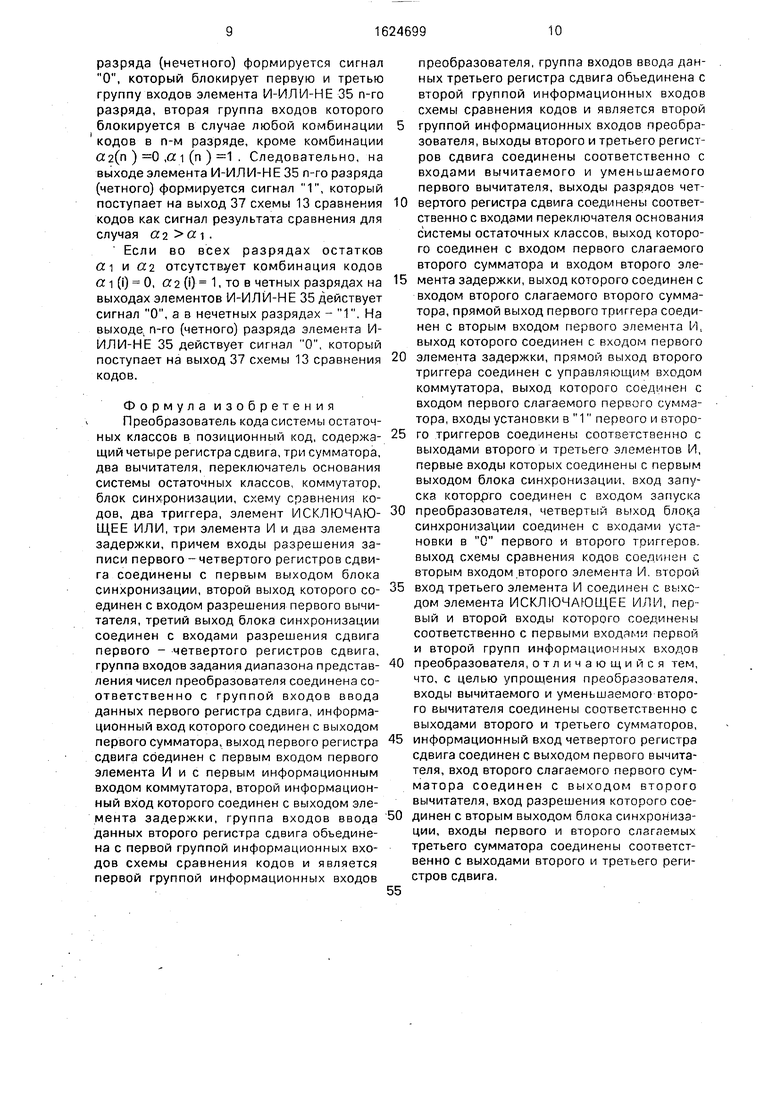

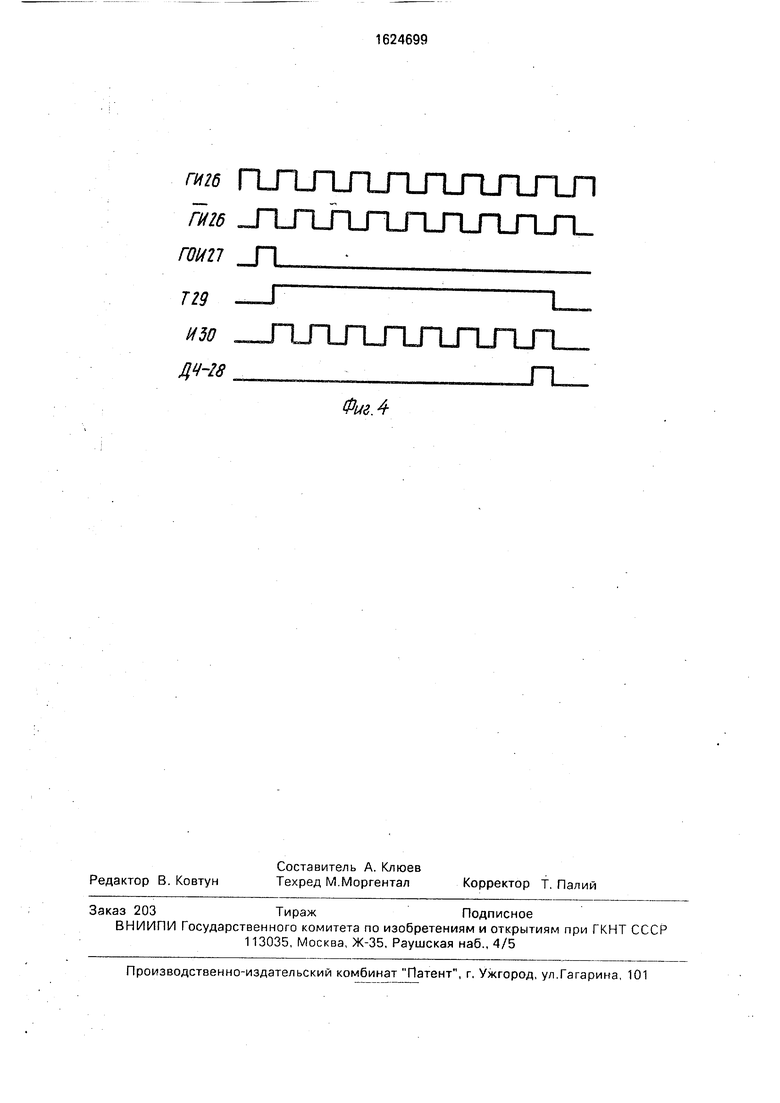

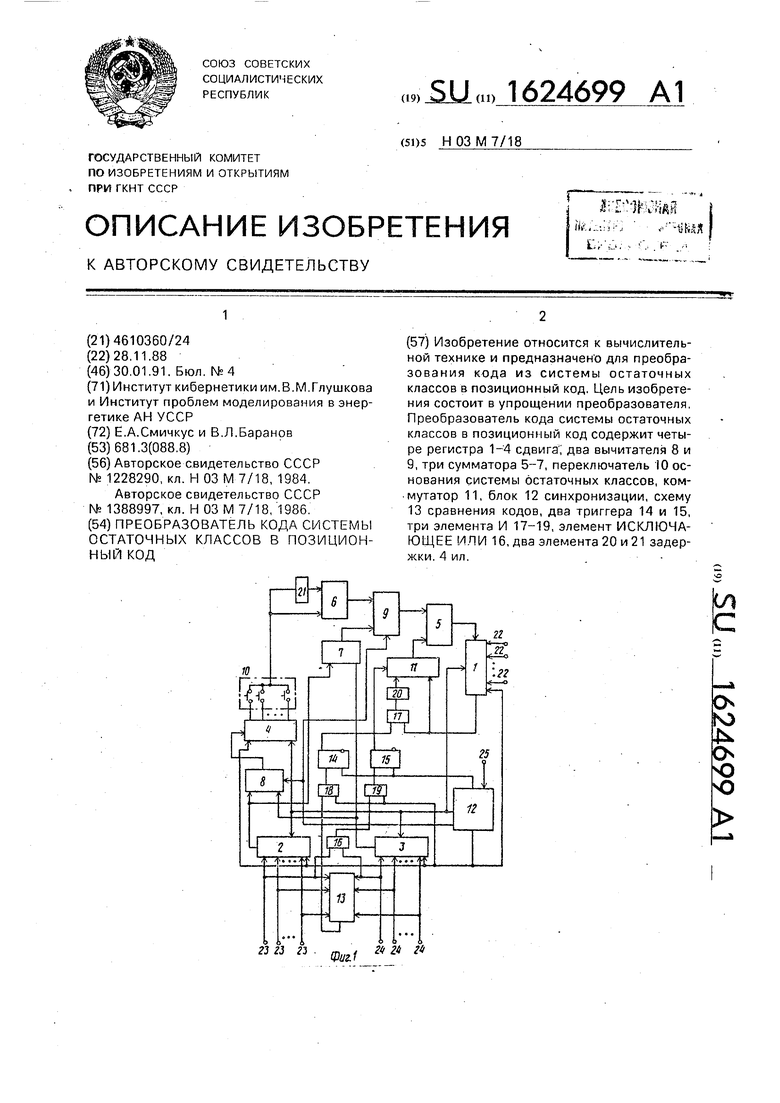

На фиг. 1 изображена структурная схема преобразователя кода системы остаточных классов в позиционный код; на фиг.2 - структурная схема блока синхронизации; на фиг.З - схема сравнения кодов; на фиг.4 - временная диаграмма синхронизирующих сигналов.

Преобразователь кода системы остаточных классов в позиционный код содержит регистры 1-4 сдвига, сумматоры 5-7, вычитатели 8 и 9, переключатель 10 основания системы остаточных классов, коммутатор 11, блок 12 синхронизации, схему 13 сравнения кодов, триггеры 14 и 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, элементы И 17- 19, элементы 20 и 21 задержки, группу входов 22 задания диапазона представления чисел, две группы информационных входов 23 и 24 и вход 25 запуска преобразователя. Блок 12 синхронизации (фиг.2) содержит генератор 26 импульсов, генератор 27 одиночных импульсов, делитель 28 частоты, триггер 29, элемент И 30 и выходы 31-34 блока 12 синхронизации, причем прямой выход генератора 26 импульсов соединен с первым входом элемента И 30, выход которого соединен с входом делителя 28 частоты, инверсный выход генератора 26 импульсов соединен с тактовым входом генератора 27 одиночных импульсов, управляющий вход которого соединен с входом 25 запуска преобразователя, выход генератора 27 одиночных импульсов соединен с входом установки в единицу триггера 29, прямой выход которого соединен с вторым входом элемента И 30, выход делителя 28 частоты соединен с входом установки в О триггера 29, выходы 31, 32,33 и 34 являются соответственно первым, вторым, третьим и четвертым выходами блока 12 синхронизации и соединены соответственно с выходом генератора 27 одиночных импульсов, с прямым выходом триггера 29, выходом элемента 1/1 30 и выходом делителя 28 частоты.

Схема 13 сравнения кодов (фиг.З) содержит поразрядные узлы сравнения, каждый из которых содержит элемент И-ИЛИ-НЕ 35 .и элемент НЕ 36, причем первые входы первой и второй групп входов элемента И-ИЛИ- НЕ 35 в нечетных разрядах соединены непосредственно, а в четных разрядах - через элемент НЕ 36 с информационными входами 24, второй вход второй группы входов и первый вход третьей группы входов элемента И-ИЛИ-НЕ 35 в нечетных разрядах соединены чэрез элемент НЕ 36, а в четных

разрядах - непосредственно с информационными входами 23, вторые входы первой и третьей групп входов элемента И-ИЛИ-НЕ 35 всех разрядов, кроме первого, соединены с выходами элементов И-ИЛИ-НЕ 35

предыдущих разрядов, вторые входы первой и третьей групп входов элемента И- ИЛИ-НЕ 35 первого разряда соединены с входом логического нуля преобразователя, выход элемента И-ИЛИ-НЕ 35 старшего разряда соединен с выходом 37 схемы 13 сравнения кодов. Временная диаграмма на выходах блока 12 синхронизации (фиг.4), составлена для импульсов положительной полярности, при коэффициенте деления делителя 28 частоты 2п 8, т.е при п 4

Преобразователь кода системы остаточных классов в позиционный код (фиг 1) работает следующим образом.

В исходном состоянии триггеры 14, 15 и

триггер 29 блока 12 синхронизации находятся в нулевом состоянии, в которые они устанавливаются в результате предыдущего цикла преобразования.

На группу входов 22 подается двоичный

код диапазона представления чисел, равный Pi Р2, где основания системы остаточных классов Pi 6N-1 и Ра 6N+1; N 21, 1 0, 1, 2, 3, .... - натуральный ряд чисел. С помощью переключателя 10 задают основание системы остаточных классов.

Регистр 1 сдвига содержит 2п разрядов, а регистры 2 и 3 сдвига - n-разрядов, где п - количество разрядов представления остатков а 1 и «2 по основаниям Pi и Р2

системы остаточных классов. Регистр 4 сдвига содержит m разрядов, где гл п-3. Параллельные n-разрядные коды остатков а и О.1 подаются соответственно на группы 23 и 24 информационных входов

преобразователя.

Запуск преобразователя осуществляется путем подачи сигнала 1 на вход 25 запуска преобразователя, который запускает генератор 27 одиночных импульсов блока 12

синхронизации. По сигналу запуска генератор 27 одиночных импульсов вырабатывает одиночный импульс в паузе между тактовыми импульсами, формируемыми генератором 26 импульсов. Выходной импульс

5 генератора 27 одиночных импульсов уста- . навливает триггер 29 в единичное состояние и поступает с выхода 31 блока 12 синхронизации на входы разрешения записи регистров 1, 2, 3 и 4 сдвига, а также на

входы элементов И 18 и 19. По этому сигналу в-регистры 1, 2 и 3 сдвига вводится исходная информация в виде параллельных двоичных кодов, регистр 4 сдвига устанавливается в нулевое состояние, так как его входы ввода данных соединены со входом О, а триггеры 14 и 15 устанавливаются в состояния, определяющие режим работы преобразователя.

Параллельные n-разрядные двоичные коды остатков a-i и а-i считываются соответственно с информационных входов 23 и 24 преобразователя и по импульсу генератора 27 одиночных импульсов блока 12 синхронизации записываются соответственно в регистры 2 и 3 сдвига. Параллельный 2п- разрядный двоичный код диапазона представления чисел считывается с группы входов 22 задания диапазона представления чисел и по импульсу генератора 27 одиночных импульсов блока 12 синхронизации записывается в регистр 1 сдвига.

Схема 13 сравнения кодов сравнивает два n-разрядных параллельных двоичных кода остатков, действующих соответственно на информационных входах 23 и 24 преобразователя и формирует сигнал 1 при .а.1 а 1 В случае на выходе схемы 13 сравнения кодов действует сигнал О.

Если а 2 о. 1, сигнал 1 на выходе схемы 13 сравнения кодов открывает элемент И 18, через который проходит импульс генератора 27 одиночных импульсов блока 12 синхронизации и устанавливает триггер 14 в единичное состояние.

В случае сс.2 а нулевой сигнал на выходе схемы 13 сравнения кодов блокирует элемент И 18 и триггер 14 сохраняет нулевое состояние.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16 сравнивает младшие разряды двоичных кодов остатков сп и а2 , действующих на первых информационных входах 23 и 24 преобразователя. Когда в младших разрядах двоичных кодов остатков действуют различные сигналы (комбинации кодов младших разрядов 01 или 10), то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 формируется сигнал 1, который открывает элемент И 19. Выходной импульс генератора 27 одиночных импульсов блока 12 синхронизации проходит через элемент И 19 и устанавливает триггер 15 в единичное состояние.

В случае комбинации кодов младших разрядов остатков ai и аг 00 и 11 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 формируется сигнал О, который блокирует элемент И 19 и триггер 15 сохраняет нулевое состояние.

После установки триггера 29 блока 12 синхронизации в единичное состояние тактовые импульсы, формируемые генератором 26 импульсов, поступает через элемент 5 И 30 на выход 33 блока 12 синхронизации и далее на входы разрешения сдвига регистров 1, 2, 3 и 4 сдвига.

Под действием тактовых импульсов генератора 26 импульсов блока 12 синхрони10 зации двоичные коды остатков а и ai сдвигаются, начиная с младших разрядов, с выходов регистров 2 и 3 сдвига соответственно. На выходе сумматора 7 формируется последовательный двоичный код

5 суммы остатков а 1 Л-ai , а на выходе вы- читателя 8 - разности остатков ai - а . Отрицательная разность формируется на выходе вычитателя 8 в дополнительном коде. Двоичный код разности остатков с

0 выхода вычитагеля 8 поступав1 на информационный вход регистра 4 сдвига и под действием тактовых импульсов генерато- , ра 26 импульсов блока 12 синхронизации спустя один, два m тактов начинает

5 сдвигаться соответственно с выходов первого, второго, ..., т-го разрядов регистра 4 сдвига. Поскольку задержка последовательного кода на один такт эквивалентна умножению на два, то на выходах перво0 го, второго, ..., т-го разрядов регистра 4 сдвига формируются соответственно после- довательные двоичные коды величин

2 («2-сп) ,2 2 (0:2-a i)2m(«2-ai)

j- Выбор одной из этих величин осуществляется с помощью переключателя 10 основания системы остаточных классов. Предположим, что основание системы остаточных классов Р2 6N+1, где N - 2К. к т, то выход к+1-го разряда регистра 4 сдвига через переключатель 10 соединяют с входами элемента 21 задержки и сумматора 6. Следовательно, на выходе переключателя 10 формируется последовательный

5 двоичный код величины 2ст (), который задерживается на такт элементом 21 задержки, что эквивалентно умножению этой величины на два. Таким образом, на выходе элемента 21 задержки

0 действует последовательный двоичный код

величины 2 (#2 - о. i), который суммируется, начиная с младших разрядов, в сумматоре 6 с последовательным двоич0

ным кодом величины 2 + ( ai - а ) , формируемым на выходе переключателя 10 основания системы остаточных классов. На выходе сумматора -6 действует последовательный двоичный код величины

&-2k(a2 О. т) , который вычитается вы ч итателем 9 из последовательного двоичного кода суммы остатков а- +«2 , действующего на выходе сумматора 7. На выходе вычитателя 9 последовательно во времени, начиная с младшего разряда, формируется последовательный двоичный код

величины («1 Ч- а2) - 6-2k(a2-o:i), который поступает на один из входов сумматора 5, поступление информации на другой вход которого зависит от состояния коммутатора 11. Если триггер 15 находится в единичном состояние, то коммутатор 11 подключает выход регистра 1 сдвига к входу сумматора 5. Если триггер 15 сохраняет нулевое состояние, то к входу сумматора 5 подключается выход элемента 20 задержки на такт. Элемент И 17 блокирует вход элемента 20 задержки, если триггер 14 находится в нулевом состоянии, либо подключает выход регистра 1 сдвига к входу элемента 20 задержки, когда триггер 14 находится в единичном состоянии.

После запуска преобразователя, двоичный код величины PV Р2 сдвигается под действием тактовых импульсов генератора 26 импульсов блока 12 синхронизации из регистра 1 сдвига, и, начиная с младшего разряда, поступает через коммутатор 11 на вход сумматора 5 в случае единичного состояния триггера 15. В этом случае на выходе сумматора 5 формируется последовательный двоичный код величины

Pr P2+ (ai + a2)-6-2k(a2-ai), который равен удвоенному значению преобразованного числа.

Когда триггер 15 находится в нулевом состоянии, а триггер 14 - в единичном состоянии, то двоичный код Pi Р2 сдвигается из регистра 1 сдвига через элемент И 17, элемент 20 задержки на такт и коммутатор 11 на вход сумматора 5. Элемент 20 задержки на такт реализует операцию умножения на два последовательного двоичного кода величины РгРа. В этом случае на выходе сумматора 5 формируется последовательный двоичный код величины

2Pr P2+ (ai + a2)-6-2k(a2-ai)3, который равен удвоенному значению преобразованного числа.

В том случае, когда триггеры 14 и 15 сохраняют нулевые состояния, элемент И 17 закрыт сигналом прямого выхода триггера 14 и на выходе коммутатора 11 действует нулевой двоичный код. В этом случае двоичный код величины

(ai-ct2)-6-2k(a2-ai)

формируемый на выходе вычитателя 9 и равный удвоенному значению преобразованного числа, проходит через сумматор 5 без изменения. Последовательный двоичный

код удвоенного значения преобразованного числа с выхода сумматора 5 за 2п тактов записывается в регистр 1 сдвига под действием тактовых импульсов, поступающих с выхода элемента И 30 блока 12 синхронизации.

Спустя 2п тактов после запуска преобразователя на выходе делителя 28 частоты формируется импульс, который устанавливает триггер 29 блока 12 синхронизации

(фиг.2) в нулевое состояние. Импульс, формируемый на выходе делителя 28 частоты, поступает на выход 34 блока 12 синхронизации и устанавливает триггеры 14 и 15 в нулевые состояния, Триггер 29 блока 12

синхронизации в нулевом состоянии формирует на прямом выходе сигнал О, который поступает на выход 32 блока 12 синхронизации и прекращает вычисления в вычитателях 8 и 9. Нулевой сигнал прямого

выхода триггера 29 блокирует также элемент И 30 и на выходе 33 блока 12 синхронизации формируется нулевой сигнал, который прекращает процесс сдвига информации в регистрах 1, 2, 3 и 4 сдвига.

Таким образом, спустя 2п тактов после запуска преобразователя в разрядах регистра 1 сдвига со второго разряда по 2п-й сформировался двоичный код преобразованного числа, имеющего остатки и a 2 по

основаниям PI 6- 2К - 1 и Р2 6- 2К + 1 соответственно. Двоичный код преобразованного числа может быть считан с выходов разрядов регистра 1 сдвига со второго разряда по 2п-й в виде параллельного двоичного кода.

Схема 13 сравнения кодов (фиг.З) работает следующим образом. На входы 23 и 24 поступают соответственно параллельные n-разрядные коды остатков а 1 и a.i,

5 Первая, начиная со старшего разряда, комбинация кодов в i-м разряде а 11 0 , а 2 1 формирует на выходе элемента И-ИЛИ-НЕ 35 четного разряда сигнал 1, а на выходе элемента И-ИЛИ-НЕ 35

0 нечетного разряда - сигнал О. Этот сигнал при любой другой комбинации кодов в старших разрядах последовательно проходит через элементы И-ИЛИ-НЕ 35 на выход 37 схемы 13 сравнения кодов в

5 виде сигнала 1. Например, допустим в п-1-м разряде действует первая, начиная со старшего разряда -комбинация кодов a i(n -1) 0 ,«2 (п -1 ) 1 . В этом случае на выходе элемента И-ИЛИ-НЕ 35 (п-1)-го

разряда (нечетного) формируется сигнал О, который блокирует первую и третью группу входов элемента И-ИЛИ-НЕ 35 п-го разряда, вторая группа входов которого блокируется в случае любой комбинации кодов в n-м разряде, кроме комбинации й2(п ) 0 ,а 1 (п ) 1 . Следовательно, на выходе элемента И-ИЛИ-НЕ 35 n-го разряда (четного) формируется сигнал 1, который поступает на выход 37 схемы 13 сравнения кодов как сигнал результата сравнения для случая a z сс 1 .

Если во всех разрядах остатков а. и а.2 отсутствует комбинация кодов а 1 () 0, а2 (i) 1, то в четных разрядах на выходах элементов И-ИЛИ-НЕ 35 действует сигнал О, а в нечетных разрядах - 1. На выходе n-го (четного) разряда элемента И- ИЛИ-НЕ 35 действует сигнал О, который поступает на выход 37 схемы 13 сравнения кодов.

Формула изобретения Преобразователь кода системы остаточных классов в позиционный код, содержа- щий четыре регистра сдвига, три сумматора, два вычитателя, переключатель основания системы остаточных классов коммутатор, блок синхронизации, схему сравнения кодов, два триггера, элемент ИСКЛЮЧАЮ- ЩЕЕ ИЛИ, три элемента И и два элемента задержки, причем входы разрешения записи первого - четвертого регистров сдвига соединены с первым выходом блока синхронизации, второй выход которого со- единен с входом разрешения первого вычитателя, третий выход блока синхронизации соединен с входами разрешения сдвига первого - четвертого регистров сдвига, группа входов задания диапазона представ- ления чисел преобразователя соединена со- ответственно с группой входов ввода данных первого регистра сдвига, информационный вход которого соединен с выходом первого сумматора, выход первого регистра сдвига соединен с первым входом первого элемента И и с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом элемента задержки, группа входов ввода данных второго регистра сдвига объединена с первой группой информационных входов схемы сравнения кодов и является первой группой информационных входов

преобразователя, группа входов ввода данных третьего регистра сдвига обьединена с второй группой информационных входов схемы сравнения кодов и является второй группой информационных входов преобразователя, выходы второго и третьего регистров сдвига соединены соответственно с входами вычитаемого и уменьшаемого первого вычитателя, выходы разрядов четвертого регистра сдвига соединены соответственно с входами переключателя основания системы остаточных классов, выход которого соединен с входом первого слагаемого второго сумматора и входом второго элемента задержки,выход которого соединен с входом второго слагаемого второго сумматора, прямой выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с входом первого элемента задержки, прямой выход второго триггера соединен с управляющим входом коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, входы установки в 1 переого и второго триггеров соединены соответственно с выходами второго и третьего элементов И, первые входы которых соединены с первым выходом блока синхронизации, вход запуска которрго соединен с входом запуска преобразователя, четвертый выход блок.а синхронизации соединен с входами установки в О первого и второго триггеров выход схемы сравнения кодов соединен с вторым входом второго элемента И второй вход третьего элемента И соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пер вый и второй входы которого соединены соответственно с первыми входами первой и второй групп информационных входов преобразователя, отличающийся тем, что, с целью упрощения преобразователя, входы вычитаемого и уменьшаемого второго вычитателя соединены соответственно с выходами второго и третьего сумматоров, информационный вход четвертого регистра сдвига соединен с выходом первого вычитателя, вход второго слагаемого первого сумматора соединен с выходом второго вычитателя, вход разрешения которого соединен с вторым выходом блока синхронизации, входы первого и второго слагаемых третьего сумматора соединены соответственно с выходами второго и третьего регистров сдвига.

23(f)

Фиг.З

ги2б

7m

ГОЙЯ П

тгд -I

изо „JlJlJTJTJTJn

Фиг А

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-30—Публикация

1988-11-28—Подача