Изобретение относится к вычислительной технике и может быть использовано для определения эксплуатационно-технических характеристик сложных систем, в частности для определения объема контролируемых параметров при ограничениях различного уровня.

Цель изобретения - повышение точности устройства за счет дополнительного контроля в остаточном интервале времени.

При превышении суммой длительностей контроля определенного заданного ограничения последнее значение длительности контроля вычитается и регистрация этого параметра контроля запрещается. Затем продолжаются дальнейший перебор и суммирование длительностей контроля с целью заполнения отрезка ЛТос пара.метров, у которого ТК СДТк1 ст.

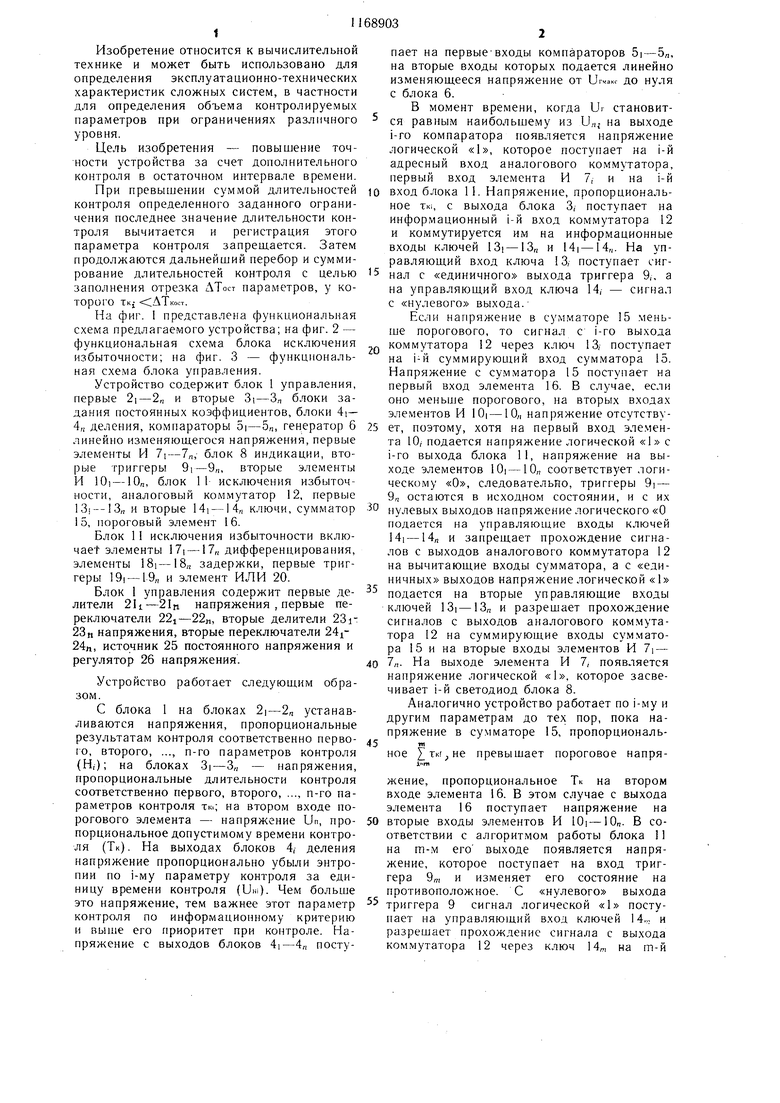

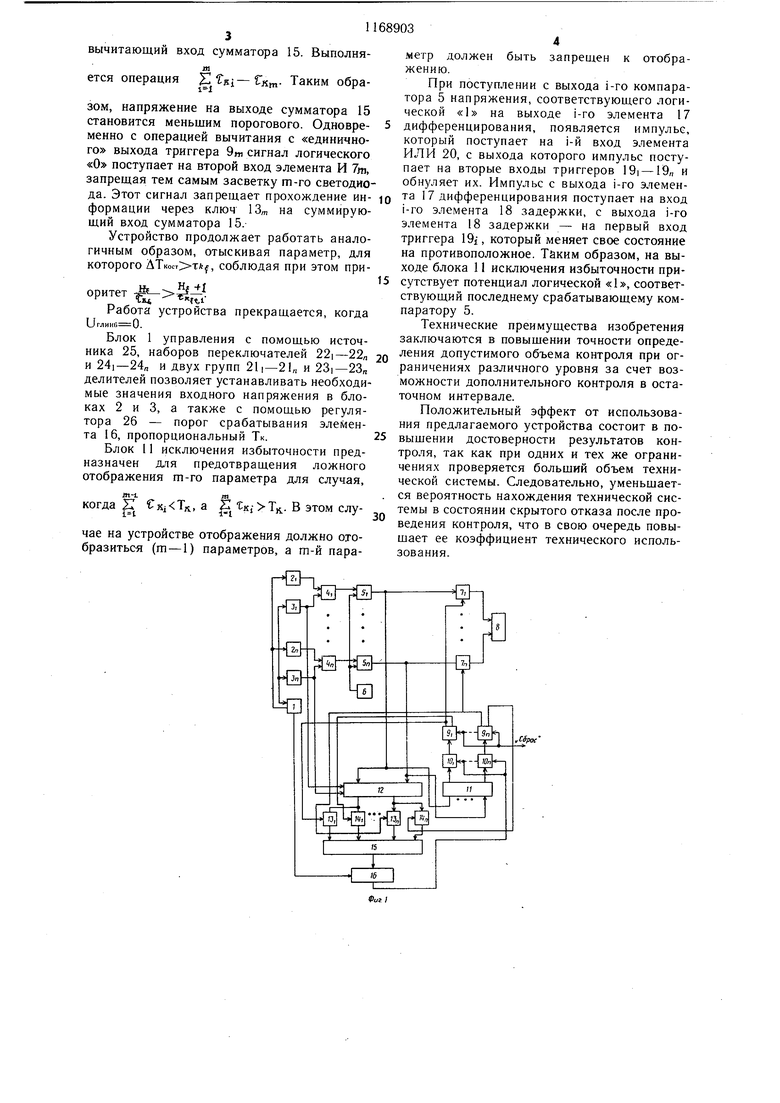

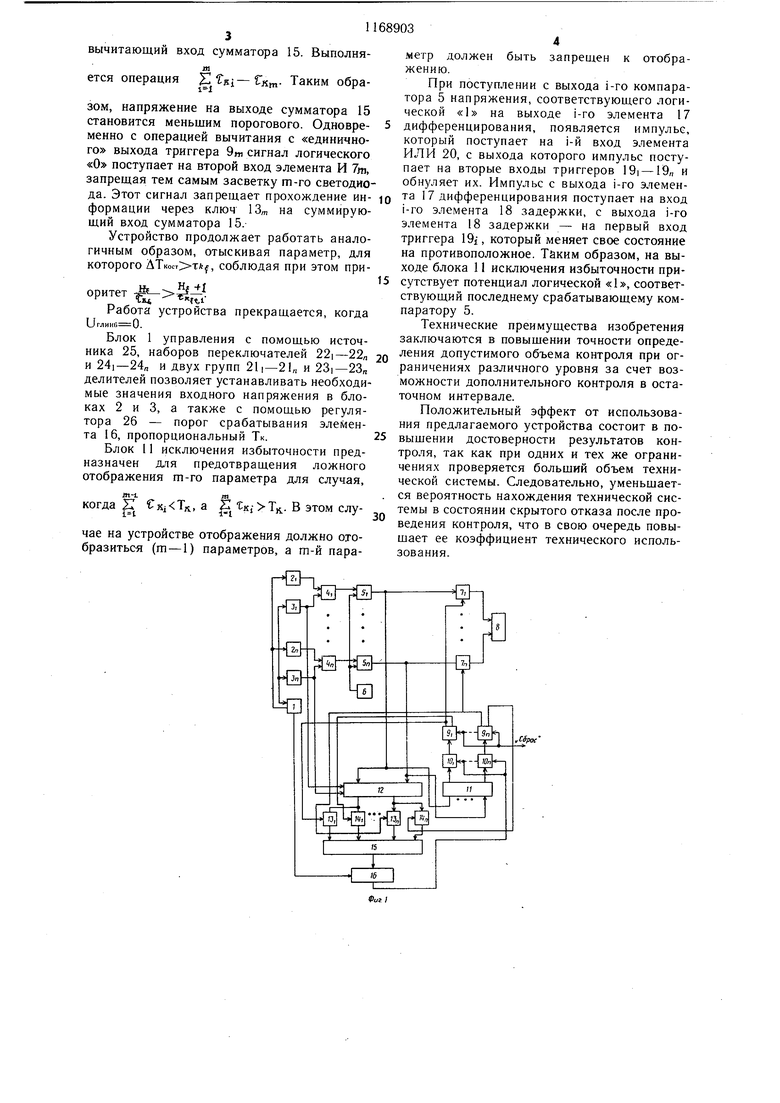

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока исключения избыточности; на фиг. 3 - функциональная схема блока управления.

Устройство содержит блок 1 управления, первые 2i-2„ и вторые 3i-3„ блоки задания постоянных коэффициентов, блоки 4i- 4„ деления, компараторы 5i-5„, генератор 6 линейно изменяющегося напряжения, первые элементы И , блок 8 индикации, вторые триггеры 9i-9„, вторые элементы И , блок 11 исключения избыточности, аналоговый коммутатор 12, первые 13I--13,, и вторые 4„ ключи, сумматор 15, пороговый элемент 16.

Блок 11 исключения избыточности вклю4aet элементы i7i -17„ дифференцирования, элементы 18i-18„ задержки, первые триггеры 19| -19„ и элемент ИЛИ 20.

Блок 1 управления содержит первые делители 21i-2In напряжения , первые переключатели 22i-22п, вторые делители 23123п напряжения, вторые переключатели 24i24п, источник 25 постоянного напряжения и регулятор 26 напряжения.

Устройство работает следующим образом.

С блока 1 на блоках 2|-2„ устанавливаются напряжения, пропорциональные результатам контроля соответственно первого, второго, ..., п-го параметров контроля (Н,); на блоках 3:-3„ - напряжения, пропорциональные длительности контроля соответственно первого, второго, ..., п-го параметров контроля тк,; на втором входе порогового элемента - напряжение IJn, пропорциональное допустимому времени контроля (Тк). На выходах блоков 4,- деления напряжение пропорционально убыли энтропии по i-му параметру контроля за единицу времени контроля (Uni). Чем больше это напряжение, тем важнее этот пара.метр контроля по информационному критерию и выше его приоритет при контроле. Напряжение с выходов блоков 4i-4„ поступает на первые-входы компараторов 5i-5л, на вторые входы которых подается линейно изменяющееся напряжение от до нуля с блока 6.

В момент времени, когда Ui становится равным наибольшему из Ул на выходе i-ro компаратора появляется напряжение логической «1, которое поступает на i-й адресный вход аналогового коммутатора, первый вход элемента И 7, и на i-й

0 вход блока 11. Напряжение, пропорциональное TKi, с выхода блока 3, поступает на информационный i-й вход коммутатора 12 и коммутируется им на информационные входы ключей и 14: -14„. На управляющий вход ключа 13, поступает сигнал с «единичного выхода триггера 9,, а на управляющий вход ключа 14, - сигнал с «нулевого выхода.Если напряжение в сумматоре 15 меньше порогового, то сигнал с i-ro выхода

Q коммутатора 12 через ключ 13/ поступает на i-й суммирующий вход сумматора 15. Напряжение с сумматора 15 поступает на первый вход элемента 16. В случае, если оно меньше порогового, на вторых входах элементов И 10; -10„ напряжение отсутств)5 ет, поэтому, хотя на первый вход эле.мента 10/ подается напряжение логической «1 с i-ro выхода блока 11, напряжение на выходе элементов Id -10„ соответствует логическому «О, следовательно, триггеры 9i - 9 остаются в исходном состоянии, и с их

нулевых выходов напряжение логического «О подается на управляющие входы ключей 14i - 14„ и запрещает прохождение сигналов с выходов аналогового коммутатора 12 на вычитающие входы сумматора, а с «единичных выходов напряжение логической «1

подается на вторые управляющие входы ключей 13i - 13л и разрещает прохождение сигналов с выходов аналогового коммутатора 12 на суммирующие входы сумматора 15 и на вторые входы элементов И 1 -

0 7л. На выходе элемента И 7, появляется напряжение логической «1, которое засвечивает i-й светодиод блока 8.

Аналогично устройство работает по i-му и другим параметрам до тех пор, пока напряжение в сумматоре 15, пропорциональ5

ное 2. тк( J не превьиоает пороговое напряi m

жение, пропорциональное Тк на втором входе элемента 16. В этом случае с выхода элемента 16 поступает напряжение на

0 вторые входы элементов И lOi-10„. В соответствии с алгоритмом работы блока 11 на т-м его выходе появляется напряжение, которое поступает на вход триггера 9,л и изменяет его состояние на противоположное. С «нулевого выхода

5 триггера 9 сигнал логической «1 поступает на управляю1дий вход ключей 14„; и разрешает прохождение сигнала с выхода коммутатора 12 через ключ 14„, на т-и вычитающий вход сумматора 15. Выполня Гк„. Таким обрается операция зом, напряжение на выходе сумматора 15 становится меньшим порогового. Одновременно с операцией вычитания с «единичного выхода триггера 9 сигнал логического «О поступает на второй вход элемента И 7щ, запрещая тем самым засветку т-го светодиода. Этот сигнал запрещает прохождение информации через ключ 13 на суммирующий вход сумматора 15. Устройство продолжает работать аналогичным образом, отыскивая параметр, для которого ДТкост т, соблюдая при этом приоритет /. Работа устройства прекращается, когда иг.. Блок 1 управления с помощью источника 25, наборов переключателей 22i-22„ и 24i-24„ и двух групп 21i-21„ и 23i-23„ делителей позволяет устанавливать необходимые значения входного напряжения в блоках 2 и 3, а также с помощью регулятора 26 - порог срабатывания элемента 16, пропорциональный Тк. Блок 11 исключения избыточности предназначен предотвращения ложного отображения т-го параметра для случая. п-д.т , а CK,.. В этом случае на устройстве отображения должно отобразиться (т -1) параметров, а ш-й параметр должен быть запрещен к отображению. При поступлении с выхода i-ro компаратора 5 напряжения, соответствующего логической «1 на выходе i-ro элемента 17 дифференцирования, появляется импульс, который поступает на i-й вход элемента ИЛИ 20, с выхода которого импульс поступает на вторые входы триггеров 19i -19„ и обнуляет их. Импульс с выхода i-ro элемента 17 дифференцирования поступает на вход i-ro элемента 18 задержки, с выхода i-ro элемента 18 задержки - на первый вход триггера 19i, который меняет свое состояние на противоположное. Таким образом, на выходе блока 11 исключения избыточности присутствует потенциал логической «1, соответствующий последнему срабатывающему компаратору 5. Технические преимущества изобретения заключаются в повышении точности опреде ™ допустимого объема контроля при ограничениях различного уровня за счет возможности дополнительного контроля в остаточном интервале. Положительный эффект от использования предлагаемого устройства состоит в повышении достоверности результатов контроля, так как при одних и тех же ограничениях проверяется больщий объем технической системы. Следовательно, уменьшается вероятность нахождения технической системы в состоянии скрытого отказа после проведения контроля, что в свою очередь повыщает ее коэффициент технического использования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения выборки контролируемых параметров | 1984 |

|

SU1168904A1 |

| Устройство для контроля работы операторов | 1984 |

|

SU1290394A1 |

| Устройство для определения выборки контролируемых параметров | 1985 |

|

SU1290264A1 |

| Устройство централизованного контроля | 1984 |

|

SU1164738A1 |

| Устройство для определения выборки контролируемых параметров | 1985 |

|

SU1287119A1 |

| Устройство для определения комплекта запаса технической системы | 1986 |

|

SU1399772A1 |

| Устройство для определения объема контролируемых параметров | 1985 |

|

SU1368860A2 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для контурного управления промышленным роботом | 1984 |

|

SU1211691A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМА КОНТРОЛИРУЕМЫХ ПАРАМЕТРОВ, содержащее первые и вторые блоки задания постоянных коэффициентов, сумматор, пороговый элемент, блоки деления, компараторы, генератор линейно изменяющегося напряжения, первые и вторые элементы И, блок индикации, блок исключения избыточности, состоящий из элементов дифференцирования, элементов задержки, первых триггеров и элемента ИЛИ, а также аналоговый коммутатор и блок управления, состоящий из первых и вторых делителей напряжения, первых и вторых переключателей, источника постоянного напряжения и регулятора напряжения, причем выходы первых делителей напряжения объединены и связаны с входами первых блоков задания постоянных коэффициентов, выходы вторых делителей напряжения также объединены и подсоединены к входам вторых блоков задания постоянных коэффициентов, выход регулятора напряжения подключен к установочному входу порогового элемента, выходы первых блоков задания постоянных коэффициентов соединены с первыми входами соответствующих блоков деления, выходы вторых блоков задания постоянных коэффициентов соединены с вторыми входами соответствующих блоков деления и с соответствующими информационными входами аналогового коммутатора, первые входы компараторов соединены с выходами блоков деления, вторые входы компараторов - с выходом генератора линейно изменяющегося напряжения, а выходы компараторов - с первыми входами первых элементов И, с соответствующими адресными входами аналогового коммутатора и с входами соответствующих элементов дифференцирования, выходы первых триггеров соединены с первыми входами вторых элементов И, к вторым входам которых подключен выход порогового элемента, выходы первых элементов И связаны с входами блока индикации, а выход сумматора соединен с входом порогового элемента, выходы элементов дифференцирования подключены к входам соответствующих элементов задержки и к входам элемента ИЛИ, выход которого связан с «нулевыми входами первых триггеров, ш (О «единичные входы которых соединены с выходами эле.ментов задержки, выходы первых и вторых переключателей подсоединены к первым входам соответствующих первых и вторых делителей напряжения, вторые входы которых подключены к положительному выходу источника постоянного напряжения, через регулятор напряжения связанному с отрицательным выходом источника, отличающееся тем, что, с целью повышения точности устройства за счет доО5 полнительного контроля в остаточном интервале, в него введены первые и вторые 00 ключи, вторые триггеры, причем выходы вторых элементов И соединены с входами О соответствующих вторых триггеров, «единичные выходы вторых триггеров связаны с со вторыми входами соответствующих первых элементов И, с управляющими входами соответствующих первых ключей, «нулевые выходы вторых триггеров соединены с управляющими входами соответствующих вторых ключей, выходы аналогового коммутатора связаны с информационными входами первых и вторых ключей, выходы первых ключей соединены с суммирующими входами сумматора, а выходы вторых ключей - с вычитающими входами сумматора.

| Аналоговый оптимизатор числа запасных блоков | 1978 |

|

SU752386A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-01-24—Подача