113041

Изобретение относится к информационно-измерительной технике, в частности к приборам для регистрации в Цифровом виде однократных или редко повторяющихся электрических сигна- 5 лов, и может быть использовано для исследования быстропротекагащих одно- кратНых процессов.

Цель изобретения - повышение точности регистрации за счет определения действительных (реальных) значений порогов (уровней) преобразования и вычисления уточненных оценок мгновенных значений. с

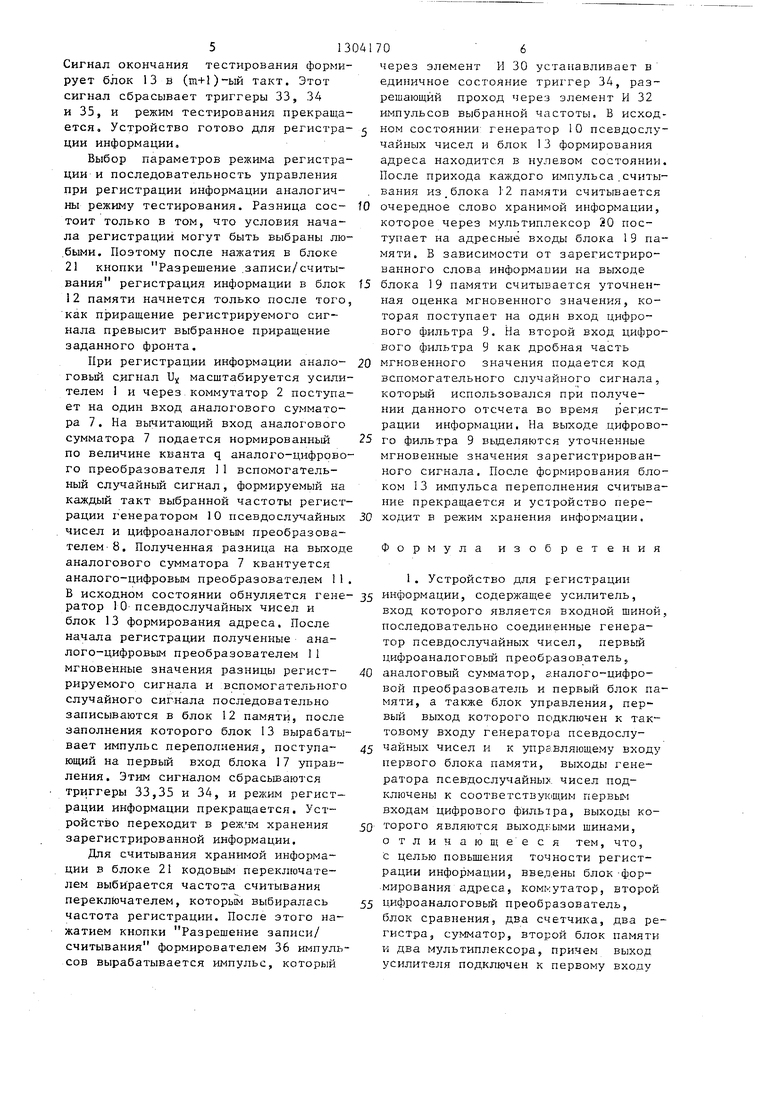

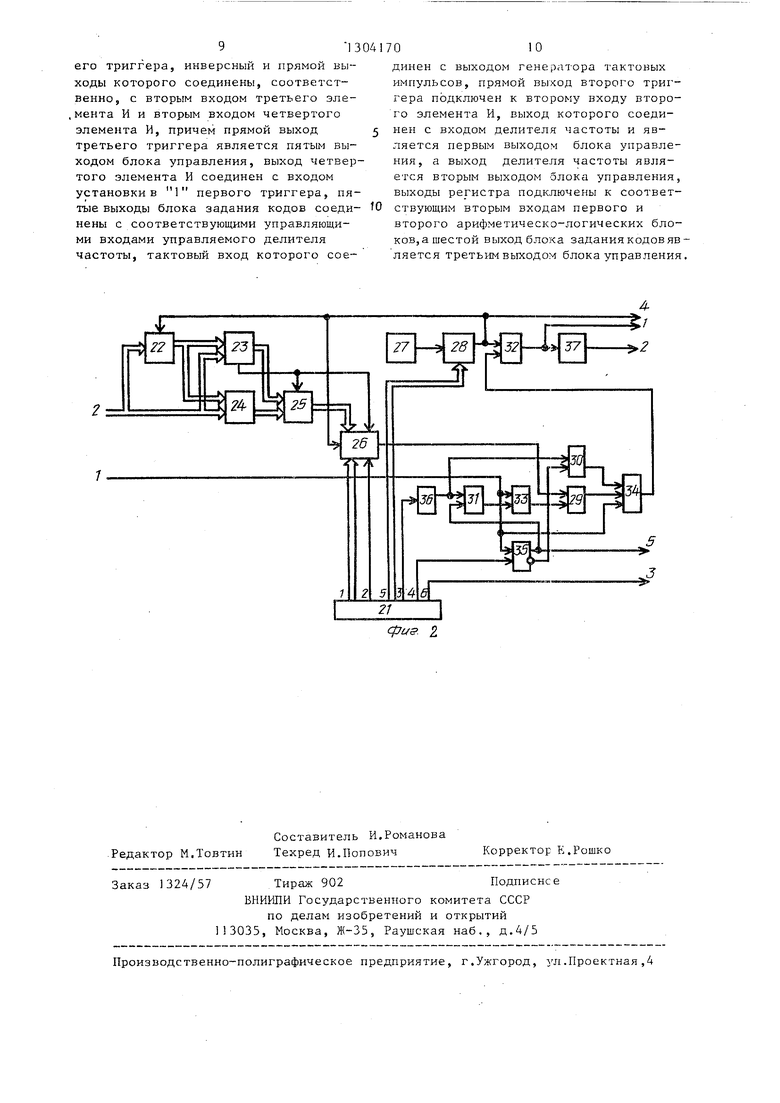

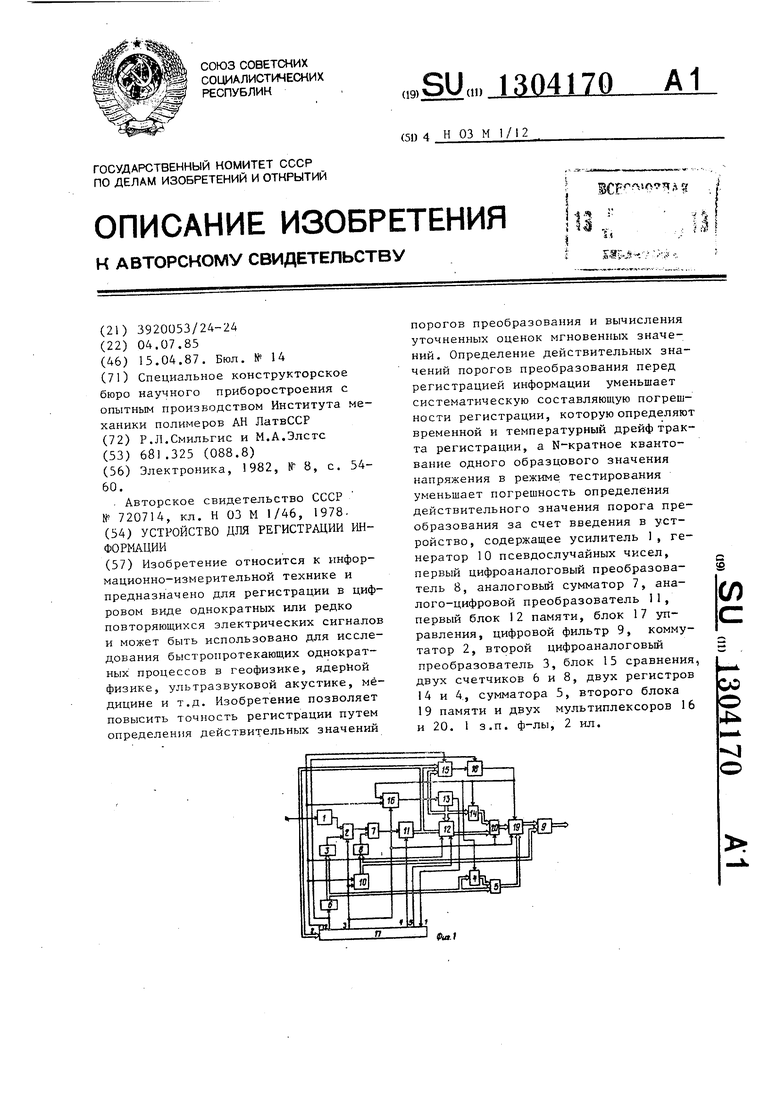

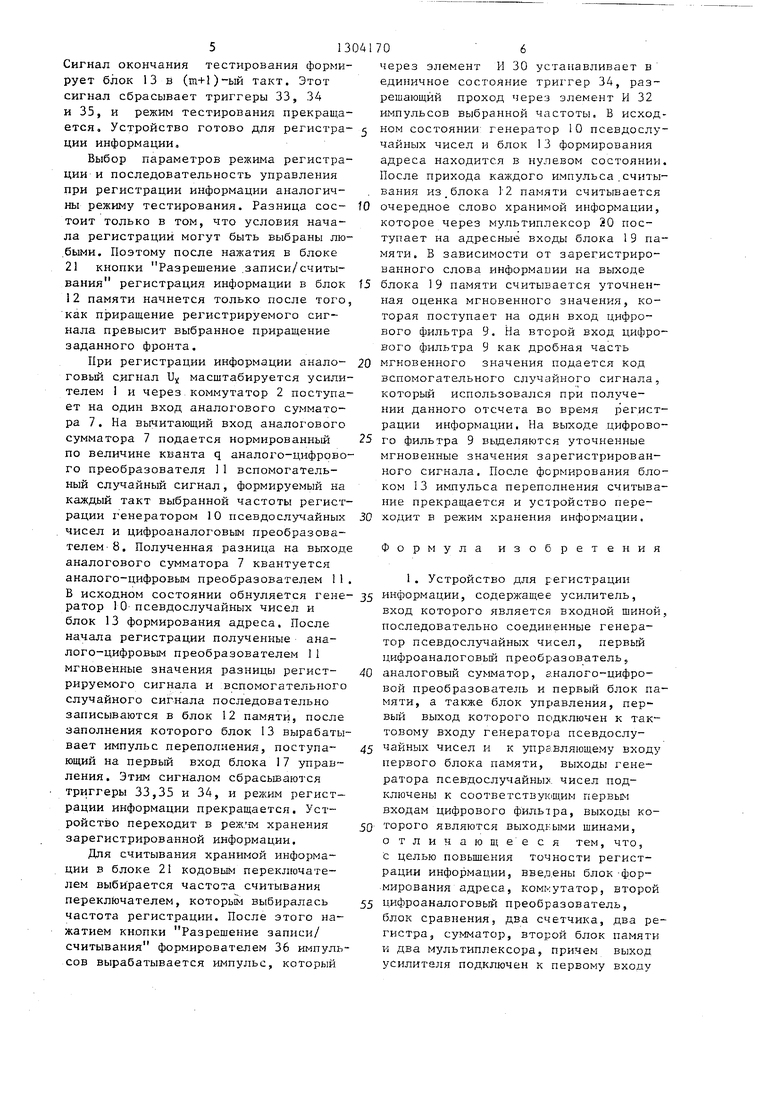

На фиг.1 изображена функциональная схема устройства для регистрации; на фиг.2 - структурная схема блока управления .

Устройство для регистрации информации содержит .усилитель 1 , коммутатор 2, первый цифроаналоговый преобразователь 3, первьп регистр 4, сумматор 5, первый счетчик 6, сумматор 7, второй цифроаналоговый преобразователь 8, цифровой фильтр 9, генератор 10 псевдослучайных чисел, аналого-цифровой.преобразователь 11, первый блок 12 памяти, блок 13 форми рования адреса, второй регистр 14, блок 15 сравнения, первый мультиплексор 16, блок 17 управления, второй счетчик 18, второй блок 19 памяти, второй мультиплексор 20. Четвертый выход блока 17 управления подключен к стробирующему входу аналого-цифровго преобразователя 11, а пятый выход блока 17 управления соединен с входом разрешения записи блока 12 памяти. Выход сумматора 5 подключен к информационному входу блока 19 памяти,, а его выход соединен с вторым входом цифрового фильтра.9, выход которого является выходом устройства

Блок 17 управления содержит блок 21 задания кодов, регистр 22, два арифметическо-логических блока 23 и 24, мультиплексор 25, цифровой компаратор 26, генератор 27 тактовых импульсов, управляемый делитель 28 частоты, четыре элемента И 29-32, три триггера 33-35, формирователь 36 импульсов и делитель 37 частоты.

Устройство работает следующим образом.

Устройство для регистрации информации может работать в трех режимах: тестирования, регистрации и с.чи .тывания записанной информации. Отли

5

0

5

702

чие работы устройства в режиме тестирования от работы в режиме регистрации состоит в том, что в режиме тестирования регистрирун:1тся образцовые значения напряжений первого цифро- аналогового преобразователя 3с Перед регистрацией информации производится тестирование устройства с целью, определения действител1.ных значений порогов квантования аналого-цифрового преобразователя 11 и последующего вычисления оценок мгновенного значения, в зависимости от полученного результата квантования. Реясим тестирования выбирается на блоке 21 нажатием переключателя lIpoBBpKii. Блок 2 представляет собой набор средств управления, а именно кнопок и переключателей, при нажатии Пб;реключателя Проверку с шестого выхода блока 21 через третий выход блока 17 управления подается сигнал, соответствующий 1. При этом блокируется управляющий вход генератора 10 псевдослучайных чисел, находящегося в нулевом состоянии, а к В1;оду аналого- цифрового преобразователя 11 через аналоговый сумматор 7 и коммутатор 2 подключается выход первого цифроана- логового преобразователя 3. Далее на блоке 21 кодовым переключателем выбирается частота регистрации. Соответствующий ей код, выбранный кодовым переключателем, с пятого выхода блока 21, поступает на управляющий вход управляемого делителя 28 частоты, посредством которого частота генератора 27 тактовых импульсов делит.„ с на 2 , где - выбранное кодовым переключателем число. После этого в блоке 21 кодовым переключателем Приращение и переключателем Нарастание - спад выбираются условия нача ла регистрации, включающие соответственно приращение регистрируемого сигнала и его фронт. Соответствующий выбранному приращению код и выбранному фронту логический сигнал по первому и второму выходам блока 21 поступают на цифровой компаратор 26. В режиме тестирования кодовый переключатель Приращение устанавливается в нулевое состояние. При нажатии в блоке 2 кнопки Подготовка триггер 35 устанавливается в единичное состояние, приводя устройство в готовность для регистрации информации. Перед началом регистрации приводятся

0

5

0

5

в нулевое состояние счетчики 6 и 18, регистры 4 и 1А и устанавливается код, равный 1, блоку 10.

При нажатии на пульте 21 управления кнопки Разрешение записи/считывания формирователем 36 импульсов формируется импульс длительностью меньше t A, где t - период генератора 27 тактовых импульсов; А - количество отсчетов, записываемых в блок 12 памяти. Сформированный импульс через элемент И 31 устанавливает в единичное состояние триггер 33, разрешающий при выполнении условий начала регистрации начать регистрацию.

Импульс Пуск вырабатывает цифровой компаратор 26 при превышении приращения регистрируемого сигнала выбранного приращения соответствук - щего фронта.

Перед началом регистрации информации регистрируемый аналоговый сигнал квантуется аналого-цифровым преобразователем 11 выбранной частоты регистрации, поступающей с выхода управляемого делителя 28 частоты по четвертому выходу блока 17 управления. Каждый результат .квантования

, блока

управления импульсов стр

/0

15

бирования блока 15 сравнения.

Во время режима тестирования с чиком 6 и цифроаналоговым преобра вателем 3 формируются 2 -1 значен образцового напряжения U , котор через коммутатор 2 и аналоговый матор 7 поступают на аналого-цифр преобразователь 11 и квантуются выбранной частотой, где п 1,2,. 2 -1, k - количество разрядов пе вого цифроаналогового преобразова ля 3. Каждое значение напряжения Иол раз квантуется и каждый полученны результат U сравнивается блоком сравнения с искомым порогом кванто ния ш, сформированным блоком 13, где ,2,...,2 , где р - количество разрядов аналого-цифрового

20 преобразователя 11. Счетчиком 18 п считывается число раз совпадения кода результата квантования Ug с кодом искомого порога т. Если в те чение N тактов, задаваемых делител

25 37 частоты, счетчик 18 не перепол нится, т.е. количество раз меньше или равно N/2, то после N т тов счетчик 18 сбрасывается и к ре зультату счетчика 6 прибавляется е

30 ница - формируется следующее значе

и. поступает через второй вход бло- ™ напряжения U и N-тактовый

Q ков 17 управления на входы арифметическо-логических блоков 23 и 24, посредством которых определяется UQ - й- UQ., - U(j, где UQ., -предыдущий результат квантования, хранящийся в регистре 22. Если UQ - ,0, то арифметичёско-логический блок 23 на выходе переполнения формирует сигнал, который одновременно с полученной разницей UQ., -UQ арифметическо-ло- гическим блоком 24 подается через мультиплексор 25 на третий и четвертый входы цифрового компаратора 26 для сравнения с выбранными условиями начала регистрации. Если же Ug .,0, то на цифровой компаратор 26 поступает разница, полученная арифметичес- ко-логическим блоком 23. Так как приращение сигнала в режиме тестирования выбирается равным нулю, то со следующим тактовым импульсом регистрации после разрешения записи цифровым компаратором 26 формируется импульс, который через элемент И 29 устанавливает в единичное состояние триггер 34, разрешающий проход через элемент И 32 по первому выходу

40 величине

HilDL.

j nn.

, где код

цикл преобразования - сравнения повторяется. Если в течение N тактов число раз UQ m больше N/2, 35 то счетчик 18 формирует сигнал, ко торый в адрес, равный т-1, блока 1 памяти записывает уточненную оценк мгновенного значения Up,, равную

, 2

m-ro порога квантования, Ijon °Д (m-l)-ro порога квантования. Эта в личина определяется сумматором 5. При этом код адреса т-1 и код вели чины UQ хранятся соответственно в регистре 14 и в регистре 4. Делени на два осуществляется переносом за пятой на один разряд. После записи и в блок 19 памяти тем же сигнало счетчика 18 в регистры 14 и 4 запи сываются соответственно m и И , а содержимому блока 13 через мультип сор 16 добавляется единица, т.е. устанавливается следующий искомый порог квантования. Аналогичным обр ,зом определяются и в блок 19 памят записываются все остальные уточнен ные оценки мгновенного значения U

45

50

55

,

13041 /О

, блока

управления импульсов стро

бирования блока 15 сравнения.

Во время режима тестирования счетчиком 6 и цифроаналоговым преобразо-- вателем 3 формируются 2 -1 значения образцового напряжения U , которые через коммутатор 2 и аналоговый сумматор 7 поступают на аналого-цифровой преобразователь 11 и квантуются выбранной частотой, где п 1,2,..., 2 -1, k - количество разрядов первого цифроаналогового преобразователя 3. Каждое значение напряжения Иол N раз квантуется и каждый полученный результат U сравнивается блоком 15 сравнения с искомым порогом квантования ш, сформированным блоком 13, где ,2,...,2 , где р - количество разрядов аналого-цифрового

преобразователя 11. Счетчиком 18 подсчитывается число раз совпадения кода результата квантования Ug с кодом искомого порога т. Если в течение N тактов, задаваемых делителем

37 частоты, счетчик 18 не переполнится, т.е. количество раз меньше или равно N/2, то после N тактов счетчик 18 сбрасывается и к результату счетчика 6 прибавляется единица - формируется следующее значе™ напряжения U и N-тактовый

0 величине

HilDL.

j nn.

, где код

цикл преобразования - сравнения повторяется. Если в течение N тактов число раз UQ m больше N/2, 5 то счетчик 18 формирует сигнал, который в адрес, равный т-1, блока 19 памяти записывает уточненную оценку мгновенного значения Up,, равную

, 2

m-ro порога квантования, Ijon °Д (m-l)-ro порога квантования. Эта величина определяется сумматором 5. При этом код адреса т-1 и код величины UQ хранятся соответственно в регистре 14 и в регистре 4. Деление на два осуществляется переносом запятой на один разряд. После записи и в блок 19 памяти тем же сигналом счетчика 18 в регистры 14 и 4 записываются соответственно m и И , а к содержимому блока 13 через мультиплексор 16 добавляется единица, т.е. устанавливается следующий искомый порог квантования. Аналогичным обра- ,зом определяются и в блок 19 памяти записываются все остальные уточненные оценки мгновенного значения U,

5

0

5

513041

Сигнал окончания тестирования формирует блок 13 в (т+1)ый такт. Этот сигнал сбрасывает триггеры 33, 34 и 35, и режим тестирования прекращается. Устройство готово для регистра- ном состоянии генератор 10 нсевдослучайных чисел и блок 13 формирования адреса находится в нулевом состоянии. После прихода каждого импульса .считывания из блока 12 памяти считывается очередное слово хранимой информации, которое через мультиплексор 20 поступает на адресные входы блока 19 памяти. В зависимости от зарегистрированного слова информаБии на выходе блока 19 памяти считывается уточненная оценка мгновенного значения, которая поступает на один вход цифрового фильтра 9. На второй вход цифрового фильтра 9 как дробная часть мгновенного значения подается код вспомогательного случайного сигнала, который использовался при получении данного отсчета во время регистрации информации. На выходе цифрового фильтра 9 вьщеляются уточненные мгновенные значения зарегистрированного сигнала. После формирования блоком 13 импульса переполнения считывание прекращается и устройство переходит в режим хранения информации.

ции информации.

Выбор параметров режима регистрации и последовательность управления при регистрации информации аналогичны режиму тестирования. Разница сое- тоит только в том, что условия начала регистрации могут быть выбраны лю.быми. Поэтому после нажатия в блоке 21 кнопки Разрешение .записи/считывания регистрация информации в блок 12 памяти начнется только после того, как п риращение регистрируемого CHI- нала превысит выбранное приращение заданного фронта.

При регистрации информации анало- говьй с.игнал Uy масштабируется усилителем 1 и через.коммутатор 2 поступает на один вход аналогового сумматора 7. На вычитающий вход аналогового сумматора 7 подается нормированный по величине кванта q аналого-цифрового преобразователя 11 вспомогательный случайный сигнал, формируемый на каждый такт выбранной частоты регистрации генератором 10 псевдослучайных

, чисел и цифроаналоговым преобразователем- 8. Полученная разница на выходе аналогового сумматора 7 квантуется аналого-цифровым преобразователем 1

40

45

В исходном состоянии обнуляется гене- 35 информации, содержащее усилитель, ратор 10- псевдослучайных чисел и блок 13 формирования адреса. После начала регистрации полученные аналого-цифровым преобразователем 11 мгновенные значения разницы регистрируемого сигнала и вспомогательного случайного сигнала последовательно записываются в блок 12 памяти, после заполнения которого блок 13 вырабатывает импульс переполнения, поступающий на первый вход блока 17 управления. Этим сигналом сбрасьшаются триггеры 33,35 и 34, и режим регистрации информации прекращается. Устройство переходит в реж. гм хранения зарегистрированной информации.

Для считывания хранимой информации в блоке 21 кодовым перекл очате- лем выбирается частота считывания переключателем, которым выбиралась частота регистрации. После этого нажатием КН.ОПКИ Разрешение записи/

вход которого является входной шин последовательно соединенные генера тор псевдослучайных чисел, первый цифроаналоговый преобразователь, аналоговый сумматор, аналого-цифро вой преобразователь и первый блок мяти, а также блок управления, пер вый выход которого подключен к та товому входу генератора псевдослучайных чисел и к упревляющему вхо первого блока памяти, выходы гене ратора псевдослучайных чисел подключены к соответствук1щим первым входам цифрового фильтра, выходы к торого являются выходными шинами, отлинаюп.1ееся тем, что с целью повышения точности регист рации информации, ввел.ены блок -фор мирования адреса, ком1 :утатор, втор 55 цифроаналоговьш преобразователь,

блок сравнения, два счетчика, два гистра, сумматор, второй блок памя и два мультиплексора, причем выхо усилителя подкл цочен к первому вход

50

считывания формирователем 36 импульсов вырабатывается импульс, который

70 6 через элемент И 30 устанавливает в единичное состояние триггер 34, разрешающий проход через элемент И 32 имнульсов выбранной частоты. В исходном состоянии генератор 10 нсевдослучайных чисел и блок 13 формирования адреса находится в нулевом состоянии. После прихода каждого импульса .считывания из блока 12 памяти считывается очередное слово хранимой информации, которое через мультиплексор 20 поступает на адресные входы блока 19 памяти. В зависимости от зарегистрированного слова информаБии на выходе блока 19 памяти считывается уточненная оценка мгновенного значения, которая поступает на один вход цифрового фильтра 9. На второй вход цифрового фильтра 9 как дробная часть мгновенного значения подается код вспомогательного случайного сигнала, который использовался при получении данного отсчета во время регистрации информации. На выходе цифрового фильтра 9 вьщеляются уточненные мгновенные значения зарегистрированного сигнала. После формирования блоком 13 импульса переполнения считывание прекращается и устройство переходит в режим хранения информации.

Формула изобретения 1. Устройство для регистрации

информации, содержащее усилитель,

вход которого является входной шиной, последовательно соединенные генератор псевдослучайных чисел, первый цифроаналоговый преобразователь, аналоговый сумматор, аналого-цифровой преобразователь и первый блок памяти, а также блок управления, первый выход которого подключен к тактовому входу генератора псевдослучайных чисел и к упревляющему входу первого блока памяти, выходы генератора псевдослучайных чисел подключены к соответствук1щим первым входам цифрового фильтра, выходы которого являются выходными шинами, отлинаюп.1ееся тем, что, с целью повышения точности регистрации информации, ввел.ены блок -формирования адреса, ком1 :утатор, второй цифроаналоговьш преобразователь,

блок сравнения, два счетчика, два регистра, сумматор, второй блок памяти и два мультиплексора, причем выход усилителя подкл цочен к первому входу

713

коммутатора, второй вход которого подключен к выходу второго цифроана- логового преобразователя, а выход соединен с вторым входом аналогового сумматора, входы второго цифроанало- гового преобразователя объединены с соответствующими информационными входами первого регистра, первыми входами сумматора, вторыми входами соединенного с соответствующими вы- ходами первого регистра, и подключены к соответствующим выходам первого счетчика, счетный вход которого объединен с входом сброса второго счетчика и подключен к второму выхо- ду блока управления, третий выход которого подключен к управляющему входу коммутатора, к управляющему входу генератора псевдослучайных чисел, к входу разрешения записи вто рого блока памяти, к входу управления первого мультиплексора и к входу управления второго мультиплексора, первые информационные входы которого соединены с выходами второго ре гистра, а вторые информационные входы - с выходами первого блока памяти первый выход блока управления соединен с первым информационным входом первого мультиплексора и с входом стробирования блока сравнения, выход первого мультиплексора подключен к тактовому входу блока формирования адреса, первьш выход которого соединен с первым входом блока управ лення, вторые входы которого объединены с первыми информационными входами блока сравнения и подключены к выходу аналого-цифрового преобразователя, а вторые информационные входы блока сравнения объединены с информа ционными входами второго регистра, адресными входами первого блока памяти и подключены к вторым выходам блока формирования адреса, выход блока сравнения подключен к счетному входу второго счетчика, выход которого соединен с вторым информа- 1Ц1ОННЫМ входом первого мультиплексора, с управляющими входами первого и второго регистров и с управляющим входом второго блока памяти, входы адреса которого подключены к выходам второго мультиплексора, информационные входы второго блока памяти сое- динены с выходом сумматора, а выходы подключены к вторым входам цифрового фильтра, четвертый выход блока уп708

равления подключен к стробирующему входу аналого-цифрового преобразователя, а пятый выход соединен с входом разрешения записи первого блока памяти.

2. Устройство по n .l , о т л и - чающееся тем, что блок управления выполнен на блоке задания кодов, регистре, двух арифметическо- логических блоках, мультиплексоре, цифровом компараторе, генераторе тактовых импульсов, управляемом делителе частоты, четырех элементах И, делителе частоты, трех триггерах и формирователе импульсов, первые и второй выходы блока задания кодов подключены к соответствующим первым и второму входам цифрового компаратора соответственно, третьи входы которого соединены с соответствующими выходами мультиплексора, четвертый вход объединен с управляющим входом мультиплексора, выходом переноса первого арифметическо-логического блока, первые информационные входы мультиплексора подключены к соответствующим выходам первого арифметическо-логического блока, а вторые информационны входы соединены с соответствующими выходами второго арифметическо-логического блока, первые входы которого объединены с первыми входами первого арифметическо-логического блока, информационными входами регистра и являются вторыми входами блока управления первым входом которого являются вхо- установки в О первого, второго и третьего триггеров, прямой выход первого триггера подключен к первому входу первого элемента И, второй вход которого подключен к выходу цифрового компаратора, пятый вход которого объединен с входом управления регистра, первым входом второго элемента И и подключен к выходу управляемого делителя частоты и является четвертым выходом блока управления, выход первого элемента И соединен с первым входом установки в второго триггера 5 второй вход установки в которого подключен к выходу третьего элемента И, первый вход которого объединен с первым входом четвертого элемента И и подключен к выходу формирователя импульсов, вход которого подключен к третьему выходу блока задания кодов, четвертый выход которого подключен к входу установки в 1 треть9 13041

его триггера, инверсный и прямой Bt)i ходы которого соединены, соответственно, с вторым входом третьего эле- ,мента И и вторым входом четвертого элемента И, причем прямой выход 5 третьего триггера является пятым выходом блока управления, выход четвертого элемента И соединен с входом установки в 1 первого триггера, пятые выходы блока задания кодов соеди- tO нены с соответствующими управляющими входами управляемого делителя частоты, тактовый вход которого соеСоставитель И.Романова .Редактор М.Товтин Техред И.Попович

1324/57

Тираж 902Подписнсе

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1 13035, Москва, Л(-35, Раушская наб. , д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

010

динен с выходом генератора тактовых импульсов, прямой выход второго триггера подключен к второму входу второго элемента И, выход которого соединен с входом делителя частоты и является первым выходом блока управления, а выход делителя частоты является вторым выходом блока управления, выходы регистра подключены к соответствующим вторым входам первого и второго арифметическэ-логических блоков,ашестой выход блока задания кодов является третьим выходом блока управления.

фиг. 2.

Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство для вычисления средней мощности случайных сигналов | 1982 |

|

SU1034044A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство управления вибрационными испытаниями | 1989 |

|

SU1735825A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Счетчик активной и реактивной мощности | 1986 |

|

SU1408382A1 |

Изобретение относится к информационно-измерительной технике и предназначено для регистрации в цифровом виде однократных или редко повторяющихся электрических сигналов и может быть использовано для исследования быстропротекающих однократных процессов в геофизике, ядерНой физике, ультразвуковой акустике, медицине и т.д. Изобретение позволяет повысить точность регистрации путем определения действительных значений порогов преобразования и вычисления уточненных оценок мгновенных значений. Определение действительных значений порогов преобразования перед регистрацией информации уменьшает систематическую составляющую погрешности регистрации, которую определяют временной и температурный дрейф тракта регистрации, а N-кратное квантование одного образцового значения напряжения в режиме тестирования уменьшает погрешность определения действительного значения порога преобразования за счет введения в устройство, содержащее усилитель 1, генератор 10 псевдослучайных чисел, первый цифроаналоговый преобразователь 8, аналоговый сумматор 7, аналого-цифровой преобразователь 11, первый блок 12 памяти, блок 17 управления, цифровой фильтр 9, коммутатор 2, второй цифроаналоговый преобразователь 3, блок 15 сравнения, двух счетчиков 6 и 8, двух регистров 14 и 4, сумматора 5, второго блока 19 памяти и двух мультиплексоров 16 и 20. 1 з.п. ф-лы, 2 ил. i сл оз о 4

| Электроника, 1982, W 8, с | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Устройство для регистрации информации | 1978 |

|

SU720714A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-15—Публикация

1985-07-04—Подача