ется тактовым входом устройства, а установочный вход регистра 4 -го блока умножения соединен с установочными входами третьего и четвертого регистров и с входом запуска устройства, первые входы элементов И первого и четвертого блоков умножения соединены и являются входом реальной части второго аргумента устройства, входом мнимой части которого являются

первые входы элементов И второго и третьего блоков умножения, вторые входы элементов И первого и третьего блоков умножения подключены к информационному выходу третьего регистра , а информациоиный выход четвертого регистра подключен к вторьи входам элементов И второго и четвертого блоков умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631555A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631556A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

УСТРОЙСТВО ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первый и второй регистры, информационные входы которых являются соответственно входами реальной и мнимой частей первого операнда устройства, первый и второй сумматоры-вычитатели, выходы которых являются выходами соответственно реальной и мнимой частей первого и второго операндов устройства, управляющие входы первого и второго регистров, первого и второго сумматоров-вычитателей соединены и являются тактовым входом устройства, входом запуска которого являются установочные входы первого и второго регистров, отличающееся тем, что, с целью упрощения устройства, оно содержит третий и четвертый регистры, первый и второй сумматоры, первый и второй коммутаторы, дешифратор знаков, четыре блока умножения и регистр знака, выходы первого и второго разрядов которого подключены к управляющим входам соответственно первого и второго коммутаторов, выходы которых подключены к первым входам соответственно первого и второго сумматоров-вычитателей, вторые входы которых подключены к выходам соответственно первого и второго сумматоров, информационные входы первого и второго коммутаторов подключены к информационным выходам соответственно первого и второго регистров, информационные входы третьего, и четвертого регистров являются соответственно входами реальной и мнимой частей коэффициентов устройства, знаковым входом которого является инфармационный вход регистра знака, (+2)-й (, 4) выход которого подключен к -i-My входу дешифратора знака, причем каждый блок умножения содержит сумматор, коммутатор, регистр и элемент И, выход которого подключен к первому входу сумматора, выход переноса которого подключен к первому информационному входу коммутатора, второй информационньй вход которого подключен к выходу старшего разряда регистра, выход младших разрядов которого подключен к второму входу сумматора, выход суммы которого подключен к информационному входу регистра, выходы коммутаторов первого и вторрго блоков умножения .подключены соответственно к первому и второму входам первого сумматора, а выходы коммутаторов третьего и четвертого блоков умножения - соответственно к первому и второму входам второго сумма,тора, i-й

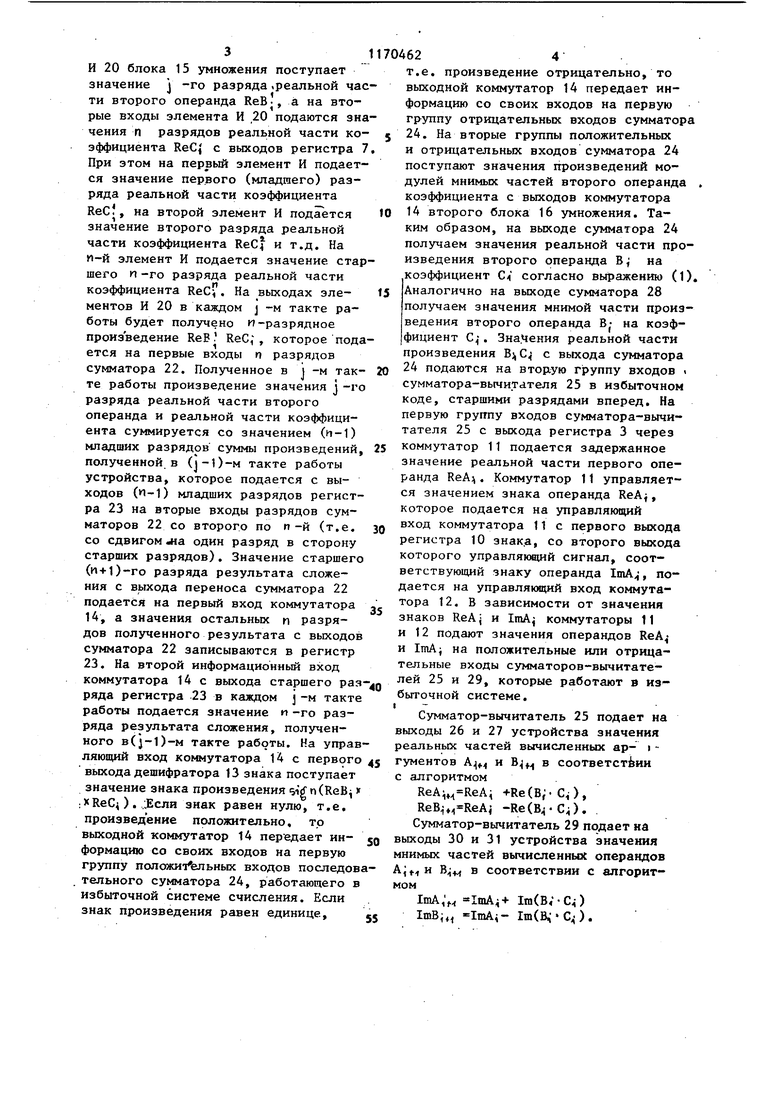

Изобретение относится к вычислительной технике и может быть использовано при определении спектральных характеристик сигналов. Цель изобретения - упрощение устройства. На чертеже изображена блок-схема устройства. Устройство содержит входы 1 и 2 реальной и мнимой частей первого опе ранда А, регистры 3 и 4, входы 5 и 6 реальной и мнимой частей коэффициента Cj, регистры 7 и 8, группу знаковых входов 9 устройства, регистр 10 знака, коммутаторы 11 и 12, дешифратор 13 знаков, коммутатор 14, блоки 15-18 умножения, входы. 19 реальной части второго операнда устрой ства В , элемент И 20, вход 21 мнимой части второго операнда устройства, сумматор 22, регистр 23, сумма тор 24, сумматор-вычитатель 25, выходы 26 и 27 реальных частей соответ ственно первого А|4| и второго Bj, операндов, сумматор 28, сумматор-вычитатель 29, выходы 30 и 31 мнимых частей соответственно первого А;, и второго В операндов устройства. входы 32 запуска устройства, тактовы вход 33 устройства. Устройство для быстрого преобразования Фурье работает по алгоритму А;,-А;+В;С; В;,,«А;-В;С;. Произведение операнда В на весовой коэффициент Сд вычисляется по алгоритму . Re (Вд С ) ReB ReC,- -UmB:; ImC, (1) Im(B C )IinBi ReCi -ReB, ImC . (2) В начале каждого цикла работы на первый управляющий вход 32 устройства подается импульс запуска, а на группу входов 9 устройства подаются значения знаков реальной и мнимых частей операндов и коэффициента, которые заносятся в регистр 10 знака импульсов запуска. Одновременно на входы 5 и 6 устройства подаются значения h разрядов реальной и мнимой частей коэффициента, которые заносятся в п-разрядные регистры 7 и 8, Импульс запуска устанавливают также в нулевое состояние регистры 3 и 4 и регистры 23 блоков умножения. Начиная с первого такта работы, на входы 1 и 2 устройства подаются значения вещественной и мнимой частей первого операнда А;; последовательно разряд за разрядом, начиная от старшего разряда, которые поступают в регистры 3 и 4. Одновременно на входы 19 и 21 устройства подаются значения реальной и мнимой частей второго аргумента В также последовательным кодом, старшими разрядами вперед, которые поступают на первые входы элементов И 20 и блоков 15-18 умножения. На второй управлякнций вход 33 устройства поступают тактовые импул сы которые подаются на управляющие входы регистров 3 и 4, регистров 23 блоков умножения, сумматоров 24 и 2:8 и сумматоров-вычитателей 25 и 29. Работу блоков 15-18 умножения рассматривают на примере работы блока 15 умножения, так как все блоки, умножения работают аналогично. В каждом j -м такте работы (j 1,2,...) на первые входы элемента

И 20 блока 15 умножения поступает значение j -го разряда .реальной части второго операнда ReB-, а на вторые входы элемента И ,20 подаются значения п разрядов реальной части коэффициента ReCJ с выходов регистра 7 При этом на первый элемент И подается значение первого (младшего) разряда реальной части коэффициента ReCJ, на второй элемент И подается значение второго разряда реальной части коэффициента ReC и т.д. На и-й элемент И подается значение старшего и-го разряда реальной части коэффициента Rec. На выходах элементов И 20 в каждом j -м такте работы будет получено и-разрядное произведение ReB ReC;, которое подается на первые входы и разрядов сумматора 22. Полученное в j -м такте работы произведение значения j-го разряда реальной части второго операнда и реальной части коэффициента суммируется со значением (п-1) младших разрядов суммы произведений, полученной в (j-O-м такте работы устройства, которое подается с выходов (ч-1) младших разрядов регистра 23 на вторые входы разрядов сумматоров 22 со второго по п-и (т.е. со сдвигом ла один разряд в сторону старших разрядов). Значение старшего (и+1)-го разряда результата сложения с выхода переноса сумматора 22 подается на первый вход коммутатора 14, а значения остальньк п разрядов полученного результата с выходов сумматора 22 записываются в регистр 23. На второй информационный вход коммутатора 14 с выхода старшего раз ряда регистра 23 в каждом -м такте работы подается значение и-го разряда результата слежения, полученного B(J-I)-M такте работы. На управляющий вход коммутатора 14 с первого выхода дешифратора 13 знака поступает значение знака произведения jirf n(ReBi ;XReC ) . .:Если знак равен нулю, т.е. произведение положительно, то выходной коммутатор 14 передает информацию со своих входов на первую группу положительных входов последовтельного сумматора 24, работающего в избыточной системе счисления. Если знак произведения равен единице,

т.е. произведение отрицательно, то выходной коммутатор 14 передает информацию со своих входов на первую группу отрицательных входов сумматор 24. На вторые группы положительных и отрицательных входов сумматора 24 поступают значения произведений модулей мнимых частей второго операнда коэффициента с выходов коммутатора 14 второго блока 16 умножения. Таким образом, на выходе сумматора 24 получаем значения реальной части произведения второго операнда В на коэффициент С согласно выражению (1 Аналогично на выходе сумматора 28 получаем значения мнимой части произведения второго операнда В- на коэффициент . Значения реальной части произведения В;, С с выхода сумматора 24 подаются на втор:ую г;руппу входов сумматора-вычитателя 25 в избыточном коде, старшими разрядами вперед. На первую группу входов сумматора-вычитателя 25 с выхода регистра 3 через коммутатор 11 подается задержанное значение реальной части первого операнда ReA;i. Коммутатор 11 управляется значением знака операнда ReA, которое подается на управляющий вход коммутатора 11 с первого выхода регистра 10 знака, со второго выхода которого управляющий сигнал, соответствующий знаку операнда , подается на управлякмдий вход коммутатора 12. В зависимости от значения знаков ReAj и ImAj коммутаторы 11 и 12 подают значения операндов ImAj на положительные или отрицательные входы сумматоров-вычитателей 25 и 29, которые работают в избыточной системе.

Сумматор-вычитатель 25 подает на выходы 26 и 27 устройства значения реальных частей вычисленных ар- i гументов А,. и в соответствии с алгоритмом

ReA;i ReAi fRe(B;-C,),

-Re().

Сумматор-вычитатель 29 подает на выходы 30 и 31 устройства значения мнимых частей вычисленных операндов и в соответствии с алгоритмом

1тА,н «ImA Im(B4-C)

Iin(Bi;Cx).

| Устройство для выполнения быстрого преобразования фурье | 1976 |

|

SU598085A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для быстрого преобразования фурье | 1977 |

|

SU750494A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-30—Публикация

1982-10-15—Подача