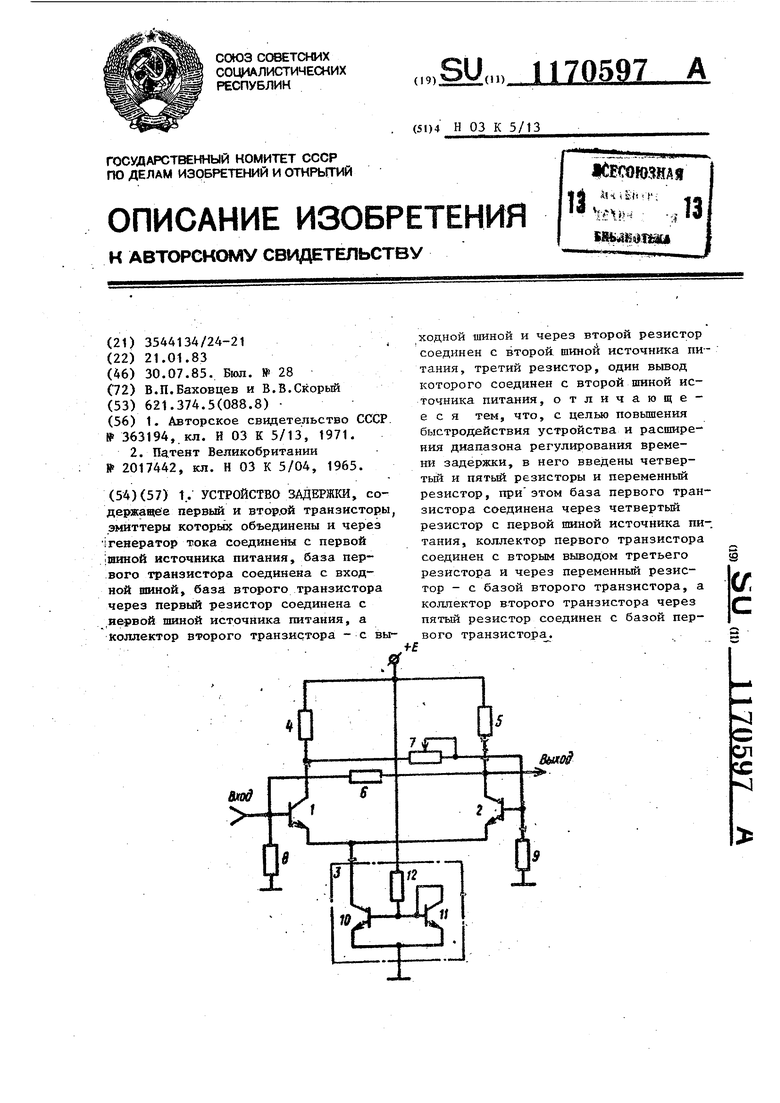

2. Устройство по. п. 1, о т л и чающееся тем, что генератор тока выполнен на третьем и четвертом транзисторах, базы которых объединены и соединены с коллектором четвертого транзистора, подключенно-1170597 го через тестой, резистор к второйшине источника питания, эмиттеры третьего и четвертого транзисторов объединены и являются выходом генератора тока, а коллектор третьего,транзистора - входом генератора тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ ПЛТгеТ1Ш-ТГШ:^;Е;л?= | 1973 |

|

SU363194A1 |

| Устройство осциллографической развертки | 1982 |

|

SU1075387A1 |

| Пороговое устройство | 1975 |

|

SU546097A1 |

| Устройство подсвета луча электронно-лучевой трубки | 1981 |

|

SU1002971A2 |

| Двухтактный релаксатор | 1978 |

|

SU765987A1 |

| Устройство для реакции на аварию в схеме управления потребителями электроэнергии | 1990 |

|

SU1795495A1 |

| Устройство осциллографической развертки | 1979 |

|

SU864144A1 |

| Устройство задержки | 1981 |

|

SU980187A1 |

| Стабилизированный инвертор | 1981 |

|

SU964908A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

Т.. УСТРОЙСТВО ЗАДЕРЖКИ, с держащее первый и втор.ой транзисто эмиттеры которых объединены и чере генератор тока соединены с первой |шиной источника питания, база пер вого транзистора соединена с входной шиной, база второго транзистор через первый резистор соединена с первой шиной источника питания, а , - Коллектор второго транзистора - с ходной иганой и через второй резистор соединен с второй шиной источника питания, третий резистор, один вьюод которого соединен с второй шиной источника питания, отличающееся тем, что, с целью повышения быстродействия устройства и расширения диапазона регулирования времени задержки, в него введены четвертьй и пятый резисторы и переменный резистор, при этом база первого транзистора соединена через четвертый резистор с первой пшной источника питания, коллектор первого транзистора соединен с вторым выводом третьего резистора и через переменный резистор - с базой второго транзистора, а коллектор второго транзистора через пятый резистор соединен с базой первого транзистора.

Изобретение относится к импульсной технике и может быть использовано в устройствах НС диапазона. Известно устройство задержки, по воляющее на выходе получать импульсы с короткими фронтами ( не), регулировка времени задержки в котором осуществляется переменным резис тором, содержащее релаксатор на транзисторе с туннельным диодом в эмиттерной цепи и бистабильную туннельно-диодную ячейку с транзистором сброса, база которого через резистор соединена с эмиттером транзистора релаксатора, а база транзистора релаксатора соединена через переменный резистор с шиной питания и через .разделительный диод - с выходом бистабильной туннельно-диодной ячейки 1. Недостатками данного устройства являются высокая критичность к соотношению амплитуды входных импульсов и напряжению ьпитания, что обуславливается необходимостью уравнивания .напряжений на аноде и катоде разделительного диода; низкая амплитуда выходных импульсов (0,4 В), так как они снимаются непосредственно с туннельного диода. Для большинства устройств такой амплитуды выходных импульсов недостаточно. Поэтому для усиления задержанных импульсов должен быть использован дополнительньй широкополосный усилитель, что, в свою очередь, значительно усложняет устройство задержки. Наиболее близким к предлагаемому является устройство задержки, содержащее первьй и второй транзисторы, эмиттеры которьк объединены и че рез генератор тока подключены к первой шине источника питания. База пер вого транзистора соединена с источником опорного напряжения, а база второго транзистора - с входной шиной. Коллектор первого транзистора соединен с выходной шиной и через резистор - со второй шиной источника литания. Коллектор второго транзистора подключен к второй шине источника питания LZJ . Недостатками известного устройства являются низкое быстродействие, приводящее к затягиванию фронтов выходных импульсов за счет интегрирования тока генератора тока конденсатором, шунтирующим базо-коллекторный переход транзистора генератора тока; высокое нулевое время задержки, которое не позволяет осуществлять зе- держку коротких входных импульсов и ограничивает диапазон регулирования времени задержки. Цель изобретения - повьш1ение быстродействия устройства и расширение диапазона регулирования времени задержки. Поставленная цель достигается тем, что в устройство задержки, содержащее первый и второй транзисторы эмиттеры которых объединены и через генератор тока соединены с пер вой шиной источника питания, база первого транзистора соединена с входной шиной, база второго транзистора через первый резистор соединена с первой шиной источника питания, а коллектор второго транзистора - с выходной шиной и через второй резис тор соединен с второй шиной источника питания, третий резистор, один из выводов которого соединен с второй, шиной источника питания, введены четвертый и пятый резисторы и переменный резистор, при этом база первого транзистора соединена через четвертый

Авторы

Даты

1985-07-30—Публикация

1983-01-21—Подача