Изобретение относится к области импульсной техники и может быть использовано, например, для согласования задержек в цепях быстродействующих устройств автоматики, для формирования импульсов заданной длительности, для моделирования задержек сигнала в устройствах вычислительной техники.

Известно устройство задержки импульсов, содержащее релаксатор на транзисторе с туннельным диодом в эмиттерной цепи и бистабильную туннельно-диодную ячейку с транзистором сброса, база которого через резистор соединена с эмиттером транзистора релаксатора.

Однако такое устройство, характеризующееся высокой стабильностью и малым временем восстановления, не обеспечивает возможности регулирования времени задержки выходных импульсов относительно входных.

Цель изобретения - регулирование интервалов задержки в щироких .пределах.

Она достигается тем, что между базой транзистора релаксатора, подсоединенной через переменный резистор к источнику напряжения коллекторного питания, и выходом бистабильной туннельно-диодной ячейки введен разделительный лолуп.роводниковый диод.

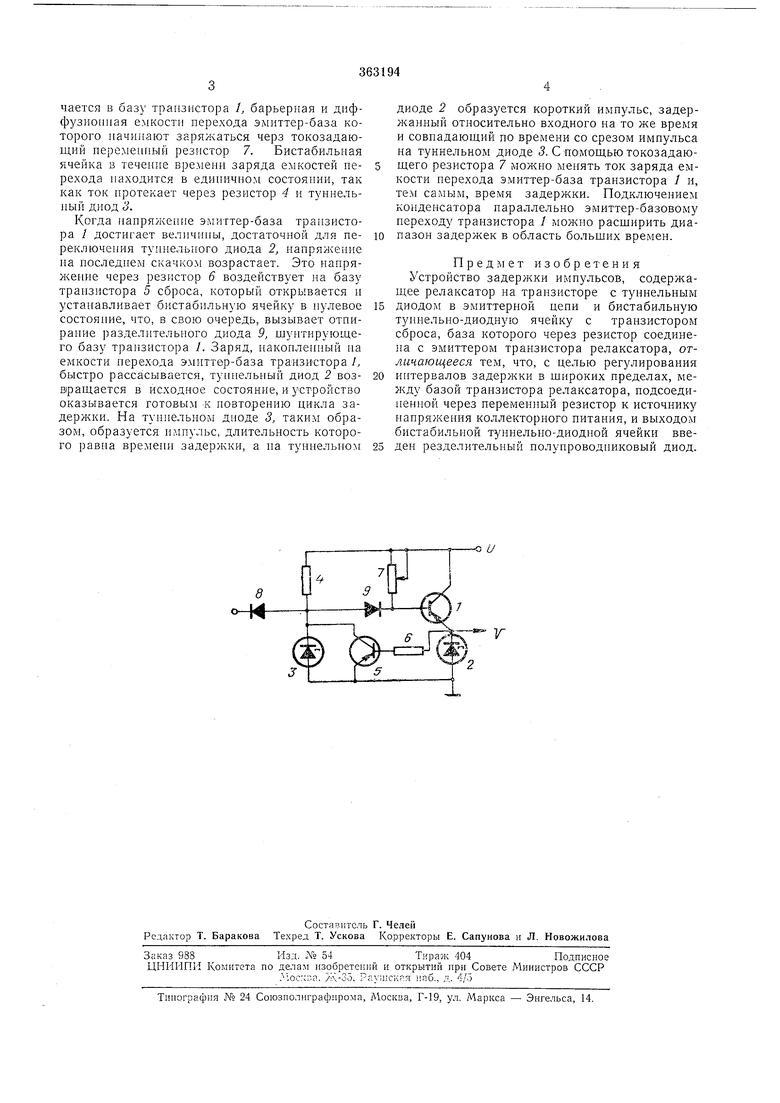

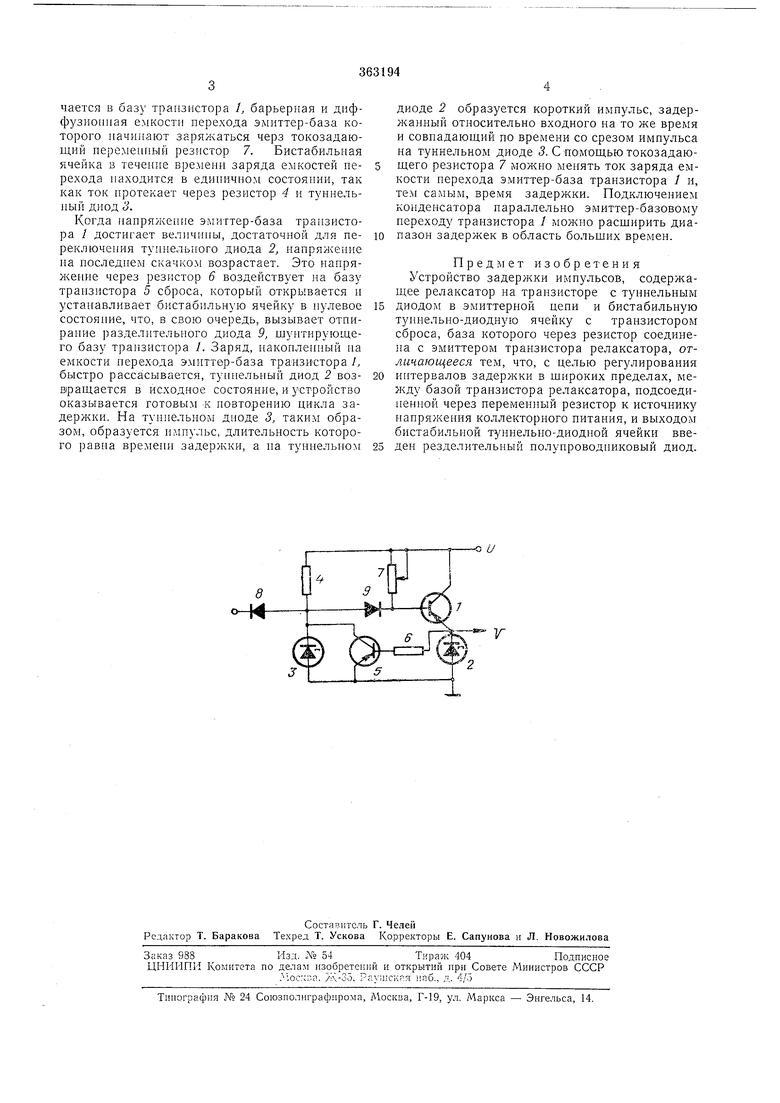

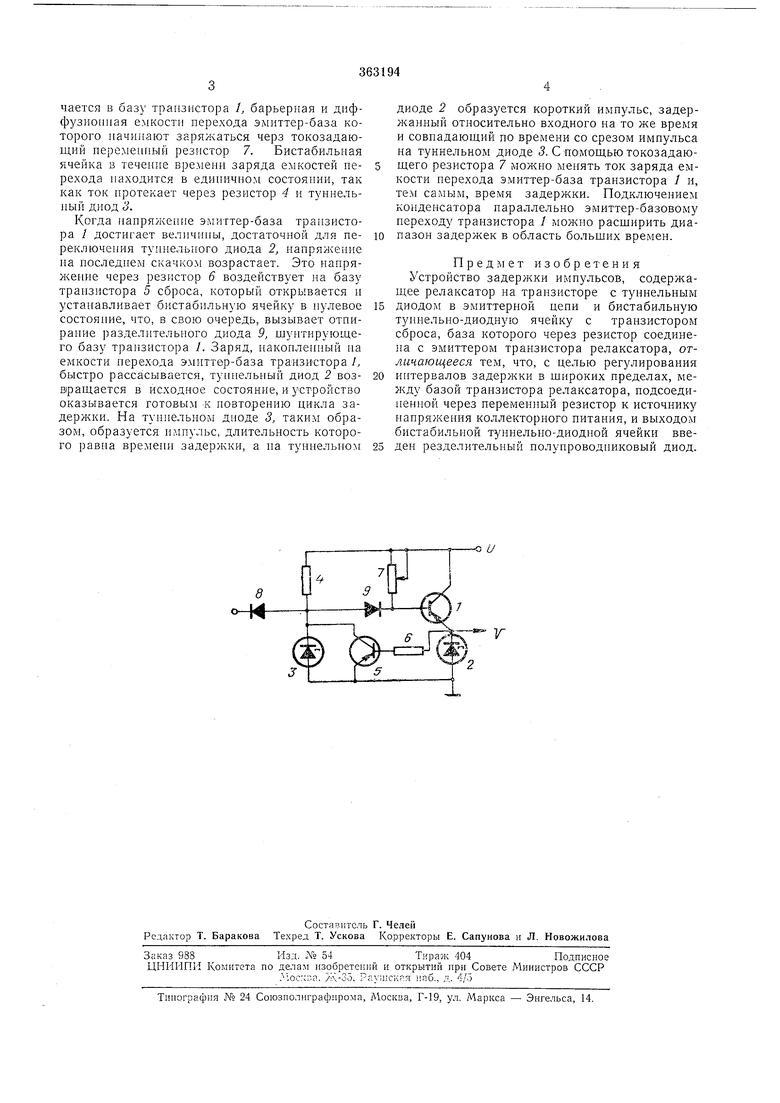

На чертеже изображена принципиальная схема предлагаемого устройства.

Оно содержит релаксатор на транзисторе /

с туннельным диодом 2 в эмнттерной цепи, бистабильную туннель 10-днодную ячейку, состоящую из туннельного диода 3 и резистора 4, с транзистором 5 сброса, база которого через резистор 6 соединена с эмнттером транзистора релаксатора и переменный резистор 7. Диод 5 служит для подачи импульса установки бистабильной туннельно-.диодной ячейки в единичное состояние. Разделительный полупроводниковый диод 9 введен между базой транзистора / релаксатора, нодсоединенно , в свою очередь, через переменный резистор 7 к источнику напряжения коллектор 1ого питания, и выходом бистабильной ту}1нельно-днодной ячейки. Выходное напря кен е снимается с туннельного диода 2.

Исходным для б стабнльной ячейки является нулевое состояние. При этом напряжение на туннельном диоде 3 мало, через этот диод резистор 4 и резистор 7 протекает ток. Напряжение на базе транзистора 1 релаксатора мало для перек.тючения тунне.тьного диода 2, находящегося в нулевом состоянии.

Входной импульс, поступающий через диод 8 на туннельный диод 3, переводит бистабильную ячейку в единичное состояние. Нри этом напряжение на туннельном диоде 3 и на аноде разделительного диода 9 скачком возрастает. Диод 9 переходит в непроводящее состояние, и ток, ранее протекавший через него, переключается в базу транзистора /, барьерная и диффузионная емкостн перехода эмиттер-база которого начинают заряжаться черз токозадающий переменный резистор 7. Бистабильная ячейка в течение времени заряда емкостей перехода находится в единичном состоянии, так как ток протекает через резистор 4 и тупне.тьный диод 3.

Когда напряжение эмиттер-база транзистора / достигает величины, достаточной для переключения туннельного диода 2, напряжение па последнем скачком возрастает. Это напряжение через резистор 6 воздействует на базу транзистора 5 сброса, который открывается и устанавливает бистабильную ячейку в пулевое состояние, что, в свою очередь, вызывает отпирание разделительного диода 9, шуитирующего базу транзистора /. Заряд, 1 акопле 1ный на емкости перехода эмиттер-база транзистора /, быстро рассасывается, туннельный диод 2 возвращается в исходное состояние, и устройство оказывается готовым к повторепию цикла задержки. На тупнелыюм дноде 3, таким образом, образуется импульс, длительность которого равна времени задержки, а па туннельном

диоде 2 образуется короткий импульс, задержанный относительпо входного на то же время и совпадающий по времени со срезом импульса на туннельном диоде 5. Cпoмoщьютoкoзaдaющего резистора 7 можно менять ток заряда емкости перехода эмиттер-база трапзистора 1 и, тем самым, время задержки. Подключением конденсатора параллельно эмиттер-базовому переходу транзистора / можно расщирить диапазон задержек в область больших времен.

Предмет изобретения Устройство задержки импульсов, содержащее релаксатор на транзисторе с туннельным

диодом в эмиттерной цепи и бистабильную туннельно-диодную ячейку с транзистором сброса, база которого через резистор соединена с эмиттером транзистора релаксатора, отличающееся тем, что, с целью регулирования

интервалов задержки в широких пределах, между базой транзистора релаксатора, подсоединенной через перемеппый резистор к источнику напряжепия коллекторного питания, и выходом бистабильной тупнельно-диодной ячейки введен разделительный полупроводниковый диод.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1983 |

|

SU1170597A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «НЕ-ИЛИ» | 1971 |

|

SU305588A1 |

| ПАТ?Ш'Ш-[1ХСГ'Е^:чДП | 1973 |

|

SU362487A1 |

| Быстродействующий логический элемент или-и-не | 1973 |

|

SU478441A1 |

| ОСВЕТИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2031554C1 |

| Логическая схема или-и-не | 1973 |

|

SU474109A1 |

| Динамический элемент | 1979 |

|

SU928619A1 |

| РАСПРЕДЕЛИТЕЛЬ—СЧЕТЧИК | 1972 |

|

SU332577A1 |

| Расширитель импульсов | 1977 |

|

SU687575A1 |

| РЕГИСТР СДВИГАПйТЕН t iiu* Ii:AJi г.: .:- ?:.a\! | 1972 |

|

SU350048A1 |

Авторы

Даты

1973-01-01—Публикация