2. Интегратор по п. 1, отличающийся тем, что коммутирующий каскад содержит коммутирующий транзистор, коллектор которого соединен с выходом коммутирующего каскада и через четвертый резистор - с

входом питания, база - через пятый резистор с общей шиной, соединенной через третий диод с эмиттером коммутирующего транзистора, который через третий конденсатор соединен с входом коммутирующего каскада.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1981 |

|

SU993473A1 |

| ИНДИКАТОР ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ | 1992 |

|

RU2060508C1 |

| Мультивибратор | 1978 |

|

SU741421A1 |

| Однотактный стабилизированный преобразователь постоянного напряжения | 1990 |

|

SU1777212A1 |

| Видеоусилитель | 1985 |

|

SU1322415A1 |

| Пороговый элемент | 1973 |

|

SU758499A1 |

| Мультивибратор | 1982 |

|

SU1160537A1 |

| Стабилизатор напряжения с самозащитой | 1982 |

|

SU1046751A1 |

| Частотно-фазовый детектор | 1980 |

|

SU921043A1 |

| Интегратор | 1979 |

|

SU802960A1 |

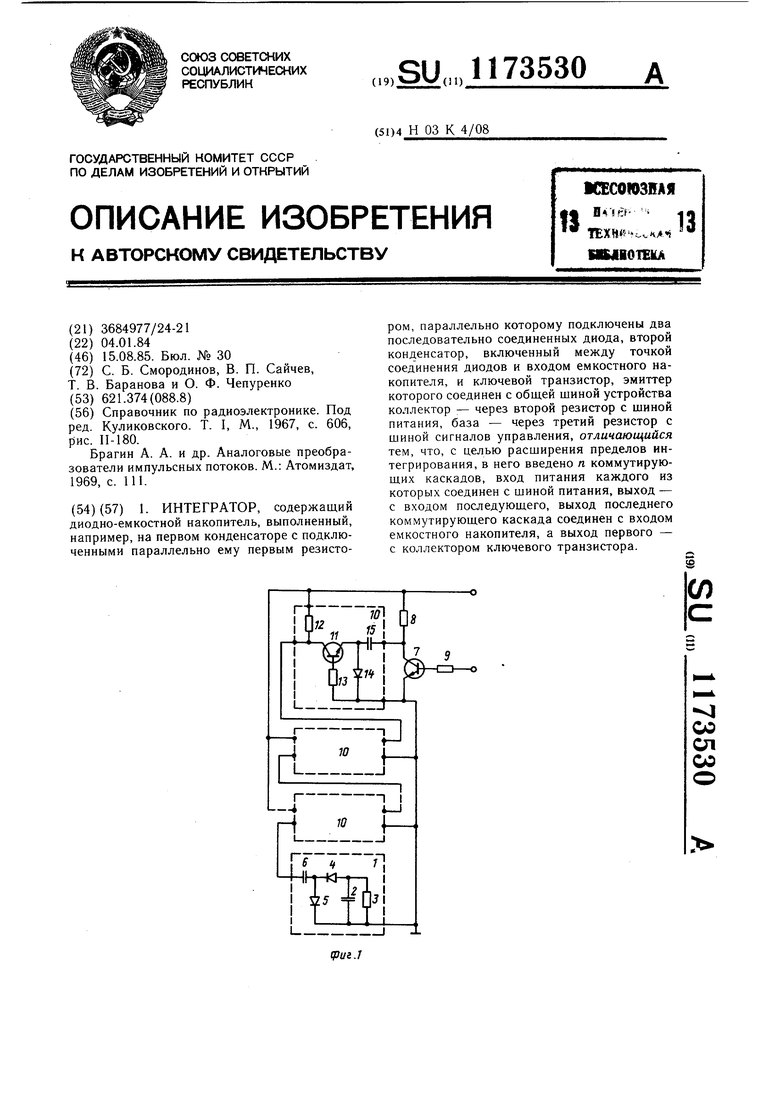

1. ИНТЕГРАТОР, содержащими диодно-емкостной накопитель, выполненный, например, на первом конденсаторе с подключенными параллельно ему первым резистором, параллельно которому подключены два последовательно соединенных диода, второй конденсатор, включенный между точкой соединения диодов и входом емкостного накопителя, и ключевой транзистор, эмиттер которого соединен с общей шиной устройства коллектор - через второй резистор с шиной питания, база - через третий резистор с шиной сигналов управления, отличающийся тем, что, с целью расширения пределов интегрирования, в него введено п коммутирующих каскадов, вход питания каждого из которых соединен с шиной питания, выход - с входом последующего, выход последнего коммутирующего каскада соединен с входом емкостного накопителя, а выход первого - с коллектором ключевого транзистора. (О с.(Л со ел со - 10 ч ч1 НркЬ|-I I mi

Изобретение относится к импульсной технике и может быть использовано в схемах аналоговой обработки импульсных сигналов.

Целью изобретения является расширение пределов интегрирования.

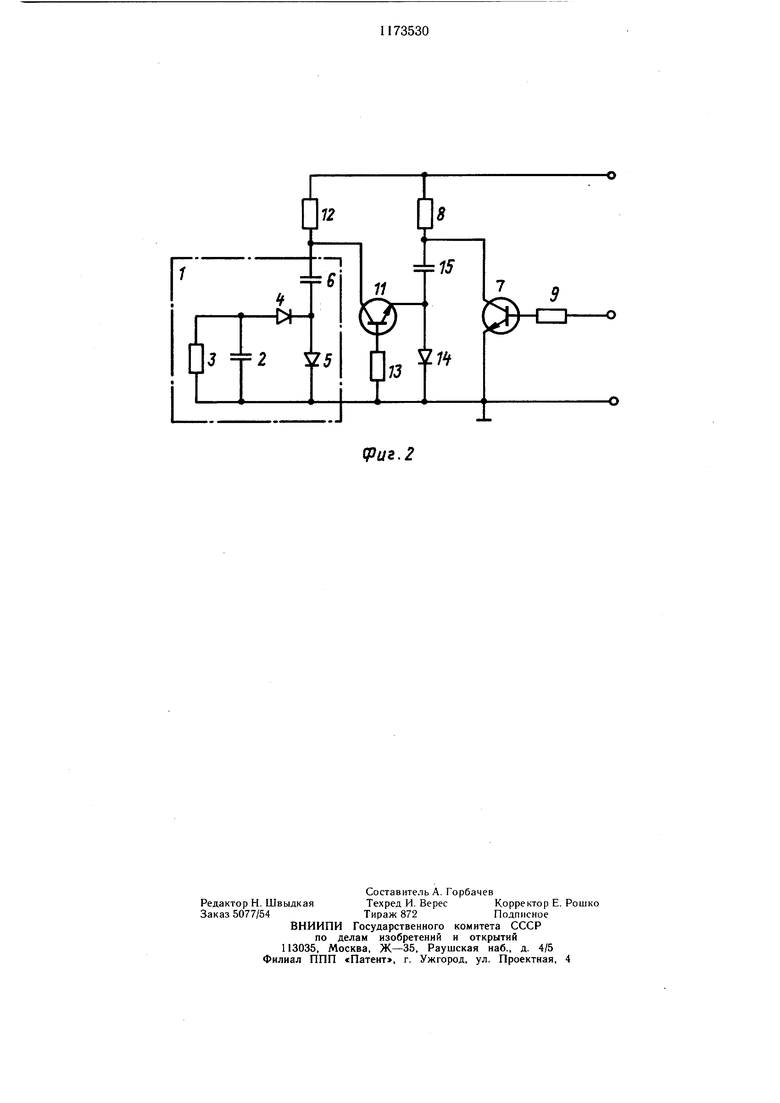

На фиг. 1 приведена принципиальная электрическая схема устройства; на фиг. 2 - однокаскадная схема устройства.

Устройство содержит диодно-емкостный накопитель 1, выполненный, например, на первом конденсаторе 2, с параллельно подключенным первым резистором 3, параллельно которому подключены два последовательно соединенных диода 4, 5, а второй конденсатор 6 включен между общей точкой соединения диодов 4, 5 и входом емкостного накопителя 1, ключевой транзистор 7, эмиттер которого соединен с общей щиной устройства, коллектор, через который резистор 8 соединен с шиной питания, база через третий резистор 9 - с шиной управления, п коммутирующих каскадов, вход питания каждого из которых соединен с шиной питания, выход каждого из которых соединен с входом последующего, а выход последнего - с входом емкостного накопителя 1, а вход первого - с коллектором ключевого транзистора 7. Коммутирующий каскад 10 содержит коммутирующий транзистор 11, коллектор которого соединен с выходом его, а через четвертый резистор 12 - с входом питания, база через пятый резистор 13 - с общей шиной, соединенной через третий диод 14 с эмиттером коммутирующего транзистора 11, который через третий конденсатор 15 соединен с входом коммутирующего каскада.

Устройство работает следующим образом при включении одного коммутирующего каскада 10 (фиг. 2).

В исходном состоянии транзисторы 7 и 11 закрыты. Конденсаторы 6, 15 заряжены до напряжения источника питания. Конденсатор 2 разряжен. При поступлении на вход импульсов положительной полярности транзистор 7 открывается. Потенциал его коллектора становится близким к нулю, а потенциал эмиттера транзистора 11 - отрицательным относительно общей щины. Это вызывает протекание базового тока через транзистор 11, приводящий к его насыщению т. е. появлению отрицательного потенциала на верхней обкладке конденсатора 6, а следовательно, двойного напряжения питания на нижней обкладке этого конденсатора относительно общей точки. Данное напряжение через диод 4 передается на накопительный конденсатор 2.

Поскольку в этой схеме в отличие от

5 схемы прототипа возможно накопление напряжения, по величине сравнимого с напряжением питания, то линейное изменение накапливаемого напряжения у предлагаемого интегратора значительно больще. Это

Q позволяет повысить точность срабатывания схемы при использовании ее, например, совместно с пороговым устройством.

В общем случае для заданной точности интегрирования количество коммутирующих каскадов может быть Л. В практических

5 схемах, как правило, (электрическая схема устройства для данного исполнения приведена на фиг. 1 и работа ее аналогична работе однокаскадной схемы).

Отличительные особенности устройства сводятся к повышению точности и расширению пределов интегрирования, что достигается за счет умножения напряжения на накопительном конденсаторе.

При одинаковых накопленных напряжениях устройство более точно отрабатывает команду исполнения, а при сохранении точности позволяет накопить большее количество импульсов, т. е. имеет более широкие по сравнению с прототипом пределы интегрирования.

| Справочник по радиоэлектронике | |||

| Под ред | |||

| Куликовского | |||

| Т | |||

| I, М., 1967, с | |||

| РАСПРЕДЕЛИТЕЛЬНЫЙ МЕХАНИЗМ ДЛЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО ГОРЕНИЯ | 1922 |

|

SU606A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Брагин А | |||

| А | |||

| и др | |||

| Аналоговые преобразователи импульсных потоков | |||

| М.: Атомиздат, 1969, с | |||

| Говорящий кинематограф | 1920 |

|

SU111A1 |

Авторы

Даты

1985-08-15—Публикация

1984-01-04—Подача