vj

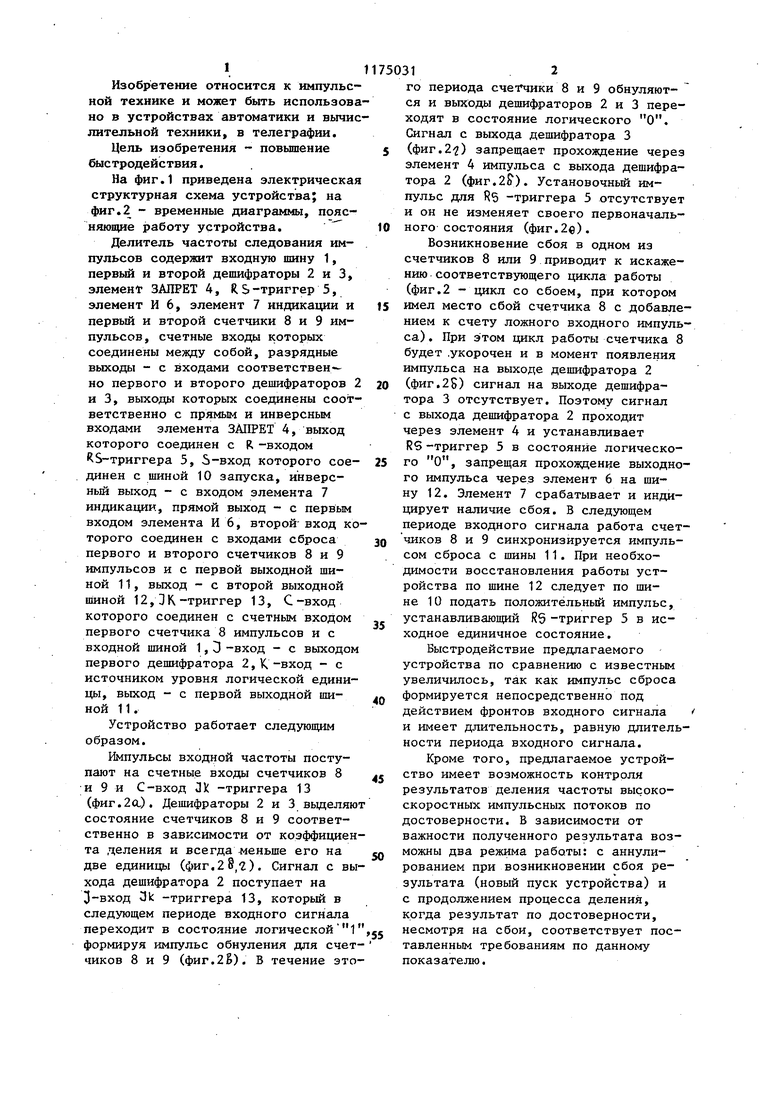

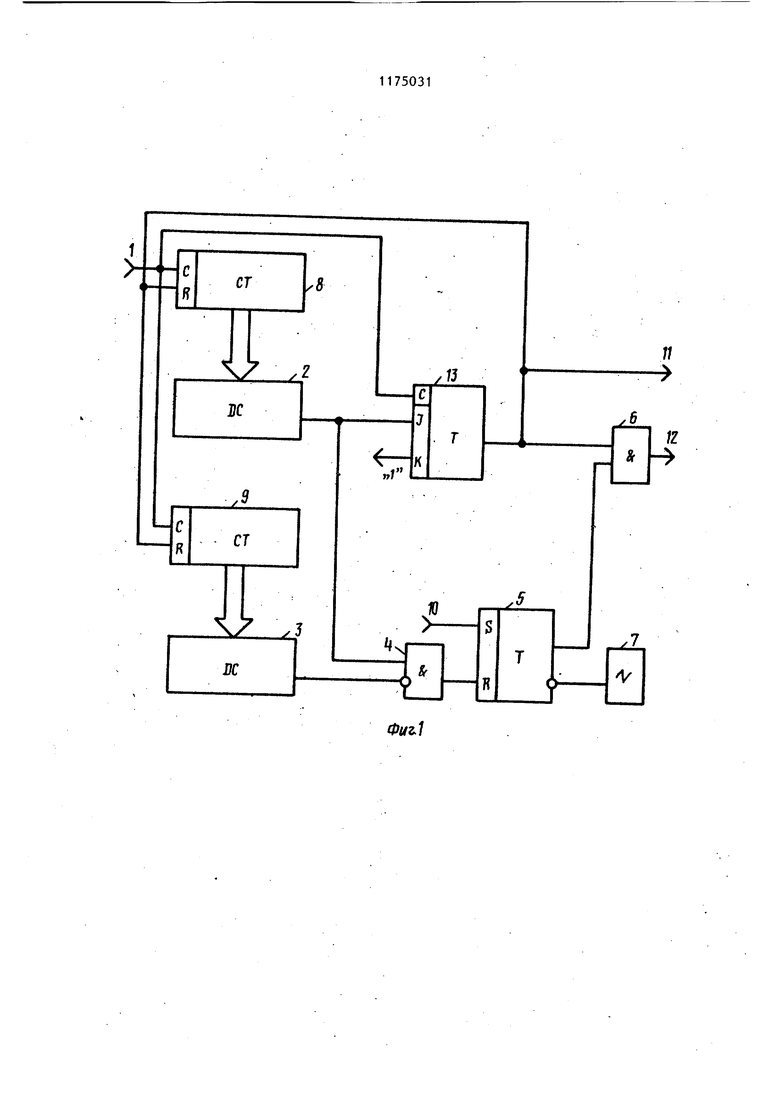

О 00 1 Изобретение относится к импульс ной технике и может быть использов но в устройствах автоматики и вычи лительной техники, в телеграфии. Цель изобретения - повышение быстродействия. На фиг.1 приведена электрическа структурная схема устройства; на фиг.2 - временные диаграммы, поясняющие работу устройства. Делитель частоты следования импульсов содержит входную шину 1, первый и второй дешифраторы 2 и 3, элемен ЗАПРЕТ 4, R S -триггер 5, элемент И 6, элемент 7 индикации и первый и второй счетчики 8 и 9 импульсов, счетные входы которых соединены между собой, разрядные выходы - с входами соответствен но первого и второго дешифраторов и 3, выходы которых соединены соот ветственно с прямым и инверсным входами элемента ЗАПРЕТ 4, выход которого соединен с R -входом S-триггера 5, S-вход которого сое динен с шиной 10 запуска, инверсный выход - с входом элемента 7 индикации, прямой выход - с первым входом элемента И 6, второй- вход к торого соединен с входами сброса первого и второго счетчиков 8 и 9 импульсов и с первой выходной шиной 11, выход - с второй выходной 1ПИНОЙ 12, Dк-триггер 13, С-вход которого соединен с счетным входом первого счетчика 8 импульсов и с входной шиной 1,3 -вход - с выходо первого дешифратора 2,К -вход - с источником уровня логической едини цы, выход - с первой выходной шиной 11. Устройство работает следующим образом. Импульсы входной частоты поступают на счетные входы счетчиков 8 и 9 и С-вход JK -триггера 13 (фиг.2и,). Дешифраторы 2 и 3 вьщеля состояние счетчиков 8 и 9 соответственно в зависимости от коэффицие та деления и всегда меньше его на две единицы (фиг.28д). Сигнал с в хода дешифратора 2 поступает на 3-вход 3k -триггера 13, который в следующем периоде входного сигнала переходит в состояние логической формируя импульс обнуления для сче чиков 8 и 9 (фиг.2§). В течение эт 12 го периода счегчики 8 и 9 обнуляются и выходы дешифраторов 2 и 3 переходят в состояние логического О. Сигнал с выхода дешифратора 3 (фиг.22) запрещает прохождение через элемент 4 импульса с выхода дешифратора 2 (фиг.2). Установочный импульс для R5 -триггера 5 отсутствует и он не изменяет своего первоначального состояния (фиг.2€). Возникновение сбоя в одном из счетчиков 8 или 9 приводит к искажению- соответствзтощего цикла работы (фиг.2 - цикл со сбоем, при котором имел место сбой сче;тчика 8 с добавлением к счету ложного входного импульса) . При этом цикл работы счетчика 8 будет .укорочен и в момент появления импульса на выходе дешифратора 2 (фиг.25) сигнал на выходе дешифратора 3 отсутствует. Поэтому сигнал с выхода дешифратора 2 проходит через элемент 4 и устанавливает RS -триггер 5 в состояние логического О, запрещая прохождение выходного импульса через элемент 6 на шину 12. Элемент 7 срабатывает и индицирует наличие сбоя. В следующем периоде входного сигнала работа счетчиков 8 и 9 синхронизируется импульсом сброса с шины 11. При необходимости восстановления работы устройства по шине 12 следует по шине 10 подать положительный импульс, устанавливающий R5 -триггер 5 в исходное единичное состояние. Быстродействие предлагаемого устройства по сравнению с известным увеличилось, так как импульс сброса формируется непосредственно под действием фронтов входного сигнала и имеет длительность, равную длительности периода входного сигнала. Кроме того, предлагаемое устройство имеет возможность контроля результатов деления частоты высокоскоростных импульсных потоков по достоверности. В зависимости от важности полученного результата возможны два режима работы: с аннулированием при возникновении сбоя результата (новый пуск устройства) и с продолжением процесса деления, когда результат по достоверности, несмотря на сбои, соответствует поставленным требованиям по данному показателю.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с целочисленным коэффициентом деления | 1983 |

|

SU1095414A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Счетчик импульсов с цифровой индикацией | 1984 |

|

SU1231602A1 |

| ИМИТАТОР ИР-60-500 ДЛЯ ОТЛАДКИ КОРАБЕЛЬНЫХ ЦИФРОВЫХ УПРАВЛЯЮЩИХ СИСТЕМ | 1998 |

|

RU2138846C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УРОВНЯ НАПРЯЖЕНИЯ | 1990 |

|

RU2018140C1 |

| Устройство для счета импульсов | 1985 |

|

SU1275760A1 |

| Вторичные кварцевые часы для синхронизации генератора псевдослучайной последовательности | 1991 |

|

SU1835532A1 |

| Делитель частоты следования импульсов | 1986 |

|

SU1378054A1 |

| Устройство для контроля цифровых сигналов | 1981 |

|

SU1032428A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий входную шину, -первый и второй дешифраторы, элемент ЗАПРЕТ, RS-триггер, элемент И, элемент индикации и первый и второй счетчики импульсов, счетные входы которых соединены между собой, разрядные выходы - с входами соот- ; ветственно первого и второго дешифраторов, выходы которых соединены соответственно с прямым и инверсным , входами элемента ЗАПРЕТ, выход кото: рого соединен с 1 -входом R S -триггера, которого соединен с шиной запуска, инверсный выход - с входом элемента индикации, прямой ; выход - с первым входом элемента И, второй вход которого соединен с входами сброса первого и второго счетчиков импульсов и с первой выходной шиной, выход - с второй выходной шиной, отличающийся тем, что, с целью повьш1ения быстродействия, в него введен 3 К-триггер, i С-вход которого соединен со счетным входом первого счетчика и мпульсов и (Л с входной шиной, 3 -вход - с выходом первого депшфратора К -вход - с источником уровня логической единицы, выход - с первой выходной шиной.

| Делитель частоты с любым целочисленным коэффициентом деления | 1976 |

|

SU624371A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-23—Публикация

1984-03-23—Подача