Изобретение относится к вычислительной технике и дискретной автоматике и может быть использовано при построении аппаратурных средств контроля и диагностики дискретных блоков на этапах выходного контроля, а также при эксплуатации.

Цель изобретения - повышение достоверности контроля.

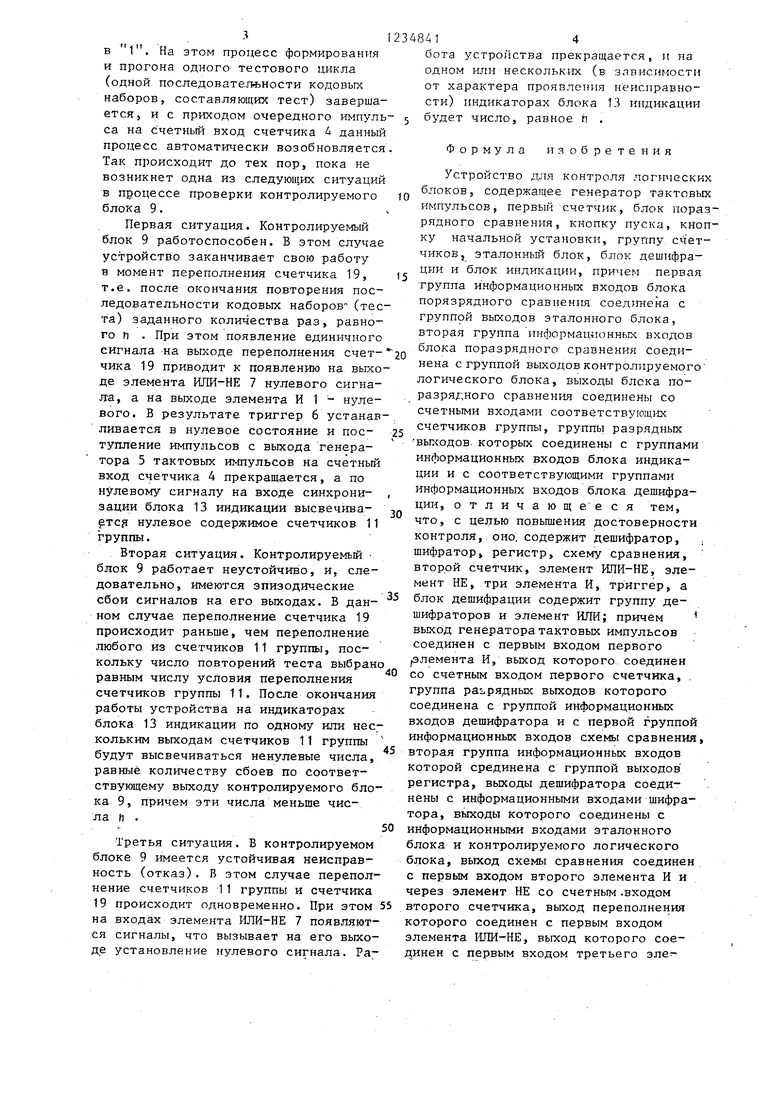

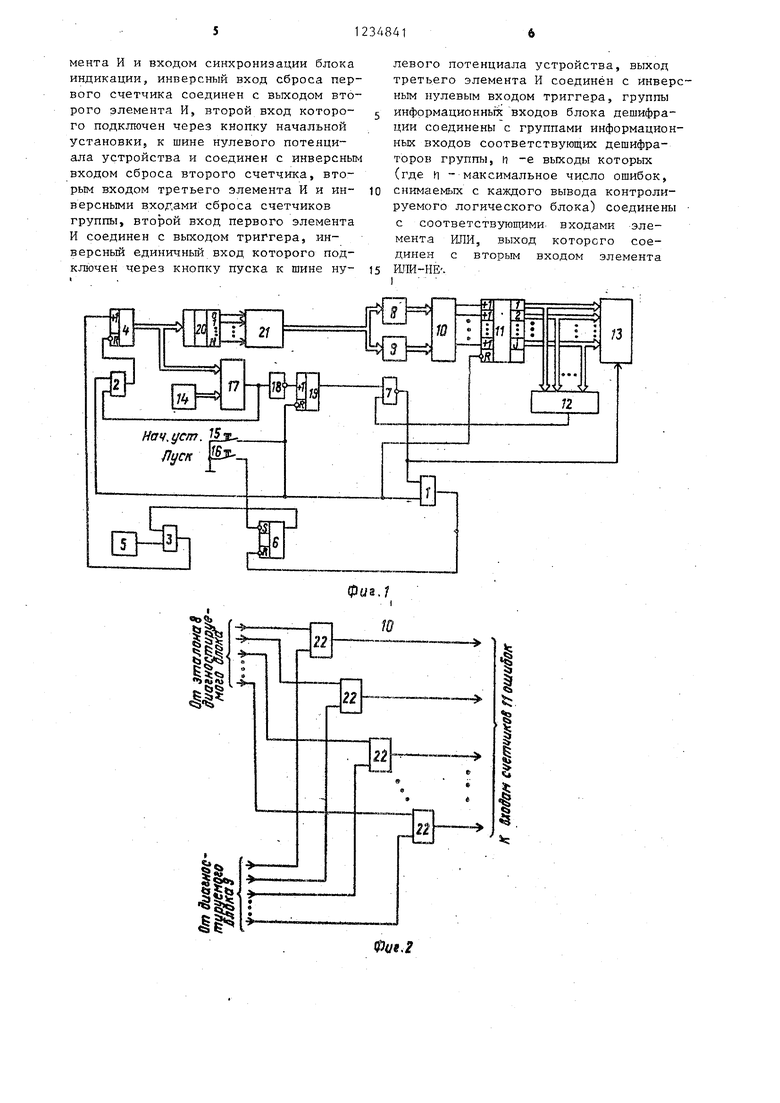

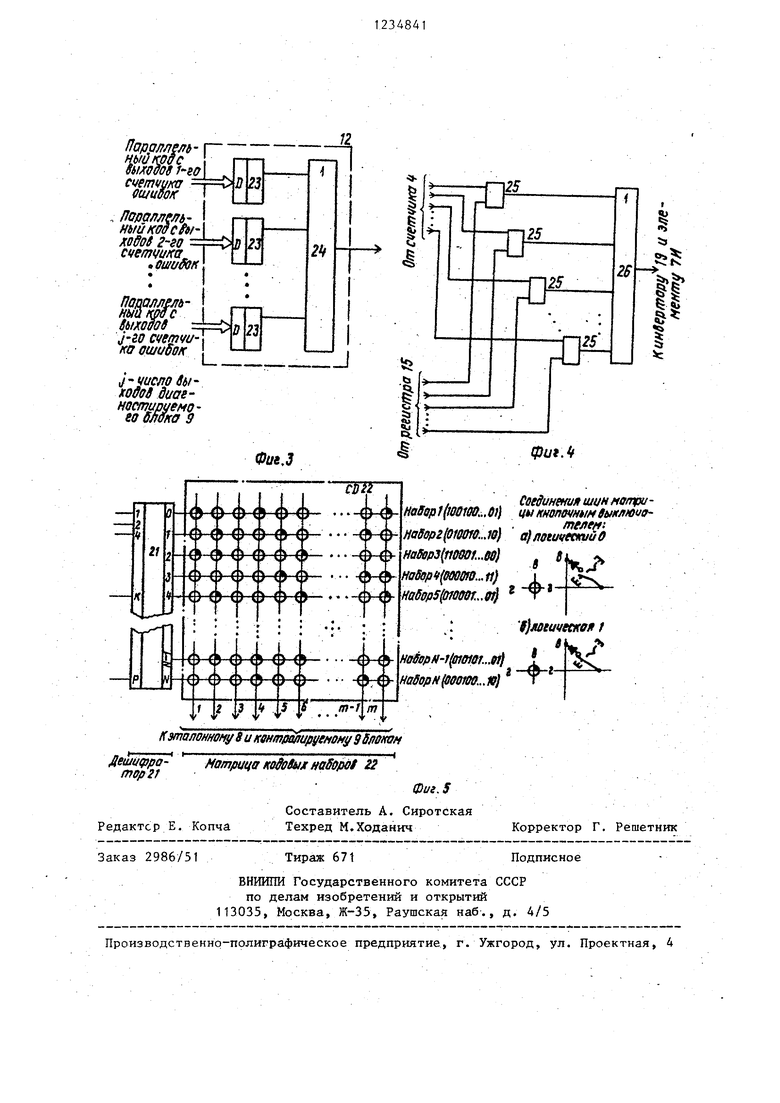

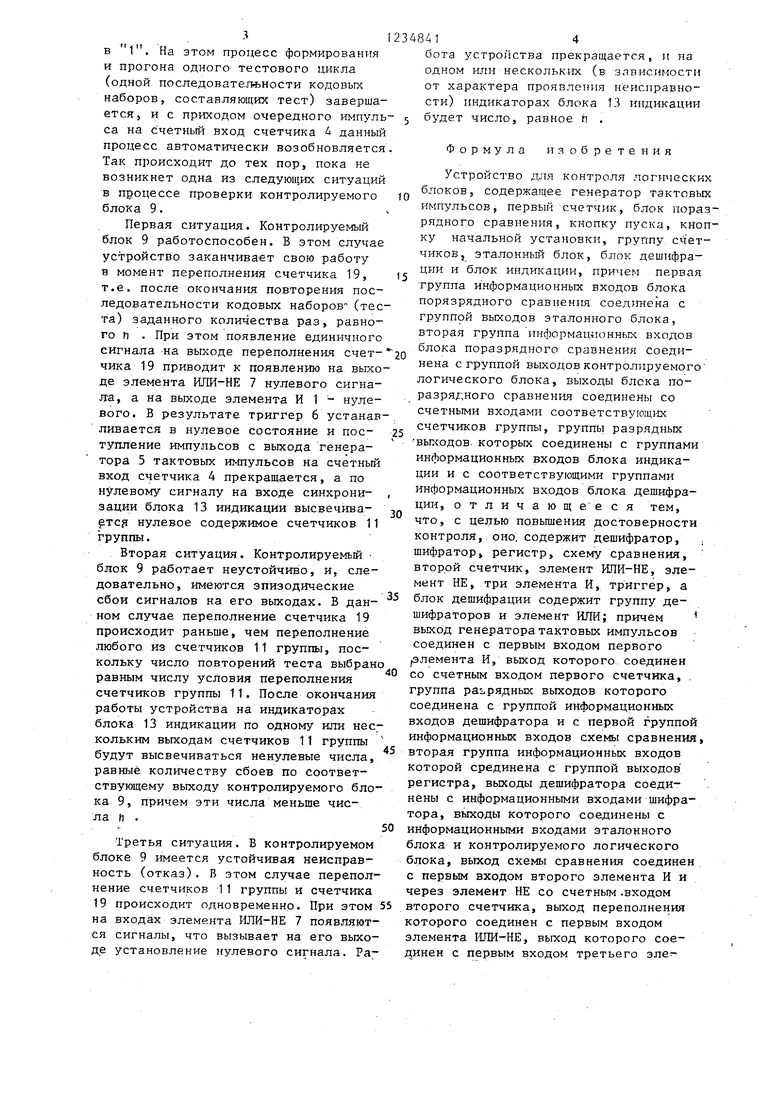

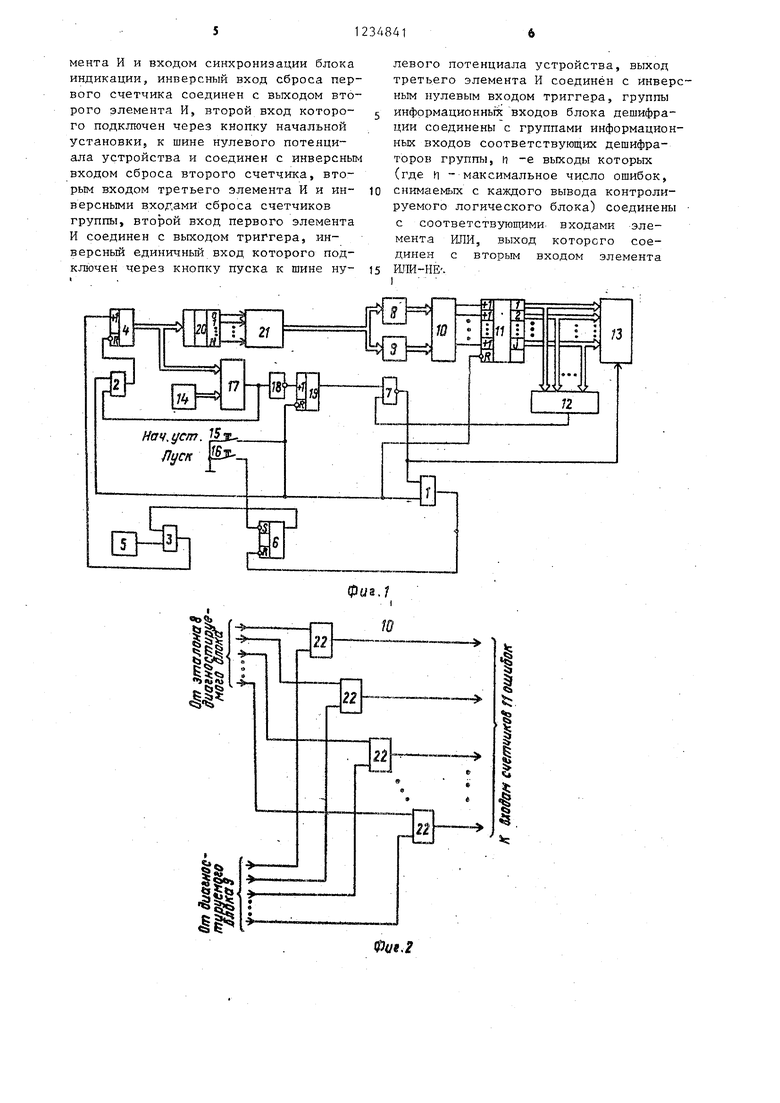

На фиг. 1 изображена функциональная блок-схема устройства на фиг. 2- блок поразрядного сравнения; на фиг. 3 блок дешифрации; на фиг. 4 - схема сравнения; на фиг. 5 - шифратор.

Устройство (фиг. 1) содержит элементы И 1-3, счетчик 4, генератор 5 тактовых импульсов, триггер б, элемент ИЛИ-НЕ 7, эталонный блок 8,, контролируемый Логический,блок 9, блок 10 поразрядного сравнения, группу счетчиков 11, блок 12 дешифрации, блок 13 индикации, регистр 14, кнопку 15 начальной установки, кнопку 16 .пуска, схему 17 сравнения, элемент НЕ 18, Счетчик 19, дешифратор 20, шифратор 21.

Блок поразрядного сравнения (фиг. 2) содержит группу-сумматоров 22 по модулю два.

Блок дешифрации (фиг. 3) содержит группу дешифраторов 23, элемент ИЛИ 24.

Схема сравнения (фиг. 4) содержит группу сумматоров 25 по модулю два, элемент ИЛИ 26.

ydTpoftcTBo работает следующим образом.

При замыкании контактов кнопки 15 начальной установки сигнал логического нуля поступает на инверсные, входы сброса счетчиков 11 группы, счетчика 19, а также через элементы И 1 и 2 - соответственно на .инверсный вход триггера 6 и инверсшэтй вход сброса счетчика 4. Установка в нуль указанных элементов определяет исходное состояние устройства, при котором за счет исключен.ия возможности прохождения импульсов генератора 5 такто- .вых импульсов на счетный вход счетчика 4 отсутствует динамическое изменение сигналов во всех точках-устройства. Перед началом работы устройства в регистр 14 заносится код напере заданного числа, определяющего количество тестовых наборов в тесте контролируемого логического блока 9, а на наборном поле 1 :ифратора (фиг. 5)

5

0

5

0

5

0

5

0

5

вручную устанавливаются эти наборы в том порядке их последующего считывания, который также определяется тестом контролируемого логического блока 9.

Процесс испытания контролируемого логического блока 9 начинается в момент замыкания контактов кнопки 16 пуска. При этом сигналом логического нуля триггер 6 переводится в единичное состояние, открывается элемент И 3, и непрерывная последовательность импульсов с выхода генератора 5 тактовых импульсов поступает на счетный вход счетчика 4. Счетчик 4 на своих выходах формирует параллельный код, значенггя которого последовательно меняются. Данный код одновременно поступает на группу вх.одов схемы 1 7 сравнения и группу информационных входов дешифратора 20, который последовательно во времени формирует единичные сигналы возбуждения шифратора 21 (фиг. 5). С выходов последнего тестовые наборы в установленной очередности (в очередности возбуждения шин шифратора) поступают на входы эталонного 8 контролируемого 9 блоков. Результаты поразрядных сравнений выходных реакций блоков 8 и 9, фор- мируеиь1е блоком 10 поразрядного сравнения (фиг. 2), накапливаются в счетчиках 11 группы. При этом накапливаемая информация в каждом отдельном счетчике группы снимается и в виде параллельного двоичного кода подается на.соответствующие группы информационных входов блока 13 индикации и соответствующие входы блока. 12 дешифрации. В момент поступления на счетный вход счетчика 4 количества импульсов, равного заданному количеству тестовых наборов в тесте контролируемого блока 95 происходит сравнение кодов на всех входах схемы 17 сравнения, что вызывает появление сигнала логического нуля на его выходе-. Последнее приводит к возникновению положительного перепада сигнала (пе-. реход из О в 1) на счетном входе счетчика 19 и, следовательно, содержимое данного счетчика увеличивается на единицу. Одновременно с этим про- ис содит изменение сигнала на выходе элемента И 2 из 1 в О, и счетчик 4 обнуляется, что приводит к несовпадению кодов, которое зафиксирует схема 17 сравнения, и значегп1е ее выходного сигнала изменяется с О

3

в Ч. На этом процесс формирования и прогона одного тестового цикла (одной последоватехньности кодовых наборов, составляющих тест) завершается, и с приходом очередного импульса на счетный вход счетчика данный процесс автоматически возобновляется Так происходит до тех пор, пока не возникнет одна из следующих ситуаций в процессе проверки контролируемого блока 9.

Первая ситуация. Контролируемый блок 9 работоспособен. В этом случае устройство заканчивает свою работу в момент переполнения счетчика 19, т.е. после окончания повторения последовательности кодовых наборов (теста) заданного количества раз, равного м . При этом появление единичного сигнала -на выходе переполнения счетчика 19 приводит к появлению на выходе элемента ИЛИ-НЕ 7 нулевого сигнала, а на выходе элемента И 1 - нулевого. В результате триггер 6 устанав ливается в нулевое состояние и поступление импульсов с выхода генератора 5 тактовых импульсов на счетный вход счетчика 4 прекращается, а по нулевому сигналу на входе синхронизации блока 13 индикации высвечива- тср нулевое содержимое счетчиков 11 группы.

Вторая ситуация. Контролируемьй блок 9 работает неустойчиво, и, следовательно, имеются эпизодические сбои сигналов на его выходах. В данном случае переполнение счетчика 19 происходит раньше, чем переполнение любого из счетчиков It группы, поскольку число повторений теста выбрано равным числу условия переполнения счетчиков группы 11. После окончания работы устройства на индикаторах блока 13 индикации по одному или нескольким выходам счетчиков 11 группы будут высвечиваться ненулевые числа, равные количеству сбоев по соответствующему выходу контролируемого блока 9, причем эти числа меньше чис

Третья ситуация. В контролируемом блоке 9 имеется устойчивая неисправность (отказ). В этом случае переполнение счетчиков 11 группы и счетчика 19 происходит одновременно. При этом на входах элемента ИЛИ-НЕ 7 появляются сигналы, что вызывает на его выходе установление нулевого сигнала. Ра

.

12348А14

бота устройства прекращается, и на одном или нескольких (в зависимости от характера проявления неисправности) индикаторах блока 13 индикации будет число, равное h .

10

15

25

2о.

0

5

30

35

0

5

Формула изобретения

Устройство для контроля логических блоков, содержащее генератор тактовых импульсов, первый счетчик, блок поразрядного сравнения, кнопку пуска, кнопку начальной установки, группу, сч ет- чиков, эталонный блок, блок дешифрации и блок индикации, причем первая труппа информационных входов блока порязрядного сравнения соедтгена с группой выходов эталонного блока, вторая группа информашюнных входов блока поразрядного сравнения соединена с группой выходов контролируемого логического блока, выходы блока поразрядного сравнения соединены со счетными входами соответствующих счетчиков группы, группы разрядных вьпшдов. которых соединены с группами информационных входов блока индикации и с соответствующими группами информационных входов блока дешифрации, отличающе еся тем, что, с целью повьш1ения достоверности контроля, оно, содержит дешифратор, . шифратор, регистр, схему сравнения, второй счетчик, элемент ИЛИ-НЕ, элемент НЕ, три элемента И, триггер, а блок дешифрации содержит группу дешифраторов и элемент ИЛИ; причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, . группа разрядных выходов которого соединена с группой информационных входов дешифратора и с первой группой информационных входов схемы сравнения, вторая группа информационных входов которой срединена с группой выходов регистра, выходы дешифратора соединены с информационными входами щифра- тора, выходы которого соединены с информационными входами эталонного блока и контролируемого логического блока, выход схемы сравнения соединен с первым входом второго элемента И и через элемент НЕ со счетным .входом второго счетчика, выход переполнения которого соединен с первым входом элемента 11ЛИ-НЕ, выход которого сое- ;5инен с первым входом третьего элегмента И и входом синхронизации блока индикации, инверсный вход сброса первого счетчика соединен с выходом второго элемента И, второй вход которого подключен через кнопку начальной установки, к шине нулевого потенциала устройства и соединен с инверсным входом сброса второго счетчика, вторым входом третьего элемента И и инверсными входами сброса счетчиков группы, второй вход первого элемента И соединен с выходом триггера, инверсный единичный вход которого подключен через кнопку пуска к шине ну

левого потенциала устройства, выход третьего элемента И соединён с инверсным нулевым входом триггера, группы информационньгх входов блока дешифрации соединены с группами информационных входов соответствующих дешифраторов группы, и -е выходы которых (где и - максимальное число ошибок, снимаем1)1х с каждого вывода контролируемого логического блока) соединены с соответствующими, входами элемента ИЛИ, выход которого соединен с вторым входом элемента ИЛИ-НЕ . 1

На Ч, уст. |jE- Луск РЕ--,

L

Г-, Чп

THTI

Г

lid

;з

11

фуэ.

Фи.З

к эталонному S и кантрадируемомуЗВовмм

Дешифра- mop2f

Матрица HaSoiiOi 22

Редактор Е. Копча

Составитель А. Сиротская Техред М.Ходанич

Заказ 2986/51

Тираж 67t

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг Л

.Соединения шин fiomfyjНваврцЮ01№,.01} цы KNOnWHUH выкяючу o8opZ imw.JQ) a}notwetmuO

HaSep3(nOSQt.M HaBoft4(sosm...n} Ha6opS(DfO(Hff,,,fft

fjjiffeweorfff f

HaSof)-i(tnmi.,№ll HaSoflft(oeom.

:; -tФиг. 5

Корректор Г, Решетник

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля распределителя | 1982 |

|

SU1111178A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

Изобретение .относится к вычислительной технике и может быть использовано при тестовой диагностике логических блоков, С целью повышения достоверности контроля оно содержит генератор тактовых импульсов, сиргхро- низирующий работу устройства, триггер, который задает рабочий интервал времени , счетчик, дешифратор и шифратор, участвующие в формировании тестов. регистр, который хранит информацию о последующем тесте, схему сравнения, которая фиксирует момент совпадения данных с регистра и со счетч11ка и запрещает дальнейшее формирование тестов. Диагностирование логического блока происходит традиционно - путем .сравнения реакции с эталоном на каждом выходе в блоке сравнения. Если на каком-либо выводе контролируемого логического блока обнаружен сбой (или сбои), на каждом выводе логического блока это будет зафиксировано счетчиками группы, показания счетчиков выводятся на индикацию в моменты, определяемые схемой сравнения или блоком дешифрации. Последняя содержит дешифраторы группы, каждый из которых служит для выявления ситуации переполнения счетчиков группы . Эти сигналы с дешифраторов поступают на элемент ИЛИ, через который и происходит сброс триггера, вьшвления показаний счетчиков группы и начального сброса счетчика и счетчиков группы, 5 ил. ш (Л ю со 4 00

| Устройство для диагностики неисправностей в логических схемах | 1975 |

|

SU548862A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для диагностики дискретных блоков | 1974 |

|

SU627479A1 |

Авторы

Даты

1986-05-30—Публикация

1984-12-25—Подача