Изобретение относится к вычислительной технике и может быть использовано при разработке микроэвм или ЭВМ других классов с полупроводниковой оперативной памятью.

Целью изобретения является повышение надежности работы загрузчика за счет выработки сигнала сброса при вводе произвольного объема информации.

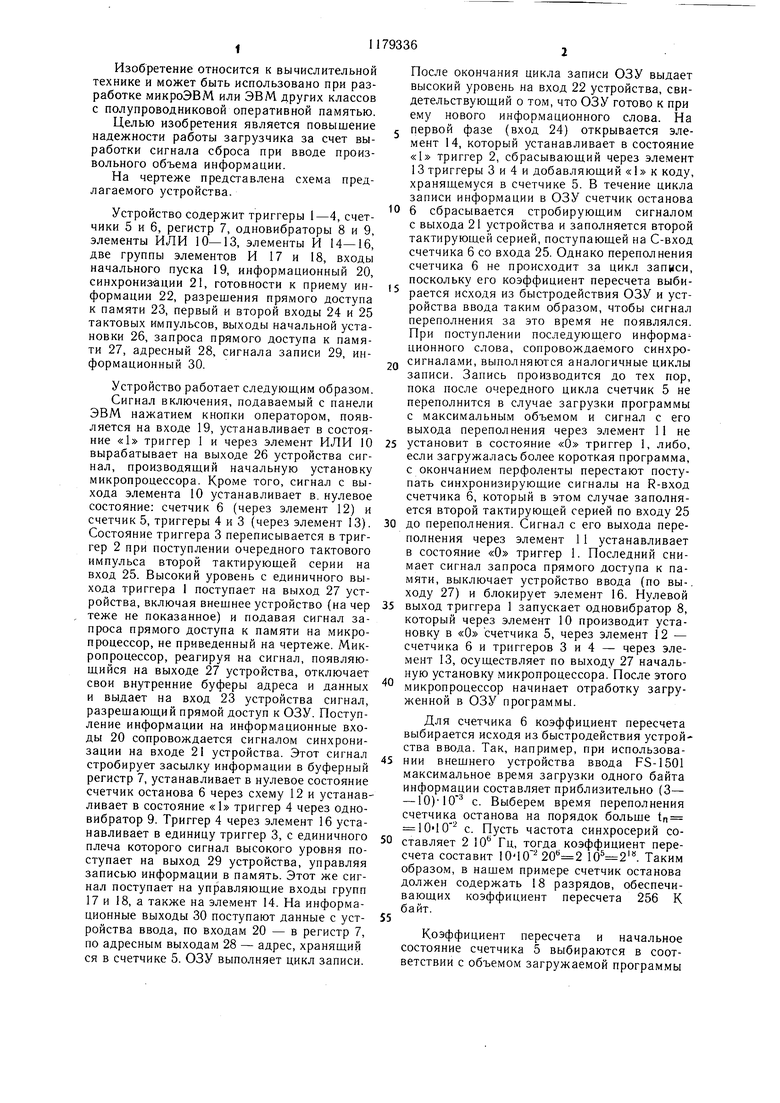

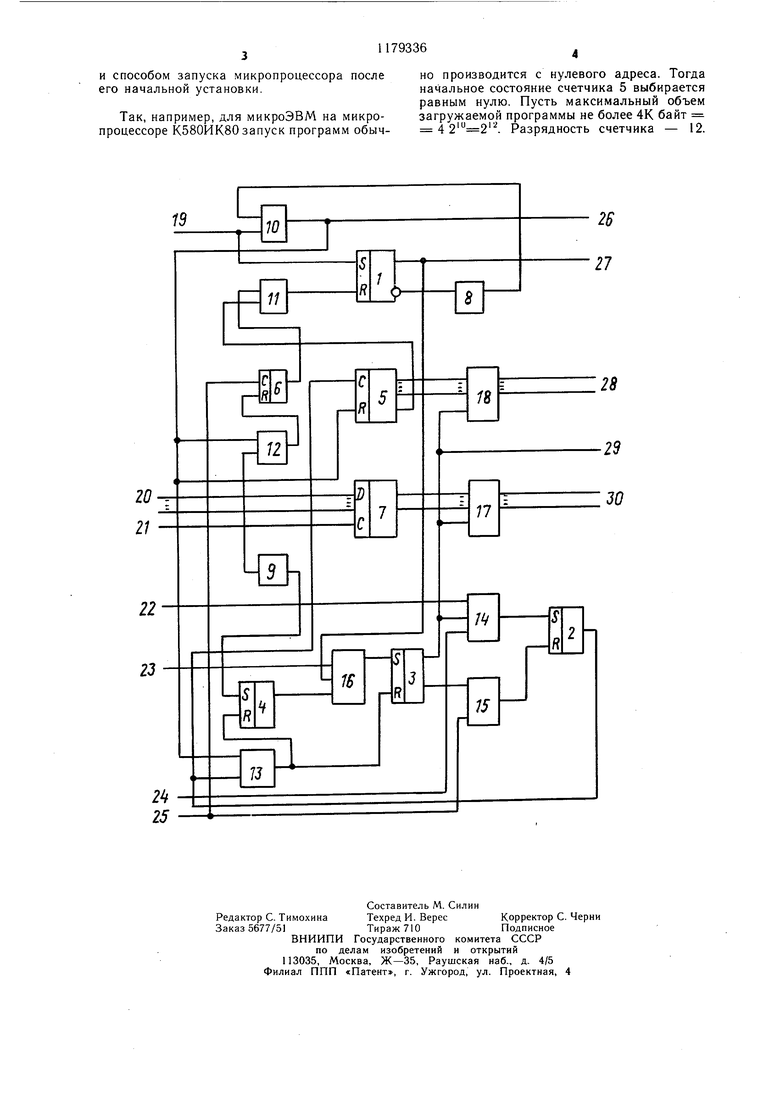

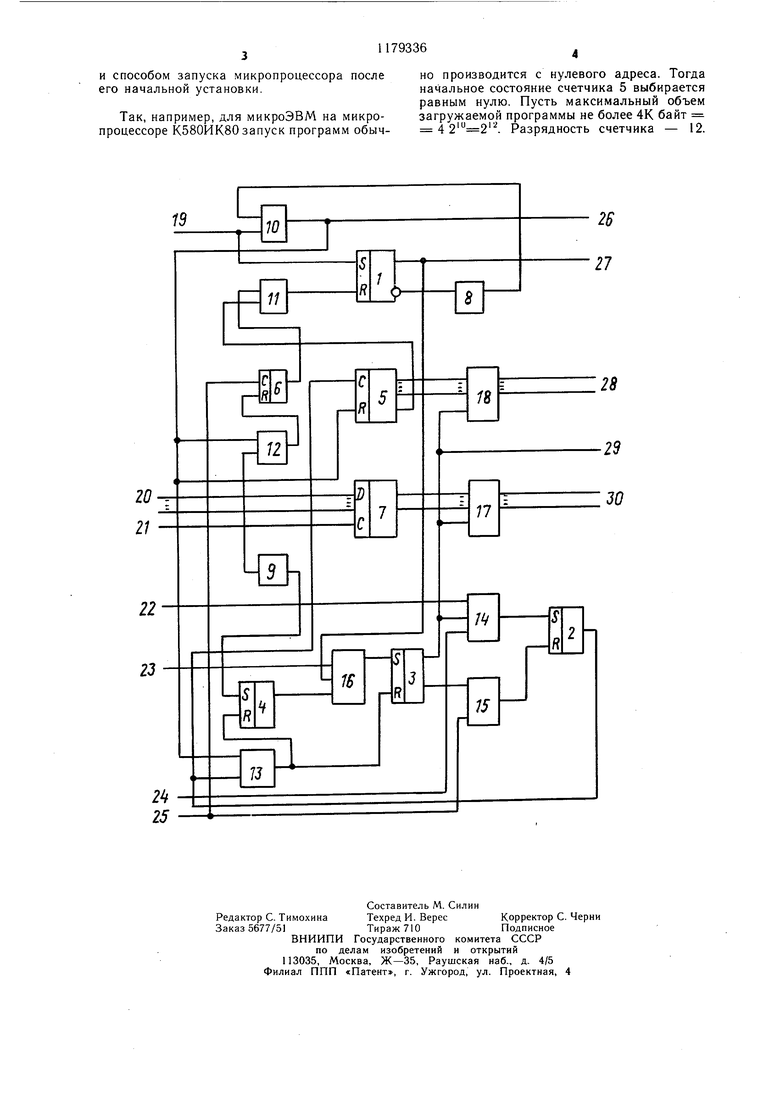

На чертеже представлена схема предлагаемого устройства.

Устройство содержит триггеры 1-4, счетчики 5 и 6, регистр 7, одновибраторы 8 и 9, элементы ИЛИ 10-13, элементы И 14-16, две группы элементов И 17 и 18, входы начального пуска 19, информационный 20, синхрониз-ации 21, готовности к приему информации 22, разрешения прямого доступа к памяти 23, первый и второй входы 24 и 25 тактовых импульсов, выходы начальной установки 26, запроса прямого доступа к памяти 27, адресный 28, сигнала записи 29, информационный 30.

Устройство работает следуюшим образом.

Сигнал включения, подаваемый с панели ЭВМ нажатием кнопки оператором, появляется на входе 19, устанавливает в состояние «1 триггер 1 и через элемент ИЛИ 10 вырабатывает на выходе 26 устройства сигнал, производяш,ий начальную установку микропроцессора. Кроме того, сигнал с выхода элемента 10 устанавливает в. нулевое состояние: счетчик 6 (через элемент 12) и счетчик 5, триггеры 4 и 3 (через элемент 13). Состояние триггера 3 переписывается в триггер 2 при поступлении очередного тактового импульса второй тактируюш,ей серии на вход 25. Высокий уровень с единичного выхода триггера 1 поступает на выход 27 устройства, включая внешнее устройство (на чер теже не показанное) и подавая сигнал запроса прямого доступа к памяти на микропроцессор, не приведенный на чертеже. Микропроцессор, реагируя на сигнал, появляюшийся на выходе 27 устройства, отключает свои внутренние буферы адреса и данных и выдает на вход 23 устройства сигнал, разрешающий прямой доступ к ОЗУ. Поступление информации на информационные входы 20 сопровождается сигналом синхронизации на входе 21 устройства. Этот сигнал стробирует засылку информации в буферный регистр 7, устанавливает в нулевое состояние счетчик останова 6 через схему 12 и устанавливает в состояние «1 триггер 4 через одновибратор 9. Триггер 4 через элемент 16 устанавливает в единицу триггер 3, с единичного плеча которого сигнал высокого уровня поступает на выход 29 устройства, управляя записью информации в память. Этот же сигнал поступает на управляющие входы групп 17 и 18, а также на элемент 14. На информационные выходы 30 поступают данные с устройства ввода, по входам 20 - в регистр 7, по адресным выходам 28 - адрес, хранящий ся в счетчике 5. ОЗУ выполняет цикл записи.

После окончания цикла записи ОЗУ выдает высокий уровень на вход 22 устройства, свидетельствующий о том, что ОЗУ готово к при ему нового информационного слова. На с первой фазе (вход 24) открывается элемент 14, который устанавливает в состояние «I триггер 2, сбрасывающий через элемент 13 триггеры 3 и 4 и добавляющий «1 к коду, хранящемуся в счетчике 5. В течение цикла записи информации в ОЗУ счетчик останова

0 6 сбрасывается стробирующим сигналом с выхода 21 устройства и заполняется второй тактирующей серией, поступающей на С-вход счетчика 6 со входа 25. Однако переполнения счетчика 6 не происходит за цикл записи, поскольку его коэффициент пересчета выбирается исходя из быстродействия ОЗУ и устройства ввода таким образом, чтобы сигнал переполнения за это время не появлялся. При поступлении последующего информационного слова, сопровождаемого синхроQ сигналами, выполняются аналогичные циклы записи. Запись производится до тех пор, пока после очередного цикла счетчик 5 не переполнится в случае загрузки программы с максимальным объемом и сигнал с его выхода переполнения через элемент 11 не

5 установит в состояние «О триггер 1, либо, если загружалась более короткая программа, с окончанием перфоленты перестают поступать синхронизирующие сигналы на R-вход счетчика 6, который в этом случае заполняется второй тактирующей серией по входу 25

0 до переполнения. Сигнал с его выхода переполнения через элемент 11 устанавливает в состояние «О триггер 1. Последний снимает сигнал запроса прямого доступа к памяти, выключает устройство ввода (по вы-. ходу 27) и блокирует элемент 16. Нулевой

5 выход триггера 1 запускает одновибратор 8, который через элемент 10 производит установку в «О счетчика 5, через элемент 12 - счетчика 6 и триггеров 3 и 4 - через элемент 13, осуществляет по выходу 27 начальную установку микропроцессора. После этого

микропроцессор начинает отработку загруженной в ОЗУ программы.

Для счетчика 6 коэффициент пересчета выбирается исходя из быстродействия устройства ввода. Так, например, при использова5 НИИ внешнего устройства ввода FS-1501 максимальное время загрузки одного байта информации составляет приблизительно (3- -10)-10 с. Выберем время переполнения счетчика останова на порядок больще tn 1010 с. Пусть частота синхросерий составляет 2 10 Гц, тогда коэффициент пересчета составит lOlO . Таким образом, в нашем примере счетчик останова должен содержать 18 разрядов, обеспечивающих коэффициент пересчета 256 К байт.

Коэффициент пересчета и начальное состояние счетчика 5 выбираются в соответствии с объемом загружаемой программы

и способом запуска микропроцессора после его начальной установки.

Так, например, для микроЭВМ на микропроцессоре К580ИК80 запуск программ обычно производится с нулевого адреса. Тогда начальное состояние счетчика 5 выбирается равным нулю. Пусть максимальный объем загружаемой программы не более 4К байт . Разрядность счетчика - 12.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для подсчета минимального значения интенсивности размещения в многопроцессорных кубических циклических системах при однонаправленной передаче информации | 2018 |

|

RU2688236C1 |

| УСТРОЙСТВО ПЛАНИРОВАНИЯ ТОПОЛОГИИ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ | 2012 |

|

RU2530275C2 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1987 |

|

SU1495780A1 |

| Устройство для формирования векторов на газоразрядной индикаторной панели | 1988 |

|

SU1642509A1 |

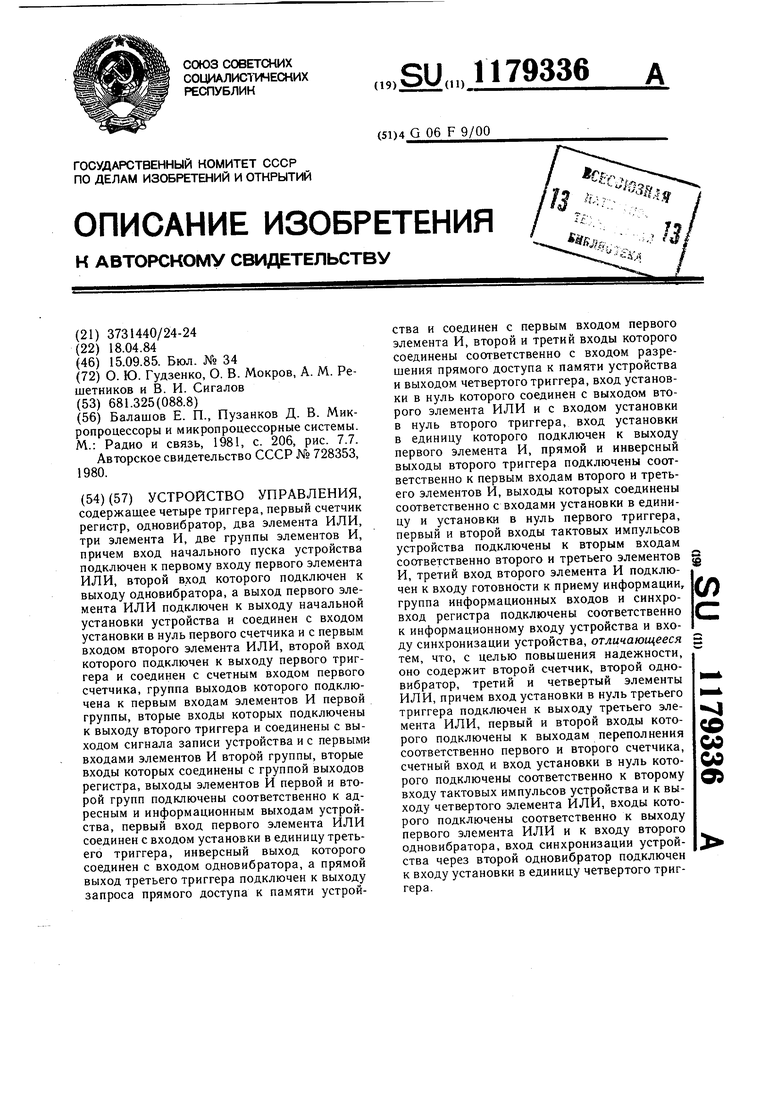

УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее четыре триггера, первый счетчик регистр, одновибратор, два элемента ИЛИ, три элемента И, две группы элементов И, причем вход начального пуска устройства подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу одновибратора, а выход первого элемента ИЛИ подключен к выходу начальной установки устройства и соединен с входом установки в нуль первого счетчика и с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу первого триггера и соединен с счетным входом первого счетчика, группа выходов которого подключена к первым входам элементов И первой группы, вторые входы которых подключены к выходу второго триггера и соединены с выходом сигнала записи устройства и с первыми входами элементов И второй группы, вторые входы которых соединены с группой выходов регистра, выходы элементов И первой и второй групп подключены соответственно к адресным и информационным выходам устройства, первый вход первого элемента ИЛИ соединен с входом установки в единицу третьего триггера, инверсный выход которого соединен с входом одновибратора, а прямой выход третьего триггера подключен к выходу запроса прямого доступа к памяти устройства и соединен с первым входом первого элемента И, второй и третий входы которого соединены соответственно с входом разрешения прямого доступа к памяти устройства и выходом четвертого триггера, вход установки в нуль которого соединен с выходом второго элемента ИЛИ и с входом установки в нуль второго триггера, вход установки в единицу которого подключен к выходу первого элемента И, прямой и инверсный выходы второго триггера подключены соответственно к первым входам второго и третьего элементов И, выходы которых соединены соответственно с входами установки в единицу и установки в нуль первого триггера, первый и второй входы тактовых импульсов устройства подключены к вторым входам соответственно второго и третьего элементов И, третий вход второго элемента И подклю(Л чен к входу готовности к приему информации, группа информационных входов и синхровход регистра подключены соответственно к информационному входу устройства н входу синхронизации устройства, отличающееся тем, что, с целью повышения надежности, оно содержит второй счетчик, второй одновибратор, третий и четвертый элементы ИЛИ, причем вход установки в нуль третьего триггера подключен к выходу третьего элемента ИЛИ, первый и второй входы кото со рого подключены к выходам переполнения соответственно первого и второго счетчика, 00 Од счетный вход и вход установки в нуль которого подключены соответственно к второму входу тактовых импульсов устройства и к выходу четвертого элемента ИЛИ, входы которого подключены соответственно к выходу первого элемента ИЛИ и к входу второго одновибратора, вход синхронизации устройства через второй одновибратор подключен к входу установки в единицу четвертого триггера.

| Балашов Е | |||

| П., Пузанков Д | |||

| В | |||

| Микропроцессоры и микропроцессорные системы | |||

| М.: Радио и связь, 1981, с | |||

| Гидравлический способ добычи торфа | 1916 |

|

SU206A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Система регенирации атмосферы автономнойгЕРМОКАбиНы | 1978 |

|

SU728353A1 |

Авторы

Даты

1985-09-15—Публикация

1984-04-18—Подача