Изобретение относится к накоплению информации, а именно к имитаторам сигналов управления позиционированием магнитных головок записи-воспроизведения, и может быть использовано для испытания накопителей на магнитных дисках (НМД).

Известен имитатор сигналов стенда для испытания накопителей на магнитных дисках, содержащий выходную шину, одновибратор, генератор импульсов, входную шину, триггер, счетчик, блок начальной установки [1]. Недостатком этого устройства является узкая область применения, состоящая в невозможности одновременного испытания нескольких накопителей с одновременным контролем их состояния и работоспособности.

Известен имитатор сигналов управления позиционирования магнитных головок относительно магнитных дисков, содержащий генератор импульсов, одновибратор, два счетчика, триггер, блок начальной установки, три элемента И-НЕ, группу элементов И, элемент НЕ и дешифратор [2]. Недостатком этого устройства является узкая область применения, состоящая в невозможности изменять в зависимости от типа накопителей частоту следования сигналов "Шаг", максимальное число цилиндров (дорожек) на пакете дисков, контролировать состояние накопителей.

Наиболее близким к предлагаемому изобретению по технической сущности и достигаемому положительному эффекту является имитатор сигналов управления позиционированием магнитных головок относительно магнитных дисков, содержащий генератор импульсов, одновибратор, три счетчика импульсов, четыре триггера, группу триггеров, генератор констант, группу регистров, группу одновибраторов, блок постоянной памяти, коммутатор, две группы элементов И, пять элементов И, причем выход одновибратора подключен к счетному входу первого триггера, инверсный выход первого триггера подключен к входной шине направления устройства, выход генератора импульсов подключен к счетному входу второго счетчика, выход одновибратора подключен к прямым входам элементов И первой группы, выходы которых подключены к соответствующим линиям выходной шины "Шаг", линии входной шины сигналов "Индекс" через группу одновибраторов подключены к первым входам элементов И второй группы, к вторым входам которых подключены соответствующие линии входной шины сигналов нулевой дорожки накопителей, выходы второй группы элементов И подключены к входам первого элемента И, выход которого подключен к входу сброса первого, к установочному синхронному второго и синхронизирующим входам второго и третьего триггеров, а также к счетному входу третьего счетчика, линии входной шины готовности накопителей к работе подключены к входам второго элемента И, выход которого подключен к входу генератора импульсов, выходы группы одновибраторов подключены к первой группе входов третьего элемента И, вторая группа входов которой подключена к входной шине "Установка завершена", выход третьего элемента И подключен к единичному асинхронному входу второго триггера, нулевой асинхронный вход которого подключен к синхровходу первого триггера, выход второго триггера подключен к управляющему входу одновибратора, первые информационные выходы генератора констант подсоединены к информационным входам третьего счетчика и первым информационным входам коммутатора, выходы которого подключены к адресным входам блока постоянной памяти, информационные выходы третьего счетчика подключены к вторым информационным входам коммутатора и группы регистров, информационные выходы которой подключены к соответствующим выходным шинам граничной частоты, информационные выходы блока постоянной памяти подключены к информационным входам второго счетчика, выход которого подключен к своему синхровходу и к входу запуска одновибратора, вторая группа выходов генератора констант подключена к информационным входам первого счетчика, второй выход которого подключен к синхронным установочным входам группы триггеров, прямые выходы триггеров которой подключены к синхровходам соответствующих регистров группы, к инверсным входам соответствующих элементов И первой группы и к входам четвертого элемента И, выход четвертого элемента И подключен к асинхронному входу сброса третьего триггера, инверсный выход которого подсоединен к входам установки в нуль третьего счетчика и группы триггеров, прямой выход третьего триггера подсоединен к входу сброса четвертого триггера и к первому входу пятого элемента И, выход которого подключен к управляющему входу коммутатора, прямой выход первого триггера подключен к синхровходу первого счетчика и к второму входу пятого элемента И, выход четвертого триггера подключен к синхронному установочному входу третьего триггера, к синхровходу третьего счетчика и к входам сброса группы регистров, установочный вход четвертого триггера является входом установки режима устройства, синхровходы триггеров группы подключены к соответствующим линиям входной шины сигналов нулевой дорожки устройства, информационный вход первого триггера подсоединен к шине логической единицы устройства [3].

Недостатком этого устройства является узкая область применения, что заключается, во-первых, в невозможности одновременно управлять позиционерами магнитных головок накопителей различных типов (по числу цилиндров и частоте следования импульсов "Шаг"), во вторых, в отсутствии возможности контроля времени появления сигналов идентификации состояния контролируемых накопителей и контроля частоты вращения шпинделя дисков накопителей, в третьих, в малой степени автоматизации и гибкости процесса контроля накопителей.

Невозможность одновременного управления позиционерами магнитных головок обусловлена тем, что в устройстве одновременно от блока констант может быть установлена жестко только одна номинальная частота следования импульсов "Шаг" и число цилиндров в накопителях.

Контроль наличия сигналов идентификации состояния накопителей в устройстве производится интегрированно. Отсутствие одного или нескольких сигналов от одного из подключенных накопителей вызовет остановку всего устройства, при этом определить аварийный накопитель устройство не может. Кроме того, устройство контролирует только факт наличия сигналов идентификации состояния, но не учитывает временные границы их появления. Контроль вращения шпинделя накопителей в устройстве-прототипе осуществляется путем перезапуска одновибраторов, длительность импульсов которых равна периоду следования сигналов "Индекс". При этом нет возможности испытывать накопители с различными скоростями вращения шпинделей, так как длительность импульсов одновибраторов установлена жестко, а также не представляется возможность обнаружить накопитель, частота вращения шпинделя которого больше допустимой, что, в свою очередь, приведет к ошибкам записи и чтения информации.

Малая степень автоматизации и отсутствие гибкости процесса испытания накопителей объясняются, во-первых, необходимостью вручную устанавливать в блоке констант номер частоты следования импульсов "Шаг" и максимальное число цилиндров, во-вторых, в отсутствии возможности оперативного изменения программы испытаний и передачи результатов испытаний во внешнюю универсальную ЭВМ, а также отображения текущих результатов испытаний накопителей.

Целью изобретения является расширение области применения устройства путем обеспечения возможности одновременного управления позиционированием магнитных головок накопителей различных типов, контроля наличия и временных границ сигналов о состоянии накопителей и повышения степени автоматизации и гибкости процесса испытания накопителей.

Цель достигается тем, что в имитатор сигналов управления позиционированием магнитных головок относительно магнитных дисков, содержащий генератор импульсов, одновибратор, счетчик, первый, второй, третий и четвертый регистры, первый, второй, третий и четвертый триггеры, блок постоянной памяти, первую и вторую группы из n элементов И (n - число подключенных накопителей), первый, второй, третий, четвертый и пятый элементы И, группу из n входов сигналов "Готовность", группу из n входов сигналов "Нулевая дорожка", группу из n входов сигналов "Установка завершена", группу из n входов сигналов "Шаг", группу из n входов сигналов "Направление", группу из n входов сигналов "Индекс", причем первый выход генератора импульсов соединен со счетным вычитающим входом счетчика импульсов, первый выход которого подключен к его синхровходу, выходы первой группы элементов И подключены к соответствующим линиям выходной шины "Шаг", дополнительно введены шестой элемент И, блок оперативной памяти, микропроцессов, контроллер последовательного интерфейса, программируемый таймер, пятый и шестой триггеры, первый и второй дешифраторы, первый и второй мультиплексоры, первый, второй, третий, четвертый и пятый шинные формирователи, первый и второй элементы ИЛИ, вход начальной установки устройства, вход приема информации, вход запроса на прием информации, группа из n входов сигналов "Ошибка", группа из n входов сигналов "Тип накопителя", вход кода номера накопителя, выход шины индикации, выход передачи информации, выход запроса на передачу информации, причем вход начальной установки устройства через одновибратор соединен с входом начальной установки микропроцессора, второй выход генератора импульсов подключен к синхровходу микропроцессора, первая группа выходов которого через первый шинный формирователь подключена к выходной шине индикации устройства, вторая группа выходов микропроцессора подключена к первой группе адресных входов блока постоянной памяти, четвертый разрядный выход этой группы выходов микропроцессора подсоединен к первому управляющему входу блока постоянной памяти, третья группа выходов микропроцессора подключена к первой группе адресных входов блока оперативной памяти, группа информационных входов-выходов микропроцессора подключена к информационным входам первого регистра, информационные выходы которого подключены к вторым группам адресных входов блоков постоянной и оперативной памяти, первый разрядный выход первого регистра подключен к входу выбора режима контроллера последовательного интерфейса, к первому адресному входу таймера, к первым информационным входам первого дешифратора и второго шинного формирователя, второй разрядный выход первого регистра подключен к второму адресному входу таймера и вторым информационным входам первого и второго элементов И, восьмой разрядный выход первого регистра подключен к вторым входам первого и второго элементов И, к первому входу третьего элемента И и к первому разрешающему входу блока оперативной памяти, четвертый разрядный выход первого регистра подключен к второму входу третьего элемента И, группа информационных выходов блоков постоянной и оперативной памяти подключена к информационным входам контроллера последовательного интерфейса и таймера, к первым входам-выходам третьего шинного формирователя, вторая группа входов-выходов которого подключена к информационным входам-выходам микропроцессора, первая группа входов-выходов четвертого шинного формирователя подключена к информационным входам второго, третьего и четвертого регистров, вторая группа входов-выходов четвертого шинного формирователя подключена к первой группе входов-выходов третьего шинного формирователя, первая, вторая, третья, четвертая и пятая группы из n входов первого мультиплексора являются соответственно группами входов сигналов "Готовность", сигналов "Ошибка", сигналов "Нулевая дорожка", сигналов "Установка завершена", сигналов "Тип накопителя", шестая группа входов первого мультиплексора подключена к выходам второго дешифратора, информационные входы которого являются входами номера накопителя, первый, второй, третий, четвертый, пятый и шестой выходы первого мультиплексора подключены соответственно к первому, второму, третьему, четвертому, шестому и восьмому разрядным входам-выходам первой группы входов четвертого шинного формирователя, выход сигнала чтения микропроцессора подключен к входам чтения контроллера последовательного интерфейса и таймера, к первому входу второй группы входов первого дешифратора, к третьему входу второго шинного формирователя, к входу направления передачи четвертого шинного формирователя и к первым входам первого и второго элементов ИЛИ, выход сигнала записи микропроцессора подключен к входам записи контроллера последовательного интерфейса и таймера, к четвертому информационному входу второго шинного формирователя, к входу управления чтения/записи блока оперативной памяти, к первому входу первой группы входов первого дешифратора, к второму входу второго элемента ИЛИ, выход сигнала разрешения адресации внешней памяти микропроцессора подключен к второму входу первого элемента ИЛИ, выход которого подключен к разрешающему входу третьего шинного формирователя, выход второго элемента ИЛИ подключен к второму разрешающему входу блока оперативной памяти, выход стробирующего сигнала при чтении из внешней памяти микропроцессора подключен к управляющему входу первого регистра и к второму управляющему входу блока постоянной памяти, выход третьего элемента И подключен к разрешающим входам второго и четвертого шинных формирователей, первый выход генератора импульсов подключен к синхровходу контроллера последовательного интерфейса и к синхровходу первого канала таймера, второй выход счетчика подключен к входам синхронизации передачи и приема информации контроллера последовательного интерфейса, к синхровходу третьего канала таймера, первый выход второго шинного формирователя подключен к первому адресному входу первого мультиплексора, к управляющему входу второго регистра и к первому входу четвертого элемента И, второй выход второго шинного формирователя подключен к второму адресному входу первого мультиплексора, к управляющему входу третьего регистра и к второму входу четвертого элемента И, выход которого подключен к управляющему входу пятого регистра, третий выход второго шинного формирователя подключен к управляющему входу первого мультиплексора, четвертый выход второго шинного формирователя подключен к синхровходам второго, третьего и четвертого регистров, разрядные выходы второго регистра подключены к первым входам соответствующих элементов И первой и второй групп соответственно, разрядные выходы третьего регистра подключены к вторым входам соответствующих элементов И второй группы, выходы которой являются соответствующими выходами сигнала "Направление" устройства, информационные выходы четвертого регистра подключены к адресным входам второго мультиплексора, информационные входы которого являются входами сигнала "Индекс" устройства, а выход подключен к синхровходу первого триггера, инверсный выход которого подключен к своему информационному входу, а прямой выход подключен к синхровходу второго триггера и к первому входу пятого элемента И, информационный вход второго триггера подключен к шине логической единицы устройства, а выход подключен к управляющему входу первого канала таймера, первый выход первой группы выходов первого дешифратора подключен к единичному и нулевому установочным входам соответственно третьего и четвертого триггеров, второй выход первой группы выходов первого дешифратора подключен к единичному установочному входу пятого триггера, третий выход первой группы выходов первого дешифратора подключен к входам сброса третьего и пятого триггеров, инверсные выходы которых подключены к входам сброса второго и шестого триггеров соответственно, прямой выход третьего триггера подключен к первому входу пятого шинного формирователя, к разрешающему входу которого подключен выход второй группы выходов первого дешифратора, выход пятого элемента И подключен к синхровходу четвертого триггера, информационный вход которого подключен к шине логической единицы устройства, а выход подсоединен к второму входу пятого шинного формирователя, выход первого канала таймера подключен к второму входу пятого элемента И и к синхровходу третьего триггера, выход второго канала таймера подключен к синхровходу пятого триггера, выход третьего канала таймера подключен к синхровходу своего второго канала, к первому входу шестого элемента И, к синхровходу шестого триггера, информационный вход которого подключен к шине логической единицы, а выход подключен к управляющему входу второго канала таймера и к второму входу шестого элемента И, выход которого подключен к вторым входам всех элементов И первой группы, выход первого элемента И подсоединен к входу выбора корпуса таймера и к вторым входам первой и второй групп входов первого дешифратора, управляющий вход третьего канала которого подсоединен к шине логической единицы устройства, выход второго элемента И подключен к входу выбора корпуса контроллера последовательного интерфейса, выход запроса прерывания которого подключен к одноименному входу микропроцессора, выходы информации и запроса на передачу информации контроллера последовательного интерфейса являются одноименными выходами устройства, входы приема информации и запроса на прием информации контроллера последовательного интерфейса являются одноименными входами устройства, вход начальной установки контроллера последовательного интерфейса подключен к шине логического нуля устройства, первый и второй разрядные входы счетчика подключены к шине логического нуля устройства, а третий и четвертый разрядные входы счетчика подключены к шине логической единицы, первый, второй и третий выходы пятого шинного формирователя подключены соответственно к восьмому, первому и второму разрядным входам третьего шинного формирователя, прямой выход пятого триггера подключен к третьему информационному входу пятого шинного формирователя, информационные входы третьего и пятого триггеров подключены к шине логического нуля устройства.

Сущность изобретения состоит в обеспечении управления позиционированием магнитных головок различных типов, одновременно подключенных к имитатору путем идентификации типа накопителя на каждом цикле испытаний по сигналу "Тип накопителя", и программного задания частоты следования и количества импульсов "Шаг" в пачке, подаваемой на вход управления перемещением привода магнитных головок выбранного накопителя; в обеспечении раздельного для каждого накопителя анализа наличия и времени появления сигналов идентификации состояния путем программной установки временних границ допустимого времени появления этих сигналов с последующим запоминанием факта отсутствия определенного сигнала в заданном временном интервале и исключении соответствующего накопителя из дальнейших испытаний. При этом контроль скорости вращения пакета дисков для каждого накопителя производится на отсутствие выхода этой величины за допустимые границы как в меньшую, так и в большую сторону; в повышении автоматизации и гибкости процесса испытаний подключенных накопителей путем программного изменения алгоритма испытаний и его параметров, а также документирования результатов испытаний за счет обеспечения обмена информацией между имитатором и универсальной миниЭВМ по последовательному интерфейсу и обеспечении передачи текущих результатов испытаний на средства видеоотображения. Сущность изобретения реализуется за счет введения новой совокупности элементов и их связей, определяющих соответствие устройства критерию "новизна".

Введение микропроцессора обеспечивает автоматизацию процесса контроля сигналов о состоянии контролируемых НМД, а также управление работой всех узлов устройства согласно принятому алгоритму испытаний НМД.

Введение трехканального программируемого таймера обеспечивает формирование временных интервалов, соответствующих минимальному и максимальному периодам следования импульсного сигнала "Индекс" НМД, последовательности импульсов с частотой следования сигналов "Шаг" для позиционионирования магнитных головок НМД различных типов путем деления частоты синхроимпульсов на коэффициент, зависящий от типа НМД, и временного интервала, соответствующего заданному числу импульсов "Шаг" в пачке для позиционирования магнитных головок от нулевой дорожки до максимальной и назад.

Введение контроллера последовательного интерфейса обеспечивает подключение устройства к стандартному входу последовательного интерфейса универсальной ЭВМ для передачи последней результатов контроля НМД и задания режима работы устройства путем записи информации о контролируемых НМД и режимах их контроля в блок оперативной памяти устройства.

Введение блока оперативной памяти обеспечивает запись, хранение и чтение исходных данных о типах подключенных НМД, режиме их контроля промежуточных данных контроля и результатов контроля.

Введение новых связей блока постоянной памяти обеспечивает хранение программы работы устройства по контролю НМД. По своей сути этот блок является памятью программ микропроцессора.

Введение новых связей первого регистра обеспечивает адресацию ячеек блока оперативной памяти, а также других элементов памяти устройства, к которым относятся таймер, контроллер интерфейса, второй, третий и четвертый регистры и некоторые другие элементы устройства.

Введение новых связей второго регистра обеспечивает адресацию активного в текущем цикле контроля НМД путем записи в него унитарного кода номера НМД.

Введение новых связей третьего регистра обеспечивает управление направлением движения привода магнитных головок активного НМД путем записи в соответствующий разряд регистра нуля либо единицы, соответствующих движению либо от нулевой дорожки, либо к нулевой.

Введение новых связей четвертого регистра обеспечивает адресацию НМД, для которого производится процедура контроля периода следования сигналов "Индекс", путем записи в регистр двоичного кода номера этого НМД.

Введение новых связей первого триггера обеспечивает формирование импульсов, длительность которых равна периоду следования сигналов "Индекс", контролируемого НМД, а период - в два раза больше.

Введение новых связей второго триггера обеспечивает формирование управляющего сигнала на запуск первого канала таймера для формирования временного интервала для контроля периода следования сигнала "Индекс" контролируемого НМД.

Введение новых связей четвертого триггера обеспечивает формирование результата контроля периода следования сигнала "Индекс" контролируемого НМД.

Введение пятого триггера обеспечивает разблокировку шестого триггера на время формирования пачки импульсов "Шаг", число импульсов в которой равно числу цилиндров НМД.

Введение шестого триггера обеспечивает формирование временного интервала времени, в течение которого выдается пачка импульсов "Шаг" с заданным числом импульсов.

Введение первого мультиплексора, который является шестиканальным, позволяет осуществлять выбор сигналов интентификации состояния контролируемого в текущем цикле контроля НМД.

Введение второго мультиплексора обеспечивает выбор последовательности сигналов "Индекс" контролируемого НМД из числа подключенных к устройству.

Введение первого дешифратора, который является двухканальным, обеспечивает формирование управляющих сигналов для третьего, четвертого и пятого триггеров с целью программного управления микропроцессором процедурами контроля периода следования сигналов "Индекс" и формирования пачек сигнала "Шаг".

Введение второго дешифратора позволяет преобразовать двоичный позиционный код номера подключенного НМД в двоичный унитарный код.

Введение первого шинного формирователя обеспечивает передачу двоично-закодированной текущей информации о текущих результатах контроля на средства видеоотображения (например, матрица светодиодов) от микропроцессора при условии обеспечения нагрузочной способности последнего.

Введение второго шинного формирователя обеспечивает передачу управляющей информации на второй, третий и четвертый регистры, а также на первый мультиплексор только в том случае, если они адресуются микропроцессором в соответствии с программной работой устройства.

Введение третьего шинного формирователя обеспечивает двухсторонний обмен информации между микропроцессором и всеми другими адресуемыми элементами устройства, а также непосредственно с блоками постоянной и оперативной памяти, таймером и контроллером последовательного интерфейса.

Введение четвертого шинного формирователя обеспечивает передачу сигналов идентификации состояния контролируемого НМД на информационные входы микропроцессора и запись микропроцессором во второй, третий и четвертый регистры соответствующих кодов.

Введение пятого шинного формирователя обеспечивает по команде микропроцессора передачу на его информационные входы информации о режимах таймера в результате контроля периода следования сигналов "Индекс".

Введение новых связей первой группы элементов И служит для передачи пачки импульсов "Шаг" только на тот НМД, позиционирование которого должно выполняться в текущем цикле.

Введение новых связей второй группы элементов И служит для передачи сигнала "Направление" только в активный в текущем цикле контроля НМД.

Введение новых связей первого и второго элементов И обеспечивает адресацию микропроцессором таймера и контроллера последовательного интерфейса соответственно.

Введение новых связей третьего элемента и обеспечивает адресацию микропроцессором первого мультиплексора при чтении сигналов идентификации состояния контролируемого НМД, или второго, третьего и четвертого регистров при записи информации в них.

Введение четвертого элемента И обеспечивает адресацию четвертого регистра при записи номера НМД, период следования сигналов "Индекс" которого будет контролироваться.

Введение пятого элемента И обеспечивает переключение четвертого триггера только в том случае, если период следования сигналов "Индекс" контролируемого НМД больше заданного интервала времени, формируемого первым каналом таймера.

Введение шестого элемента И позволяет передавать на выход устройства строго определенное число импульсов "Шаг", соответствующее числу цилиндров контролируемого НМД.

Введение новых связей первого элемента ИЛИ обеспечивает формирование сигнала управления направлением передачи информации через третий шинный формирователь.

Введение новых связей второго элемента ИЛИ обеспечивает формирование разрешающего сигнала для обращения к блоку оперативной памяти, при обращении к нему микропроцессора для записи или чтения информации.

Введение новых связей одновибратора позволяет производить начальную установку микропроцессора.

Введение новых связей счетчика позволяет синхронизировать работу таймера и контроллера последовательного интерфейса.

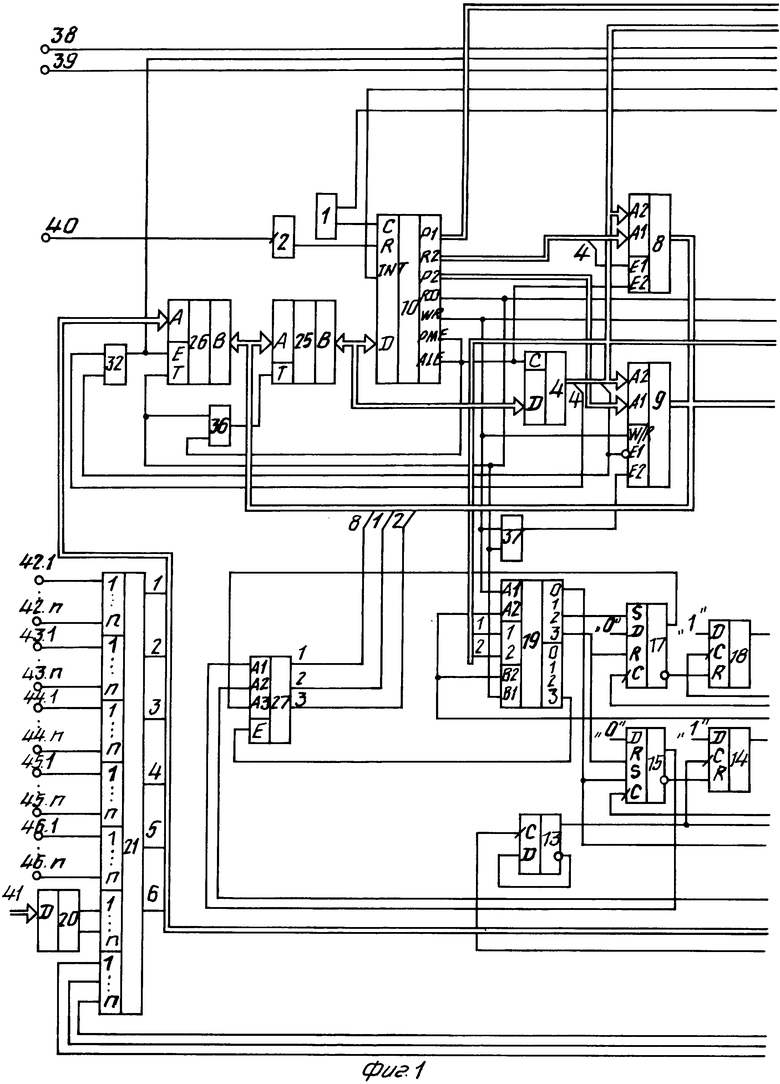

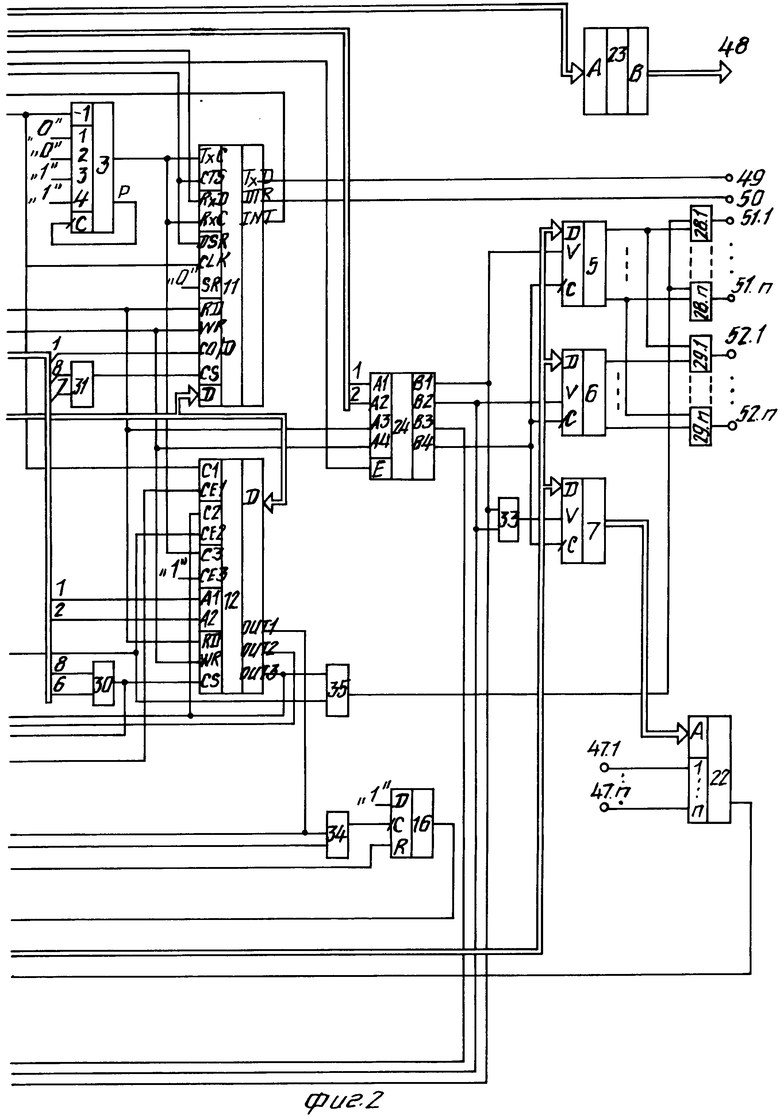

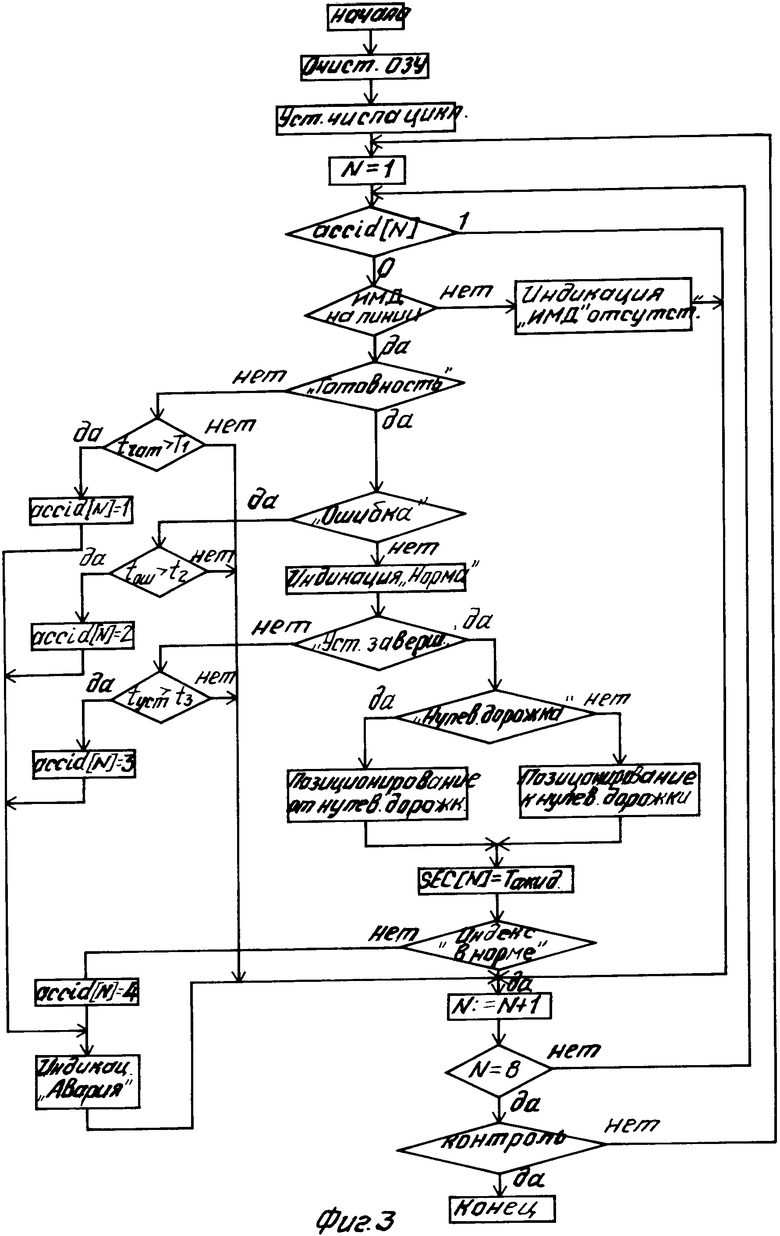

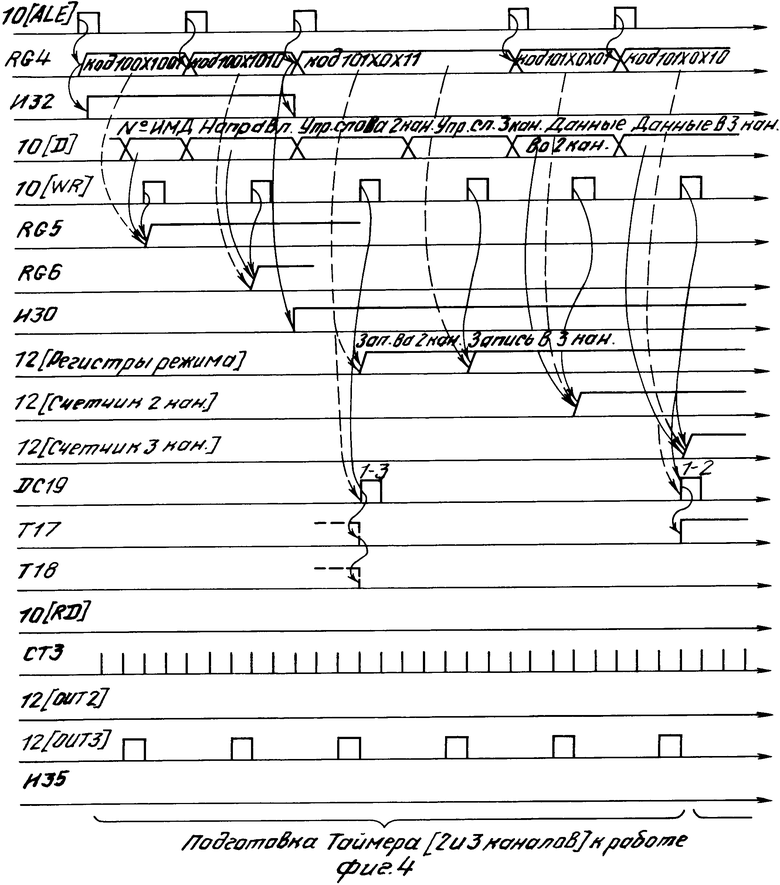

На фиг. 1,2 представлена функциональная схема предложенного устройства; на фиг. 3 представлена граф-схема; на фиг. 4-6 - временные диаграммы работы устройства.

Имитатор сигналов управления позиционированием магнитных головок относительно магнитных дисков содержит генератор 1 импульсов, одновибратор 2, счетчик 3, первый 4, второй 5, третий 6 и четвертый 7 регистры, блок 8 постоянной памяти, блок 9 оперативной памятии, микропроцессор 10, контроллер 11 последовательного интерфейса, программируемый таймер 12, первый 13, второй 14, третий 15, четвертый 16, пятый 17 и шестой 18 триггеры, первый 19 и второй 20 дешифраторы, первый 21 и второй 22 мультиплексоры, первый 23, второй 24, третий 25, четвертый 26 и пятый 27 шинные формирователи, первую 28, вторую 29 группы из n элементов И (n - число подключенных накопителей), первый 30, второй 31, третий 32, четвертый 33, пятый 34, шестой 35 элементы И, первый 36 и второй 37 элементы ИЛИ, вход 38 приема информации, вход 39 запроса на прием информации, вход 40 начальной установки, группу входов 41 кода номера накопителя, группу из n входов 42 сигналов "Готовность", группу из n входов 43 сигналов "Ошибка", группу из n входов 44 сигналов "Нулевая дорожка", группу из n входов 45 сигналов "Установка завершена", группу из n входов 46 сигналов "Тип накопителя", группу из n входов 47 сигналов "Индекс", выход 48 шины индикации, выход 49 передачи информации, выход 50 запроса на передачу информации, n выходов 51 сигналов "Шаг" и n выходов 52 сигналов "Направление".

Первый выход генератора 1 импульсов соединен со счетным вычитающим входом счетчика 3, первый выход которого подключен к его синхровходу. Выходы первой группы элементов И 28.1-28.n подключены к соответствующим выходам 51.1-51.n сигнала "Шаг" устройства.

Вход 40 начальной установки устройства через одновибратор 2 соединен с входом начальной установки микропроцессора 10. Второй выход генератора 1 импульсов подключен к синхровходу С микропроцессора 10, первая группа выходов Р1 которого через первый шинный формирователь 23 подключена к выходной шине 48 индикации устройства. Вторая группа выходов Р2 микропроцессора 10 подключена к первой группе адресных входов А1 блока 8 постоянной памяти, а четвертый разрядный выход второй группы выходов микропроцессора 10 подсоединен к первому управляющему входу Е1 блока 8 постоянной памяти. Третья группа выходов Р3 микропроцессора 10 подключена к первой группе адресных входов А1 блока 9 оперативной памяти. Группа информационных входов-выходов D микропроцессора 10 подключена к информационным входам первого регистра 4.

Группа информационных выходов первого регистра 4 подключена к вторым группам адресных входов А2 блоков постоянной 8 и оперативной 9 памяти. Первый разрядный выход первого регистра 4 подключен к входу выбора режима СО/D контроллера 11 последовательного интерфейса, к первому адресному входу А1 таймера 12, к первым информационным входам первого дешифратора 19 и второго шинного формирователя 24. Второй разрядный выход первого регистра 4 подключен к второму адресному входу таймера 12, к вторым информационным входам первого дешифратора 19 и второго шинного формирователя 24.

Шестой и седьмой разрядные выходы первого регистра 4 подключены к первым входам соответственно первого 30 и второго 31 элементов И. Восьмой разрядный выход первого регистра 4 подключен к вторым входам первого 30 и второго 31 элементов И, к первому входу третьего элемента И 32 и к первому разрешающему входу блока 9 оперативной памяти. Четвертый разрядный выход первого регистра 4 подключен к второму входу третьего элемента И 32.

Группы информационных выходов блоков постоянной 8 и оперативной 9 памяти подключены к информационным входам контроллера 11 последовательного интерфейса и таймера 12, к первым входам-выходам третьего шинного формирователя 25, вторая группа входов-выходов которого подключена к информационным входам-выходам D микропроцессора 10.

Первая группа входов-выходов А четвертого шинного формирователя 26 подключена к информационным входам D второго 5, третьего 6 и четвертого 7 регистров. Вторая группа входов-выходов В четвертого шинного формирователя 26 подключена к первой группе входов-выходов А третьего шинного формирователя 25.

Первая, вторая, третья, четвертая и пятая группы из n входов первого мультиплексора 21 являются соответственно группами входов сигналов "Готовность" 42.1-42.n, сигналов "Ошибка" 43.1-43.n, сигналов "Нулевая дорожка" 44.1-44. n, сигналов "Установка завершена" 45.1-45.n, сигналов "Тип накопителя" 46.1-46.n. Шестая группа входов первого мультиплексора 21 подключена к выходам второго дешифратора 20, информационные входы D которого являются входами 41 номера накопителя. Первый, второй, третий, четвертый, пятый и шестой выходы первого мультиплексора 21 подключены соответственно к первому, второму, третьему, четвертому, шестому и восьмому входам-выходам первой группы входов четвертого шинного формирователя 26. Выход сигнала чтения RD микропроцессора 10 подключен к входам чтения RD контроллера 11

последовательного интерфейса и таймера 12, к первому входу второй группы входов В1 первого дешифратора 19, к третьему входу 3 второго шинного формирователя 24, к входу Т направления четвертого шинного формирователя 26 и к первым входам первого 36 и второго 37 элементов ИЛИ.

Выход сигнала записи WR микропроцессора 10 подключен к входам записи WR контроллера 11 последовательного интерфейса и таймера 12, к четвертому информационному входу А4 второго шинного формирователя 24, к входу управления чтение-запись WR блока 9 оперативной памяти, к первому входу первой группы входов первого дешифратора 19, к второму входу второго элемента ИЛИ 37. Выход сигнала разрешения адресации внешней памяти РМЕ микропроцессора 10 подключен к второму входу первого элемента ИЛИ 36. Выход первого элемента ИЛИ 36 подключен к разрешающему входу Т третьего шинного формирователя 25. Выход второго элемента ИЛИ 37 подключен к второму разрешающему входу Е2 блока 9 оперативной памяти. Выход стробирующего сигнала при чтении из внешней памяти АLE микропроцессора 10 подключен к управляющему входу С первого регистра 4 и к второму управляющему входу Е2 блока 8 постоянной памяти. Выход третьего элемента И 32 подключен к разрешающим входам Е второго 24 и четвертого 26 шинных формирователей.

Первый выход генератора 1 импульсов подключен к синхровходу СLК контроллера 11 последовательного интерфейса и к синхровходу первого канала С1 таймера 12. Второй выход счетчика 3 подключен к входам синхронизации передачи ТхС и приема RxC информации контроллера 11 последовательного интерфейса, к синхровходу третьего канала С3 таймера 12. Первый выход В1 второго шинного формирователя 24 подключен к первому адресному входу А1 первого мультиплексора 21, к управляющему входу V второго регистра 5 и к первому входу четвертого элемента И 33. Второй выход В2 второго шинного формирователя 24 подключен к второму адресному А2 входу первого мультиплексора 21, к управляющему входу V третьего регистра 6 и к второму входу четвертого элемента И 33, выход которого подключен к управляющему входу четвертого регистра 7. Третий выход В3 второго шинного формирователя 24 подключен к управляющему входу первого мультиплексора 21. Четвертый выход В4 второго шинного формирователя 24 подключен к синхровходам второго 5, третьего 6 и четвертого 7 регистров. Разрядные выходы второго регистра 5 подключены к первым входам соответствующих элементов и первой 28 и второй 29 групп соответственно. Разрядные выходы третьего регистра 6 подключены к вторым входам соответствующих элементов И второй группы 29, выходы которой являются соответствующими выходами 52 сигнала "Направление" устройства. Информационные выходы четвертого регистра 7 подключены к адресным входам А второго мультиплексора 22, информационные входы которого являются входами 47 сигнала "Индекс" устройства, а выход подключен к синхровходу С первого триггера 13, инверсный выход которого подключен к своему информационному D входу, а прямой выход подключен к синхровходу С второго триггера 14 и к первому входу пятого элемента И 34. Информационный вход второго триггера 14 подключен к шине логической единицы устройства, а выход подключен к управляющему входу первого канала СЕI таймера 12. Первый выход первой группы выходов первого дешифратора 19 подключен к единичному и нулевому установочным входам соответственно третьего 15 и четвертого 16 триггеров. Второй выход первой группы выходов первого дешифратора 19 подключен к единичному установочному входу пятого триггера 17. Третий выход первой группы выходов первого дешифратора 19 подключен к входам сброса третьего 15 и пятого 17 триггеров, инверсные выходы которых подключены к входам сброса второго 14 и шестого 18 триггеров соответственно. Прямой выход третьего триггера 15 подключен к первому входу пятого шинного формирователя 27, к разрешающему входу которого подключен выход второй группы выходов первого дешифратора 19. Выход пятого элемента И 34 подключен к синхровходу четвертого триггера 16, информационный вход которого подключен к шине логической единицы, а выход подсоединен к второму входу пятого шинного формирователя 27. Выход первого канала OU Т1 таймера 12 подключен к второму входу пятого элемента И 34 и к синхровходу третьего триггера 15. Выход второго канала OU Т2 таймера 12 подключен к синхровходу пятого триггера 17. Выход третьего канала OU Т3 таймера 12 подключен к синхровходу своего второго канала С2, к первому входу шестого элемента ИЛИ 35, выход которого подключен к вторым входам всех элементов И первой группы 28. Выход первого элемента И 30 подключен к входу выбора С5 корпуса таймера 12 и к вторым входам первой и второй групп входов первого дешифратора 19, управляющий вход третьего канала СЕ3 которого подключен к шине логической единицы. Выход второго элемента ИЗ1 подключен к входу CS выбора корпуса контроллера последовательного интерфейса 11, выход запроса прерывания INT которого подключен к одноименному входу микропроцессора 10. Выходы информации ТхD и запроса на передачу информации DTR контроллера 11 последовательного интерфейса являются одноименными выходами 49 и 50 устройства. Входы приема информации RxD и запроса на прием информации DSR контроллера 11 последовательного интерфейса являются одноименными входами 38 и 39 устройства. Вход начальной установки SR контроллера 11 последовательного интерфейса подключен к шине логического нуля устройства, первый и второй разрядные входы счетчика 3 подключены к шине логического нуля устройства, а третий и четвертый разрядные входы счетчика 3 подключены к шине логической единицы. Первый, второй и третий выходы пятого шинного формирователя 27 подключены соответственно к восьмому, первому и второму разрядным входам третьего шинного формирователя 25, прямой выход пятого триггера 17 подключен к третьему информационному входу пятого шинного формирователя 27, информационные входы третьего 15 и пятого 17 триггеров подключены к шине логического нуля устройства.

Рассмотрим назначение элементов схемы имитатора сигналов управления позиционированием магнитных головок относительно магнитных дисков.

Генератор 1 импульсов обеспечивает синхронизацию работы микропроцессора 10, контроллера 11 последовательного интерфейса и является источником счетных импульсов для счетчика 3 и первого канала программируемого таймера 12. Он имеет два выхода. Первый выход подключен к входам счетчика 3 и синхровходу первого канала. Частота следования импульсов на этом выходе в два раза меньше, чем частота следования импульсов второго выхода, который подключен к синхровходу микропроцессора 10.

Одновибратор 2 формирует короткий импульс установки микропроцессора 10 в исходное состояние по положительному фронту сигнала на входе 39 начальной установки устройства.

Счетчик 3 импульсов является делителем частоты импульсов, поступающих на его счетный вычитающий вход с первого выхода генератора 1 импульсов, и обеспечивает синхронизацию работы контроллера 11 последовательного интерфейса, для чего импульсы с его второго выхода, который является выходом старшего разряда, поступают на входы синхронизации приема RxC и передачи ТхС контроллера 11 последовательного интерфейса. Кроме того, эти импульсы используются в качестве синхронизирующих в третьем канале программируемого таймера 12. Коэффициент деления счетчика 3 равен 12. Такой коэффициент деления обеспечивается записью в каждом такте счета по информационным входам числа 12. Запись этого числа производится по сигналу переполнения, поступающего на синхровход счетчика 3 с его же первого выхода, который является выходом переполнения Р.

Первый регистр 4 является адресным регистром для блоков постоянной 8 и оперативной 9 памяти, а также других элементов устройства. Некоторые сигналы с его разрядных выходов используются для управления работой контроллера 11 последовательного интерфейса и программируемого таймера 12. Адресный код в регистр 4 записывается с информационных входов-выходов D микропроцессора 10 при наличии на его выходе ALЕ стробирующего сигнала адреса при чтении из внешней памяти, который поступает на управляющий С-вход записи регистра 4.

Второй регистр 5 обеспечивает запись и хранение унитарного кода маски накопителя, в котором производится позиционирование магнитных головок. Единица в n-разрядном коде маски соответствует активному накопителю из числа подключенных к имитатору, нуль- пассивным. Запись кода маски в регистр 5 производится по информационным входам D с информационных входов-выходов D микропроцессора 10 через шинные формирователи 25 и 26 при наличии единицы в первом разряде регистра 4 адреса, поступающего на управляющий V-вход регистра 5 через шинный формирователь 24. Запись информации в регистр 5 осуществляется по переднему фронту сигнала записи WR микропроцессора, поступающего на синхровход регистра 5 через шинный формирователь 24.

Третий регистр 6 предназначен для записи и хранения сигналов направления движения позиционеров накопителей. В одном из n разрядов регистра 6 записывается сигнал, управляющий направлением движения одного из n подключенных к имитатору накопителей. Запись в регистр 6 осуществляется так же, как в регистр 5, с той лишь разницей, что единичный сигнал на его управляющий V-вход поступает с второго разряда адресного регистра 4.

Четвертый регистр 7 предназначен для записи кода номера накопителя, для которого производится контроль периода следования сигнала "Индекс". Запись кода номера НМД производится аналогично записи информации в регистры 5 и 6, с тем только отличием, что по управляющему V-входу он открыт для записи при единичном сигнале, поступающем с выхода элемента И33 в том случае, когда в первом и втором разрядах адресного регистра 4 записаны единицы.

Блок 8 постоянной памяти обеспечивает хранение программы работы микропроцессора 10 для выполнения имитатором своих задач. Старшие разряды адреса постоянной памяти на группу входов А блока 8 поступают с выходов Р2 микропроцессора 10. При этом старший разряд кода с выходов порта Р2 микропроцессора 10 при обращении к блоку 8 постоянной памяти должен быть равен единице, так как он поступает на первый разрешающий вход Е1 этого блока. Младшие разряды адреса постоянной памяти поступают на группу адресных входов А2 блока 8 с информационных выходов регистра 4 адреса. Считывание информации с выходов блока 8 постоянной памяти производится через шинный формирователь 25 на информационные входы-выходы D микропроцессора 10 при поступлении с его выхода ALE сигнала стробирования адреса внешней памяти.

Блок 9 оперативной памяти обеспечивает хранение данных в процессе работы имитатора. Старшие разряды адреса на группу адресных входов А1 этого блока поступают с группы выходов Р3 микропроцессора 10, а младшие разряды адреса оперативной памяти поступают на группу адресных входов А2 с выхода регистра 4 адреса. При этом старший разряд адресного кода в регистре 4 должен быть равен 0, так как он поступает на инверсный разрешающий вход Е1 блока 9 оперативной памяти. На второй разрешающий вход Е2 сигнал поступает с выхода элемента ИЛИ 37. Он принимает единичное значение в том случае, когда производится обращение к внешней памяти данных, о чем свидетельствует наличие сигналов чтения RD или записи WR на выходах соответственно RD или WR микропроцессора 10. Режим работы блока 9 оперативной памяти "Чтение-запись" определяется значением сигнала на его входе WR, поступающим с выхода записи WR микропроцессора 10. Данные при записи и чтении в оперативную память поступают или выдаются на двунаправленную выходную шину, которая через шинный формирователь 25 подключена к информационным входам-выходам D микропроцессора 10.

Микропроцессор 10 обеспечивает управление процессом функционирования всего устройства и осуществляет необходимые вычисления в соответствии с алгоритмом испытаний НМД. При описании устройства в качестве примера выбран микропроцессор КМ1816ВЕ48. Работа микропроцессора 10 синхронизируется внешним генератором 1, второй вход которого подключен к синхровходу С микропроцессора 10. Запуск микропроцессора 10 осуществляется подачей импульса на его R-вход инициализации с выхода одновибратора 2. Микропроцессор 10 работает с внешней памятью, поэтому для выбранного микропроцессора на вход ЕМА подают сигнал логической единицы (на схеме не показано). Обмен данными между микропроцессором 10 и другими элементами устройства, а также выдача адресной информации и прием командной информации осуществляются через двунаправленный порт с входами-выходами D, подключенными к входам-выходам шинного формирователя 25. Выдача информации о состоянии контролируемых накопителей на внешнюю индикацию осуществляется через порт с группой выходов Р1, подключенных к входам шинного формирователя 23. Четыре младших разряда третьего порта микропроцессора 10 с группой выходов Р2 используются в качестве старших разрядов адреса блока 8 постоянной памяти. Четыре старших разряда третьего порта микропроцессора 10 с группой выходов Р3 используются в качестве старших разрядов адреса блока 9 оперативной памяти.

Управляющие выходы сигналов RD-чтения информации из внешней памяти, WR-записи информации во внешнюю память, РМЕ-строба чтения из внешней памяти, ALE-строба адреса внешней памяти используются микропроцессором 10 для организации обмена информацией с элементами внешней памяти, которыми являются: блок 8 постоянной памяти, блок 9 оперативной памяти, контроллер 11 последовательного интерфейса, программируемый таймер 12, регистры 4-7, входной мультиплексор 21.

Вход сигнала прерывания INT микропроцессора 10 подключен к соответствующему выходу контроллера 11 последовательного интерфейса и используется для включения режима обмена информацией между имитатором и внешней ЭВМ.

Контроллер 11 последовательного интерфейса предназначен для обмена информацией между имитатором и внешней ЭВМ по последовательному интерфейсу. Данные в параллельном коде поступают (выдаются) на информационные D входы контроллера 11 с информационных входов-выходов D микропроцессора 10 через шинный формирователь 25 по запросу прерывания, поступающего с выхода INT контроллера 11 на одноименный вход микропроцессора 10. Микропроцессор 10 выбирает контроллер 11 последовательного интерфейса в качестве источника/приемника информации путем записи в адресный регистр 4 кода, два старших разряда которого равны единице, при этом на выходе элемента И 31 вырабатывается единичный сигнал, который поступает на вход CS-выбора кристалла контроллера 11. Младший разряд адресного кода при этом определяет режим работы контроллера 11 управление/данные. Запись или считывание информации в контроллер 11 по параллельному D-входу определяется сигналами записи WR или считывания RD, поступающими с входов микропроцессора 10 на одноименные входы контроллера 11. Запрос от внешней ЭВМ на передачу в имитатор очередного слова информации в последовательном коде осуществляется с входа 39 устройства на вход DSR контроллера 11, прием информации в последовательном коде осуществляется с входа 38 устройства на вход RxD устройства. Запрос к внешней ЭВМ на передачу информации передается с выхода DTR контроллера 11 на выход 50 устройства. Выдача информации в последовательном коде осуществляется с выхода TxD на выход 49 устройства. Синхронизация контроллера 11 осуществляется подачей последовательности импульсов с первого выхода генератора 1 импульсов на вход контроллера 11. Синхронизация приема и выдачи информации в последовательном коде осуществляется подачей импульсов с второго выхода счетчика 3 импульсов на выходы RxC и TxC контроллера 11 соответственно.

Программируемый таймер 12 представляет собой трехканальный счетчик времени. Первый канал таймера 12 используется для формирования временного интервала, соответствующего сигналу минимально допустимому, а затем максимально допустимому периоду следования импульсов "Индекс" контролируемого НМД. Второй канал таймера обеспечивает подсчет числа импульсов "Шаг", поступающих с выхода третьего канала таймера OUT3 на синхровход С2 второго канала, и выдает на своем выходе OUT2 импульсный сигнал, когда число импульсов достигает величины, записанной в его счетчике. Это число равно числу цилиндров в контролируемом НМД. Третий канал таймера обеспечивает деление частоты импульсной последовательности с выхода счетчика 3 на записанный коэффициент деления таким образом, чтобы на выходе OUТ3 канала частота импульсов соответствовала частоте следования импульсного сигнала "Шаг" для заданного НМД. Перед началом работы любого канала таймера он должен быть запрограммирован. Для этого микропроцессор 10 записывает в регистр 4 код, адресующий таймер, шестой и восьмой разряды которого должны быть равны единице. При этом на выходе элемента И 30 вырабатываемый единичный сигнал в таймер 12 по входу CS выбора кристалла становится активным. После этого микропроцессор 10 может записать по входам D таймера 12 в соответствующий канал управляющее слово и содержимое счетчика. Все три канала таймера в устройстве работают в режиме формирования временных интервалов, отмечая его окончание подачей импульса на соответствующем выходе OUT. Принадлежность управляющего слова определенному каналу таймера 12 определяется содержимым специального поля в этом слове, а счетчики каналов адресуют двухразрядным кодам на входах А1 и А2 таймера, который поступает с двух младших разрядных выходов регистра 4. Начало отсчета временного интервала в любом канале начинается при появлении единичного сигнала на управляющем входе СЕ этого канала.

Триггер 13 предназначен для формирования импульса длительностью, равной периоду следования сигнала "Индекс" от выбранного накопителя, путем деления частоты следования коротких импульсов "Индекс" на два. Для этого триггер 13 работает в режиме Т-триггера, а на его синхровход подается сигнал "Индекс" выбранного накопителя с выхода мультиплексора 22.

Триггер 14 предназначен для формирования импульса с длительностью, равной максимальному или минимальному периоду следования сигналов "Индекс", границы которых определяются первым каналом таймера 12. По переднему фронту импульса с выхода триггера 13 триггер 14 устанавливается в единичное состояние, а сигнал с его прямого выхода разрешает работу по отсчету времени первого канала таймера 12. Когда таймер 12 отсчитает промежуток времени, равный максимальному или минимальному периоду следования сигнала "Индекс", на его первом выходе OUT1 появится короткий импульс, который установит триггер 15 в нулевое состояние, а сигнал с инверсного выхода триггера 15, поступив на вход сброса триггера 14, установит его в нуль, запрещает дальнейшую работу первого канала таймера 12.

Триггер 15 обеспечивает установку триггера 14 в исходное состояние перед и после процедуры контроля периода следования сигналов "Индекс". Перед началом измерений триггер 15 устанавливается в единицу импульсом с первого выхода первой половины дешифратора 19. При этом разблокируется по входу сброса триггер 14. По завершении очередного цикла контроля периода следования сигнала "Индекс" триггер 15 устанавливается в нулевое состояние, блокируя тем самым в нулевом состоянии триггер 14. Выходной сигнал триггера 15 поступает также через шинный формирователь 27 в восьмой разряд шины данных и при нулевом сигнале извещает процессор 10, что измерение завершено.

Триггер 16 фиксирует результат контроля периода следования сигнала "Индекс". При записи в счетчик данных первого канала таймера 12 длины заданного интервала с первого выхода первой группы выходов дешифратора 19 на вход сброса триггера 16 поступает импульс и устанавливает его в нуль. Если период следования сигнала "Индекс" больше заданного интервала, то импульс с первого выхода таймера 12 пройдет через открытый элемент И 34 и установит триггер 16 в единичное состояние. Если же период следования сигнала "Индекс" меньше заданного интервала, то к моменту прихода импульса окончания заданного интервала с выхода OUТ1 таймера 12 элемент И 34 будет закрыт нулевым сигналом с выхода триггера 13 и триггера 16 останется в нулевом состоянии. Выходной сигнал триггера 16 считывается через шинный формирователь 27 в первый разряд шины данных для передачи в микропроцессор 10.

Триггер 17 формирует временный интервал, в течение которого работает второй канал таймера 12, формирующий импульс "Шаг". Перед работой таймера по формированию импульсов "Шаг" с третьего выхода первой группы выходов дешифратора 19 на вход триггера 17 поступает импульс, который устанавливает его в исходное нулевое состояние. После записи заданного числа шагов в третий канал таймера 12 на втором выходе первой группы дешифратора 19 будет выдан единичный импульс, который установит триггер 17 в единичное состояние, снимая тем самым сигнал, удерживающий в нуле по R-входу триггер 18. По завершении выдачи третьим каналом заданного числа импульсов "Шаг" на выходе OUT2 второго канала таймера 12 появится единичный импульс, который сбросит триггер 17 в нуль. Прямой выход триггера 17 формирует сигнал оповещения о том, что выдается пачка импульсов "Шаг".

Триггер 18 формирует временной интервал, в течение которого выдается пачка с заданным количеством импульсов "Шаг". При наличии нулевого сигнала на R-входе триггера 18, поступающего с инверсного выхода триггера 17, триггер 18 разблокирован. Первый импульс, поступивший с выхода третьего канала таймера 12, поступая на синхровход триггера 18, устанавливает его в единичное состояние. При этом единичный сигнал с прямого выхода триггера 18, во-первых, разрешает работу второго канала таймера 12 по подсчету числа импульсов "Шаг" в пачке и, во-вторых, открывает элемент И 35 для передачи импульсов "Шаг" на выходы устройства. Сброс триггера 18 в нуль осуществляется единичным сигналом с инверсного выхода триггера 17 при прохождении на вход второго канала таймера 12 заданного числа импульсов.

Дешифратор 19 является двухканальным и служит для управления работой таймера 12 путем переключения триггеров 14-18. Информационные входы дешифратора 19 подключены к первому и второму разрядным входам регистра 4 адреса, которые управляют режимом работы таймера 12. Первая половина дешифратора 19 работает при наличии единичных сигналов на входах А1 и А2, которыми являются сигнал записи WR микропроцессора 10 и сигнал адресации таймера 12, который вырабатывается элементом И30. Вторая половина дешифратора 19 работает при наличии единичных сигналов на входах В 1 и В2, которыми являются сигнал RD микропроцессора 10 и сигнал адресации таймера 12 с выхода элемента И30. В режиме записи информации в таймер 12 первая группа выходов дешифратора 19 формирует следующие сигналы: при значении сигналов на информационных входах кода "11" (запись управляющего слова в каналы 0,1 или 2 таймера 12) возбуждается выход 3, сигнал которого обнуляет триггеры 14-18. При значении сигналов на информационных входах кода "00" (загрузка счетчика канала 0 таймера 15 в единичное состояние) разблокируется триггер 17 и триггер 16 в нулевое состояние, подготавливая их к циклу контроля периода следования сигнала "Индекс" контролируемого НМД. При значении сигналов кода "10" на информационных входах дешифратора 19 (загрузка счетчика канала 2 таймера 12) возбуждается выход 2, сигнал которого обнуляет триггер 17, чем разблокируется триггер 18, подготавливая устройство к выдаче пачки импульсов "Шаг". В режиме чтения информации при наличии на информационных входах дешифратора 19 кода "11" таймер 12 остановлен и через шинный формирователь 27 производится чтение состояний триггеров 15, 16 17 и состояний и результатов контроля таймера 12.

Дешифратор 20 обеспечивает дешифрацию номера накопителя, код которого поступает от накопителя.

Мультиплексор 21 является шестиканальным и служит для подключения к устройству с целью контроля интерфейсных сигналов одного из контролируемых накопителей. Адрес контролируемого накопителя в виде двухразрядного кода (в качестве примера рассматривается четыре контролируемых накопителя) поступает из регистра 4 адреса через шинный формирователь 24. Разрешение работы мультиплексора 21 по Е-входу осуществляется сигналом чтения RD микропроцессора 10, поступающим через третий выход шинного формирователя 24. Интерфейсные сигналы накопителя с выходов мультиплексора 21 через шинные формирователи 25 и 26 поступают на информационные входы-выходы D микропроцессора 10.

Мультиплексор 22 служит для подключения к устройству с целью контроля периода следования сигнала "Индекс" выбранного накопителя. Сигналы "Индекс" контролируемых накопителей поступают на информационные входы мультиплексора 22 с входов 27.1-27.n устройства. Адрес контролируемого накопителя поступает с выходов регистра 7.

Шинный формирователь 23 обеспечивает выдачу информации о ходе и результатах контроля накопителей с выходов Р1 микропроцессора 10 на выходы 48 устройства для их последующей индикации.

Шинный формирователь 24 обеспечивает передачу двухразрядного кода адреса с выходов регистра 4, а также сигналов "Запись" и "Чтение" микропроцессора 10 для выбора одного из регистров 5-7 или выбора интерфейсных сигналов одного из накопителей мультиплексором 21. При этом выбор регистров 5-7 осуществляется в режиме записи,а выбор группы интерфейсных сигналов - в режиме чтения. Шинный формирователь 24 обеспечивает передачу сигналов в одном направлении при наличии единичного сигнала, поступающего с выхода элемента И 32.

Шинный формирователь 25 является двунаправленным и служит для обмена информацией между микропроцессором 10 и всеми видами памяти устройства, включая блоки постоянной 8 и оперативной 9 памяти, последовательный интерфейс 11 и программируемый таймер 12. Запись информации в микропроцессор 10 через шинный формирователь 25 осуществляется при наличии единичного сигнала на его управляющем Т-входе, который формируется элементом ИЛИ 36 либо при выработке микропроцессором 10 сигнала RD чтения, либо при выработке микропроцессором 10 сигнала РМЕ чтения из внешней памяти. Передача информации от микропроцессора 10 к элементам памяти устройства осуществляется при нулевом значении сигнала на Т-входе шинного формирователя 25.

Шинный формирователь 26 является двунаправленным и служит для записи в микропроцессор 10 интерфейсных сигналов контролируемого НМД с выходов мультиплексора 21 и для записи управляющей информации из микропроцессора 10 в регистры 5-7. Шинный формирователь 26 передает информацию при наличии единичного сигнала на его разрешающем Е-входе, поступающего с выхода элемента И 32 при единичном значении четвертого и восьмого разрядов адресного кода в регистре 4 адреса. Направление передачи определяется сигналом на управляющем Т-входе шинного формирователя 26. Запись интерфейсных сигналов в микропроцессор 10 осуществляется при единичном сигнале на Т-входе шинного формирователя 26, поступающего с выхода сигнала чтения RD микропроцессора 10. При нулевом значении этого сигнала информация передается от микропроцессора 10 в регистры 5-7.

Шинный формирователь 27 обеспечивает передачу сигналов о состоянии таймера 12 и результатах контроля периода следования сигнала "Индекс" контролируемого НМД на входы шинного формирователя 25 и затем на информационные входы-выходы микропроцессора 10. Передача информации осуществляется при единичном сигнале на разрешающем Е-входе, который формируется на выходе второй группы выходов дешифратора 19 при условии единичных значений первого и второго разрядов адресного кода в регистре 4 в режиме чтения микропроцессора 10 при условии адресации таймера 12.

Группа элементов и 28.1-28.n обеспечивает передачу импульсов "Шаг" позиционирования магнитных головок на те накопители, которые исправны. Импульсы "Шаг" поступают на входы групп элементов и 28 с выхода элемента И 35. Открываются же элементы и 28 группы, на входы которых поступают единичные сигналы с разрядных выходов регистра 5.

Группа элементов И 29.2-29.n обеспечивает передачу сигнала "Направление" на исправные НМД. Сигналы, определяющие направление движения магнитных головок НМД, поступают на входы соответствующих элементов и 29 с разрядных выходов регистра 6, а разрешающие сигналы - с разрядных выходов регистра 5.

Элемент И 30 обеспечивает адресацию таймера 12 при единичном значении шестого и восьмого разрядов адресного кода на выходах регистра 4 адреса. При этом единичный сигнал с выхода элемента И 30 разрешает работу таймера 12 по входу СS выбора кристалла.

Элемент И 31 обеспечивает адресацию контроллера 11 последовательного интерфейса при единичном значении седьмого и восьмого разрядов адресного кода на соответствующих выходах регистра 4 адреса. При этом единичный сигнал с выхода элемента И 31 разрешает работу контроллера 11 последовательного интерфейса по входу CS выбора кристалла.

Элемент И 32 формирует сигнал разрешения передачи информации через шинные формирователи 24 и 26 при единичном значении четвертого и восьмого разрядов адресного кода на соответствующих разрядных выходах регистра 4 адреса.

Элемент И 33 формирует сигнал разрешения записи информации по V-входу в регистр 7 в том случае, если первый и второй разряды адресного кода в регистре 4 принимают единичное значение.

Элемент И 34 обеспечивает передачу импульса с выхода первого канала таймера 12 на синхровход триггера 16 только в том случае, если триггер 13 находится в единичном состоянии, т.е. пока не закончится измеряемый период следования сигнала "Индекс".

Элемент И 35 обеспечивает передачу на выходы 51 устройства через группу элементов И 28 пачки импульсов "Шаг" с заданным количеством импульсов с выхода OUТ3 третьего канала таймера. Для этого элемент И 35 открывается единичным сигналом с первого выхода триггера 18.

Элемент ИЛИ 36 обеспечивает передачу информации через шинный формирователь 25 на информационные входы-выходы D микропроцессора 10 либо в режиме чтения микропроцессора 10, либо при наличии сигнала строба чтения из внешней памяти РМЕ микропроцессора 10.

Элемент ИЛИ 37 обеспечивает разрешение работы блока 9 оперативной памяти по второму разрешающему входу в режиме записи или считывания информации микропроцессором 10.

Рассмотрим работу устройства.

При запуске устройства на вход 40 подается импульс, по переднему фронту которого одновибратор 2 вырабатывает короткий импульс начальной установки микропроцессора 10. После этого микропроцессор 10 начинает выполнение программы испытаний НМД. Сначала последовательно от всех НМД, подключенных к устройству, проверяется наличие сигналов о их состоянии. При этом микропроцессор 10 под действием управляющей программы записывает в регистр 4 адреса код номера НМД, сигналы которого должны контролироваться. Код адреса должен иметь вид А=100Х1А1А0 (здесь Х - любое значение, код А1А0 - двоичный код номера НМД). После записи кода адреса в регистр 4 микропроцессор 10 выставляет активный сигнал чтения на выходе RD. При этом сигналы А4 и А8 с выхода регистра 4 откроют элемент И 32, единичный сигнал с выхода элемента И 32 разрешит передачу информации через шинные формирователи 24 и 26. Единичный сигнал с выхода RD микропроцессора 10, поступая на Т-входы шинных формирователей 25 и 26, установит направление передачи от мультиплексора 21 к микропроцессору 10. Проходя через шинный формирователь 24, сигнал разрешит работу мультиплексора 21, а адресные разряды А2 и А1 поступят на адресные входы мультиплексора 21 и подключатся к входам каналов мультиплексора 21 входов сигналов о состоянии адресуемого НМД.

С выхода первого канала мультиплексора 21 сигнал "Готовность" адресуемого НМД поступает на первый информационный разрядный вход D1 микропроцессора 10, с выхода второго канала мультиплексора 21 на D2 вход микропроцессора 10 поступает сигнал "Ошибка", с выхода третьего канал мультиплексора 21 на вход D3 поступает сигнал "Нулевая дорожка", с выхода четвертого канала мультиплексора 21 на вход D4 микропроцессора 10 поступает сигнал "Установка завершена", с выхода пятого канала мультиплексора 21 на вход D6 поступает сигнал "Тип накопителя" (рассматривается два типа), с выхода шестого канала мультиплексора 21 на вход D8 микропроцессора поступает код номера НМД.

Накопители проверяются устройством последовательно путем программного изменения индекса N.

В соответствии с алгоритмом проверки сигналов НМД (фиг. 3) последовательно для каждого адресуемого накопителя проверяется наличие контролируемых сигналов от НМД и факт появления этих сигналов в установленные интервалы времени. В случае, если один из контролируемых сигналов на момент проверки отсутствует, но появляется в течение заданного времени, проверка этого НМД в данном цикле контроля не производится, факт этого случая и причина запоминаются, но для дальнейших испытаний он не исключается. Если же один из контролируемых сигналов в заданном интервале времени не появляется, то для него устанавливается программная метка ошибки accid[N]=1 и он считается забракованным и в дальнейших испытаниях не участвует.

Последним проверяется сигнал "Нулевая дорожка", который определяет направление позиционирования. В зависимости от значения этого сигнала выполняется аппаратно подпрограмма позиционирования магнитных головок либо к нулевой дорожке, либо к максимальной дорожке.

После выполнения позиционирования следует интервал времени ожидания sec[N]=8 с. Затем контролируется период следования сигнала "Индекс", т.е. частота вращения шпинделя накопителя, и если он в норме, путем изменения переменной N на единицу устройство переходит к контролю следующего НМД в текущем цикле контроля. Если текущий цикл контроля завершен, то переменной N присваивается значение 1 и начинается следующий цикл контроля.

Процедура позиционирования магнитных головок НМД производится следующим образом (см. временные диаграммы на фиг. 4, 5). Микропроцессор 10 со своих информационных входов-выходов D записывает в регистр 4 адреса код 100х1001 путем подачи импульса АLE. При этом разрешается работа шинны формирователей 24 и 26. На Т-входах направления шинных формирователей 25 и 26 будут нулевые сигналы, что обеспечит передачу информации от информационных входов-выходов D микропроцессора 10. Одновременно первым разрядом адресного кода А1, поступающим через шинный формирователь 24 на V-вход регистра 5, будет разрешена запись информации в регистр 5. Затем микропроцессор 10 выставляет на своих D-входах-выходах унитарный код контролируемого накопителя, который по сигналы записи WR микропроцессора 10, поступающего на синхровход регистра 5, будет записан в этот регистр.

Аналогичным образом записан унитарный код направления движения магнитных головок НМД в регистр 6. Только при этом в адресный регистр 4 будет записываться адресный код 100х1010.

После записи информации в регистры 5 и 6 начинается программирование второго и третьего каналов таймеров 12, участвующих в формировании пачки импульсов "Шаг". Для этого микропроцессор 10 записывает в регистр 4 адреса адресный код 101х0х11. При этом элемент И 30 вырабатывает единичный сигнал, который разрешает работу таймера 12 по входу CS выбора кристалла. На адресные входы А0А1 таймера подаются единичные сигналы, обеспечивая режим приема управляющих слов. После этого микропроцессор 10 последовательно выставляет на своих D-входах-выходах управляющие слова второго и третьего каналов таймера 12, вырабатывая одновременно активный сигнал записи WR, обеспечивая тем самым запись информации через шинный формирователь 25 и таймер 12. Одновременно с этим вырабатывается единичный сигнал на третьем выходе первой половины дешифратора 19, обеспечивая установку триггера 17 в нуль. Затем аналогичным образом микропроцессор 10 записывает данные в счетчики второго и третьего каналов таймера 12. Для записи данных во второй канал адресный код в регистре 4 должен иметь значение 101х0х01, в третий канал - 101х0х10. В зависимости от типа контролируемого НМД микропроцессор 10 записывает в счетчик второго канала таймера число цилиндров накопителя, а в счетчик третьего канала-коэффициент деления исходной частоты до частоты следования импульсов "Шаг".

При записи информации в счетчик второго канала таймера 12 на информационных входах дешифратора 19 будет код 10. При появлении сигнала WR микропроцессора дешифратор 19 выработает единичный сигнал на втором выходе своей первой половины, который установит триггер 17 в единичное состояние. При этом разблокируемый триггер 18 в единичный сигнал установится на третьем входе шинного формирователя 7, который может быть считан микропроцессором 10, и говорит о том, что устройство занято формированием пачки импульсов "Шаг".

Первый импульс с выхода третьего канала таймера 120 UT3 установит триггер 18 в единичное состояние, разрешая работу второго канала таймера 12 и открывая элемент И 35. Так как длительность импульса с выхода OUT3 таймера гораздо больше времени срабатывания триггера 18, то уже первый импульс пройдет через элемент И 35. Импульс "Шаг" с выхода элемента И 35 будет передаваться через один открытый элемент И группы 51 на вход адресуемого унитарным кодом в регистре 5 накопителя.

Когда число импульсов "Шаг" будет равно числу цилиндров НМД, на выходе второго канала таймера 12 OUT2 появится единичный импульс, который установит триггер 17 в нулевое состояние. При этом триггер 18 установится также в нуль и запретит работу второго канала таймера 12 и передачу импульсов "Шаг" через элемент И 35 на выход устройства. На этом процедура формирования пачки импульсов "Шаг" закончится.

Процедура контроля периода следования сигнала "Индекс" контролируемого НМД заключается в сравнении импульса длительностью этого периода с интервалом времени, формируемым первым каналом таймера 12. При этом сначала таймер 12 формирует интервал времени больше номинального на величину допуска, а затем меньше. Импульсы длительностью, равной периоду следования сигнала "Индекс", формируются триггером 13, работающим в счетном режиме. Сигналы "Индекс" на синхровход триггера 13 поступают с выхода мультиплексора 22, который выбирает адресуемый НМД по адресу, записанному в регистр 7. Запись адреса НМД в регистр 7 производится с выходов D микропроцессора 10 при адресном коде в регистре 4, равном 101х0х11. При этом сигнал элемента И 33 разрешает запись информации в регистр 7.

Процедура контроля сигнала "Индекс" (см. временные диаграммы на фиг. 6) начинается в записи в первый канал таймера 12 управляющего слова, которая осуществляется так же, как и при записи управляющих слов во второй и третий каналы таймера 12. При этом сбрасывается в нуль триггер 15, что блокирует триггер 14. При записи кода длительности формируемого интервала времени в счетчик первого канала таймера 12 в регистр 4 адреса записывается код 101х0х10. При этом по сигналу записи WR микропроцессора 10 дешифратор 19 вырабатывает единичный импульс на первом выходе своей первой половины. Этот сигнал устанавливает триггер 15 в единичное состояние, разблокируя работу триггера 14 и устанавливая в нуль триггер 16. Передний фронт первого импульса с выхода триггера 13 установит триггер 14 в единичное состояние, разрешая работу первого канала таймера 12. Единичный сигнал с выхода триггера 13 разрешает также работу элемента И 34. Если временной интервал времени, формируемый таймером 12, завершится раньше конца времени действия импульса с выхода триггера 13, то триггер 16 будет установлен в единичное состояние импульсом, поступающим на синхровход триггера 16 с выхода OUT1 первого канала таймера 12 через открытый элемент И 34. Таким образом единичное состояние триггера 16 говорит о том, что период следования импульсов "Индекс" больше заданного интервала времени. Если период следования импульсов "Индекс" меньше заданного интервала времени, то триггер 13 перейдет в нулевое состояние раньше, чем появится импульс на выходе первого канала таймера 12. При этом триггер 16 останется в нулевом состоянии, так как импульс с выхода OUT1 таймера 12 не сможет пройти на синхровход триггера 16 через элемент И 34.

Микропроцессор 10 считывает состояние триггера 16, записав в регистр 4 адреса код 101х0х11. При поступлении сигнала чтения с выхода RD микропроцессора на выходе второй половины дешифратора 19 появится единичный сигнал, который разрешит чтение информации с выходов шинного формирователя 27. При этом значения сигналов на входах микропроцессора 10 будут говорить о следующих ситуациях: D8= 0/1 - измерение завершено/не завершено; D1=0/1 - Тиндекса больше/меньше; D2=0/1 - шаги завершены/идут.

В устройстве предусмотрена возможность передачи результатов контроля НМД в универсальную ЭВМ через контроллер 11 последовательного интерфейса. Инициирует работу контроллера 11 микропроцессор 10. Для этого он записывает в регистр 4 адреса код 110х0хХХ1. При этом единичный сигнал появляется на выходе элемента и 31 и адресует контроллер по входу CS выбора кристалла. Единичный сигнал на входе CO/D переводит контроллер 11 в режим программирования. На своих информационных входах-выходах микропроцессор 10 последовательно выставляет код выбора режима 01001110, а затем код команды 00000111. При этом устанавливается асинхронный режим с однобайтной длиной слова обмена данными при отсутствии контроля на четность/нечетность с длиной стоп/бита, равной длине информационного бита. Команда с кодом 00000111 запрашивает внешнюю ЭВМ о возможности обмена данными как от внешней ЭВМ в устройство, так и в обратном направлении. При обмене данными в адресный регистр 4 должен быть записан код 110х0хХ0. При этом нулевой сигнал на входе СО/D контроллера 11 переводит последний в режим обмена данными. О готовности контроллера 11 к обмену байтом данных с микропроцессором 10 контроллер 11 посылает со своего выхода INT сигнал запроса прерывания на одноименный вход микропроцессора 10.

Оценим технико-экономическую эффективность предлагаемого устройства по сравнению с устройством-прототипом. В качестве критерия оценки выберем относительную величину потери времени при испытаниях НМД за счет возможности отсутствия одного из сигналов идентификации накопителя.

Предположим, что вероятность отказа накопителя сразу после сборки (до испытания и выявления неработоспособных, а следовательно, отсутствия одного из сигналов от накопителя "Готовность" "Установка завершена", "Нулевая дорожка", "Тип накопителя", "Номер накопителя" или наличие сигнала "Ошибка") будет Р1=0,95 и вероятность пропадания одного из сигналов распределена равномерно по времени испытаний. Предположим также, что к имитатору подключается одновременно число накопителей n=4, а время одного цикла испытания одного накопителя равно Т=10 с, число циклов К=100.

Тогда время полного испытания всех подключенных накопителей будет равно

tисп=n˙T˙k

Предположим время смены накопителей (их установка и подключение к имитатору) составляет tсм=20 мин=1200 с.

Тогда потеря времени в устройстве-прототипе составит:

tпотn=( ˙ tисп+tсм)˙(1-P1)=(

˙ tисп+tсм)˙(1-P1)=(  ˙ n ˙T ˙ k+tсм)˙( 1-P1 ).

˙ n ˙T ˙ k+tсм)˙( 1-P1 ).

В предлагаемом устройстве выход из строя одного из проверяемых накопителей будет вызывать только то, что одно из испытательных мест имитатора не будет использоваться.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С НОСИТЕЛЯ МАГНИТНОЙ ЗАПИСИ | 1992 |

|

RU2018174C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

Изобретение относится к накоплению информации, а именно к имитаторам сигналов управления позиционированием магнитных головок, и может быть использовано для испытания накопителей на магнитных дисках. Сущность изобретения заключается в том, что за счет введения новых элементов и их связей, которые позволяют обеспечить управление позиционированием магнитных головок накопителей различных типов, одновременно подключенных к имитатору, разделенный для каждого накопителя анализ наличия и времени появления сигналов идентификации состояния путем программной установки временных границ допустимого времени появления этих сигналов, контроль скорости вращения дисков для каждого накопителя и повышение степени автоматизации и гибкости процесса испытаний, расширена область применения устройства. 6 ил.