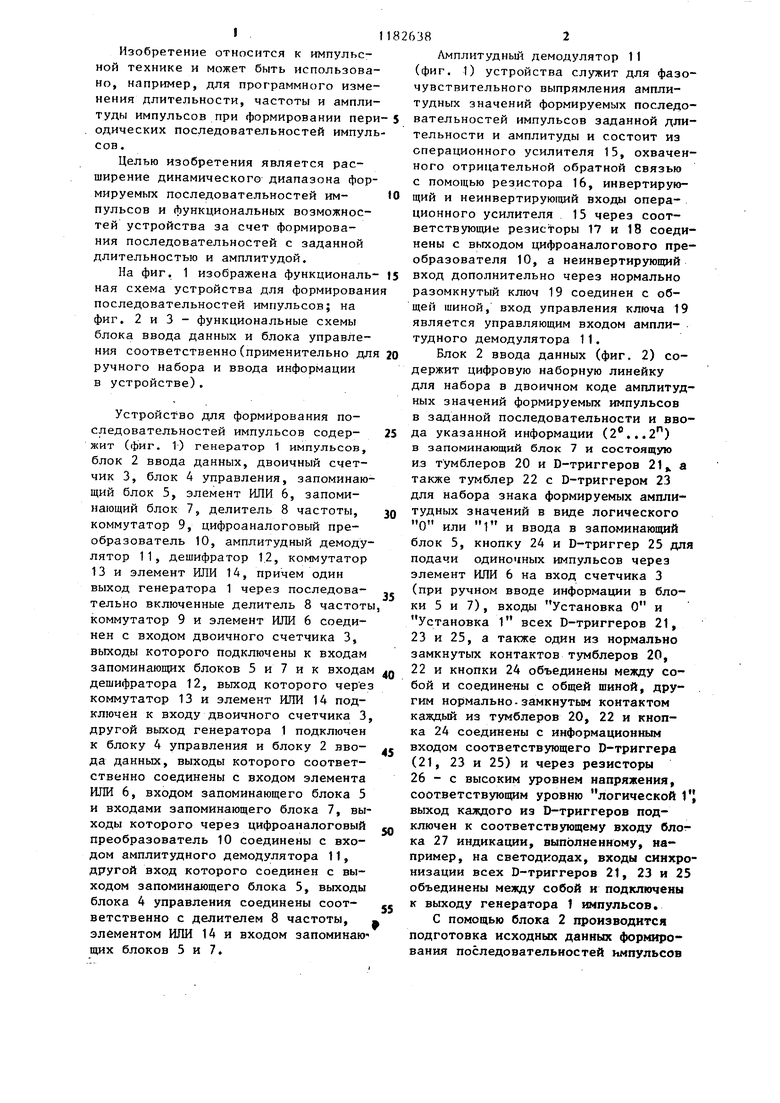

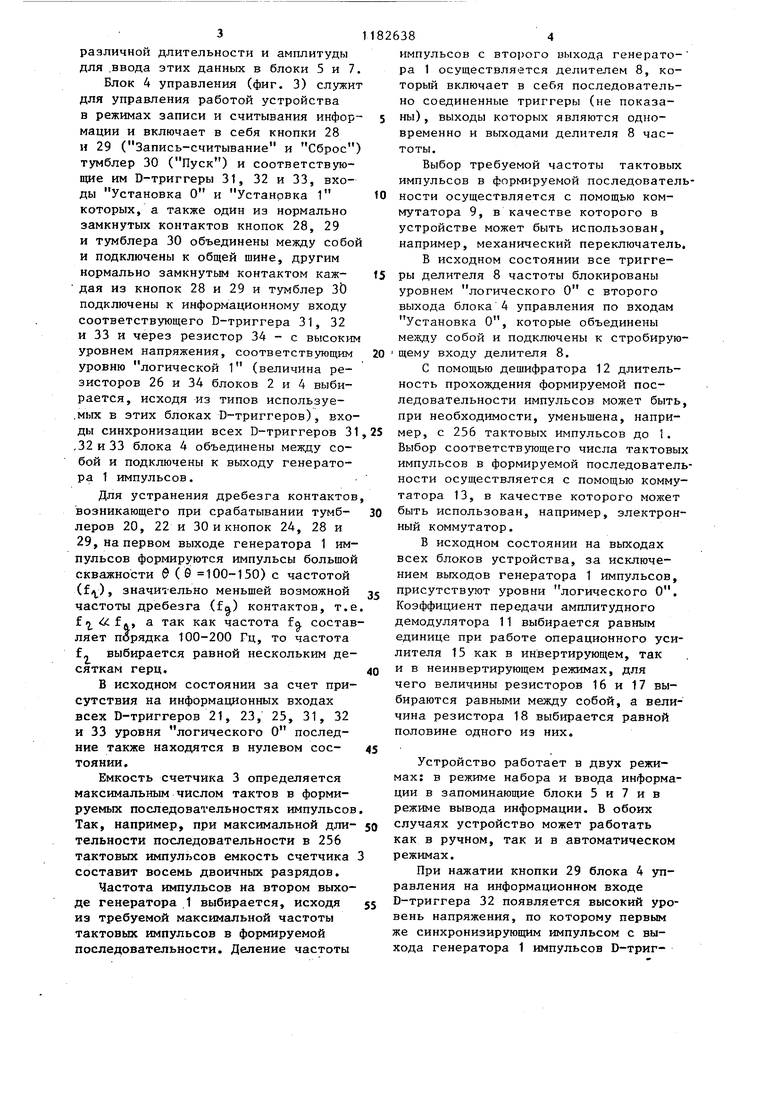

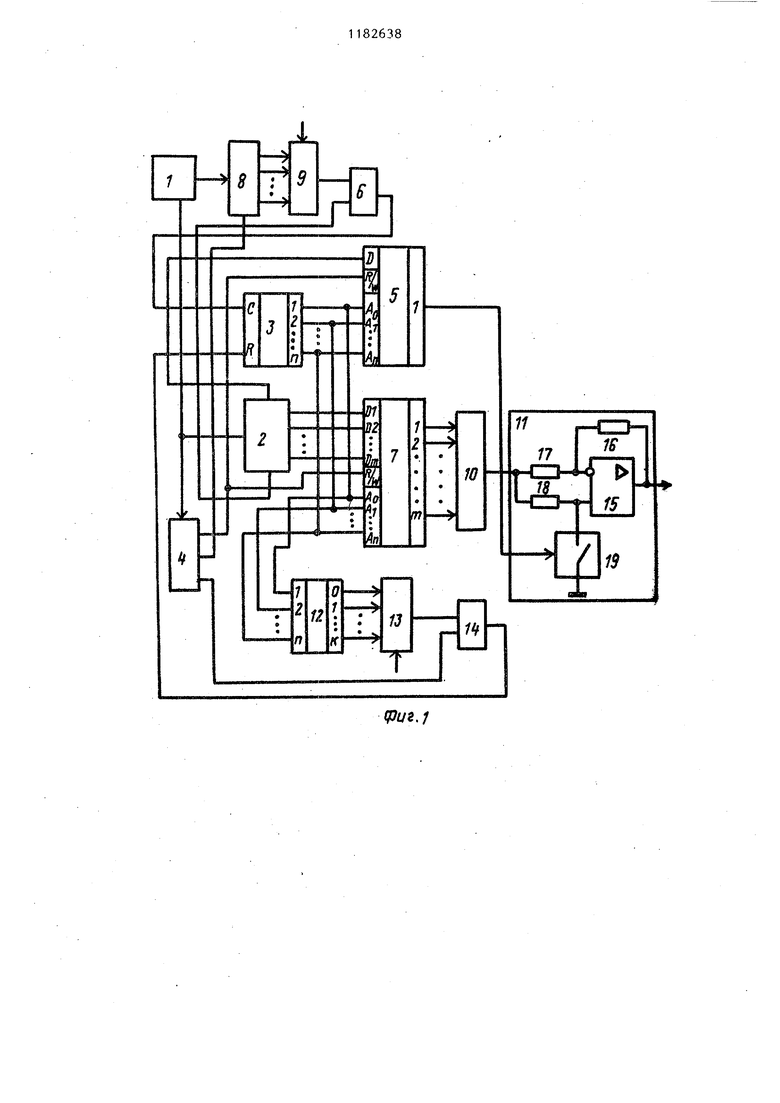

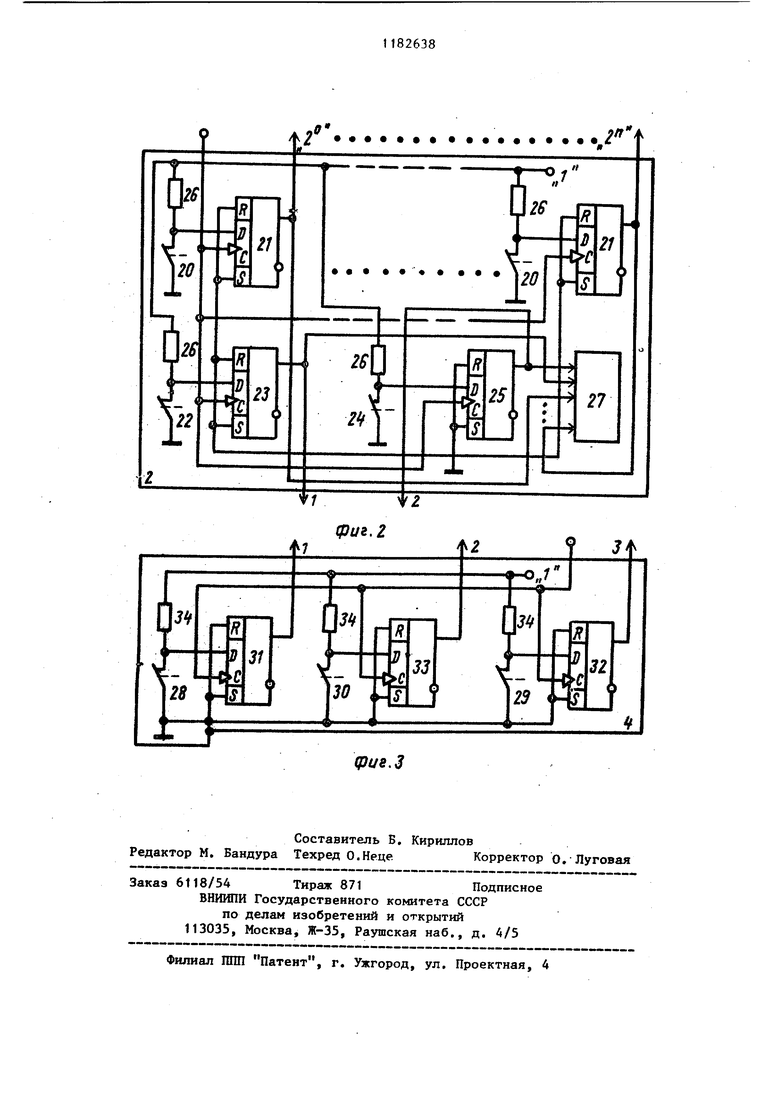

Изобретение относится к импульсной технике и может быть использова но, например, для программного изменения длительности, частоты и ампли туды импульсов при формировании пер одических последовательностей импул сов. Целью изобретения является расширение динамического диапазона фор мируемых последовательностей импульсов и функциональных возможностей устройства за счет формирования последовательностей с заданной длительностью и амплитудой. На фиг. 1 изображена функциональ ная схема устройства для формирован последовательностей импульсов; на фиг, 2 и 3 - функциональные схемы блока ввода данных и блока управления соответственно(применительно дл ручного набора и ввода информации в устройстве). Устройство для формирования последовательностей импульсов содержит (фиг. 1) генератор 1 импульсов, блок 2 ввода данных, двоичный счетчик 3, блок 4 управления, запоминающий блок 5, элемент ИЛИ 6, запоминающий блок 7, делитель 8 частоты, коммутатор 9, цифроаналоговый преобразователь 10, амплитудный демодулятор 11, дешифратор 1.2, коммутатор 13 и элемент ИЛИ 14, причем один выход генератора 1 через последовательно включенные делитель 8 частоты коммутатор 9 и элемент ИЛИ 6 соединен с входом двоичного счетчика 3, выходы которого подключены к входам запоминающих блоков 5 и 7 и к входам дешифратора 12, выход которого через коммутатор 13 и элемент ИЛИ 14 подключен к входу двоичного счетчика 3 другой выход генератора 1 подключен к блоку А управления и блоку 2 ввода данных, выходы которого соответственно соединены с входом элемента ИЛИ 6, входом запоминающего блока 5 и входами запоминающего блока 7, выходы которого через цифроаналоговый преобразователь 10 соединены с входом амплитудного демодулятора 11, другой вход которого соединен с выходом запоминающего блока 5, выходы блока 4 управления соединены соответственно с делителем 8 частоты, элементом ИЛИ 14 и входом запоминающих блоков 5 и 7. Лмплитудньй демодулятор 11 (фиг. 1) устройства служит для фазочувствительного выпрямления амплитудных значений формируемых последовательностей импульсов заданной длительности и амплитуды и состоит из операционного усилителя 15, охваченного отрицательной обратной связью с помощью резистора 16, инвертирующий и неинвертирующий входы операционного усилителя 15 через соответствующие резисторы 17 и 18 соединены с выходом цифроаналогового преобразователя 10, а неинвертирующий вход дополнительно через нормально разомкнутый ключ 19 соединен с общей шиной, вход управления ключа 19 является управляющим входом амплитудного демодулятора 11. Блок 2 ввода данных (фиг, 2) содержит цифровую наборную линейку для набора в двоичном коде амплитудных значений формируемых импульсов в заданной последовательности и ввода указанной информации (2°,..2) в запоминающий блок 7 и состоящую из тумблеров 20 и D-триггеров 21„ а также тумблер 22 с D-триггером 23 для набора знака формируемых амплитудных значений в виде логического О или 1 и ввода в запоминающий блок 5, кнопку 24 и D-триггер 25 для подачи одиночных импульсов через элемент ИЛИ 6 на вход счетчика 3 (при ручном вводе информации в блоки 5 и 7) , входы Установка О и Установка 1 всех D-триггеров 21, 23 и 25, а также один из нормально замкнутых контактов тумблеров 20, 22 и кнопки 24 объединены между собой и соедине«ы с общей шиной, другим нормально - замкнутым контактом каждый из тзгмблеров 20, 22 и кнопка 24 соединены с информационным входом соответствующего D-триггера (21, 23 и 25) и через резисторы 26 - с высоким уровнем напряжения, соответствующим уровню логической 1 выход каждого из D-триггеров подключен к соответствующему входу блогка 27 индикации, выполненному, например, на светодкодах, входы синхронизации всех D-триггеров 21, 23 и 25 объединены между собой и подключены к выходу генератора 1 импульсов. С помощью блока 2 производится подготовка исходных данных формирования последовательностей импульсов

различной длительности и амплитуды для .ввода этих данных в блоки 5 и 7.

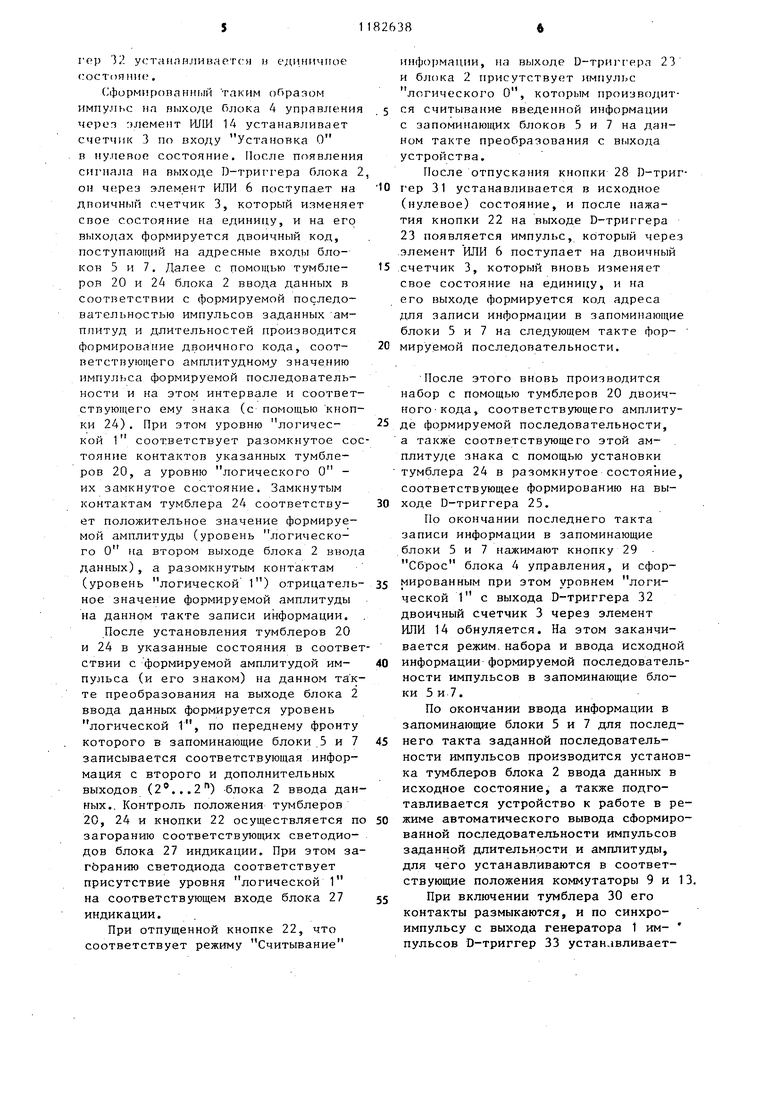

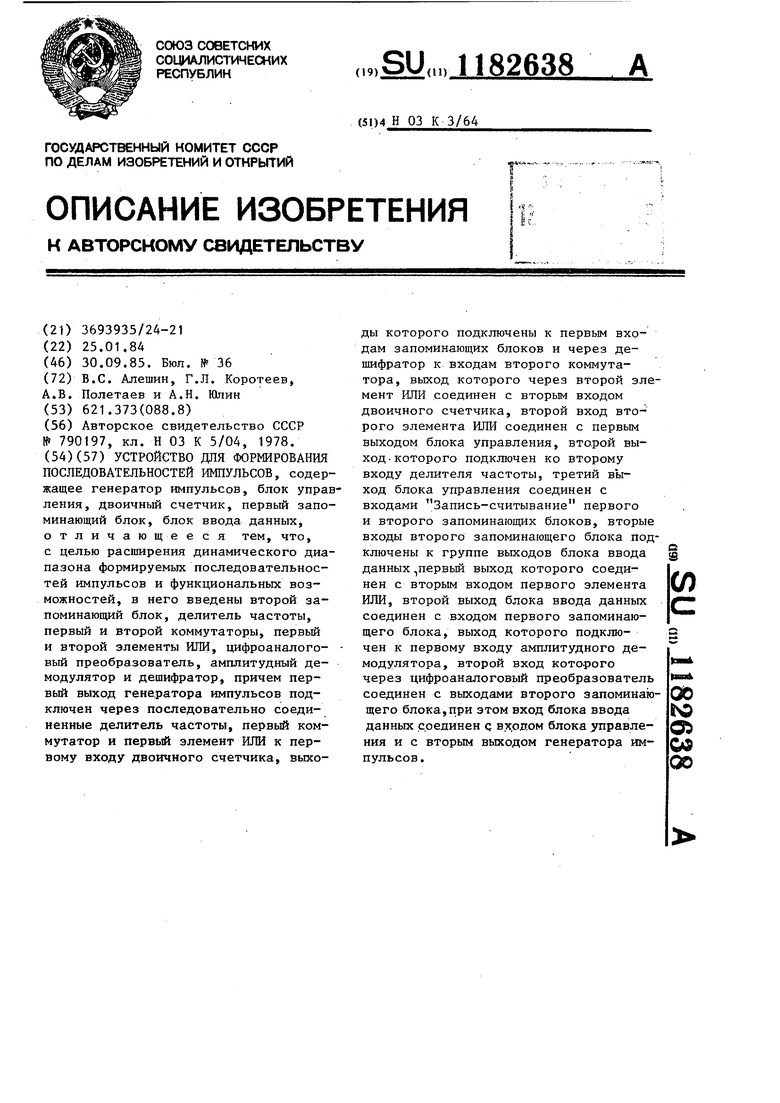

Блок 4 управления (фиг. 3) служит для управления работой устройства в режимах записи и считывания инфор- s мации и включает в себя кнопки 28 н 29 (Запись-считывание и Сброс) тумблер 30 (Пуск) и соответствующие им D-триггеры 31, 32 и 33, входы Установка О и Установка 1 Ю которых, а также один из нормально замкнутых контактов кнопок 28, 29 и тумблера 30 объединены между собой и подключены к общей шине, другим нормально замкнутым контактом каж- fS дая из кнопок 28 и 29 и тумблер ЗО подключены к информационному входу соответствующего D-триггера 31, 32 и 33 и через резистор 34 - с высоким уровнем напряжения, соответствующим 20 уровню логической 1 (величина резисторов 26 и 34 блоков 2 и 4 выбирается, исходя из типов используемых в этих блоках D-триггеров), входы синхронизации всех D-триггеров 31,25 32 и 33 блока 4 объединены между собой и подключены к выходу генератора 1 импульсов.

Для устранения дребезга контактов, озникающего при срабатывании тумб- 30 еров 20, 22 и 30 и кнопок 24, 28 и 29, на первом выходе генератора 1 имульсов формируются импульсы большой кважности & (6 100-150) с частотой (f/), значительно меньшей возможной астоты дребезга (f) контактов, т.е. f2.jCf а так как частота f составяет порядка 100-200 Гц, то частота f- выбирается равной нескольким деяткам герц.40

В исходном состоянии за счет приутствия на информационных входах всех D-триггеров 21, 23, 25, 31, 32 и 33 уровня логического О последние также находятся в нулевом сое- 5 тоянии.

Емкость счетчика 3 определяется аксимальным числом тактов в формируемых последовательностях импульсов. Так, например, при максимальной дли- 50 тельности последовательности в 256 тактовых импульсов емкость счетчика 3 составит восемь двоичных разрядов.

Частота импульсов на втором выходе генератора 1 выбирается, исходя 55 из требуемой максимальной частоты тактовых импульсов в формируемой последовательности. Деление частоты

импульсов с второго выход{1 генератора 1 осуществляется делителем 8, который включает в себя последовательно соединенные триггеры (не показаны) , выходы которых являются одновременно и выходами делителя 8 частоты.

Выбор требуемой частоты тактовых импульсов в формируемой последователности осуществляется с помощью коммутатора 9, в качестве которого в устройстве может быть использован, например, механический переключатель

В исходном состоянии все триггеры делителя 8 частоты блокированы уровнем логического О с второго выхода блока 4 управления по входам Установка О, которые объединены между собой и подключены к стробируюI щему входу делителя 8.

С помощью дешифратора 12 длительность прохождения формируемой последовательности импульсов может быть при необходимости, уменьшена, например, с 256 тактовых импульсов до 1. Выбор соответствующего числа тактовы импульсов в формир5емой последователности осуществляется с помощью коммутатора 13, в качестве которого может быть использован, например, электронный коммутатор.

В исходном состоянии на выходах всех блоков устройства, за исключением выходов генератора 1 импульсов, присутствуют уровни логического О. Коэффициент передачи амплитудного демодулятора 11 выбирается равным единице при работе операционного усилителя 15 как в инвертирующем, так и в неинвертирующем режимах, для чего величины резисторов 16 и 17 выбираются равными между собой, а величина резистора 18 выбирается равной половине одного из них.

Устройство работает в двух режимах: в режиме набора и ввода информации в запоминающие блоки 5 и 7 и в режиме вывода информации. В обоих случаях устройство может работать как в ручном, так и в автоматическом режимах.

При нажатии кнопки 29 блока 4 управления на информационном входе D-триггера 32 появляется высокий уровень напряжения, по которому первым же синхронизирующим импульсом с выхода генератора 1 импульсов D-тригrep 32 устаиянливается и единичное

состоя HIK .

Сформиронанн1 1Й таким образом UMiiyju.c на выходе блока 4 управления черол :)лемент ИЛИ 14 устанавливает счетчирс 3 по входу Установка О в нулевс е состояние. После появления сигнала на выходе D-триггера блока 2 он через элеме т ИЛИ 6 поступает на дпоичнр.1й счетчик 3, который изменяет свое состояние на единицу, и на егсэ выходах формируется двоичный код, поступающий на адресные входы блоков 5 и 7, Далее с помощью тумблеров 20 и 2А блока 2 ввода данных в соответствии с формируемой последовательностью импульсов заданных амплитуд и длительностей производится формирование двоичного кода, соответствующего амплитудному значению импульса формируемой последовательности и на этом интервале и соответствующего ему знака (с помощью кнопки 24), При этом уровню логической 1 соответствует разомкнутое состояние контактов указанных тумблеров 20, а уровню логического О их замкнутое состояние. Замкнутым контактам тумблера 24 соответствует положительное значение формируемой амплитуды (уровень логического О на втором выходе блока 2 ввода данных), а разомкнутым контактам (уровень логической 1) отрицательное значение формируемой амплитуды на данном такте записи информации.

После установления тумблеров 20 и 24 в указанные состояния в соответствии с формируемой амплитудой импульса (и его знаком) на данном такте преобразования на выходе блока 2 ввода данных формируется уровень логической 1, по переднему фронту которого в запоминающие блоки 5 и 7 записывается соответствующая информация с второго и дополнительных выходов (2...2) -блока 2 ввода данных.. Контроль положения тумблеров 20, 24 и кнопки 22 осуществляется по загоранию соответствумпщх светодиодов блока 27 индикации. При этом загЪранию светодиода соответствует присутствие уровня логической 1 на соответствующем входе блока 27 индикации.

При отпущенной кнопке 22, что соответствует режиму Считывание

информации, на выходе В-три1герп 23 и блока 2 присутствует импульс логического О, которым производится считывание введенной информации с запоминающих блоков 5 и 7 на данном такте преобразования с выхода устройства.

После отпускания кнопки 28 О-триггер 31 устанавливается в исходное (нулевое) состояние, и после нажатия кнопки 22 на выходе D-триггера 23 появляется импульс, кЬторый через элемент ИЛИ 6 поступает на двoич tый счетчик 3, который вновь изменяет свое состояние на единицу, и на его выходе формируется код адреса для записи информации в запоминающие блоки 5 и 7 на следующем такте формируемой последовательности.

После этого вновь производится набор с помощью тумблеров 20 двоичного -кода, соответствующего амплитуде формируемой последовательности, а также соответствующего этой амплитуде знака с помощью установки тумблера 24 в разомкнутое состояние, соответствующее формированию на выходе D-триггера 25.

По окончании последнего такта записи информации в запоминающие блоки 5 и 7 нажимают кнопку 29 Сброс блока 4 управления, и сформированным при этом уровнем логической 1 с выхода D-триггера 32 двоичный счетчик 3 через элемент ИЛИ 14 обнуляется. На этом заканчивается режим.набора и ввода исходной информации формируемой последовательности импульсов в запоминающие блоки 5 и 7 .

По окончании ввода информации в запоминающие блоки 5 и 7 для последнего такта заданной последовательности импульсов производится установка тумблеров блока 2 ввода данных в исходное состояние, а также подготавливается устройство к работе в режиме автоматического вывода сформированной последовательности импульсов заданной длительности и амплитуды, для чего устанавливаются в соответствующие положения коммутаторы 9 и

При включении тумблера 30 его контакты размыкаются, и по синхроимпульсу с выхода генератора 1 импульсов D-триггер 33 устанавливается в единичное состояние, при котором уровнем логической 1 с выхода блока 4 управления по стробирующему входу делителя 8 частоты снимается блокировка его триггеров, которые включаются в режим последовательного деления частоты импульсов, поступающих на его вход с выхода генератора 1 импульсов. С учетом выбранного коэффициента деления частоты импульсы с соответствующего выхода делителя 8 через коммутатор 9 и элемент ИЛИ 6 поступают на счетный вход двоичного счетчика 3, на выходе которого в соответствии с поступающими тактовыми импульсами начинает формироваться двоичный код для считывания записанной информации из соответствующих ячеек запоминающих блоков 5 и 7.

Так как при этом на выходе блока 4 управления присутствует уровень логического О, что разрешает считывание информации из запоминающих блоков 5 и 7, то на в.ыходах последних в соответствии с адресными кодовыми комбинациями двоичного счетчика 3 будут формироваться последовательности импульсов заданных амплитуд (на выходах запоминающего блока 7), а также их длительностей и знаков.

Из кодовых комбинаций, формируемых на выходах запоминающего блока 7 в цифроаналоговом преобразователе 10 производится преобразование входного двоичного кода в соответствующую выходную аналоговую величину одного знака, которая поступает на вход амплитудного демодулятора 11.

В амплитудном демодуляторе 11 в соответствии с сигналами управления, поступающими с выхода запоминающего блока 5, входная аналоговая последовательность импульсов одного и того же знака (в рассматриваемом примере положительного знака) преобразуется в требуемую последовательност импульсов заданной длительности, амплитуд и их знаков.

Так как отрицательным значением амплитуд формируемой последовательности импульсов соответствует уровень логической 1 с выхода запоминающего блока 5, то при поступлении последнего на управляющий вход .ключа 19 производится подключение инвертирующего входа операционного усилителя 15 к общей щине .и переключение режима работы его с неинвертирующего на инвертирующий без изменения коэффициента передачи,оравного единице.

На выходе операционного усилителя 15 при этом в соответствии с тактовыми импульсами с выхода коммутатора 9 будет формироваться требуемая последовательность заданных длительностей, амплитуд и знаков.

При совпадении выходного двоичного кода дешифратора 12 с ранее выбранным кодом коммутатора 13, что соответствует моменту окончания длительности формирования выбранной последовательности импульсов, на выходе последнего формируется уровень логической 1, которым через эле-, мент ИЛИ 14 счетчик 3 обнуляется, и цикл формирования заданной последовательности импульсов повторяется аналогично описанному.

Останов цикла формирования последовательности импульсов в режиме автоматического вывода информации осуществляетсяустановкой тумблера 30 блока 4 управления в исходное состояние.

(Риг.2

7

Ш

30

f

Jt

t2

J-o«/ Л

R

m

32

JJ

v

Ччх

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

| Цифровой генератор функций | 1986 |

|

SU1388842A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для передачи электрокардиосигнала по телефону | 1985 |

|

SU1286158A1 |

| РАДИОСТАНЦИЯ | 2004 |

|

RU2280950C2 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

| Цифровой демодулятор частотно-манипулированных сигналов | 1982 |

|

SU1058083A1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ, содержащее генератор импульсов, блок управления, двоичный счетчик, первый запоминающий блок, блок ввода данных, отличающееся тем, что, с целью расширения динамического диапазона формируемых последовательностей импульсов и функциональных возможностей, в него введены второй запоминающий блок, делитель частоты, первый и второй коммутаторы, первьй и второй элементы ИЛИ, цифроаналого- вый преобразователь, амплитудный демодулятор и дешифратор, причем первый выход генератора импульсов подключен через последовательно соединенные делитель частоты, первый коммутатор и первый элемент ИЛИ к первому входу двоичного счетчика, выходы которого подключены к первым входам запоминающих блоков и через дешифратор к входам второго коммутатора, выход которого через второй элемент ИЛИ соединен с вторым входом двоичного счетчика, второй вход второго элемента ИЛИ соединен с первым выходом блока управления, второй выход -которого подключен ко второму входу делителя частоты, третий выход блока управления соединен с входами Запись-считывание первого и второго запоминающих блоков, вторые входы второго запоминающего блока подключены к группе выходов блока ввода данных,первьй выход которого соеди(Л нен с вторым входом первого элемента ИЛИ, второй выход блока ввода данных с соединен с входом первого запоминающего блока, выход которого подключен к первому входу амплитудного демодулятора, второй вход которого через цифроаналоговый преобразователь Ob tsD соединен с выходами второго запоминающего блока,при этом вход блока ввода Од данных соединен с входом блока управлеОд 00 ния и с вторым выходом генератора импульсов.

| Формирователь импульсных последовательностей | 1978 |

|

SU790197A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-09-30—Публикация

1984-01-25—Подача