Изобретение относится к технике связи и может использоваться для приема дискретной информации в устройствах телеуправления, телеконтроля и системах передачи кодированных сообщений.

Известен демодулятор волн, модулированных .по частоте, для систем передачи двоичной информации, содержащий полоссвой фильтр, амплитудный ограничитель,, формирователь импульсов, генератор стабильных импульсов, пороговое устройство, счетчик, запоминсцощее устройство и цифроаналЬговЫй преобразователь И

Однако устройство не обладает высокой помехоустойчивостью, так как при обработке сигнала в цифроаналоговом преобразователе не определяется какой полосе частот принадлежит- обрабатываемый сигнгш.

Наиболее близким по технической сущности к предлагаемому является цифровой демодулятор частотно-манипулированных сигналов, содержащий решающий блок, последовательно соединенные полосовой фильтр, ограничитель и формирователь управляющих импульсов, ген-ератор опорных импульсов, выход которого подключен к первому входу первого делителя частоты, выходы которого соединены с входами первого депХифратора и блока определения рабочей полосы частот 2 .

Недостаток известного демодулятора - низкая точность демодуляции.

Цель изобретения - повышение точности демодуляции.

Для достижения поставленной цели в цифровой демодулятор частотноманипулированных сигналов, содержащий решающий блок, последовательно соединенные полосовой фильтр, ограничитель и формирователь управляющих импульсов, генератор опорных импул1зсов, выход которого под-, ключен к первому входу первого делителя частоты, выходы которого соединены с входс1ми первого-дешифратора и блока определения рабочей полосы частот, введены анализатор амплитуды, элемент И,, два элемента задержки, два блока управления, два элемента ИЛИ, два реверсивных счетчика, второй и третий дешифраI торы, два триггера, формирователь допусковых интервалов, блок сравнекия и второй делитель частоты, первый вход и выход которого соединены соответственно с выходом генератора опорных импульсов и с первыг входом блока сравнения, выходы которого поключены к входам первого блока управления, выходы которого соединены с вторым и третьим входами второго делителя частоты, четвертый вход которого соедии тн с выходом первого

триггера и с первым входом решающего блока, второй и третий входы которого соединены соответственно с выходом второго делителя частоты и с выходом второго триггера, который соединен 5 с первым входом формирователя допусковых интервалов, первый выход котоп рого подключен к второму входу блока сравнения, третий вход которого соединен с вторым выходом формирова:те10 ля допусковых интервалов и с первым входом первого триггера, второй вход которого соединен с выходом анализатора ш 1плитуды, к входу которого подключен выход полосового фильтра, 5 и с лервь. входом элемента И, второй и третий входы которого соединены соответственно с первым выходом блока определения рабочей полосы частот и с ВЫХОДСМ4 формирователя управлякщих

д импульсов,, который соединен с входом первого элемента задержки, выход которого подключён к второму входу первого делителя частоты, при этом второй вы:4од блока определения рабочей полоса частот подключен к первым входсил первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с первыми выходами второго и трютьего дешифраторов, входы которых соединены соответст0 венно с В1:лходами первого и второго реверсивных счетчиков, первые входы которых соединены соответственно Q выходами первого и втор.ого элеменIтов ИЛИ, а выход элемента И подклю5 чен к вторым входам первого и второго реверсивных счетчиков, к третьим входам которых подключены выходы . второго блока управления, и к входу второго элемента задержки, выход

0 которого подключен к соответствующим входам второго и третьего дешифраторов, вторые выходы которыэс подклю.чены к входам второго триггера, при;чем выходы первого дешифратора сОес динены с входами второго блока уп равления, третий выход второго дешифратора подключен к второму входу фврмирователгг допусковых интервалов.

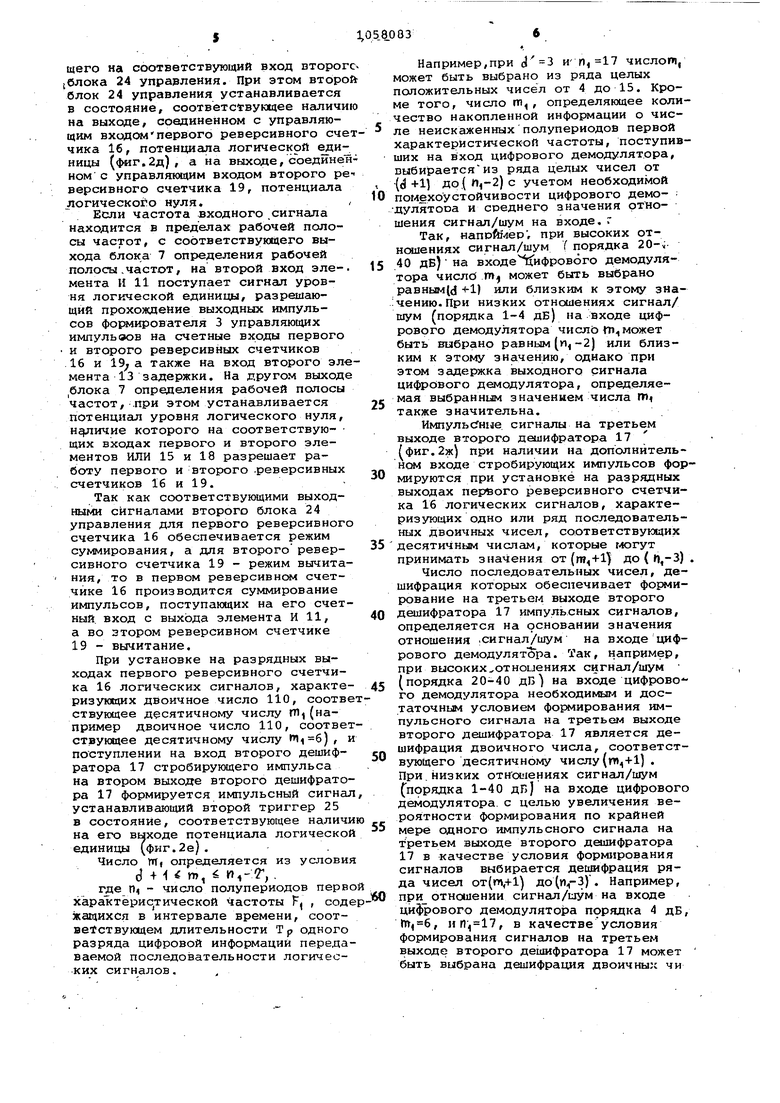

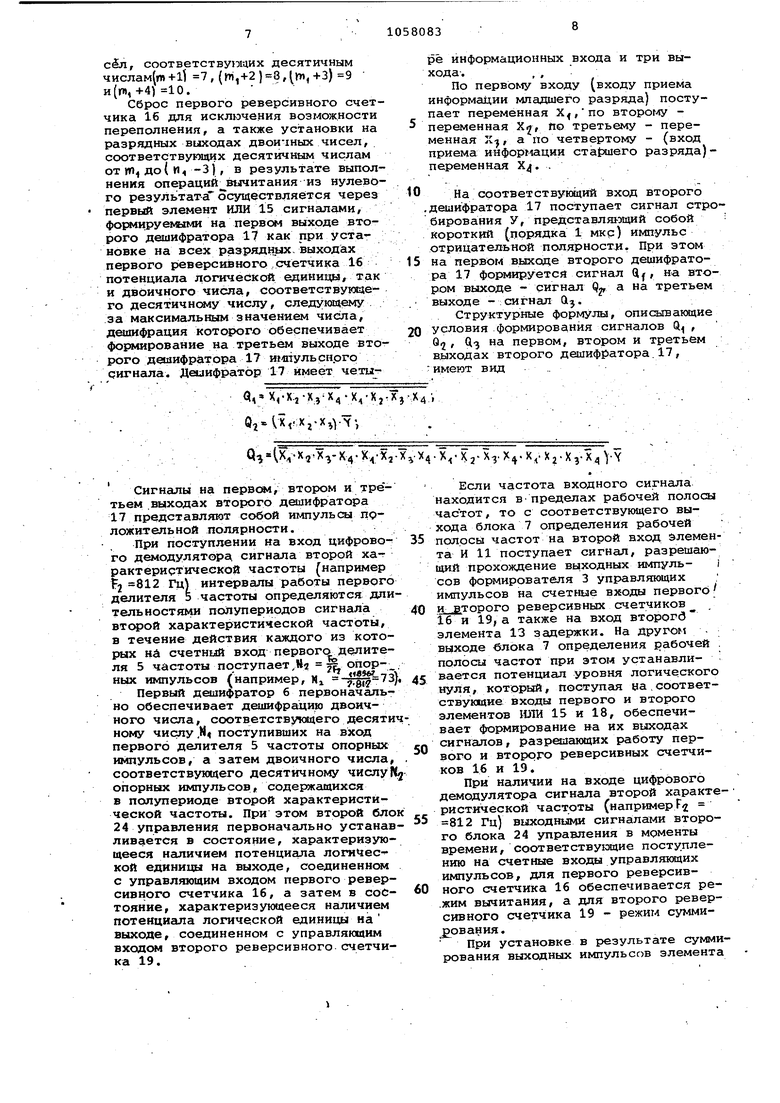

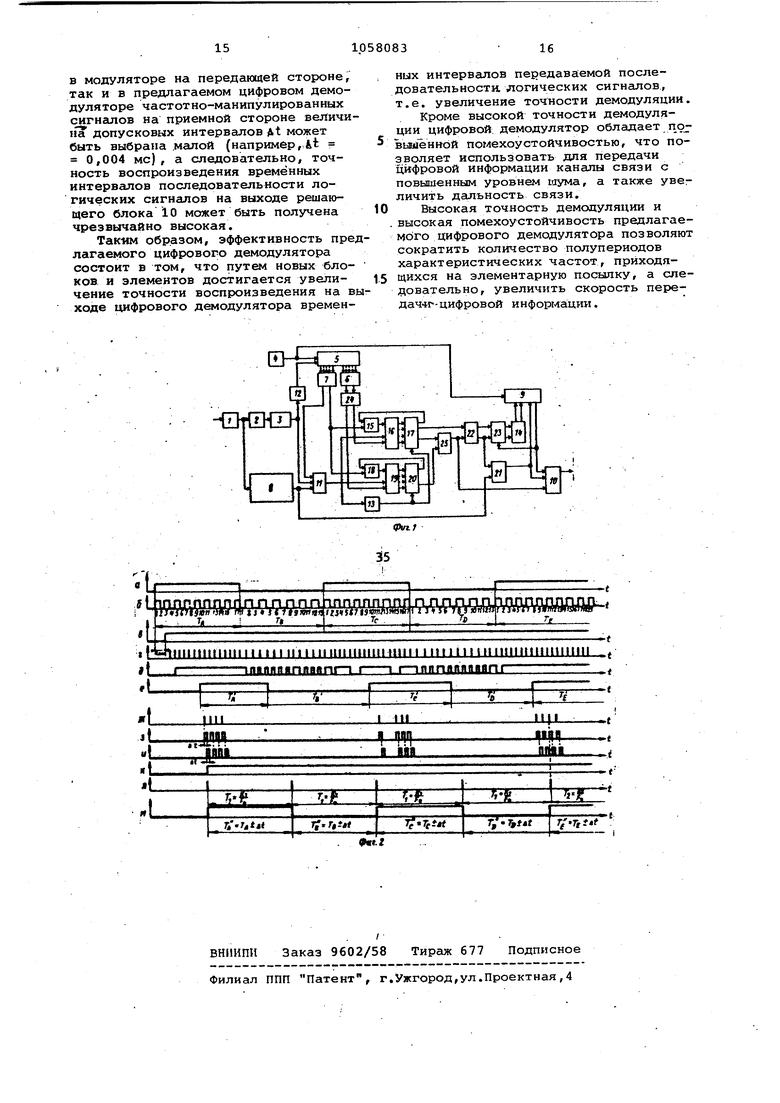

На фиг.1 представлена структурная электрическая схема демодулято0 ра; на Фиг. 2 - эш-зры напряжений, поясняющие его работу.

Демодулятор содержит полосовой фильтр 1, ограничитель 2, формирователь 3 управляющих импульсов, генератор 4 опорных импульсов, первый делитель 5 частоты, первый дешифратор Б, блок 7 определения рабочей полосы Чс1стот, анализатор 8 амплитуды, -второй делитель 9 частоты, решающий блок 10, элемент И 11, первый и второй элементы 12 и 13 задержки, соответственно, первый бЛок 14 управления,, первый элемент ИЛИ 15, первый рб версивный счетчик 16,

5 второй дешифратор 17 стробирующего импульса, второй элемент ИЛИ 18, второй реверсивный счетчик 19, третий дешифратор 20, пер вый триггер 21, формирователь 22 . допусковых интервалов, блок 23 сравнения, второй блок 24 управления и второй триггер 25. Цифровой демодулятор работает следующи1 1 образом. При поступлении на вход цифрового демодулятора одновременно с напряжением шума частотно-манипулированного сигнала, соответствующего передаваемой последовательности логических сигналов (фиг.2а) и представляющего собой чередовакие первой (например, Fj 1062 Гц) и второй (например 2 812 Гц) характеристических частот, на выходе ограничителя 2, стоящего после полосового фильтра 1, формируются прямоугольные импульсы (фиг.2б) длительности и интервалы следовани которых определяются моментами про хождения через нулево е значение, или близкое к нулевому, напряжения выходного сигнала. Ограничитель 2 обладает широким динамическим диапазоном (порядка 60 дв) и обесп чивает высокую крутизну фронтов вы ходных импульсов, уменьшающую неоднозначность моментоб срабатывани последукндах блоков. Если уровень частотно-манипулированного сигнала на выходе полосо вого фильтра 1 превыиает напряжение Упор Р батывания анализатора 8 амплитуды (например, в) , на его выходе через интервал време ни 1д,,, определяемый временем анализа амплитуды, формируется сигнал логического уровня, например уровня логической единицы (фиг.2в). Пр этом теряется информация о длитель ностях целого числа 3 первых полупериодов (например, d 3), поступи шей на вход цифрового демодулятора последовательности характеристических частот (фиг.2б,в,г). Целое число (J полупериодов, информация о длительностях которых т ряется при анализе амплитуды входн го сигнала анализатором В амплитуды, определяется по высшей из характеристических частот. Число полупериодов .j первой (высшей) характеристической частоты, приходящихся на интервал времени t , опр деляется из выражения dH,., HanpiD-iep, приЬ н 1гЗ мс и FI ; 1062 1,310. 2 1062 2,77. Число d d определяется как бли жаШЮе целое число к значению числа 6, например, npiid 2,77 числоd Анализатор 8 амплитуды формирует на .выходе сигналы логических уровней. Он обладает высокой стабильностью порога, срабатывания и возожностью регулировки его в широких пределах. Сигнал уровня логической единицы, поступаквдий с выхода анализатора 8 амплитуды на первый вход элемента И 11 и на соответствующий вход первого триггера 21, обеспечивает разрешение на их работу. В моменты времени, определяемые фронтами выходных импульсов ограничителя 2, формирователь 3 управлягацих импульсов вырабатывает короткие, импульсы (фиг. 2г} , длительность каждого из которых на несколько порядков (по крайней мере на два порядка) меньше длительности полупериода высшей из принимаемых характеристических частот. Формирователь 3 управляющих импульсов обеспечивает формирование коротких (порядка 1 мкс) управляющих импульсов в моменты времени, определяемые как положительными, так и.отрицательными фронтами входных импульсов, причем длительность каждого из соответствующих его элементов стабильна во времени при изменений напряжения питания и температуры окружающей среды. Первый элемент 12 задержки обеспечивает задер ;ску выходных импульсов формирователя 3 управляющих импульсов на время, равное или несколько большее их длительности (например, на время порядка 2 мкс. Интервалы между выходными И1.тульсами первого элемента 12 задержки являются интервалами работы первого делителя 5 частоты,на счетный вход которого поступают и myльcы от стабильного генератора 4 опорных импульсов вырабатывающего прямоугольные импульсы с частотой следования f0(например, FQ 118562 Гц). При поступлении на вход цифрового демодулятора сигнала первой характеристической частоты (например, FI 1062 Гц интервалы работы первого делителя 5 частоты определяются длительностями долупериодов сигнала первой характеристической частоты, в течение действия каждого из которых . на счетный вход первого делителя 5 частоты поступает tj опорных импульсов например, N - 5б) Первый дешифратор 6 обеспечивает дешифрацию двоичного числа, соответствующего десятичному числу опорных импульсов (например числа 111000, соответствукядего десятичному числу 56), содержащихся в полупериоде первой характеристической частоты, и формирование на соответствующем импульсного сигнала, поступающего на соответствующий вход второг блока 24 упрарления. При этом второ блок 24 управлеиия устанавливается в состояние, соответствуквдее наличи на выходе, соединенном с управляющим входомпервого реверсивного сче чика 16, потенциала логической единицы (фиг.2д), а на выходе, соединё ном с управляющим входом второго pe версивного счетчика 19, потенциала логическо1::о нуля.. Если частота входного .сигнала находится в пределах рабочей полосы частот, с соответствующего выхода блока 7 определения рабочей полосы .частот, на второй вход элемента И 11 поступает сигнал уровня логической единицы, разрешающий прохождение выходных импульсов формирователя 3 управляющих импульвов на счетные входы первого и второго реверсивных счетчиков 16 и 19 а также на вход второго эле мента 13 задержки. На другОлМ выход блока 7 определения рабочей полосы частот, .при этом устанавливается потенциал уровня логического нуля, которого на соответствующих входах первого и второго элементов ИЛИ 15 и 18 разрешает работу первого и второго -реверсивных счетчиков 16 и 19. Так как соответствующими выходными сигнапами второго блока 24 управления для первого реверсивного счетчика 16 обеспечивается режим суммирования, а для второго реверсивного счетчика 19 - режим вычитания, то в первом реверсивном счетчике 16 производится суммирование импульсов, поступающих на его счетный, вход с выхода элемента И 11, а во втором реверсивном счетчике 19 - вычитание. При установке на разрядных выходах первого реверсивного счетчика 16 Логических сигналов, характе ризующих двоичное число 110, соотве ствующее десятичному числу т, (например двоичное число 110, соотве ствующее десятичному числу ), и поступлении на вход второго дешифратора 17 стробирующего импульса на втором выходе второго дешифрато ра 17 формируется импульсный сигнал устанавливающий второй триггер 25 в состояние, соответствующее наличи на его выходе потенциала логическо единицы (фиг.2е). Число Wf определяется из услови с) - №, , . где Пч - число полупериодов перв характёрис тической частоты F, , сод жаадихся в интервале времени, соответствующем длительности Тр одного разряда цифровой информации переда ваемой последовательности логических сигналов. Например,при ( и г),17 числогч, может быть выбрано из ряда целых положительных чисел от 4 до 15. Кроме того, число т,, определяющее количество накопленной информации о числе неискаженных полупериодов первой характеристической частоты, поступивших на вход цифрового демодулятора, выбираетсяиз ряда целых чисел от (d+1 до,{ ) с учетом необходимой помехоустойчивости цифрового демо- дулятооа и среднего значения отношения сигнал/шум на входе.г Так, HanoftfviepV при высоких отнсянениях сигнал/шум Т порядка 20-v 40 ДБ) на входе ифрового демодулятора число т может быть выбрано равным(1 н-1) или близким к этому значению.При низких отношениях сигнал/ Егум (порядка 1-4 дв) на входе цифрового де;модулятора число Ш, может быть выбрано равным (м,-2) или близким к этому значению, однако при этом задержка выходного сигнала цифрового демодулятора, определяемая выбргшным значением числа т также значительна. ИмпульсГшае сигналы на третьем выходе второго дешифратора 17 фиг.2ж) при наличии на дополнительном входе; стробирующих импульсов формируются при установке на разрядных выходах перйого реверсивного счетчика 16 логических сигналов, характеризующих одно или ряд последовательных двоичных чисел, соответствующих десятичным числам, которые г-югут принимать значения от (т,+1 до ( Ц,-3) . Число последовательных чисел, дешифрация которых обеспечивает формирование на третьем выходе второго дешифратора 17 импульсных сигналов, определяется на основании значения отношения .сигнал/шум на входе цифрового демодулят ора. Так, например, при высоких отноиениях сигнал/шум (порядка 20-40 дБ) на входе цифрово го демодулятора необходимыгл и достаточн Л«1 условием формирования импульсного сигнала на третьем выходе второго дешифратора 17 является дешифрация двоичного числа, соответствующего десятичному числу (гп,+1) . При. низких отн оиениях сигнал/шум (порядка 1-40 дП) на входе цифрового демодулятора, с целью увеличения вероятности формирования по крайней мере одного импульсного сигнала на третьем выходе второго дешифратора 17 в качестве условия формирования сигналов выбирается деишфрация ряда чисел от(т,+1) до() . Например, при отношении сигнал/шум на входе цифрового демодулятора порядка 4 дБ, п,6, иП,17, в качествеусловия формирования сигналов на третьем выходе второго дешифратора 17 может быть выбрана дешифрация двоичных чи

c&i, соответствушцих десятичным числам(|П+11 7, (Hi,+2) 8,(т,+3) 9 и(п1, +4) 10.

Сброс первого реверсивного счетчика 16 для исключения возможности переполнения, а также установки на разрядных выходах двоичных чисел, соответствующих десятичным числам от пп до( и, -3) , в результате выполнения операций вычитания из нулевого результата осуществляется через первый элемент ИЛИ 15 сигналами, формируемыми на первом выходе второго дешифратора 17 как при установке на всех разрядных, выходах первого р еверсивного счетчика 16 потенциала логической единицы, так и двоичного числа, соответствующего десятичному числу, следующему за максимальным значением числа, дешифрация которого обеспечивает формирование на третьем выходе второго дешифратора 17 импульсирго сигнала. Дааифратбр 17 имеет четыa,x;-x;j-x,X4-x,-Xj-lfj-.X4i Qj.i,.;Xj.

Q iX,.X,.XvX4-X ;X,-XvX4-X,.X;j.X3.X4.X,-Xj.X,.

Сигналы на первом, втором и третьем .выходах второго дешифратора 17 представляют собой импульсы положительной полярности.

При поступлении на вход цифрового демодулятора, сигнала второй ха-г рактериртической частоты (например Fj 812 Гц) интервалы работы первого делителя 5 частоты определяются длительностями полуперирдов сигнала втсфой характеристической частоты, в течение действия каждого из которых ни счетный вход первого.,делителя 5 частоты поступает .К опор-- frj %

ных импульсов (например. Hi ),

Первый дешифратор б первоначально обеспечивает дешифрацию двоичного числа, соответствукядего десятичному числу ,И« поступивших на вход первого делителя 5 частоты опорных импульсов, а затем двоичного числа, соответствующего десятичному числуГ(2 опорных импульсов, содержащихся в полупериоде второй характеристической частоты. При этом второй блок 24 управления первоначально устанавливается в состояние, характеризующееся наличием потенцигша логи 1еской единицы на выходе, соединенном с управляющим входом первого реверсивного счетчика 16, а затем в соСтояние, характеризующееся наличием потенциала логической единицы на выходе, соединенном с управляющим входом второго реверсивного счетчика 19.

ре информационных входа и три выхода. , . .

По первому входу (входу приема информации младшего разряда) поступает переменная Х(,по второго переменная Х, По третьему - переменная Xj, а по четвертому - (вход приема инфорГ1ации ставшего разряда)переменная Хд. На соответствунвдий вход второго дешифратора 17 поступает сигнал стробирования У, представляищий собой Короткий (порядка 1 мкс) импульс отрицательной полярности. При этом на первом выходе второго дешифратора 17 формируется сигнал Gl|, на втором выходе - сигнал Q-, а на третьем выходе -; сигнал й.

Структурные ФОРМУЛЫ, описывающие условия Формирования сигналов Q , Q г (1з на первом, втором и третьем выходах второго дешифратора.17, имеют вид ..

Если частота входного сигнала находится В пределах рабочей полосы частот, то с соответствующего выхода блока 7 определения рабочей полрсы частот на второй вход элемента И 11 поступает сигнал, разрешающий прохождение выходных импульСРВ формирователя 3 управляющих импульсов на счетные входы первого и дторогр реверсивных счетчиков 16 и 19, а также на вход второгб элемента 13 задержки. На другом выходе блока 7 определения рабочей полосы частот при этом устанавливается потенциал уровня логического нуля, которьЕй, поступая аа , соответствуквдие входы первого и второго элементов Ш1И 15 и 18, обеспечивает формирование на их выходах сигналов, разрешающих работу первого и вторрго реверсивных счетчиков 16 и 19.

При наличии на входе цифрового демодулятора сигнала второй характеристической частоты (напримерF 812 Гц) выходными сигналами второго блока 24 управления в моменты времени, соответству1СЕ1ие поступлению на счетные входы управляющих импульсов, для первого реверсивного счетчика 16 обеспечивается ре.жим вычитания, а для второго реверсивного счетчика 19 - режим суммирования.

При установке в результате суммирования В1лходных импульсов элемента

И 11 на разрядных выходах второго реверсивного счетчика 19 двоичного ..числа 100, соответствующего десятичному числу 1П7{например двоичного числа 100, соответствующего десятичному числу 4) , на втором выходе третье.

го дешифратора 20 формируется импульсный сигнал, устанавливающий второй триггер 25 в состояние, соответствующее наличию на его выходе потенциала логического нуля.

Сброс второг-о реверсивного счетчика 19 для исключения возможности переполнения, а также установки на разрядных выходах двоичного числа, соответствуквдего десятично 4у числу в результате вычитания, осуществляется сигналами, формируегфлми на первом выходе третьего дешифратора 20 как при установке на всех разрядных выходах второго реверсивного

счетчика 19 потенциала логической единицы, так и двоичного числа, соответствующего десятичному числу (например, при установке на разрядных выходах второго реверсивного счетчика 19 двоичного числа 1111, соответствующего десятичног.1у числу 15, и двоичного числа 101, соответ.ствующего десятичному числу 5 при

т,4.

Третий дешифратор 20 имеет четыре информационных входа и два выхода. По первому входу (входу приема информации младшего разряда) поступает переменная Z , по второму BXQду - переменная 7,/ , по третьему входу переменная Z , а по четвертому входу (входу приема информации старшего разряда) - переменнаяZ

На соответствующий вход третьего дешифратора 20 поступает сигнгш стробирования 3 , представляющий собой короткий (порядка 1 мкс) импульс отрицательной полярности. На первом выходе третьего дешифратора 20 формируется сигнал В| , а на втором выходе - сигнал Bj.

Структурные формулы, описывающие. условия формирования сигналов В и Вд на первом и втором выходах соответственно третьего дешифратора 20, имеет вид

D Z;,25 Z42.,Z22i-j )

ВтЧ.-гг з Сигналы на первом и втором выходах третьего дешифратора 20.представляют собой импульсы положительной полярности.

Стробирование второго и третьего дешифраторов 17 .и 20 выходными импульсами сигналами первого элемента 12 задержки, задержанными по отношению к импульсам, поступающим на счетнрле входы первого и втоiporo реверсивных счетчиков 16 и 19 на время порядка 2 мкс несколько большее,чем время установления последовательно соединенных соответствующих реверсивного счетчика и 5 дешифратора, исключает возможность ложной дешифрации чисел и обеспечивает возможность сохранения информации о временных характеристиках входного сигнала.

10 При поступлении на вход цифрового демодулятора чередующейся в соответствии с передаваемой цифровой информацией последовательности первой и второй i характеристических час5 тот на выходе второго триггера 25

формируется последовательность логических сигналов, соответствукицая передаваемой последовательности логических сигналов, но имеющая знаQ чительные временные искгикения вследствие воздействия напряжения шума или помехи при прохождении по каналу связи. Выходной сигнал второго триггера 25 поступает на соответст5 вующий вход формирователя 22 допусковых интервалов и на третий вход решающего .блока 10.

Формирователь 22 допусковых интер валов при поступлении на другой вход и fflyльcнoгo сигнала с третье го выхода второго дешифратора 17 обеспечивает формирование на соответствующих выходах игтульсных сигналов, длительность Ai каждого из которых (фиг.2з,и.| определяет ве5 пичину допустимого отклонения длительностей элементарных логических сигналов Hci выходе цифрового демодулятора от длительностей соответствующих пер€:даваег«лх логических сиг0 налов.

При прохождении частотно-манипулированного сигнала по каналу связи длительности отдельных полупериодов характеристических частот под воз5 действием ujyMa оказываются искаженными, причем чем ниже отношение сигнал/шум,, на входе цифрового демодулятора,, тем большее число полупериодов характеристических частот имеют отклонения по длительности

от исходного значения, соответствующего передаваемой характеристической частоте.

Пусть передаваемая последовательность логических сигналов 101011... Предположим, что на интервале времени Тд(фиг.2б), соответствующем передаче уровня логической единицы, искажены полупериоды, обозначенные цифрами 1,2,3, на интервале времени Тр, соответствующем передаче уровня Логического нуля, искгикены полупериоды 8 и 13, на интервале времени Tg - полуперисды 1,5,6,13 и 14, на интервале времени Тр - полупериоды

4 и 12, а на интервале времени Tg искажения отсутствуют.

При npHet-ie такого частотно-маниплированного сигнала, имеющего искажения длительностей полупериодов

:характеристических частот, сигнал на управляющем входе первого реверсивного счетчика 16 имеет вид, показанный на фиг.2д а выходной сигнал второго триггера 25 имеет вид, -показанный на фиг.2 е. Моменты формирования импульсных сигналов

на третьем выходе второго дешифратора 17 определяются поступлением на дополнительный вход импульсов стробирования с выхода второго элемента Зсшержки 13, которые имеют постоянную задержку по отношению к фронтам входного сигнала первой характерис- тической частоты. Последнее обстоятельство позволяет производить автоматическую подстройку интервалов следования выходных импульсов второго делителя 9 частоты с целью обепечения соответствия длительности каждого из интервалов длительности одного разряда Тр передаваемой последовательности логических сигнало например, Т. 8 мс) .. В предлагаемом ифровом демодуляторе подстройка интервалов следования выходных импульсов BTQporo делителя 9 частоты прюизводится с помощью формирователя 22 допусковых интерв,с1Лов, блока 23 сравнения и певого блока 14 управления. Первый импульсный сигнал, формируемый на третьем выходе второго де1Я1фратора 17, от начала поступления на вход частотно-манипулированного сигнсша обеспечивает запуск формирователя 22 допусковых интервалов.

Так как начало приема частотноманипулированного сигнала характеризуется наличиет на выходе анализатора 8 амплитуды потенциала логической единицы ГФИГ.2 в), поступающего на соответствующий вход первого триггера 21, то при поступлении с соответствующего выхода формирователя 22 допусковых интервалов на другой вход первого триггера 21 импульсного сигнала (фиг. 2 и):первый триггер 21 устанавливается в сотояние, характеризующееся наличием иа выходе потенциала логической единицы (фиг.2 к) . Шлходной сигнал первого триггера 21, поступая на. установочный вход второго делителя 9 частоты, разрешает его работу.

Так как установка первого триггера 21 в состояние, соответствующее наличию на выходе потенциала логической единицы , производится при приёме сигнала первой характеристической частоты, то передним

фронтом выходного сигнала первого триггера 21 осуществляется установка решающегойлока 10 при наличии на третьем входе потенциала логической единицы в состояние, характеризующееся наличием на его выходе потенциала логической единицы (фиг. 2 ).

Суммарное время задержки формирования на выходе решающего блока 10

0 оигнала логической единицы по отно шению к соответствующему фронту сигнала первой характеристической частоты без учета задержки, определяемой быстродействием логических

5 элементов, может быть определено из .выражения

tjt: iSt-vti,

где bt - длительность выходных импульсов формирователя 22 допускоQ вых интервалов, определяющая величину допустимого уменьшения периода следования выходных импульсов второгЪ делит-еля 9 частоты,

iif - время задержки сигнала 5 вторым элементом 13 задержки.

Величины &i и i, постоянны, поэтому временные характеристики выходного сигнала решающего блока 10 связаны с временными характеристиками входного частотно-манипулированного сиг нала цифрового демодулятора.

Одновременно с установкой на выходе первого триггера 21 потенциала логической единицы начинает работу второй делитель 9 частоты, на счетный 5 вход которого поступают опорные импульсы с частотой еледования д (например FO 118562 Гц.

Коэффициент деления второго делителя 9 частоты определяется выход0 ными сигналами первого блока 14 управления.

Начало втЬрого делителя 9 частоты определяется поступлением потенциала логической единицы на его соот5 ветствукядий вход. При этом на выходе второго делителя 9 частоты формируется короткий импульс, временное положение которого относительно момента поступления разреыаквдего сигнала на его установочный вход опре-. деляется коэффициентом деления К, 948.

При наличии на управляющем входе второго делителя 9 частоты, потенциала логической единицы-и при поступлении на его счетный вход девятьсот сорока девяти импульсов на выходе формируется короткий импульс, временное положение которого относительно предшествующего выходного импульса

определяется коэффициентом деления К2 949.

.Второй делитель 9 частоты является делителем частоты с программируемым (перестраиваемым-) коэффициентом деления. Пусть в исходном состоянии коэф фициент деления второго делителя 9 частоты имеет значение К|/например ), определяемое наличие потенциала логической единицы на с ответствуюй;ем управляющем входе. При этом интервалы следования Т в ходных импульсов второго делителя9 частоты, поступающих Иа второй вход решающего блока 10 и на допол нительный вход блока 23 сравнения, . определяются из выражения i Например, при Ki 948 и ,го 118562 Гц Т П«562 При длительности одного разряда передаваемой последовательности логических сигналов Тр(например Тр 8мс) и коэффициенте деления вто рого делителя 9 частоты К погрешность воспроизведения длительности одного разряда на выходе решающего блока 10 определяется из выражения utc, -Т, . Например, при Тч 7,966 мс (8-7,966) мс 0,004 мс. I Еслипри приеме сигнала первой характеристической частоты искажен .длительность значительной части по лупериодов например, на интервале Т искажены длительности полупериодов 1,5,6,13 и 14 , то короткий вы. ходной импульс второго делителя 9 частоты не совпадает во времени ни с одним из допусковых интервалов (фиг.2з,и,л). При этом сигналы на выходах блока 23 сравнения не форми руются, а следовательно, не изменяются управляющие сигналы на выходах первого блока 14 управления и изменение коэффициента, деления второго делителя 9 частоты не произво дится. в случае, если выходной импульс второго делителя 9 частоты совпадает по времени (фиг.2 з,и,л) с вы ходным импульсом формирователя 22 допусковых интервалов, определяющим величину допустимого уменьшения периода следования выходных импульсов второго делителя 9 частоты, то на соответствуклцем выходе блока 23 сравнения формируется импульсный сигнал, обеспечивающий изменение сигналов на выходах первого блока 14 управления, а следовательно, изменеШге коэффициента деле ния второго делителя 9 частоты. При этом во втором делителе 9 часто устанавли1 ается новый коэффициент деления К2.Интервалы следования Т,; выходных ш-шульсов второго делителя 9 частот при установке коэффициента деления К определя1этся из выражения fri .. jT Например,при и Я 11б5ё2 Гц мс. -; При длительности одного разряда передаваемой последовательности логических сигналов Тр и коэ.ффициенте делениявторого делителя 9. частоты К,) погрешностьй к воспроиаведения длительности одного разряда на выходе ререшающего блока 10.определяется из выражения . U KI-TI-TO Например, при 1 8,004 Mcftti/, 8,004-8 0,004 мс. .1 Максимальная погрешностьД оспроизведения длительности одного разряда передаваемой последовательности логических сигнало.в на выходе решающего блока 10 определяется максимальной из величин it или л1к, причем, если ь1(( it jj,, ОЛЬдлакс , , то MWkcAtKZ - . Величине it допусковых интервалов определяемая длительностями выходных импульсов формирователя 22 допусковых интервалов, зависит от максимально возможного числа М последовательно и непрерывно передаваемых элементарных;посылок второй ха-. рактеристической частоты (частоты, соответствующей передаче уровня логического нуля в передаваемой последовательности характеристических частот. Длительность д1 выходных импульсов формирователя 22 допусковых интервалов определяется из выражения лим. Например, при М 10 , . 0,004 мс л1 : 10-0,004 - 0,04 мс. Выходные импульсы Дфиг.2 л)) второго делитешя 9 частоты, поступая на второй вход решающего блока 10, обеспечивают в зависимости от сигнала, поступающего на третий вход,формирование на его выходе последовательности логических сигналов (фиг.2 м) соответствующей передаваемой последовательности элементарных логических сигналов. Длительность каждого из разрядов последовательности логических сигналов на выходе решающего блока 10 отличается от длительности соответствующего разряда передаваемой последовательности, логических, сигналов на величину, не превышающую длительности it выходных импульсов, формирователя 22 допусковых интервалов. При использовании высокостабильных генераторов опорных импульсов, содержащих кварцевые резонаторы, как в модуляторе на передающей стороне так и в предлагаемом цифровом демодуляторе частотно-манипулированных сигнгшов на приемной стороне величи liaT допусковых интервгшов Д1 может быть выбрана .малой (например,it 0,004 мс), а следовательно, точность воспроизведения временных интервалов последовательности логических сигналов на выходе решающего блокаЮ может быть получена чрезвычайно высокая. Таким образом, эффективность пр лагаемого цифрового демодулятора состоит в том, что путем новых бло ков и элементов достигается увеличение точности воспроизведения на ходе цифрового демодулятора времен ных интервалов передаваемой последователь ностн логических сигналов, т.е. увеличение точности демодуляции. Кроме высокой точности демодуляции цифровой, демодулятор обладает. выоённбй помехоустойчивостью, что позволяет использовать для передачи цифровой информации каналы связи с повышенным уровнем шума, а также увег личить дальность связи. Высокая точность демодуляции и высокая помехоустойчивость предлагаемого цифрового демодулятора позволяют сократить количество полупериодов характеристических частот, приходящихся на элементарную посыпку, а следовательно, увеличить скорость передач4г-цифровой информа ции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОТКЛОНЕНИЙ ПАРАМЕТРОВ ПРИ ДОПУСКОВОМ КОНТРОЛЕ | 2016 |

|

RU2617982C1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1985 |

|

SU1241486A1 |

| Цифровой демодулятор сигналовчАСТОТНОй ТЕлЕгРАфии | 1979 |

|

SU794764A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1987 |

|

SU1427419A2 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР РАДИОИМПУЛЬСОВ (ВАРИАНТЫ) | 2021 |

|

RU2775053C1 |

| Устройство для измерения скорости изменения температуры | 1989 |

|

SU1643954A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1998 |

|

RU2136114C1 |

ЦИФРОВОЙ ДЕМОДУЛЯТОР ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ, содержащий реааающйй блок, последовательно соединенные полосовой фильтр, ограничитель и-формирова тель упра вляквдих импульсов, генератор опорных импульсов, выход которого подключен к первс |у входу первого делителя частоты, выходи которого соединены с входами первого дешифратсфа и блока определения рабочей полосы частот, о т ли чающийся тем, что, с целью повыаения точности демодуляции, вве. дены анализатор амплитудьГ элемент .И, два элеме11та задержки, два блока управления, два элемента ИЛИ, два реверсивных бчетчика, второй и третий д 1тфраторы, два триггера, формирователь допусковых интервалов, блок сравнения и второй делитель частоты, первий вход и выход которого соединены соответственно с выходом генератора опорных импульсов и с первым входом блока сравнения, которого подключены к входам первого блока управления, выходы которого соединены с ВТОЕЛЛМИ третьим входами второго делителя частбты, четвертый вход которого соединен с выходом первого триггера и с первым входом реиающего блока, второй и третий входы которого соединены соответственно с выходом второго де{Лителя частоты и с выходом второго Триггера, который соединен с первым входом формирователя допускових интервалов, первый выход которого подключен к второму входу блока сравнения, третий вход которого соединен с вторыг выходом формирователя допусковых интервалов и с первым входом первого триггера, второй вход которого соединен с выходом анализатора амплитуды, к входу которого подключен в,ыход полосового фильтра, и с первым входом элемента И, второй и третий входы которого соединены соответственно с первым выходом блока определения рабочей полосы частот и с выходом формирователя управляю. щих импульсов, который соединен с входом первого элемента задержки, вы -ffi ход которого подключен к второму (Л входу первого делителя частоты, при этом второй выход блока- определения рабочей полосы частот подключен к пер вым входам первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с первыми выходами второго и третьего дешифраторов, входы которых соединены соответственно с выходами первого и втоiporo реверсивных счетчиков, первые сд :входы которых соединены соответственно с выходами первого и второго эо элементов ИЛИ, а выход элемента И о подключен к вторым входам первого и второго реверсивных счетчиков, 00 к третьим входам которых подключесо ны выходы второго блока управления, и к входу второго элемента задержки, выход которого подключен к соответствующим входам второго и третьего дешифраторов, вторые выходы которых подключены к входам второго триггера, причем выходы первого дешифратора соединены с входами второго блока управления, третий выход второго дешифратора подключен к второму входу формирователя допусковых интервалов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| НЕРАСТВОРИМЫЙ АНОД ДЛЯ ЭЛЕКТРОЭКСТРАКЦИИ МЕТАЛЛОВ ИЗ ВОДНЫХ РАСТВОРОВ | 2003 |

|

RU2266982C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| (прототип). | |||

Авторы

Даты

1983-11-30—Публикация

1982-09-06—Подача