00

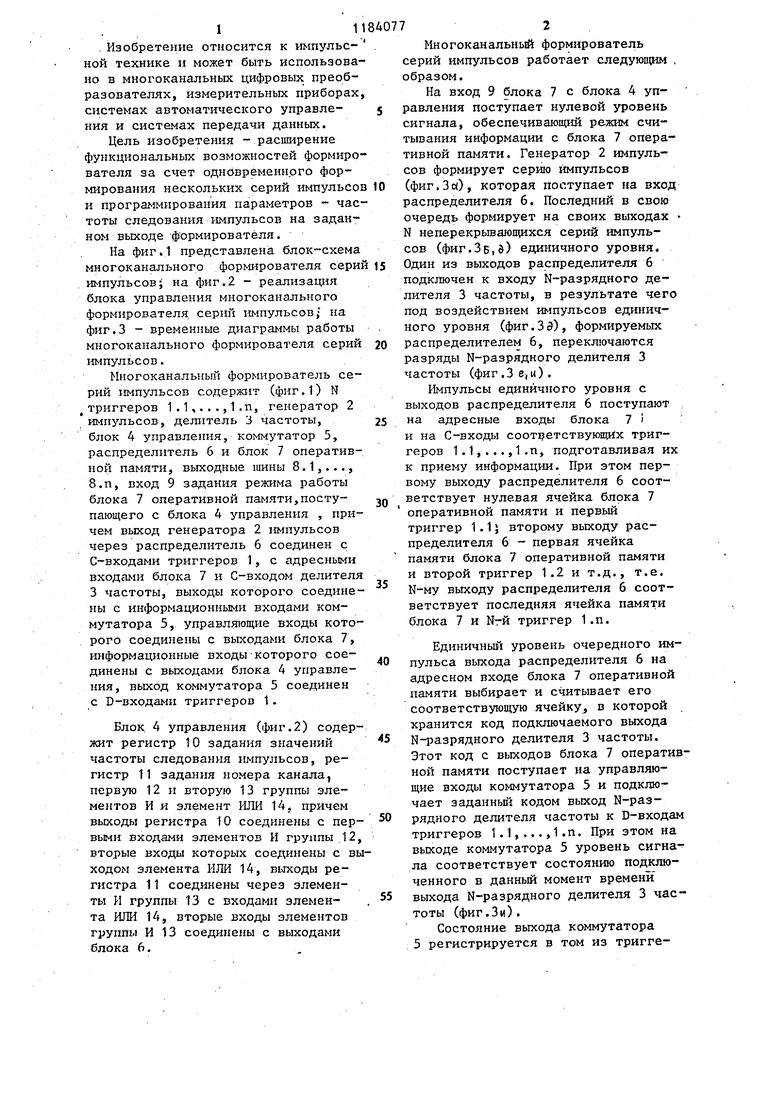

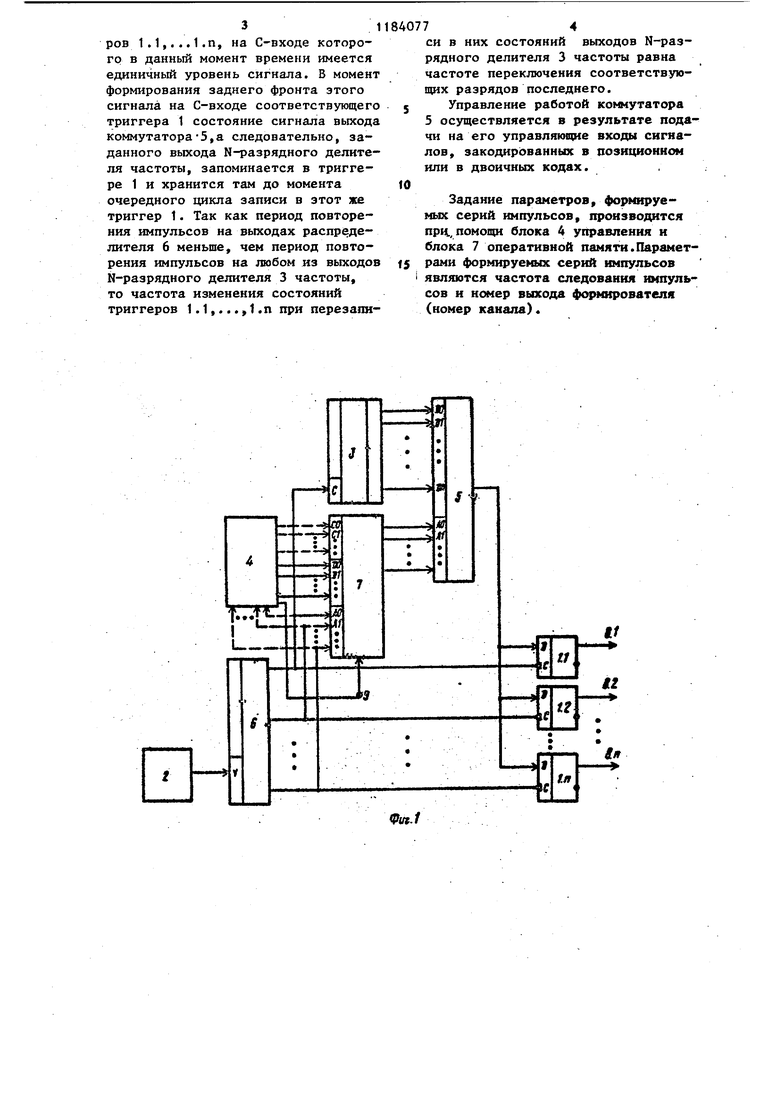

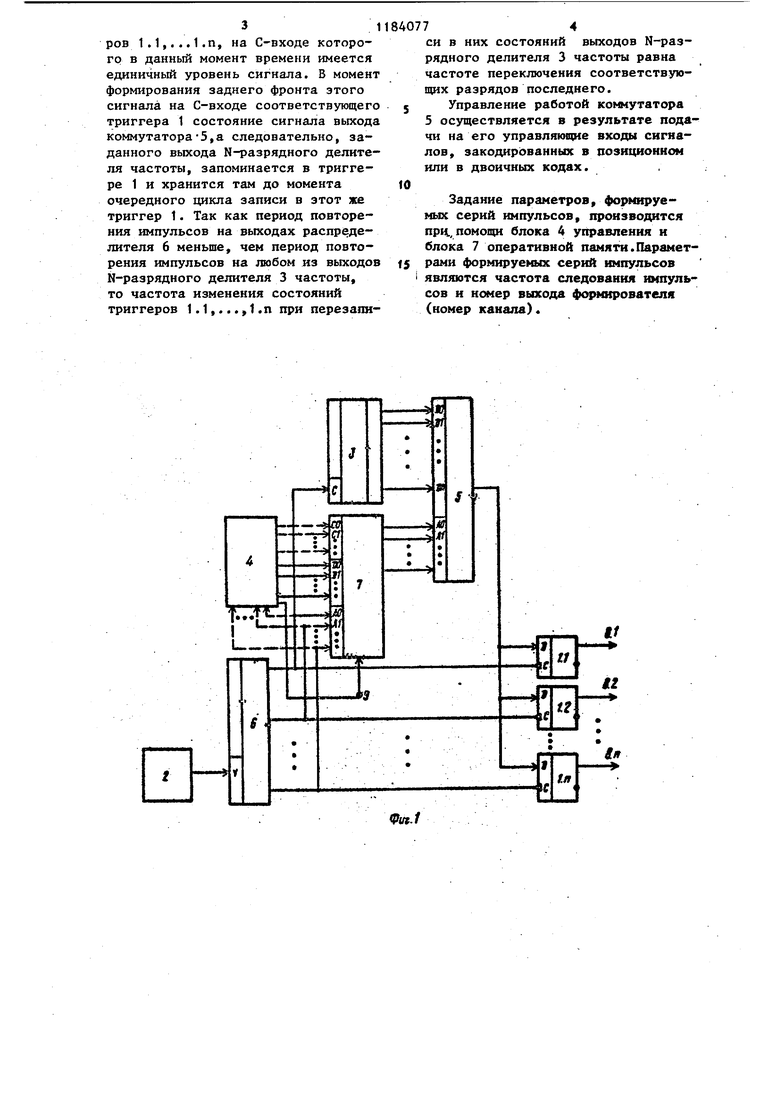

и о ч . Изобретение относится к импульсной технике и может быть использова но в многоканальных цифровых преобразователях, измерительных приборах системах автоматического управлеНИН и систамах передачи данньк. Цель изобретения - расиирение функциональных возможностей формиро вателя за счет одновременного формирования нескольких серий импульсо и программирования параметров - час тоты следования импульсов на задан ном выходе формирователя. На фигi1 представлена блок-схема многоканального формирователя сери импульсов; на фиг.2 - реализация блока управления многоканального формирователя, серий импульсов- на фиг.З - временные диаграммы работы многоканального формирователя серий импульсов. Многоканальный формирователь серий импульсов содержит (фиг.1) N триггеров 1.1,...,1.П, генератор 2 импульсов, делитель 3 Частоты, блок 4 управления, коммутатор 5, распределитель 6 и блок 7 оперативной памяти, выходные шины 8.1,..., 8.П, вход 9 задания режима работы блока 7 оперативной памяти,поступающего с блока 4 управления , причем выход генератора 2 импульсов через распределитель 6 соединен с С-входами триггеров 1, с адресными входами блока 7 и С-входом делителя 3 частоты, выходы которого соединены с информационными входами коммутатора 5, управляющие входы которого соединены с выходами блока 7, информационные входы-которого соединены с выходами блока 4 управления , выход коммутатора 5 соединен с D-входами триггеров 1. Блок. 4 управления (фиг.2) содержит регистр 10 задания значений частоты следования импульсов, регистр 11 задания номера канала, первую 12 и вторую 13 группы элементов И и элемент ИЛИ 14, причем выходы регистра 10 соединены с первьми входами элементов И группы 12, вторые входы которых соединены с вы ходом элемента ИЛИ 14, выходы регистра 11 соединены через элементы И группы 13 с входами элемента ИЛИ 14, вторые входы элементов группы И 13 соединены с выходами блока 6. Многоканальный формирователь серий импульсов работает следующим , образом. На вход 9 блока 7 с блока 4 управления поступает нулевой уровень сигнала, обеспечивающий режим считывания информации с блока 7 оперативной памяти. Генератор 2 импульсов формирует серию импульсов (фиг.Зи), которая поступает на вход распределителя 6. Последний в свою очередь формирует на своих выходах N неперекрьшающихся серий импульсов (ФИГ.ЗБ.Э) единичного уровня. Один из выходов распределителя 6 подключен к входу N-разрядного делителя 3 частоты, в результате чего под воздействием импульсов единичного уровня (фиг.ЗЭ), формируемых распределителем 6, переключаются разряды N-разрядного делителя 3 частоты (фиг .3 е, U). Импульсы единичного уровня с выходов распределителя 6 поступают на адресные входы блока 7 i и на С-входы соответствующих триггеров 1.1,...,1.п, подготавливая их к приему информации. При этом первому выходу распределителя 6 соответствует нулевая ячейка блока 7 оперативной памяти и первый триггер 1.1; второму выходу распределителя 6 - первая ячейка памяти блока 7 оперативной памяти и второй триггер 1.2 и т.д., т.е. N-му выходу распределителя б соответствует последняя ячейка памяти блока 7 и Ытй триггер 1.п. Единичный уровень очередного импульса выхода распределителя 6 на адресном входе блока 7 оперативной памяти выбирает и считывает его соответствующую ячейку, в которой хранится код подключаемого выхода N-разрядного делителя 3 частоты. Этот код с выходов блока 7 оперативной памяти поступает на управляющие входы коммутатора 5 и подключает заданньп кодом выход N-разрядного делителя частоты к D-входам триггеров 1.1,...,1.п. При этом на выходе коммутатора 5 уровень сигнала соответствует состоянию подключенного в данный момент времени выхода N-разрядного делителя 3 частоты (фиг.3м). Состояние выхода коммутатора 5 регистрируется в том из тригге3 1

ров 1 .1,...1.n, на С-входе которого в данный момент времени имеется единичный уровень сигнала. В момент формирования заднего фронта этого сигнала на С-входе соответствующего триггера 1 состояние сигнала выхода коммутатора-5,а следовательно, заданного выхода N-разрядного делителя частоты, запоминается в триггере 1 и хранится там до момента очередного цикла записи в этот же триггер 1. Так как период повторения импульсов на выходах распределителя 6 меньше, чем период повторения импульсов на любом из выходов N-разрядного делителя 3 частоты, то частота изменения состояний триггеров 1.1,...,1.П при перезапи840774

си в них состояний выходов N pa3рядного делителя 3 частоты равна частоте переключения соответствующих разрядов последнего. J Управление работой коммутатора 5 осуществляется в результате подачи на его управляющие входы сигналов, закодированных в позиционном или в двоичных кодах.

Задание параметров, формируемых серий импульсов, производится прч., помощи блока 4 управления и блока 7 оперативной памяти.Параметрами формируемых серий импульсов являются частота следования импульсов и номер выхода формирователя (номер канала).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

| Многоканальный коммутатор | 1984 |

|

SU1226644A2 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

МНОГОКАНАЛЬНЫЙ ФОРМИРОВАТЕЛЬ СЕРИЙ ИМПУЛЬСОВ, содержащий генератор импульсов, S триггеров, делитель частоты, блок управления, коммутатор, отличающийс я тем, что, с целью расширения функциональных возможностей,в него введены блок оперативной памяти и распределитель импульсов, вход которого соединен с выходом генератора импульсов, а N -выходы соединены соответственно с С -входами N триггеров и с адресными входами блока оперативной памяти, первый выход распределителя импульсов соединен с С-входом делителя частоты, адресные и информационные входы блока оперативной памяти соединены с соответствующими выходами блока управления, а вход управления блока оперативной памяти подключен к управляющему выходу блока управления, выходы блока оперативной памяти соединены с управляющими входами коммутатора, выход коммутатора соединен с сл D-входами N триггеров, информационные входы коммутатора подключены к выходам делителя частоты.

т- . :...

L n1rrH1

I/

- IZ

-

tit

Наёхобы CO..,CN5л.7 t ,.. t t

С ёыходо5 Ъл.6

Ьш:г.

иг.г

| Многоканальное устройство для формирования импульсов | 1975 |

|

SU690619A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 873399, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-10-07—Публикация

1983-09-07—Подача