Изобретение относится к контрольно-измерительной технике и предназначено для функционального контроля цифровых больших интегральных схем (БИС) при их массовом производстве.

Одним из основных требований, предъявляемых к оборудованию для контроля БИС, является обеспечение высокой производительности контроля. Известны устройства не в достаточной мере удовлетворяют указанйому требованию.

Известен ряд отечественных и зарубежных устройств для функционального контроля интегральных схем, осуществляющих контроль по программе, вырабатываемой посредством ЭВМ 1 .

Недостатком устройств является относительно низкая производительность контроля схем, состоящих из-одинаковых ячеек, например, типа БИС, ОЗУ, ПЗУ, РАЛУ, требующих одинакового режимного обеспечения и, следовательно, одинакового алгоритма контроля, формируемого с помощью специального генератора. Этот недостаток обусловлен тем, что условия контроля (частота контроля, величины напряжений источников питания, уровни входных воздействий, уровни компарации, временные соотношения и др.) остаются постоянными при переходе от одной ячейки к другой как при записи информации в контролируемую ячейку, так и при считывании. Т. е. известные устройства не позволяют перейти от одного режима контроля к другому внутри формируемой (анализируемой) тестовой последовательности. Например, при разбраковке БИС ОЗУ типа 581РУ4 на группы по быстро действию, а также при измерении быстродействия контроль БИС производят по заданному алгоритму контроля на заданной частоте. Так как данная БИС содержит 16- 10 ячеек памяти, то при ее контроле посредством алгоритма, бегущая «1 или «О требуется время 2;(1610) -f где f - частота функционального контроля. При частоте f 2МГц время контроля составит около 10 с. В случае установления неработоспособности объекта контроля на этой частоте в известных устройствах необходимо обращение к ЭВМ с целью получения новых исходных данных для контроля на другой частоте, причем весь процесс контроля повторяется с начального адреса, так как информация за вре.мя обращения к ЭВМ может быть утеряна для контролируемой БИС ОЗУ. Данное обстоятельство требует значительных временных затрат на контроль (в худшем случае имеет место п-кратное повторение испыт-аний при изменении режима испытаний в п-направлениях, где п - число одинаковых ячеек в контролируемой БИС), что снижает производительность контроля, известных устройств.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее ЭВМ, комплект устройств вводавывода и долговременного хранения кон.трольно-измерительной информации, блок сопряжения, блок управления, контактное устройство для включения объекта контроля, блоки статических испытательных воздействий и измерения статических параметров, коммутационную матрицу постоянного тока, блоки формирователей уровней, блок компараторов, генератор блбков, блок цифроаналоговых преобразователей, коммутатор задающих сигналов, блок накопления результатов, многоканальный коммутатор, преобразователь временных параметров в напряжение, аналого-цифровой преобразователь комплект задающих генераторов и блок Ы-вхбдовых схем цифрового или аналогового суммирования.

Принцип работы известного устройства состоит в том, что задающие генераторы формируют на запрограммированной основной частоте fo задающие сигналы, параметры которых программируются независимо по каждому выходу задающих генераторов по отношению к началу 1 онтрольного теста. Посредством коммутатора задающих сигналов и блока N-входовых схем цифрового или аналогового суммирования по командам из блока управления осуществляется объединение задающих сигналов в любые комбинации. Таким образом, согласно программе контроля, в известном устройстве в пределах периода TO формируется импульсная последовательность с числом импульсов от О до N. В результате, в пределах периода То известное устройство позволяет формиро-. вать их;пытательныё, контрольные, тактирующие, стробирующие и синхронизирующие последовательности сигналов с программируемыми временными соотнощениями между ними или с программируемой формой этих сигналов. Такой принцип работы известного устройства позволяет увеличить частоту контроля счетчиков, сдвиговых регистров и др. и тем самым частично решить задачу повышения производительности контроля названных схем 2.

Однако при контроле БИС, состоящих из однотипных .ячеек, переходя от одного режима контроля к другому при переходе от контроля одной ячейки к другой невозможен внутри формируемой тестовой последовательности. Это обстоятельство отрицательно влияет на производительность контроля. Таким образом, недостаток известных устройств для функционального контроля цифровых объектов выражается в низкой производительности контроля схем, состоящих из однотипных элементов, требующих одинакового режимного обеспечения.

Целью изобретения является повышение производительности устройства.

Поставленная цель достигается тем, что в устройство для контроля цифровых объектов, содержащее блок управления, коммутатор, формирователь тестовых последовательностей, связанный информационными входами с входной шиной устройства, информационными выходами - с первыми информационными входами блока компараторов и блока формирователей импульсов, первым командным входом и первым командным выходом - соответственно с первым командным выходом и с первым командным входом распределителя импульсов, подключенного информационным выходом к вторым информационным входам блока компараторов и к вторым информационным входам блока формирователей импульсов, соединенного выходом с первьши входами контактного блока, подключенного вторыми входами к выходу формирователя воздействий, а выходами - к третьим информационным входам блока компараторов, связанного с четвертыми и с третьими информационными входами блока формирователей импульсов и вьгходами блока цифроаналоговых преобразователей, введены мультиплексор, блок регистров и формирователь, адреса, а блок управления содержит первый и второй триггеры, элементы И и элемент ИЛИ, подключенный первым входом к входу «Пуск устройства, вторым входом - к нулевому входу первого триггера и к второму командному выходу формирователя тестовых последовательностей, а выходом к нулевому входу второго триггера, связанного выходом с выходной шиной устройства, а единичным входом - с единичным входом первого триггера и входной шиной устройства, подключенной к первому входу элемента И, соединенного выходом с выходной шиной устройства, а вторым входом - с выходом блока компараторов и с командным входом формирователя адреса, подключенного информационным входом к входной шине устройства, а выходом - к адресному входу мультиплексора, подключенного информационными входами к выходу блока регистров, первыми выходами - к входу распределителя импульсов, вторыми выходами - к входам формирователя воздействий, а третьими выходами - к входам блока цифроаналоговых преобразователей, причем второй командный вход формирователя тестовых последовательностей связан с выходом первого триггера, а вход блока регистров связан с входной шиной устройства.

Введение блоков регистров, мультиплексирований и формирователя адреса позволяет изменять режим контроля внутри формируемой тестовой последовательности, т.е. без обращения к внешнему устройству управления и без повторения кодовых комбинаций. Тем самым сокращается общее число обращений к устройству управления и, следовательно, повышается производительность контроля.

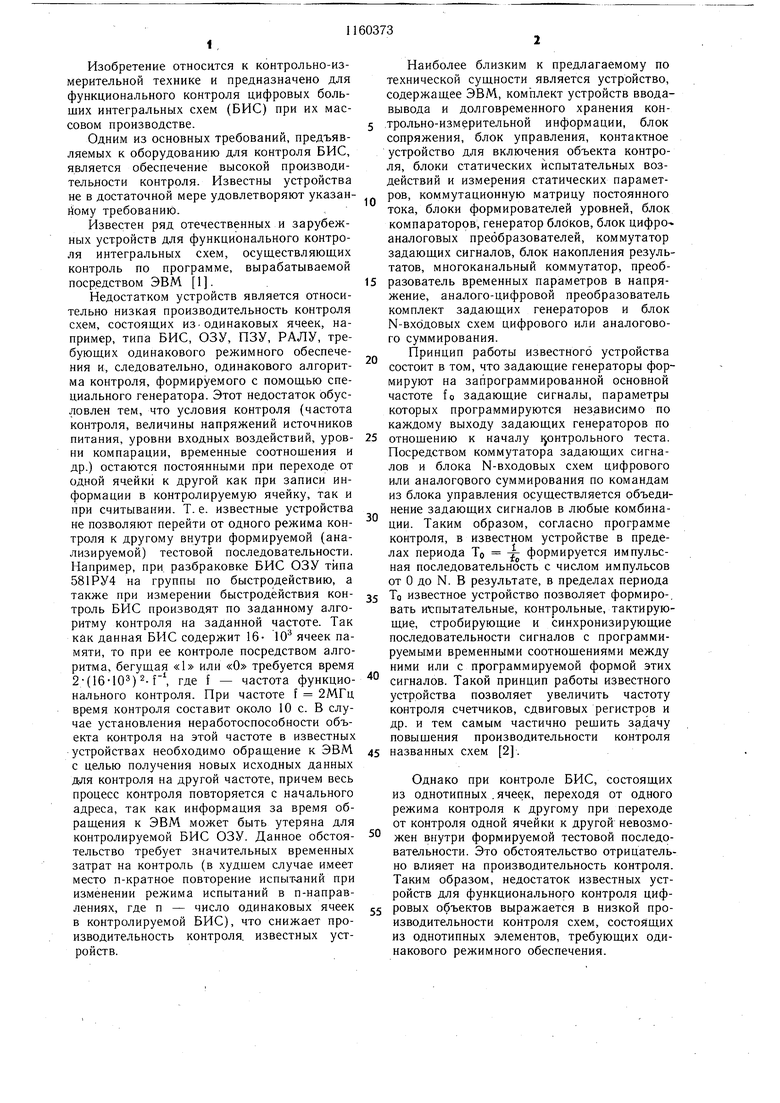

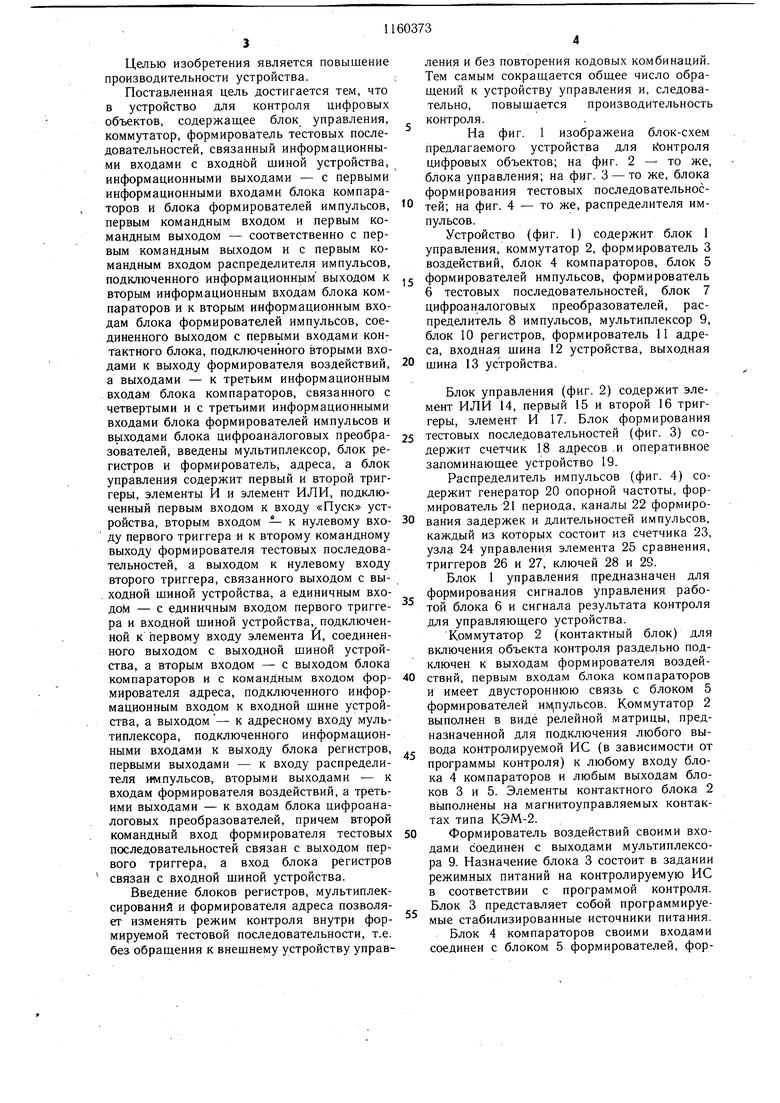

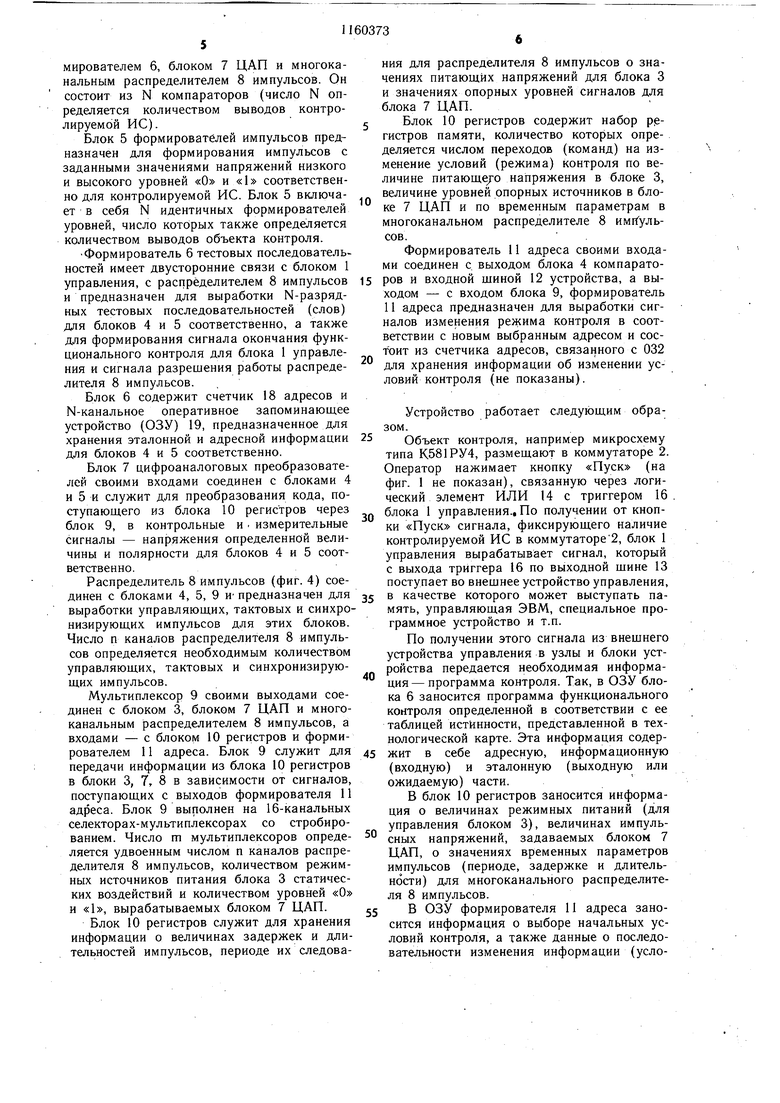

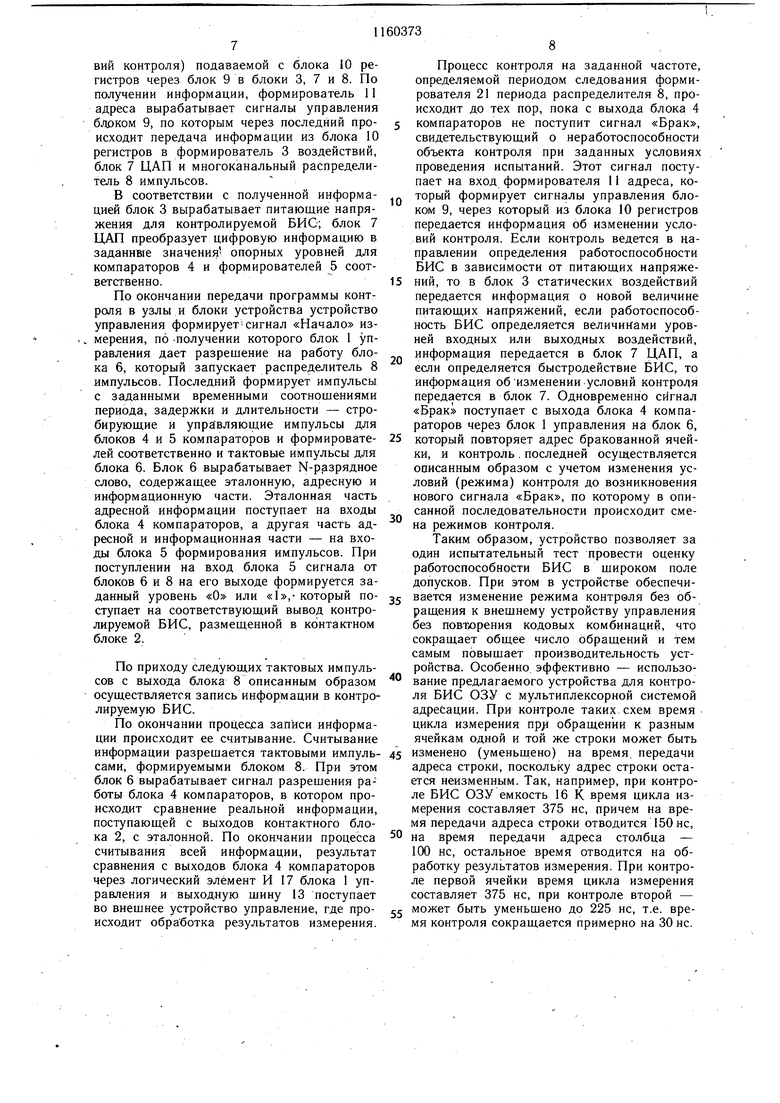

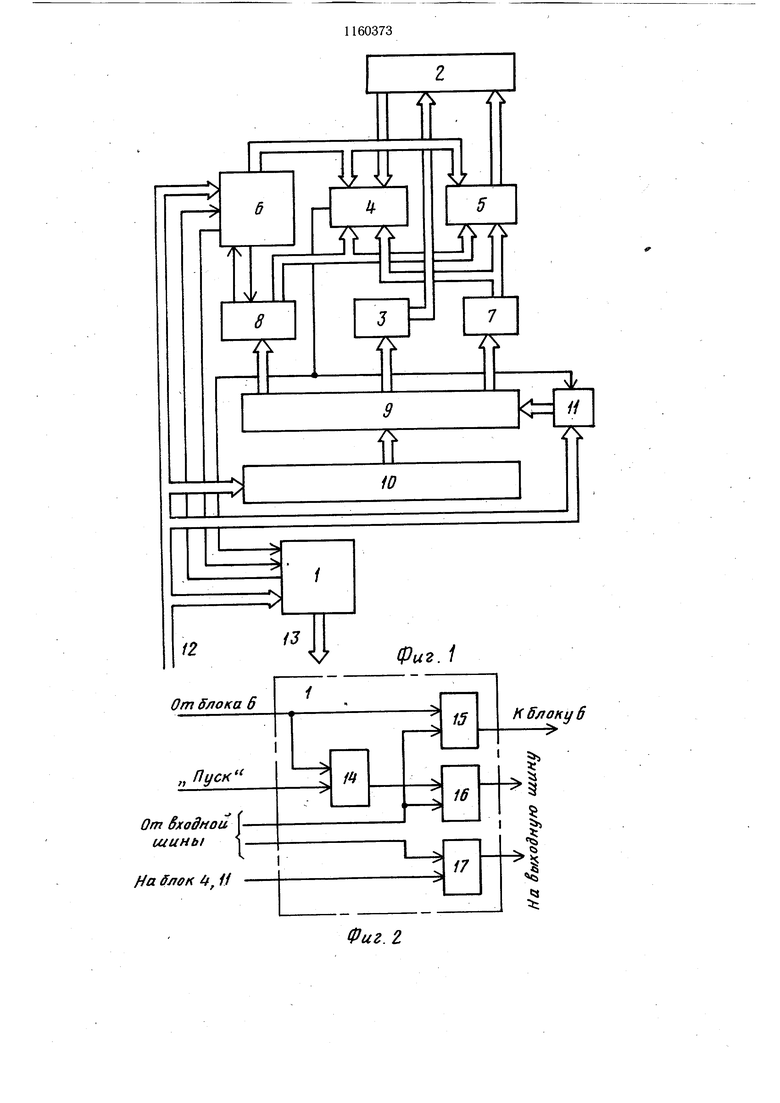

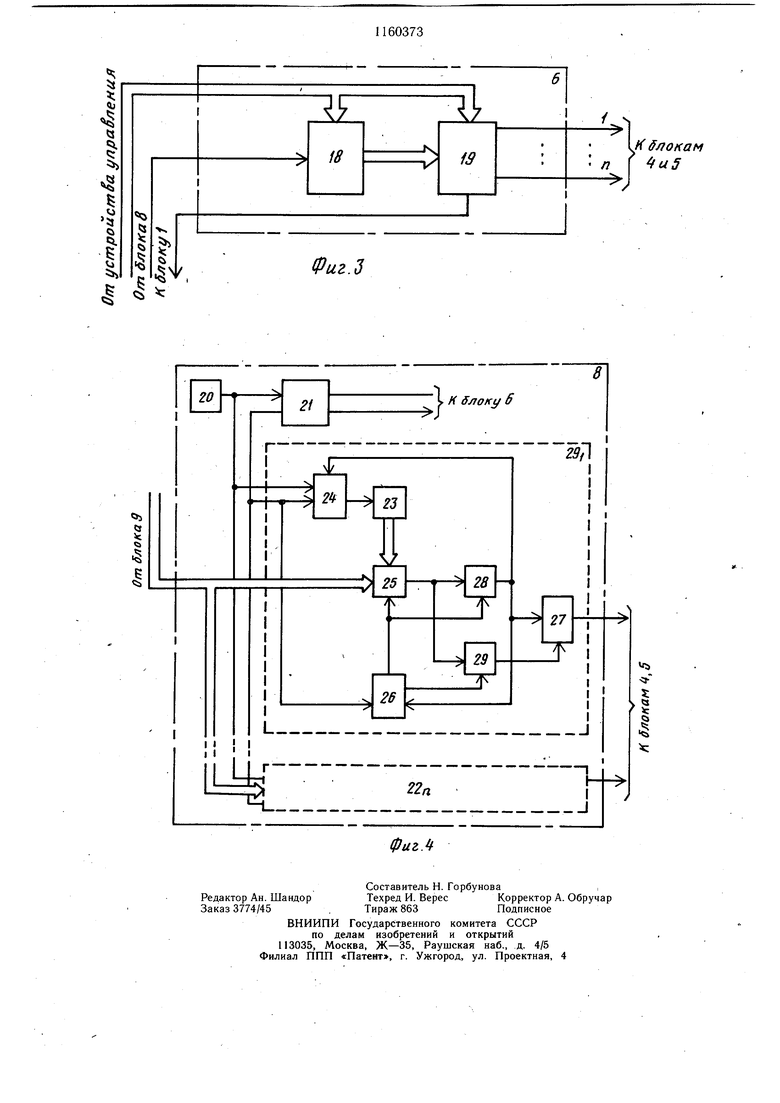

На фиг. 1 изображена блок-схем предлагаемого устройства для 1 нтроля цифровых объектов; на фиг. 2 то же, блока управления; на фит. 3 - то же, блока формирования тестовых последовательнос0 тей; на фиг. 4 - то же, распределителя импульсов.

Устройство (фиг. 1) содержит блок 1 управления, коммутатор 2, формирователь 3 воздействий, блок 4 компараторов, блок 5

5 формирователей импульсов, формирователь 6 тестовых последовательностей, блок 7 цифроаналоговых преобразователей, распределитель 8 импульсов, мультиплексор 9, блок 10 регистров, формирователь II адреса, входная шина 12 устройства, выходная

0 шина 13 устройства.

Блок управления (фиг. 2) содержит элемент ИЛИ 14, первый 15 и второй 16 триггеры, элемент И 17. Блок формирования

5 тестовых последовательностей (фиг. 3) содержит счетчик 18 адресов .и оперативное запоминающее устройство 19.

Распределитель импульсов (фиг. 4) содержит генератор 20 опорной частоты, формирователь 21 периода, каналы 22 формирования задержек и длительностей импульсов, каждый из которых состоит из счетчика 23, узла 24 управления элемента 25 сравнения, триггеров 26 и 27, ключей 28 и 29.

Блок 1 управления предназначен для формирования сигналов управления работой блока 6 и сигнала результата контроля для управляющего устройства.

Коммутатор 2 (контактный блок) для включения объекта контроля раздельно подключен к выходам формирователя воздействий, первым входам блока компараторов и имеет двустороннюю связь с блоком 5 формирователей иМ|Пульсов. Коммутатор 2 выполнен в виде релейной матрицы, предназначенной для подключения любого вывода контролируемой ИС (в зависимости от программы контроля) к любому входу блока 4 компараторов и любым выходам блоков 3 и 5. Элементы контактного блока 2 вьшолнены на магнитоуправляемых контактах типа КЭМ-2.

0 Формирователь воздействий своими входами соединен с выходами мультиплексора 9. Назначение блока 3 состоит в задании режимных питаний на контролируемую ИС в соответствии с программой контроля. Блок 3 представляет собой программируемые стабилизированные источники питания. Блок 4 компараторов своими входами соединен с блоком 5 формирователей, формирователем 6, блоком 7 ЦАП и многоканальным распределителем 8 импульсов. Он состоит из N компараторов (число N определяется количеством выводов контролируемой ИС).

Блок 5 формирователей импульсов предназначен для формирования импульсов с заданными значениями напряжений низкого и высокого уровней «О н «1 соответственно для контролируемой ИС. Блок 5 включает в себя N идентичных формирователей уровней, число которых также определяется количеством выводов объекта контроля.

Формирователь 6 тестовых последовательностей имеет двусторонние связи с блоком 1 управления, с распределителем 8 импульсов и предназначен для выработки N-разрядных тестовых последовательностей (слов) для блоков 4 и 5 соответственно, а также для формирования сигнала окончания функционального контроля для блока 1 управления и сигнала разрешения работы распределителя 8 импульсов.

Блок 6 содержит счетчик 18 адресов и N-канальное оперативное запоминающее устройство (ОЗУ) 19, предназначенное для хранения эталонной и адресной информации для блоков 4 и 5 соответственно.

Блок 7 цифроаналоговых преобразователей своими входами соединен с блоками 4 и 5 и служит для преобразования кода, поступающего из блока 10 регистров через блок 9, в контрольные и . измерительные сигналы - напряжения определенной величины и полярности для блоков 4 и 5 соответственно.

Распределитель 8 импульсов (фиг. 4) соединен с блоками 4, 5, 9 и предназначен для выработки управляющих, тактовых и синхронизирующих импульсов для этих блоков. Число п каналов распределителя 8 импульсов определяется необходимым количеством управляющих, тактовых и синхронизирующих импульсов.

Мультиплексор 9 своими выходами соединен с блоком 3, блоком 7 ЦАП и многоканальным распределителем 8 импульсов, а входами - с блоком 10 регистров и формирователем 11 адреса. Блок 9 служит для передачи информации из блока 10 регистров в блоки 3, 7, 8 в зависимости от сигналов, поступающих с выходов формирователя 11 адреса. Блок 9 выполнен на 16-канальных селекторах-мультиплексорах со стробированием. Число m мультиплексоров определяется удвоенным числом п каналов распределителя 8 импульсов, количеством режимных источников питания блока 3 статических воздействий и количеством уровней «О и «1, вырабатываемых блоком 7 ЦАП.

Блок 10 регистров служит для хранения информации о величинах задержек и длительностей импульсов, периоде их следования для распределителя 8 импульсов о значениях питающих напряжений для блока 3 и значениях опорных уровней сигналов для блока 7 ЦАП.

Блок 10 регистров содержит набор регистров памяти, количество которых определяется числом переходов (команд) на изменение условий (режима) контроля по величине питающе/о напряжения в блоке 3, величине уровней опорных источников в блоке 7 ЦАП и по временным параметрам в многоканальном распределителе 8 имгГульсов.

Формирователь 11 адреса своими входами соединен с, выходом блока 4 компараторов и входной щиной 12 устройства, а выходом - с входом блока 9, формирователь 11 адреса предназначен для выработки сигналов изменения режима контроля в соответствии с новым выбранным адресом и состоит из счетчика адресов, связанного с 032 для хранения информации об изменении условий контроля (не показаны).

Устройство работает следующим образом.

Объект контроля, например микросхему типа К581РУ4, размещают в коммутаторе 2. Оператор нажимает кнопку «Пуск (на фиг. 1 не показан), связанную через логический элемент ИЛИ 14 с триггером 16

Q блока 1 управления.. По получении от кнопки «Пуск сигнала, фиксирующего наличие контролируемой ИС в коммутаторе2, блок 1 управления вырабатывает сигнал, который с выхода триггера 16 по выходной щине 13 поступает во внешнее устройство управления,

в качестве которого может выступать память, управляющая ЭВМ, специальное программное устройство и т.п.

По получении этого сигнала из внешнего устройства управления в узлы и блоки устройства передается необходимая информация- программа контроля. Так, в ОЗУ блока 6 заносится программа функционального контроля определенной в соответствии с ее таблицей истинности, представленной в технологической карте. Эта информация содержит в себе адресную, информационную (входную) и эталонную (выходную или ожидаемую) части.

В блок 10 регистров заносится информация о величинах режимных питаний (для управления блоком 3), величинах импульсных напряжений, задаваемых блоком 7 ЦАП, о значениях временных параметров импульсов (периоде, задержке и длительности) для многоканального распределителя 8 импульсов.

5 В ОЗУ формирователя 11 адреса заносится информация о выборе начальных условий контроля, а также данные о последовательности изменения информации (услоВИЙ контроля) подаваемой с блока 10 регистров через блок 9 в блоки 3, 7 и 8. По получении информации, формирователь 11 адреса вырабатывает сигналы управления блоком 9, по которым через последний происходит передача информации из блока 10 регистров в формирователь 3 воздействий, блок 7 ЦАП и многоканальный распределитель 8 импульсов.

В соответствии с полученной информацией блок 3 вырабатывает питающие напряжения для контролируемой БИО; блок 7 ЦАП преобразует цифровую информацию в заданнв1е значения опорных уровней для компараторов 4 и формирователей 5 соответственно.

По окончании передачи программы контроля в узлы и блоки устройства устройство управления формируетсигнал «Начало измерения, по -получении которого блок 1 управления дает разрешение на работу блока 6, который запускает распределитель 8 импульсов. Последний формирует импульсы с заданными временными соотношениями периода, задержки и длительности - стробирующие и управляющие импульсы для блоков 4 и 5 компараторов и формирователей соответственно и тактовьк импульсы для блока 6. Блок 6 вырабатывает N-разрядное слово, содержащее эталонную, адресную и информационную части. Эталонная часть адресной информации поступает на входы блока 4 компараторов, а другая часть адресной и информационная части - на входы блока 5 формирования импульсов. При поступлении на вход блока 5 сигнала от блоков 6 и 8 на его выходе формируется заданный уровень «О или «1,- который поступает на соответствующий вывод контролируемой БИС, размещенной в контактном блоке 2.

По приходу следующих тактовых импульсов с выхода блока 8 описанным образом осуществляется запись информации в контролируемую БИС.

По окончании процесса записи информации происходит ее считывание. Считывание информации разрещается тактовыми импульсами, формируемыми блоком 8. При этом блок 6 вырабатывает сигнал разрешения работы блока 4 компараторов, в котором происходит сравнение реальной информации, поступающей с выходов контактного блока 2, с эталонной. По окончании процесса считывания всей информации, результат сравнения с выходов блока 4 компараторов через логический элемент И 17 блока 1 управления и выходную шину 13 поступает во внешнее устройство управление, где происходит обработка результатов измерения.

Процесс контроля на заданной частоте, определяемой периодом следования формирователя 21 периода распределителя 8, происходит до тех пор, пока с выхода блока 4 компараторов не поступит сигнал «Брак, свидетельствующий о неработоспособности объекта контроля при заданных условиях проведения испытаний. Этот сигнал поступает на вход формирователя 11 адреса, код торый формирует сигналы управления блоком 9, через который из блока 10 регистров передается информация об изменении условий контроля. Если контроль ведется в направлении определения работоспособности БИС в зависимости от питающих напряже5 НИИ, то в блок 3 статических воздействий передается информация о новой величине питающих напряжений, если работоспособность БИС определяется величинами уровней входных или выходных воздействий, информация передается в блок 7 ЦАП, а если определяется быстродействие БИС, то информация об изменении условий контроля передается в блок 7. Одновременно сигнал «Брак поступает с выхода блока 4 компараторов через блок 1 управления на блок 6,

5 который повторяет адрес бракованной ячейки, и контроль . последней осуществляется оаисанным образом с учетом изменения условий (режима) контроля до возникновения нового сигнала «Брак, по которому в опи. санной последовательности происходит смена режимов контроля.

Таким образом, устройство позволяет за один испытательный тест провести оценку работоспособности БИС в широком поле допусков. При этом в устройстве обеспечивается изменение режима контроля без обращения к внешнему устройству управления без повторения кодовых комбинаций, что сокращает общее число обращений и тем самым повыщает производительность устройства. Особенно, эффективно - использование предлагаемого устройства для контроля БИС ОЗУ с мультиплексорной системой адресации. При контроле таких схем время цикла измерения пp обращении к разным ячейкам одной и той же строки может быть

5 изменено (уменьщено) на время, передачи адреса строки, поскольку адрес строки остается неизменным. Так, например, при контроле БИС ОЗУ емкость 16 К время цикла измерения составляет 375 не, причем на время передачи адреса строки отводится 150нс,

0 на время передачи адреса столбца - 100 НС, остальное время отводится на обработку результатов измерения. При контроле первой ячейки время цикла измерения составляет 375 не, при контроле второй -

С может быть уменьшено до 225 не, т.е. время контроля сокращается примерно на 30 не.

Фиг. 2

J блокам u5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для задания тестов | 1985 |

|

SU1290265A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ ОБЪЕКТОВ, содержащее блок управления, коммутатор, формирователь тестовых последовательностей, связанный информационными входами с входной шиной устройства, информационными выходами - с первыми информационными входами блока компараторов и блока формирователей импульсов, первым командным входом и первым командным выходом - соответственно с первым командным выходом и с первым командным входом распределителя импульсов, подключенного информационным выходом к вторым информационным входам блока компараторов и к вторым информационным входам блока формирователей импульсов, соединенного с первыми входами коммутатора, подключенного вторыми входами к выходу формирователя воздействия, а выходами - к третьим информационным входам блока компараторов, связанного с четвертыми и с третьими информационными входами блока формирователей импульсов и выходами блока цифроаналоговых преобразователей, отличающееся тем, что, с целью повышения .производительности устройства, в него введены мультиплексор, блок регистров и формирователь адреса, а блок управления содержит первый и второй триггеры, элемент И и элемент ИЛИ, подключенный первым входом к входу «Пуск устройства, вторым входом - к нулевому входу первого триггера и к второму командному выходу формирователя тестовых, последовательностей, а выходом - к нулевому входу второго триггера, связанного выходом с выходной шиной устройства, а единичным входом - с единичным входом первого триггера и входной шиной устройства, подключенной к первому входу элемента И, соединенного выходом с выходной шиной устройства, (Я а вторым входом - с выходом блока компараторов и с командным входом формирователя адреса, подключенного информационным входом к входной шине устройства, а выходом - к адресному входу мультиплексора, подключенного информационными входами к выходу блока регистров, первыми выходами - к входу распределителя импульсов, вторыми выходами - к входам формиО5 рователей воздействий, а третьими выходами - к входам блока цифроаналоговых преО образователей, причем второй командный со вход формирователя тестовых последовательностей связан с выходом первого тригсо гера, а вход блока регистров - с входной шиной устройства..

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Система для автоматического контроля электрических параметров электронных схем | 1972 |

|

SU471560A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения среднего значения сигнала | 1971 |

|

SU437968A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-06-07—Публикация

1983-10-10—Подача