и выдачу информации поступают на триггеры 4, 5. Опросы триггеров 4, 5, 6 обеспечиваются счетчиком 8 через мультиплексоры 10, 11. Запись бит информации и преобразование последовательных кодов в параллельные производятся в блоке 16 памяти. Подсчет числа бит и байтов, принятых или выданных каналами, производится в адресном блоке 19. Хранение принятой информации и выдача ее каналами обеспечиваются

блоком 22 памяти через выходные регистры 23. Управление блоками 16, 22 памяти блоком 19 осуществляется распределителем 9 через формирователь 21, демультиплексоры 13, 14, 15, дешифраторы 17, 20 и блок 18 сравнения числа байтов с заданным. После обработки требований каналов соответствующие триггеры 4, 5 устанавливаются в нулевое положение через демультиплексор 12. 1, з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

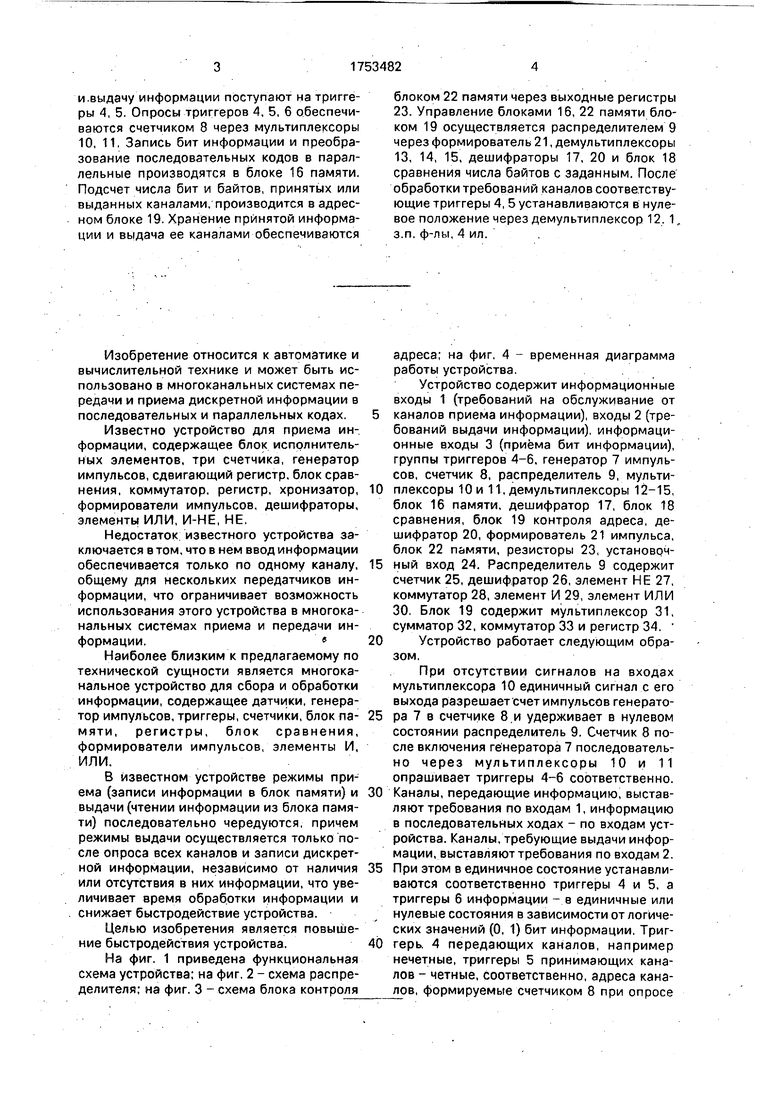

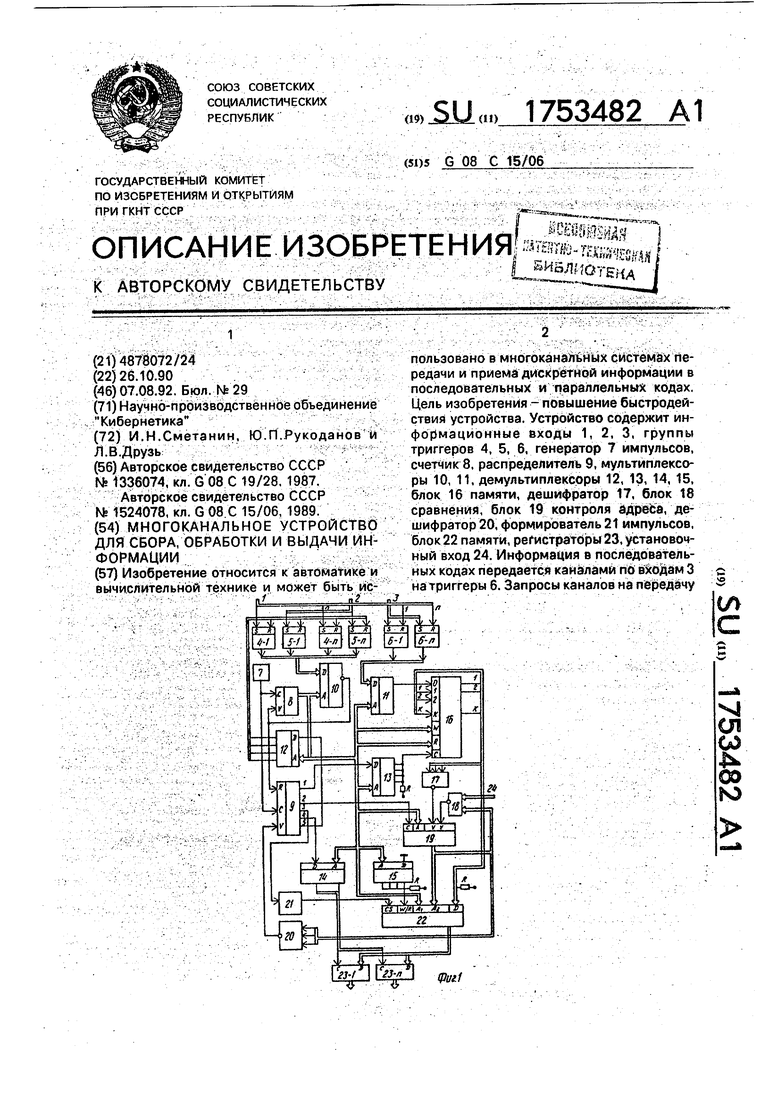

Изобретение относится к автоматике и вычислительной технике и может быть пользовано в многоканальных системах передачи и приема дискретной информации в последовательных и параллельных кодах. Цель изобретения - повышение быстродействия устройства. Устройство содержит информационные входы 1, 2, 3, группы триггеров 4, 5, 6, генератор 7 импульсов, счетчик 8, распределитель 9, мультиплексоры 10, 11, демультиплексоры 12, 13, 14, 15, блок 16 памяти, дешифратор 17, блок 18 сравнения, блок 19 контроля адреса, дешифратор 20, формирователь 21 импульсов, блок 22 памяти, регистраторы 23, установочный вход 24. Информация в последовательных кодах передается каналами по входам 3 на триггеры 6. Запросы каналов на передачу (Л С ч (Л 2 со ю фиг

Изобретение относится к автоматике и вычислительной технике и может быть использовано в многоканальных системах передачи и приема дискретной информации в последовательных и параллельных кодах.

Известно устройство для приема информации, содержащее блок исполнительных элементов, три счетчика, генератор импульсов, сдвигающий регистр, блок сравнения, коммутатор, регистр, хронизатор, формирователи импульсов, дешифраторы, элементы ИЛИ, И-НЕ, НЕ,

Недостаток известного устройства заключается в том, что в нем ввод информации обеспечивается только по одному каналу, общему для нескольких передатчиков информации, что ограничивает возможность использования этого устройства в многоканальных системах приема и передачи информации.

Наиболее близким к предлагаемому по технической сущности является многоканальное устройство для сбора и обработки информации, содержащее датчики, генератор импульсов, триггеры, счетчики, блок памяти, регистры, блок сравнения, формирователи импульсов, элементы И, ИЛИ.

В известном устройстве режимы приема (записи информации в блок памяти) и выдачи (чтении информации из блока памяти) последовательно чередуются, причем режимы выдачи осуществляется только после опроса всех каналов и записи дискретной информации, независимо от наличия или отсутствия в них информации, что увеличивает время обработки информации и снижает быстродействие устройства.

Целью изобретения является повышение быстродействия устройства.

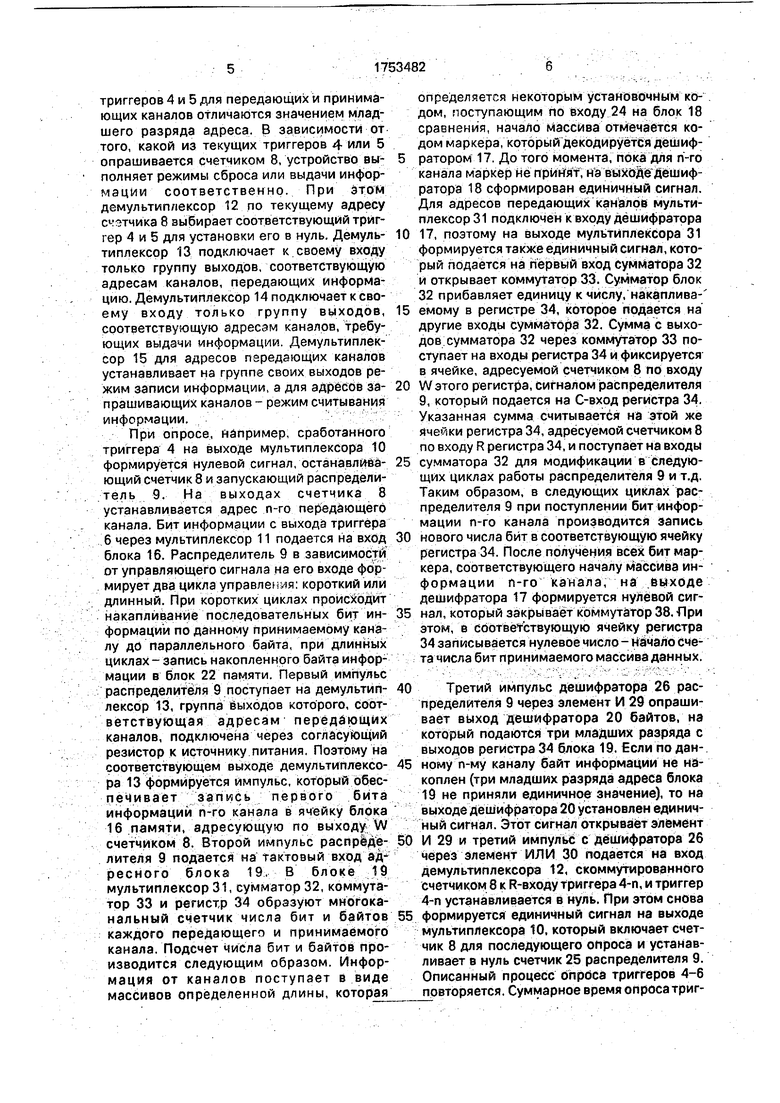

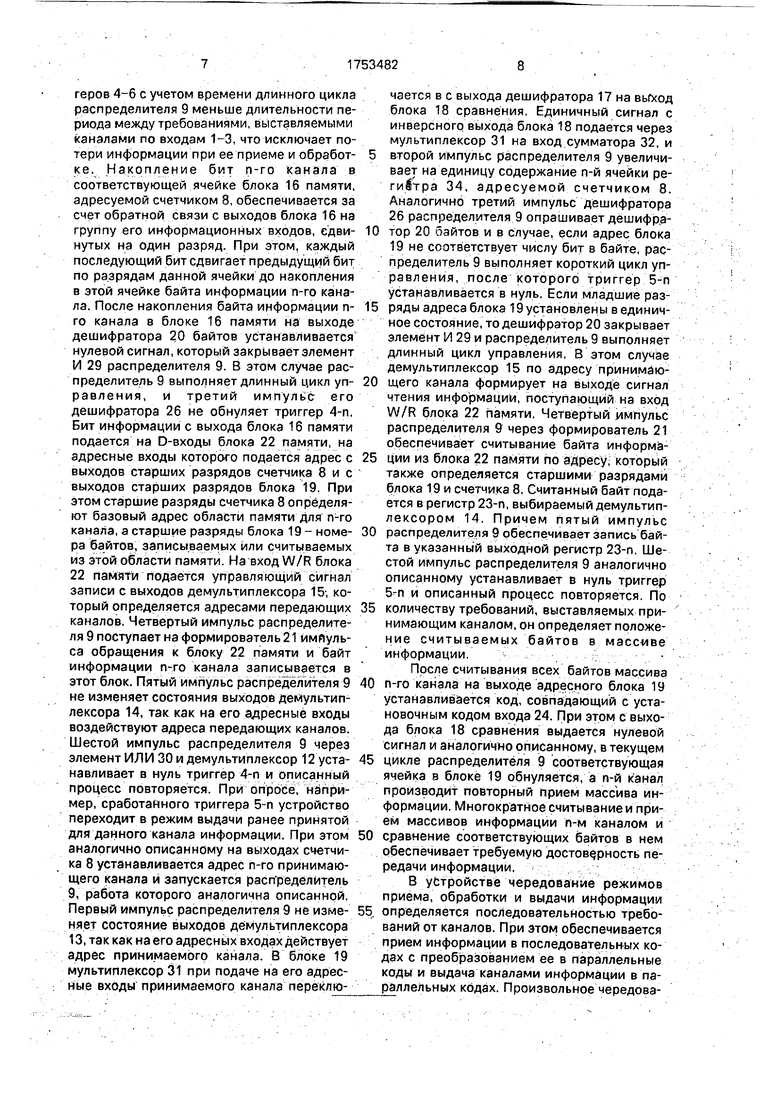

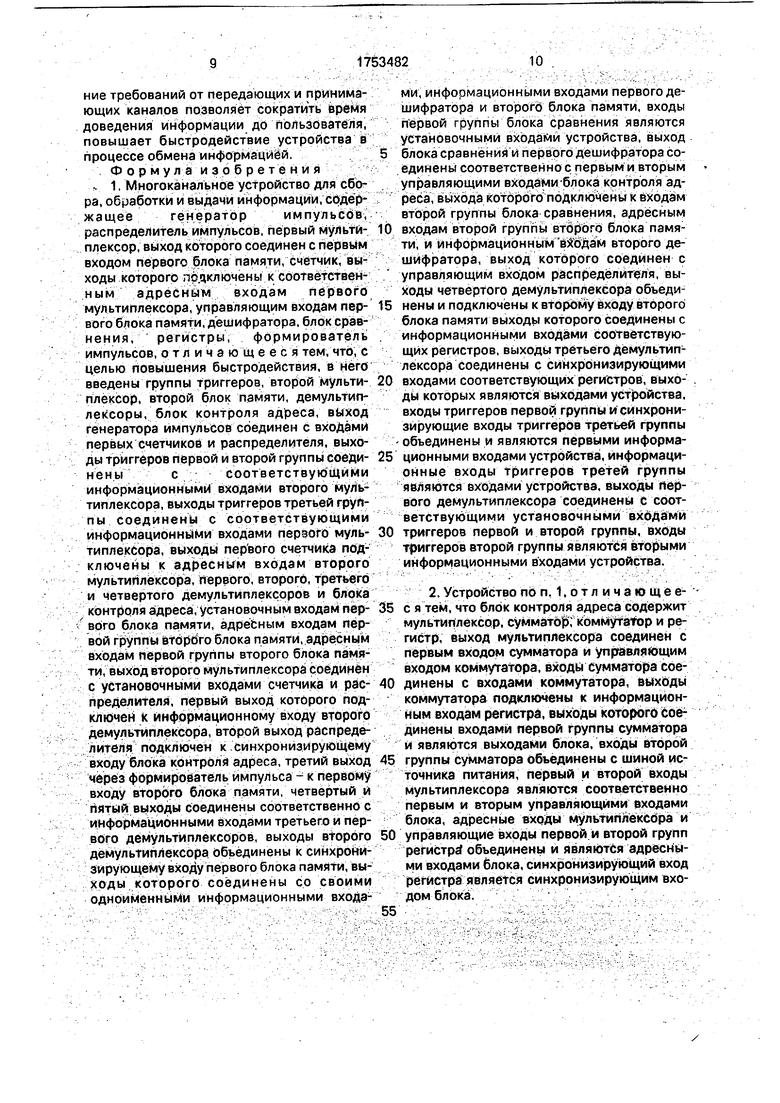

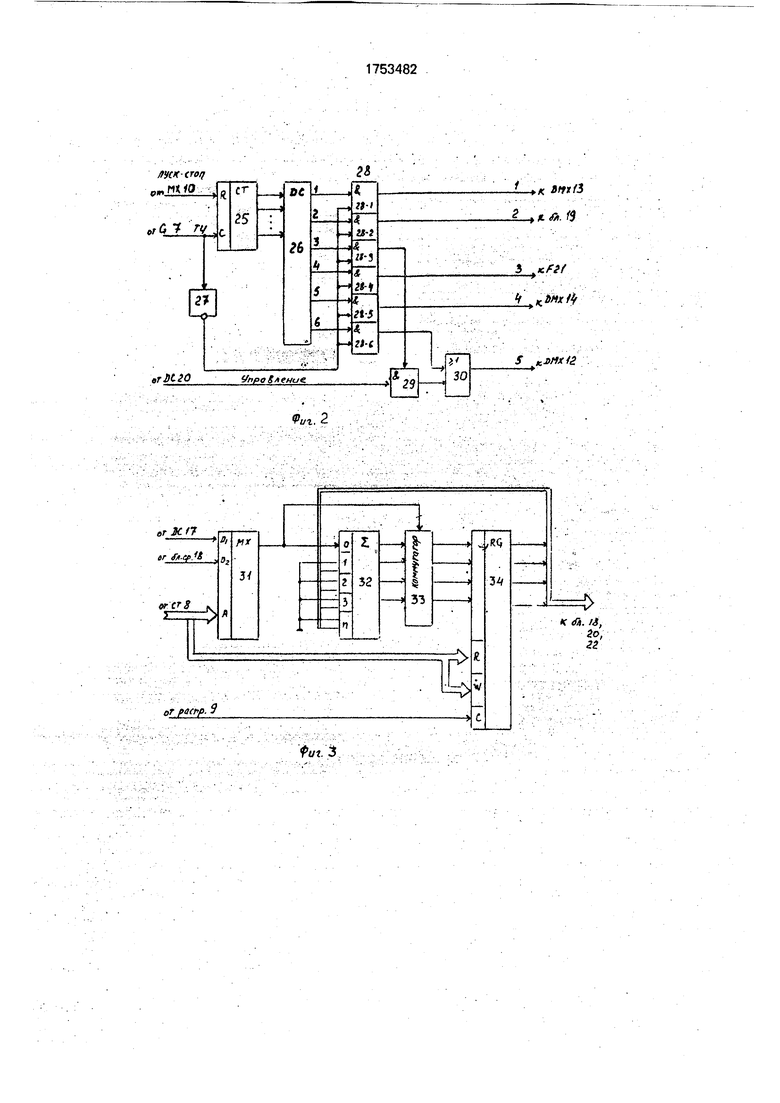

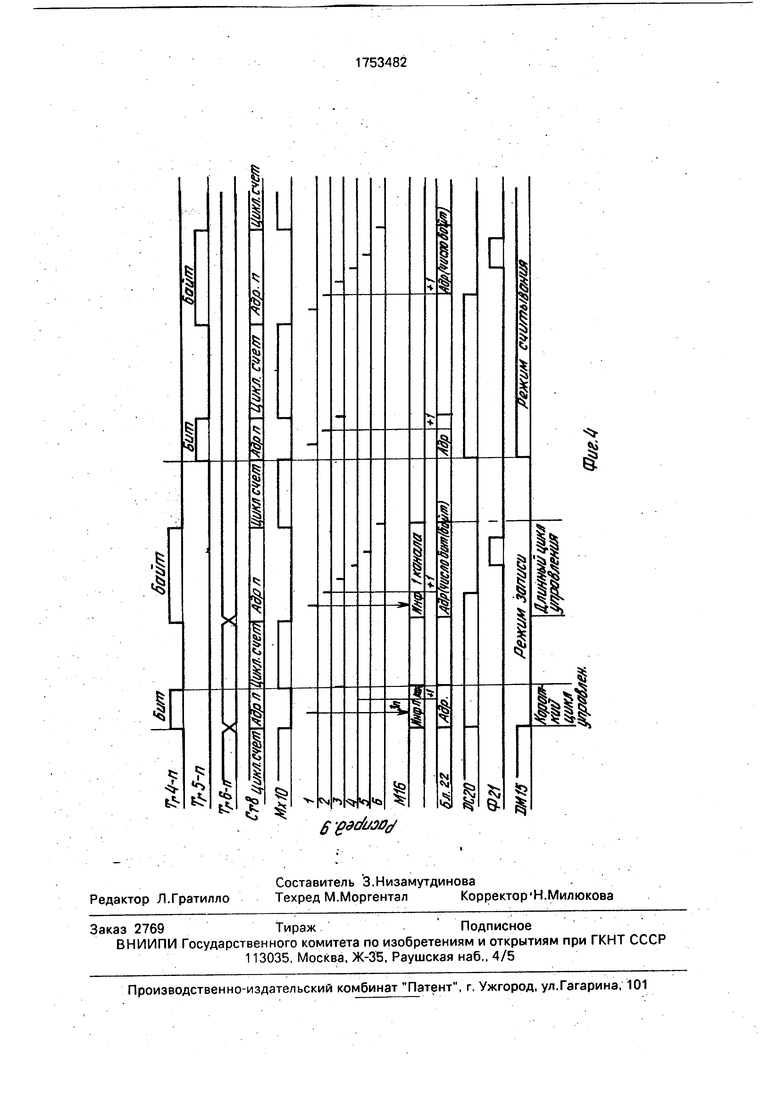

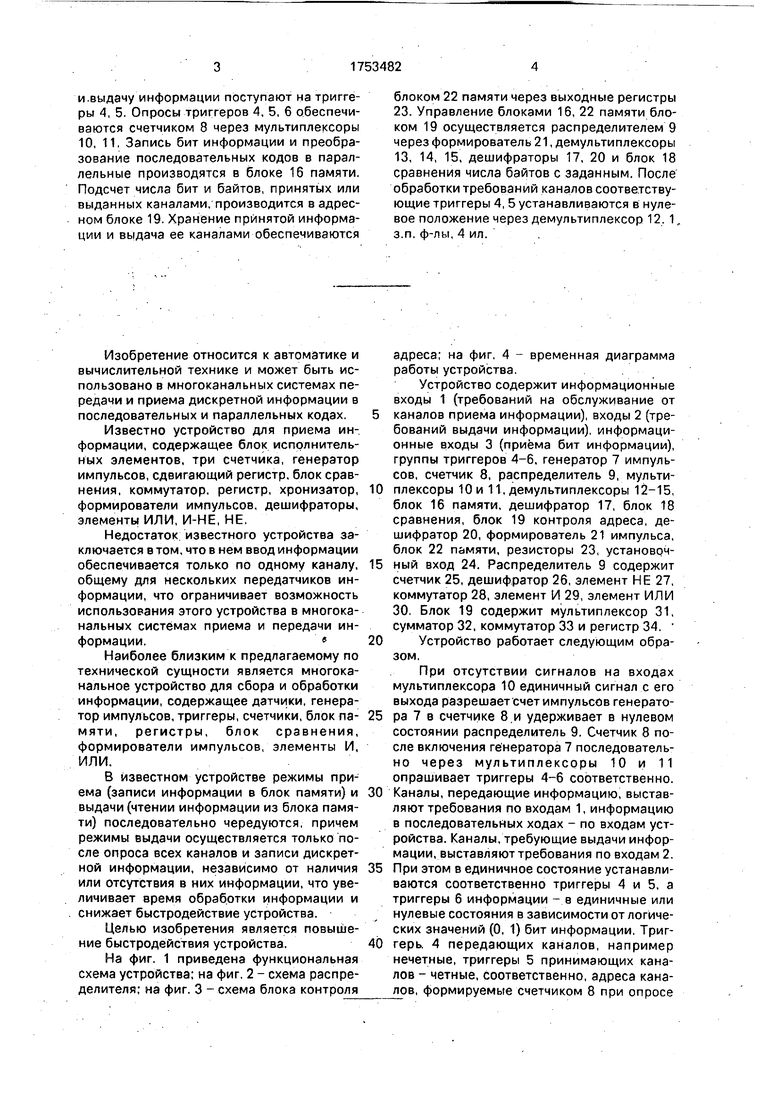

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема распределителя; на фиг. 3 - схема блока контроля

адреса; на фиг. 4 - временная диаграмма работы устройства.

Устройство содержит информационные входы 1 (требований на обслуживание от

каналов приема информации), входы 2 (требований выдачи информации), информационные входы 3 (приёма бит информации), группы триггеров 4-6, генератор 7 импульсов, счетчик 8, распределитель 9, мультиплексоры 10 и 11, демультиплексоры 12-15, блок 16 памяти, дешифратор 17, блок 18 сравнения, блок 19 контроля адреса, дешифратор 20, формирователь 21 импульса, блок 22 памяти, резисторы 23, установочный вход 24. Распределитель 9 содержит счетчик 25, дешифратор 26, элемент НЕ 27, коммутатор 28, элемент И 29, элемент ИЛИ 30. Блок 19 содержит мультиплексор 31, сумматор 32, коммутатор 33 и регистр 34.

Устройство работает следующим образом.

При отсутствии сигналов на входах мультиплексора 10 единичный сигнал с его выхода разрешает счет импульсов генератора 7 в счетчике 8 и удерживает в нулевом состоянии распределитель 9. Счетчик 8 после включения генератора 7 последовательно через мультиплексоры 10 и 11 опрашивает триггеры 4-6 соответственно.

Каналы, передающие информацию, выставляют требования по входам 1, информацию в последовательных ходах - по входам устройства. Каналы, требующие выдачи информации, выставляют требования по входам 2.

При этом в единичное состояние устанавливаются соответственно триггеры 4 и 5, а триггеры 6 информации - в единичные или нулевые состояния в зависимости от логических значений (0, 1) бит информации. Триггерь. 4 передающих каналов, например нечетные, триггеры 5 принимающих каналов - четные, соответственно, адреса кана- лов, формируемые счетчиком 8 при опросе

триггеров 4 и 5 для передающих и принимающих каналов отличаются значением младшего разряда адреса. В зависимости от того, какой из текущих триггеров 4 или 5 опрашивается счетчиком 8, устройство выполняет режимы сброса или выдачи информации соответственно. При этом демультиплексор 12 по текущему адресу ситчика 8 выбирает соответствующий триггер 4 и 5 для установки его в нуль. Демультиплексор 13 подключает к своему входу только группу выходов, соответствующую адресам каналов, передающих информацию. Демультиплексор 14 подключает к своему входу только группу выходов, соответствующую адресам каналов, требующих выдачи информации. Демультиплексор 15 для адресов передающих каналов устанавливает на группе своих выходов режим записи информации, а для адресов запрашивающих каналов - режим считывания информации.

При опросе, например, сработанного триггера 4 на выходе мультиплексора 10 формируется нулевой сигнал, останавливающий счетчик 8 и запускающий распредели- тель 9. На выходах счетчика 8 устанавливается адрес n-го передающего канала. Бит информации с выхода триггера 6 через мультиплексор 11 подается на вход блока 16. Распределитель 9 в зависимости от управляющего сигнала на его входе формирует два цикла управления: короткий или длинный. При коротких циклах происходит накапливание последовательных бит информации по данному принимаемому каналу до параллельного байта, при длинных циклах- запись накопленного байта информации в блок 22 памяти. Первый импульс распределителя 9 поступает на демультиплексор 13, группа выходов которого, соответствующая адресам передающих каналов, подключена через согласующий резистор к источнику питания. Поэтому на соответствующем выходе демультиплексо- ра 13 формируется импульс, который обеспечивает запись первого бита информации n-го канала в ячейку блока 16 памяти, адресующую по выходу W счетчиком 8. Второй импульс распределителя 9 подается на тактовый вход адресного блока 19. В блоке 19 мультиплексор 31, сумматор 32, коммутатор 33 и регистр 34 образуют многоканальный счетчик числа бит и байтов каждого передающего и принимаемого канала. Подсчет числа бит и байтов производится следующим образом. Информация от каналов поступает в виде массивов определенной длины, которая

определяется некоторым установочным кодом, поступающим по входу 24 на блок 18 сравнения, начало массива отмечается кодом маркера, который декодируется дешифратором 17. До того момента, пока для п-го канала маркер не принят, на выходе Дешифратора 18 сформирован единичный сигнал. Для адресов передающих каналов мультиплексор 31 подключен к входу дешифратора

17, поэтому на выходе мультиплексора 31 формируется также единичный сигнал, который подается на первый вход сумматора 32 и открывает коммутатор 33. Сумматор блок 32 прибавляет единицу к числу, накапливаемому в регистре 34, которое подается на другие входы сумматора 32. Сумма с выходов сумматора 32 через коммутатор 33 поступает на входы регистра 34 и фиксируется в ячейке, адресуемой счетчиком 8 по входу

W этого регистра, сигналом распределителя 9, который подается на С-вход регистра 34. Указанная сумма считывается на этой же ячейки регистра 34, адресуемой счетчиком 8 по входу R регистра 34, и поступает на входы

сумматора 32 для модификации в следующих циклах работы распределителя 9 и т.д. Таким образом, в следующих циклах распределителя 9 при поступлении бит информации n-го канала производится запись

нового числа бит в соответствующую ячейку регистра 34. После получения всех бит маркера, соответствующего началу массива информации п-го канала, на выходе дешифратора 17 формируется нулевой сигнал, который закрывает коммутатор 38, Лри этом, в соответствующую ячейку регистра 34 записывается нулевое число - начало счета числа бит принимаемого массива данных.

Третий импульс дешифратора 26 распределителя 9 через элемент И 29 опрашивает выход дешифратора 20 байтов, на который подаются три младших разряда с выходов регистра 34 блока 19. Если по данному n-му каналу байт информации не накоплен (три младших разряда адреса блока 19 не приняли единичное значение), то на выходе дешифратора 20 установлен единичный сигнал. Этот сигнал открывает элемент

И 29 и третий импульс с дешифратора 26 через элемент ИЛИ 30 подается на вход демультиплексора 12, скоммутированного счетчиком 8 к R-входу триггера 4-п, и триггер 4-п устанавливается в нуль. При этом снова

формируется единичный сигнал на выходе мультиплексора 10, который включает счетчик 8 для последующего опроса и устанавливает в нуль счетчик 25 распределителя 9. Описанный процесс опроса триггеров 4-6 повторяется. Суммарное время опроса триггеров 4-6 с учетом времени длинного цикла распределителя 9 меньше длительности периода между требованиями, выставляемыми каналами по входам 1-3, что исключает потери информации при ее приеме и обработке. Накопление бит n-го канала в соответствующей ячейке блока 16 памяти, адресуемой счетчиком 8, обеспечивается за счет обратной связи с выходов блока 16 на группу его информационных входов, сдвинутых на один разряд. При этом, каждый последующий бит сдвигает предыдущий бит по разрядам данной ячейки до накопления в этой ячейке байта информации n-го канала. После накопления байта информации п- го канала в блоке 16 памяти на выходе дешифратора 20 байтов устанавливается нулевой сигнал, который закрывает элемент И 29 распределителя 9. В этом случае распределитель 9 выполняет длинный цикл управления, и третий импульс его дешифратора 26 не обнуляет триггер 4-п. Бит информации с выхода блока 16 памяти подается на D-входы блока 22 памяти, на адресные входы которого подается адрес с выходов старших разрядов счетчика 8 и с выходов старших разрядов блока 19. При этом старшие разряды счетчика 8 определяют базовый адрес области памяти для п-го канала, а старшие разряды блока 19 - номера байтов, записываемых или считываемых из этой области памяти. На вход W/R блока 22 памяти подается управляющий сигнал записи с выходов демультиплексора 15-, который определяется адресами передающих каналов. Четвертый импульс распределителя 9 поступает на формирователь 21 имйуль- са обращения к блоку 22 памяти и байт информации n-го канала записывается в этот блок. Пятый импульс распределителя 9 не изменяет состояния выходов демультиплексора 14, так как на его адресные входы воздействуют адреса передающих каналов. Шестой импульс распределителя 9 через элемент ИЛИ 30 и демультиплексор 12 устанавливает в нуль триггер 4-п и описанный процесс повторяется. При опросе, например, сработанного триггера 5-п устройство переходит в режим выдачи ранее принятой для данного канала информации. При этом аналогично описанному на выходах счетчика 8 устанавливается адрес n-го принимающего канала и запускается распределитель 9, работа которого аналогична описанной. Первый импульс распределителя 9 не изменяет состояние выходов демультиплексора 13, так как на его адресных входах действует адрес принимаемого канала. В блоке 19 мультиплексор 31 при подаче на его адресные входы принимаемого канала переключается в с выхода дешифратора 17 на вьГход блока 18 сравнения. Единичный сигнал с инверсного выхода блока 18 подается через мультиплексор 31 на вход сумматора 32, и второй импульс распределителя 9 увеличивает на единицу содержание n-й ячейки ре- 34, адресуемой счетчиком 8. Аналогично третий импульс дешифратора 26 распределителя 9 опрашивает дешифра0 тор 20 байтов и в случае, если адрес блока 19 не соответствует числу бит в байте, распределитель 9 выполняет короткий цикл управления, после которого триггер 5-п устанавливается в нуль, Если младшие раз5 ряды адреса блока установлены в единичное состояние, то дешифратор 20 закрывает элемент И 29 и распределитель 9 выполняет длинный цикл управления. В этом случае демультиплексор 15 по адресу принимаю0 щего канала формирует на выходе сигнал чтения информации, поступающий на вход W/R блока 22 памяти. Четвертый импульс распределителя 9 через формирователь 21 обеспечивает считывание байта информа5 ции из блока 22 памяти по адресу, который также определяется старшими разрядами блока 19 и счетчика 8. Считанный байт подается в регистр 23-п, выбираемый демультип- лексором 14. Причем пятый импульс

0 распределителя 9 обеспечивает запись байта в указанный выходной регистр 23-п. Шестой импульс распределителя 9 аналогично описанному устанавливает в нуль триггер 5-п и описанный процесс повторяется. По

5 количеству требований, выставляемых принимающим каналом, он определяет положение считываемых байтов в массиве информации.

После считывания всех байтов массива

0 n-го канала на выходе адресного блока 19 устанавливается код, совпадающий с установочным кодом входа 24. При этом с выхода блока 18 сравнения выдается нулевой сигнал и аналогично описанному, в текущем

5 цикле распределителя 9 соответствующая ячейка в блоке 19 обнуляется, а n-й канал производит повторный прием массива информации. Многократное считывание и прием массивов информации n-м каналом и

0 сравнение соответствующих байтов в нем обеспечивает требуемую достоверность передачи информации.

В устройстве чередование режимов приема, обработки и выдачи информации

5 определяется последовательностью требований от каналов. При этом обеспечивается прием информации в последовательных кодах с преобразованием ее в параллельные коды и выдача каналами информации в па- раллельных кодах. Произвольное чередование требований от передающих и принимающих каналов позволяет сократить время доведения информации до пользователя, повышает быстродействие устройства в процессе обмена информацией.

Формула изобретения - 1, Многоканальное устройство для сбора, обработки и выдачи информации, содер- жащее генератор импульсов, распределитель импульсов, первый мульти- плексор, выход которого соединен с первым входом первого блока памяти, счетчик, выходы которого подключены к соответствен- ным адресным входам первого мультиплексора, управляющим входам пер- вого блока памяти, дешифратора, блок сравнения, регистры, формирователь импульсов, отличающееся тем, что, с целью повышения быстродействия, в него введены группы триггеров, второй мульти- плексор, второй блок памяти, демультип- лексоры, блок контроля адреса, выход генератора импульсов соединен с входами первых счетчиков и распределителя, выходы триггеров первой и второй группы соеди- неныссоответствующими

информационными входами второго мультиплексора, выходы триггеров третьей груп- пы соединены с соответствующими информационными входами первого муль- типлексора, выходы первого счетчика подключены к адресным входам второго мультиплексора, первого, второго, третьего и четвертого демультиплексоров и блока контроля адреса, установочным входам пер- вого блока памяти, адресным входам первой группы второго блока памяти, адресным входам первой группы второго блока памяти, выход второго мультиплексора соединен с установочными входами счетчика и рас- пределителя, первый выход которого подключен к информационному входу второго демультиплексора, второй выход распределителя подключен к синхронизирующему входу блока контроля адреса, третий выход через формирователь импульса - к первому входу второго блока памяти, четвертый и пятый выходы соединены соответственно с информационными входами третьего и первого демультиплексоров, выходы второго демультиплексора объединены к синхронизирующему входу первого блока памяти, выходы которого соединены со своими одноименными информационными входа

ми, информационными входами первого дешифратора и второго блока памяти, входы первой группы блока сравнения являются установочными входами устройства, выход блока сравнения и первого дешифратора соединены соответственно с первым и вторым управляющими входами блока контроля адреса, выхода которого подключены к входам второй группы блока сравнения, адресным входам второй группы второго блока памяти, и информационным входам второго дешифратора, выход которого соединен с управляющим входом распределителя, выходы четвертого демультиплексора объединены и подключены к второму входу второго блока памяти выходы которого соединены с информационными входами соответствующих регистров, выходы третьего демультиплексора соединены с синхронизирующими входами соответствующих регистров, выходы которых являются выходами устройства, входы триггеров первой группы и синхронизирующие входы триггеров третьей группы объединены и являются первыми информационными входами устройства, информационные входы триггеров третей группы являются входами устройства, выходы первого демультиплексора соединены с соответствующими установочными входами триггеров первой и второй группы, входы триггеров второй группы являются вторыми информационными входами устройства.

ffXK (roq

I

| Устройство для приема информации | 1986 |

|

SU1336074A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Многоканальное устройство для сбора и обработки информации | 1988 |

|

SU1524078A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1992-08-07—Публикация

1990-10-26—Подача