1 1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации, информационно-измерительных системах.

Цель изобретения - увеличение быстродействия.

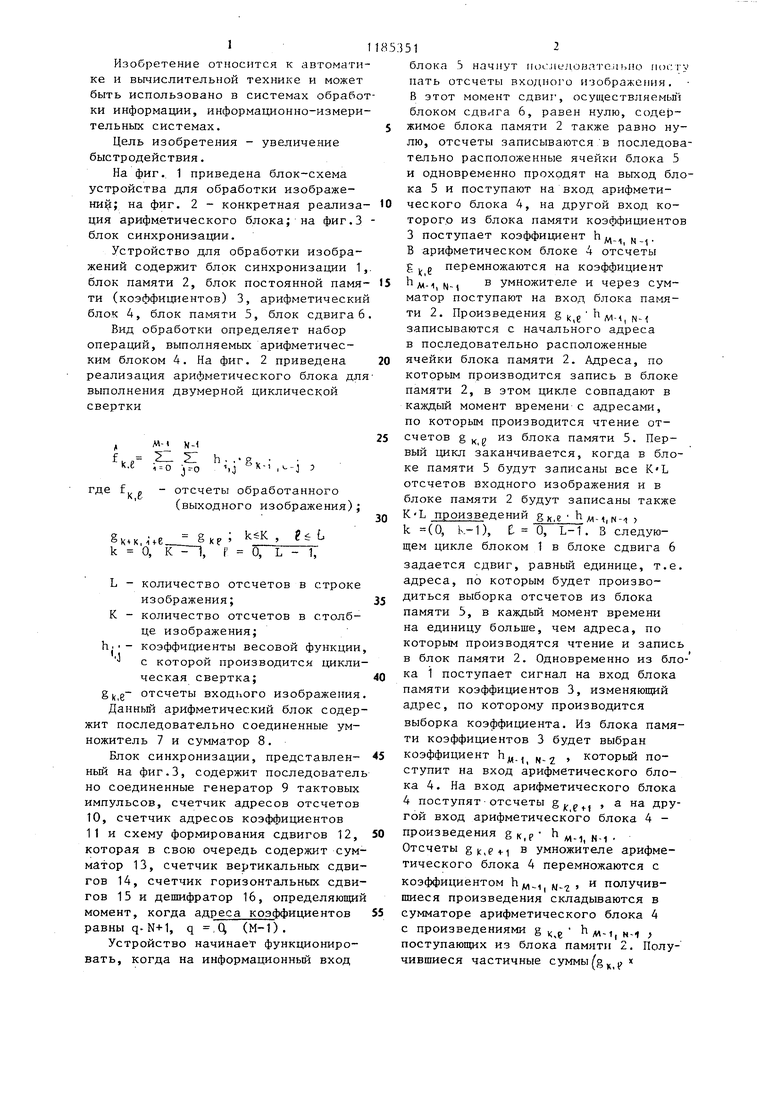

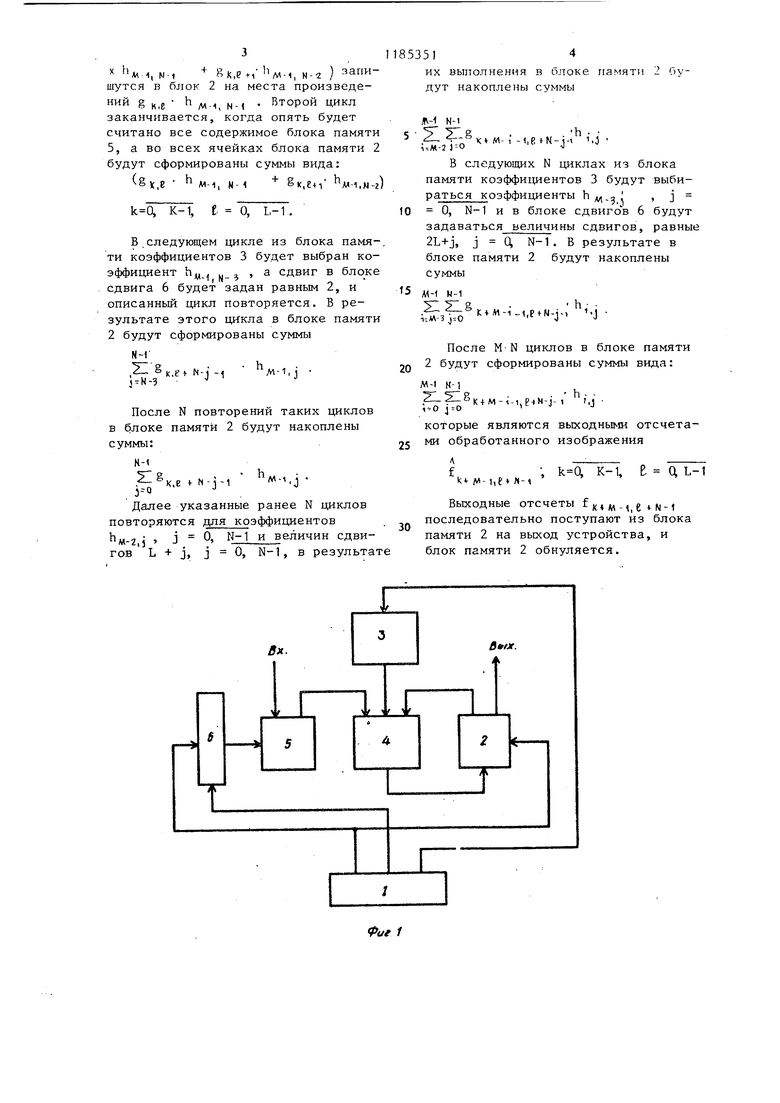

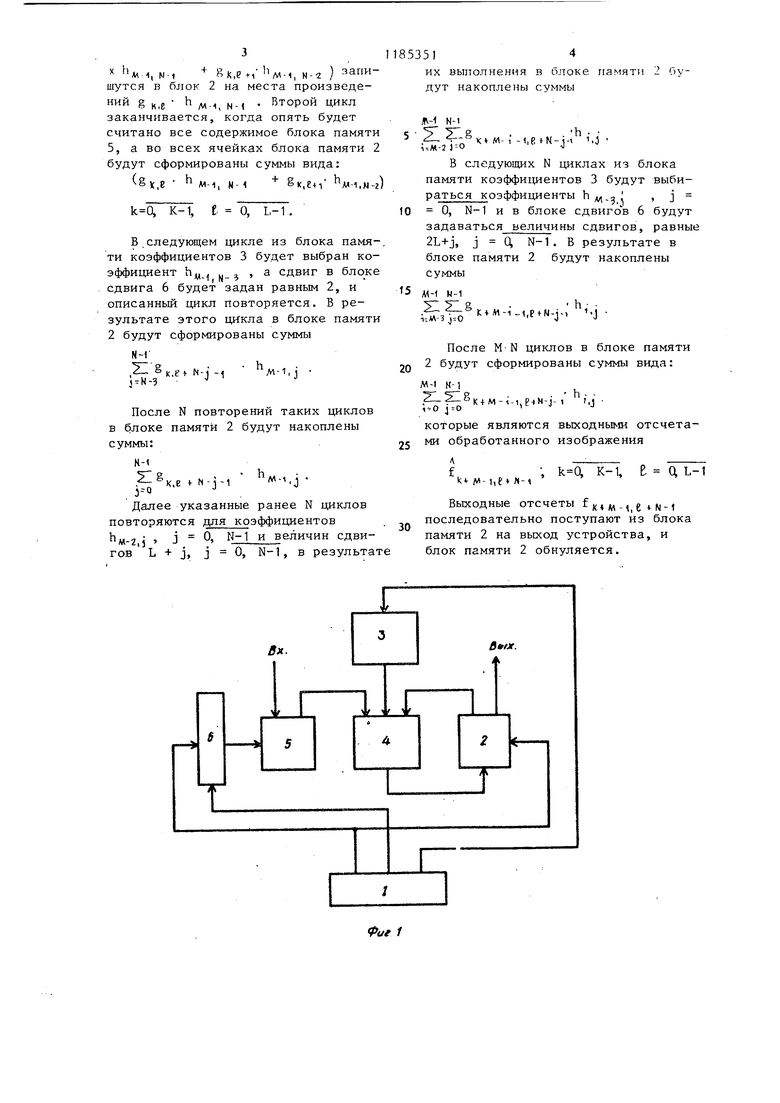

На фиг. 1 приведена блок-схема устройства для обработки изображени$; на фиг. 2 - конкретная реализация арифметического блока; на фиг.З блок синхронизации.

Устройство для обработки изображений содержит блок синхронизации 1,. блок памяти 2, блок постоянной памяти (коэффициентов) 3, арифметический блок 4, блок памяти 5, блок сдвига 6.

Вид обработки определяет набор операций, выполняемых арифметическим блоком 4. На фиг. 2 приведена реализация арифметического блока для выполнения двумерной циклической свертки

;, М- V-1

f L. я - 51 h . . g

k.e

ij 1 I --J 3

где f „ - отсчеты обработанного

(выходного изображения);

, g L

, i4e.

кр k О, К, Г О, L - 1,

L - количество отсчетов в строке

изображения;

К - количество отсчетов в столбце изображения;

h.- коэффициенты весовой функции с которой производится циклическая свертка;

ё k,e отсчеты входного изображения Данньй арифметический блок содержит последовательно соединенные умножитель 7 и сумматор 8.

Блок синхронизации, представленный на фиг.З, содержит последователь но соединенные генератор 9 тактовых импульсов, счетчик адресов отсчетов 10, счетчик адресов коэффициентов 11 и схему формирования сдвигов 12, которая в свою очередь содержит сумматор 13, счетчик вертикальных сдвигов 14, счетчик горизонтальных сдвигов 15 и дешифратор 16, определяющий момент, когда адреса коэффициентов равны q. N+1, q ,0, (М-1).

Устройство начинает функционировать, когда на информационный вход

512

блока 5 начнут |с)слеловл1ел но посгу пать отсчеты входного и-зображсния, В этот момент сдвиг, осуществляемьпЧ блоком сдвига 6, равен нулю, содержимое блока памяти 2 также равно нулю, отсчеты записываютсяВ последовательно расположенные ячейки блока 5 и одновременно проходят на выход блока 5 и поступают на вход арифметического блока 4, на другой вход которого из блока памяти коэффициентов

3поступает коэффициент hj, f

В арифметическом блоке 4 отсчеты g ,. g перемножаются на коэффициент

TM-I, N-1 умножителе и через сумматор поступают на вход блока памяти 2. Произведения g j, h д., |, записываются с начального адреса в последовательно расположенные

ячейки блока памяти 2. Адреса, по которым производится запись в блоке памяти 2, в этом цикле совпадают в каждый момент времени с адресами, по которым производится чтение отсчетов g Kg из блока памяти 5. Первый цикл заканчивается, когда в блоке памяти 5 будут записаны все KL отсчетов Входного изображения и в блоке памяти 2 будут записаны также

KL произведений g.g h м-,к- у

k (0, Ь-1), t О, L-1. В следующем цикле блоком 1 в блоке сдвига 6 задается сдвиг, равньй единице, т.е. адреса, по которым будет производиться выборка отсчетов из блока памяти 5, в каждый момент времени на единицу больше, чем адреса, по которым производятся чтение и запись в блок памяти 2. Одновременно из блока i поступает сигнал на вход блока памяти коэффициентов 3, изменяющий адрес, по которому производится выборка коэффициента. Из блока памяти коэффициентов 3 будет выбран

коэффициент Ьдд., .2 который поступит на вход арифметического блока 4. На вход арифметического блока

4поступят - отсчеты , , а на другой вход арифметического блока 4 произведения g к,р h д,. . ,

Отсчеты g(c,eti в умножителе арифметического блока 4 перемножаются с коэффициентом Ь,,, н-т. получившиеся произведения складываются в

сумматоре арифметического блока 4 с произведениями g ц h,.,- ) поступающих из блока памяти 2. Получившиеся частичные суммы ,x м 1, N-1 8к,е 1.,Ьд,., „ J запишутся в блок 2 на места произведений g „.f h д,, ,j . Второй цикл заканчивается, когда опять будет считано все содержимое блока памяти 5, а во всех ячейках блока памяти 2 будут сформированы суммы вида: (8к,8 h „., ц, + g,e,,. h.,) , К-1, t О, L,-1. В.следующем цикле из блока памя-, ти коэффициентов 3 будет выбран коэффициент Ьд,,| , а сдвиг в блоке сдвига 6 будет задан равным 2, и описаиньш цикл повторяется. В результате этого цикла в блоке памяти 2 будут сформированы суммы M-l,j к.е t N-j После N повторений таких циклов в блоке памяти 2 будут накоплены суммы:

Н-

ZIs

К.Е Ч - j -1

J--0

Далее указанные ранее N циклов повторяются для коэффициентов M-2,j J 0 N-1 и величин сдвигов L + J, j О, N-1, в результате 1185 10 5 2Q 25

Выходные отсчеты fx4MMetN-l последовательно поступают из блока памяти 2 на выход устройства, и блок памяти 2 обнуляется. 514 их выполнения в блоке тгамяти 2 Оудут накоплены суммы следующих N циклах из блока памяти коэффи1щентов 3 будут выбираться коэффициенты h .. , j 0, N-1 и в блоке сдвигов 6 будут задаваться величины сдвигов, равные 2L+J j О, N-1. В результате в блоке памяти 2 будут накоплены суммы м-1 М-1 .P N-j- -J После М N циклов в блоке памяти 2 будут сформированы суммы вида: .,,,.,p,.j.; h.. которые являются выходньп ш отсчетами обработанного изображения

Риг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки изображений | 1987 |

|

SU1464176A1 |

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для обработки информации | 1989 |

|

SU1665388A1 |

| Устройство параллельной обработки видеоинформации | 1984 |

|

SU1262527A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| Цифровой коррелятор | 1976 |

|

SU636619A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

1. УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ, содержащее блок сдвига, управляющий вход которого подключен к первому выходу блока синхронизации, второй выход которого подключен к информационному входу блока сдвига и адресному входу первого блока памяти, выход которого является информационным выходом устройства, отличающееся тем, что, с целью увеличения бьютродействия, в него введены блок постоянной памяти, умножитель, сумматор и второй блок памяти, выход которого подключен к первому входу умножителя, выход которого подключен Л первому входу сумматора, выход которого подключен к информационному входу первого блока памяти, выход которого подключен к второму входу суммато ра, третий выход блока синхронизации подключен к адресному входу блока постоянной памяти, выход которого подключен к второму входу умножителя, информационный выход блока сдвига подключен к адресному входу второго блока памяти, информационный вход которого является информационным входом устройства. 2. Устройство по П.1, от л и чающееся тем, что блок синхронизации содержит сумматор, дешифi ратор, четыре счетчика и генератор (Л тактовых импульсов, выход которого подключен к счетному входу первого счетчика, выход переноса которого подключен к счетным входам второго и третьего счетчиков, информационные выходы которых соединены соответственно с входом дешифратора и первым входом сумматора, второй вход кото00 СП рого подключен к информационному выходу четвертого счетчика, счетный со ел вход которого соединен с установочным входом третьего счетчика и подключен к выходу дешифратора, выход сумматора, информационные выходы первого и второго счетчиков являются соответственно первым, вторым и третьим выходами блока синхронизации.

| Рабинер Л., Гоулд Б | |||

| Теория о применении цифровой обработки сигналов | |||

| - М.: Мир, 1978 | |||

| Авторское свидетельство СССР № 913418, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-15—Публикация

1983-07-19—Подача