I

Изобретение относится к специа.пиэированным средствам цифровой вьлчислительной техники и может быть использовано при измерении функции корреляции случайных сигналов в режиме эксперимента по дискретным временным выборкам наблюдаеглых сигналов,

Известен коррелятор-аналог l, содержащий запоминающую ячейку, квантователь, промежуточное запоминающее устройство, блок умножения, элемент ИЛИ, два к.гаоча, три тактовых генератора, управляющий триггер, коммутатор и ряд интеграторов.

Недостатком этого коррелятора явля ется то, что он требует увеличения времени измерения корреляционных функций, так как при его работе осуществляется предварительное запоминание ряда отсчетов входного сигнала, а затем происходит процесс их обработки арифметическими узлами. Во время работы арифметических узлов часть сигнала не используется.

Наиболее близок по построению высокоточный динамический цифровой коррелятор 2, содержащий аналого-цифропой г(реобразовате.пь, информационinifi вход которого является входом корР8.гятора, а виход подключен к первим

входам блока умножения и коммутатора, выход которого подключен к первому входу первого блока памяти, выход которого соединен со вторым входом коммутатора, блок управления, первьлй выход которого соединен с управляюишми входами аналого-цифрового преобразователя и с третьим входом коммутатора, второй выход блока управления соединен с первым входом второг-о блока памяти, выход которого подключен к первому входу сумматора, второй вход которого соединен с выходом блока умножения, выход сумматора подключен ко второму входу второго блока памяти.

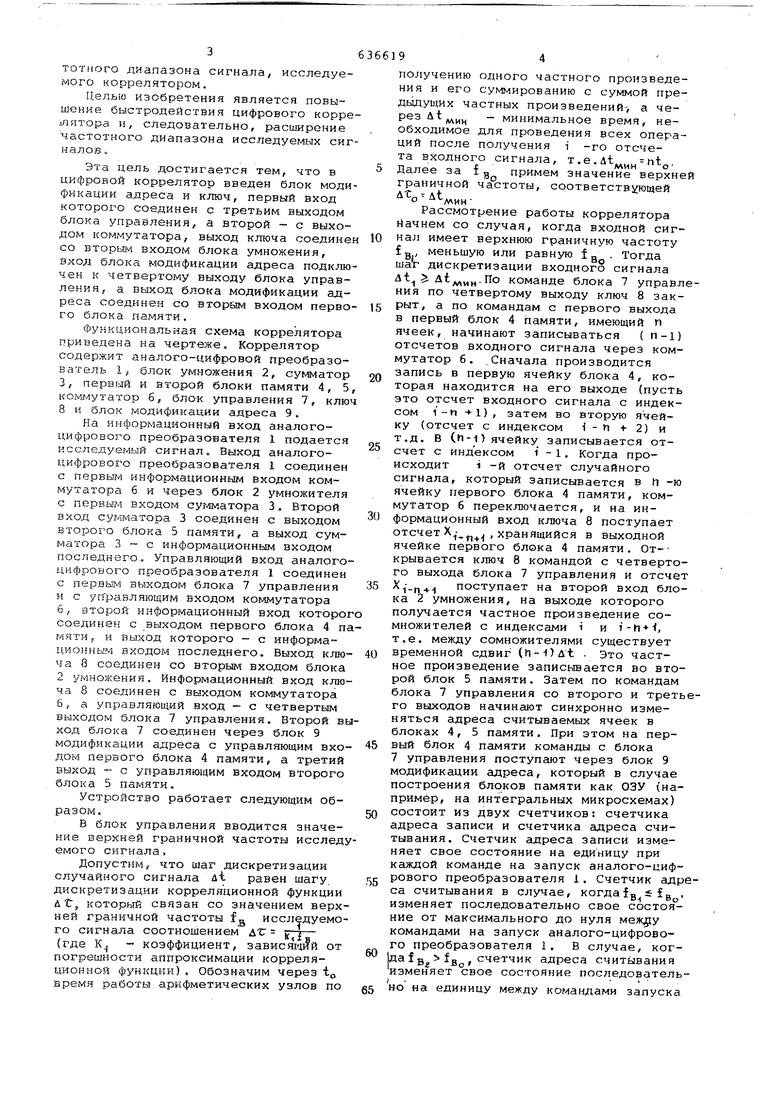

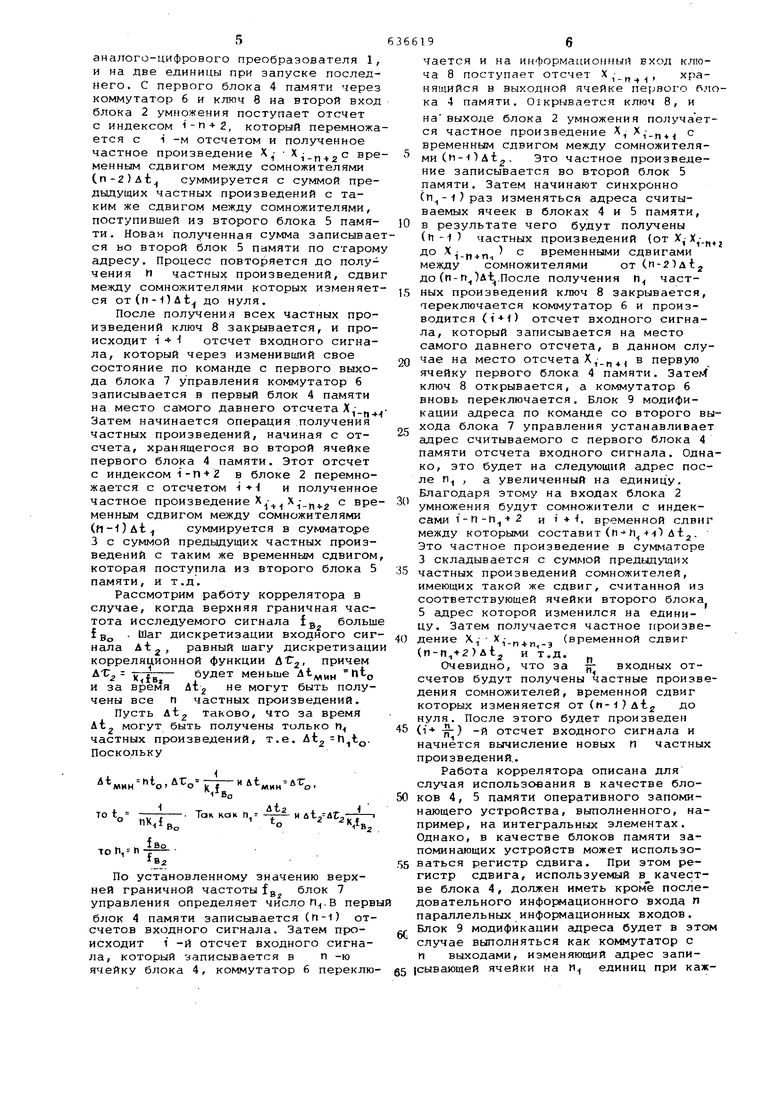

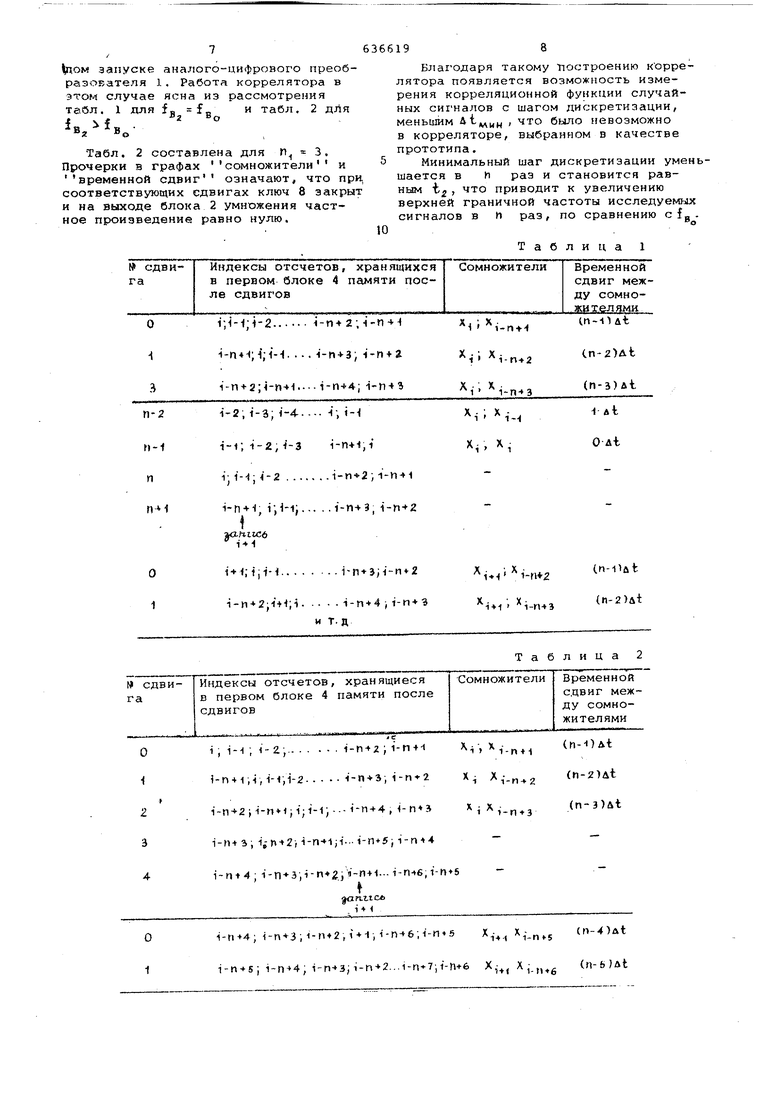

Недостатком динамического цифрового коррелятора является его относительно низкое быстродействие, ограничиваемое скоростью работы узлов арифметики. Так, при числе точек измерения корреляционной функЕХИи равном 200 и частоте запуска аналого-цифрового преобразователя 10 кГц, время получения одного частного произведения и его суммирования с прел адуцими равно 0,5 МКС, что является пределом для современных интегральных схем. Низкая частота квантования исследуемого сигнала приводит к сужению частотного диапазона сигнала, исследуемого коррелятором. Целью изобретения является повышение быстродействия цифрового коррелятора н, следовательно, расширение частотного диапазона исследуемых сигналов . Эта цель достигается тем, что в цифровой коррелятор введен блок модификации адреса и ключ, первый вход которого соединен с третьим выходом блока управления, а второй - с выходом коммутатора, выход ключа соединен со вторым входом блока умножения, вхол блока модификации адреса подключен к четвертому выходу блока управления, а выход блока модификации адреса соединен со вторбвд входом первого блока памяти. Функциональная схема коррелятора приведена на чертеже. Коррелятор содержит аналого-цифровой преобразователь If блок умножения 2, сумматор 3, первый и второй блоки памяти 4, 5 коммутатор 6, блок управления 7, ключ 8 и блок модификации адреса 9. На информационный вход аналогоцифрового преобразователя 1 подается исследуемый сигнал. Выход аналогоцифрового преобразователя 1 соединен с первым информационным входом коммутатора 6 и через блок 2 умножителя с первыт входом сумматора 3, Второй вход сугпматора 3 соединен с выходом второго блока 5 памяти, а выход сумматора 3 - с информационным входом последнего о Управляющий вход аналогоцифрового преобразователя 1 соединен с первы выходом блока 7 управления и с управляющим входом коммутатора б, второй информационный вход которог соединен с выходом первого блока 4 па мяти и выход которого - с информацио1 ным входом последнего. Выход ключа 8 соединен со вторым входом блока 2 умножения. Информационный вход ключа 8 соединен с выходом коммутатора б, а управляющий вход - с четвертым выходом блока 7 управления. Второй вы ход блока 7 соединен через блок 9 модификации адреса с управляющим входом первого блока 4 памяти, а третий выход - с управляющим входом второго блока 5 памяти. Устройство работает следующим образом. В блок управления вводится значение верхней граничной частоты исслед емого сигнала. Допустим, что шаг дискретизации случайного сигнала dt равен шагу, дискретизации корреляционной функции ufp который связан со значением верх ней граничной частоты f исследуемо го сигнала соотношением дг 5711в (где К - коэффициент, зави-сящйй от погрешности аппроксимации корреляционной функции) . Обозначим через t,, время работы арифметических узлов по получению одного частного произведения и его суммированию с суммой предыдущих частных произведений , а через - минимальное время, необходимое для проведения всех операций после получения i -го отсчета входного сигнала, т.е. At..,, nt-,. „ f -ДЛИН W Далее за ig примем значение верхней граничной частоты, соответствующей ,,,. Рассмотрение работы коррелятора Начнем со случая, когда входной сигнал имеет верхнюю граничную частоту ц меньшую или равную f . Тогда шаг дискретизации входного сигнала At $ At. По команде блока 7 управления по четвертому выходу ключ 8 закрыт, а по командам с первого выхода в первый блок 4 памяти, имеющий п ячеек, начинают записываться ( п-1) отсчетов входного сигнала через коммутатор 6. .Сначала производится запись в первую ячейку блока 4, которая находится на его выходе (пусть это отсчет входного сигнала с индексом 1 -п 1) , затем во вторую ячейку (отсчет с индексом i - я 2) и т.д. В Сп-1) ячейку записывается отсчет с индексом 1 - 1. Когда происходит i -и отсчет случайного сигнала, который записывается в п -ю ячейку первого блока 4 памяти, коммутатор 6 переключается, и на информационный вход ключа 8 поступает отсчет . , хранящийся в выходной ячейке первого блока 4 памяти. От-крывается ключ 8 командой с четвертого выхода блока 7 управления и отсчет поступает на второй вход блока 2 умножения, на выходе которого получается частное произведение сомножителей с индексами i и i-n, т.е. между сомножителями существует временной сдвиг (М--1)1 - Это частное произведение записывается во второй блок 5 памяти. Затем по командам блока 7 управления со второго и третьего выходов начинают синхронно изменяться адреса считываемых ячеек в блоках 4, 5 памяти. При этом на первый блок 4 памяти команды с блока 7 управления поступают через блок 9 модификации адреса, который в случае построения блоков памяти как ОЗУ (например, на интегральных микросхемах) состоит из двух счетчиков: счетчика адреса записи и счетчика адреса считывания. Счетчик адреса записи изменяет свое состояние на единицу при каждой команде на запуск аналого-цифрового преобразователя 1. Счетчик адреса считывания в случае, когдаfg i fg. изменяет последовательно свое состояние от максимального до нуля меяфу командами на запуск аналого-цифрового преобразователя 1. В случае, когLaafg fв , счетчик адреса считывания свое состояние последовательно на единицу между командами запуска 5 аналого-цифрового преобразователя 1 и на лве единицы при запуске послед него. С первого блока 4 памяти чере коммутатор 6 и ключ 8 на второй вхо блока 2 умножения поступает отсчет с индексом i-n + 2, который перемнож ется с 1 -м отсчетом и полученное частное произведение X. 1-042 менным сдвигом между сомножителями (n-2)A-fc суммируется с суммой пре дыдущих частных произведений с таким же сдвигом между сомножителями, поступившей из второго блока 5 памя ти. Новая полученная сумма записыва ся во второй блок 5 памяти по старом адресу. Процесс повторяется до полу чения И частных произведений, сдви между сомножителями которых изменяет ся oT(n-i}At до нуля. После получения всех частных произведений ключ 8 закрывается, и происходит -1 отсчет входного сигнала, который через изменивЕиий свое состояние по команде с первого выхода блока 7 управления коммутатор 6 записывается в первый блок 4 памяти на место самого давнего отсчета X; ,,1 пЗатем начинается операция получения частных произведений, начиная с отсчета, хранящегося во второй ячейке первого блока 4 памяти. Этот отсчет с индексом 1-п-«-2 в блоке 2 перемножается с отсчетом -i и полученное частное произведение с вре менным сдвигом между сомножителями (fl-OAt суммируется в сумматоре 3 с суммой предьщущих частных произведений с таким же временным сдвигом которая поступила из второго блока 5 памяти, и т.д. Рассмотрим работу коррелятора в случае, когда верхняя граничная частота исследуемого сигнала fg больш «- . Шаг дискретизации входного сиг нала At 2, равный шагу дискретизаци корреляционной функции С, причем 1ГТв- будет меньше ntg и за время Atg не могут быть получены все п частных произведений. Пусть 2 таково, что за время At могут быть получены только П частных произведений, т.е. -И оПоскольку MMH 0 o jf| мин о. Так как п -т- и й1,ДГ По установленному значению верхней граничной частоты f g, блок 7 управления определяет число 1.в перв блок 4 памяти записывается (Г)-1) отсчетов входного сигнала. Затем происходит 1 -и отсчет входного сигнала, который записывается в п -ю ячейку блока 4, коммутатор 6 переклю вр 19 чается и на информацион 1ый вход ключа 8 поступает отсчет X нящийся в выходной ячейке первого блока 4 памяти. Открывается ключ 8, и на выходе блока 2 умножения получается частное произведение Х Х,- с временным сдвигом между сомножителями (и . Это частное произведение записывается во второй блок 5 памяти. Затем начинают синхронно (п -1}раз изменяться адреса считываемых ячеек в блоках 4 и 5 памяти, в результате чего будут получены (и--() частных произведений (от X,. до -Х ) с временными сдвигами между сомножителями от (п-2)д42 до (n-rt)Afc,.После получения п частных произведений ключ 8 закрывается, переключается коммутатор 6 и производится ( f) отсчет входного сигнала, который записывается на место самого давнего отсчета, в данном случае на место отсчета Х,- в первую ячейку первого блока 4 памяти. Затег ключ 8 открывается, а коммутатор 6 вновь переключается. Блок 9 модификации адреса по команде со второго выхода блока 7 управления устанавливает адрес считываемого с первого блока 4 памяти отсчета входного сигнала. Однако, зто будет на следующий адрес после л , а увеличенный на единицу. Благодаря этому на входах блока 2 умножения будут сомножители с индексами i-n-n - 2 и , временной слвиг между которыми составит (п- частное произведение в сутиматоре 3 складывается с суммой предыдущих частных произведений сомножителей, имеющих такой же сдвиг, считанной из соответствующей ячейки второго блока 5 адрес которой изменился на единицу. Затем получается частное произведение 4 .,..„ , (временной сдвиг 1 - 1-n-frri,-3 (n-n,-t2)At., и Т.Д. Очевидно, что за входных отсчетов будут получены частные произведения сомножителей, временной сдвиг которых изменяется от ( до нуля. После этого будет произведен (i -) -и отсчет входного сигнала и начнется вычисление новых п частных произведений.. Работа коррелятора описана для случая использования в качестве блоков 4, 5 памяти оперативного запоминающего устройства, выполненного, например, на интегральных элементах. Однако, в качестве блоков памяти запоминающих устройств может использоваться регистр сдвига. При этом регистр сдвига, используемый в качестве блока 4, должен иметь кромЪ последовательного инфО1 ационного входа п параллельных информационных входов. Блок 9 модификации адреса будет в этом случае выполняться как коммутатор с и выходами, изменяющий адрес записывающей ячейки на И единиц при каж1дом запуске аналого-цифрового преобразователя 1. Работа коррелятора в этом случае ясна из рассмотрения табл. 1 для f fо и табл. 2 дЛя i«

B

В,

Табл. 2 составлена для П 3. Прочерки в графах сомножители и временной сдвиг означают, что при соответствующих сдвигах ключ 8 закрыт и на выходе блока 2 умножения частное произведение равно нулю.

Благодаря такому построению коррелятора появляется возможность измерения корреляционной функ11ии случайных сигналов с шагом дискретизации, меньшим Дt,д , что было невозможно в корреляторе, выбранном в качестве прототипа.

Минимальный шаг дискретизации уменьшается в h раз и становится равным t , что приводит к увеличению верхней граничной частоты исследуемых сигналов в и раз, по сравнению с f .

. °

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛОМЕТР | 1972 |

|

SU419895A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Цифровой коррелятор | 1979 |

|

SU851412A1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Многоканальный коррелятор | 1977 |

|

SU646341A1 |

| Цифровой коррелятор | 1986 |

|

SU1328825A1 |

i , i--i ; -2,1-п4д; 1-n + + 1

1-П + 1И,1-1,1-21-n-v3,

)1;1-i; -.- i-n-b4 , , X i-n + 3

i-M+3; i,) ... i-n+5) i-n 4i-nt 4 ; ,.j 1-пчв,1-п + .ггсА i-n+4; ,, ., . i-n + 5 ; i-n + 4; i-n + 2.,.i-n 7|i-n+6

Таблица 2

(n-l)At (n-2)At (n-3)ut (п-4)д1 (Формула изобретения

Цифровой коррелятор, содержащий аналого-цифровой преобразователь, информационный вход которого является входом коррелятора, а выход подключен к первым входам блока умножения и коммутатора, выход которого подключен к первому входу первого блока памяти, выход которого соединен со вторым входом коммутатора, блок управления, первый выход которого соединен с управляющими входами аналого-цифрового преобразователя и с третьим входом коммутатора, второй выход блока управления соединен с первым входом второго блока памяти, выход которого подключен к первому входу сумматора, второй вход которого соединен с выходом блока умножения ВЫХОД сумматора подключен ко второму

входу второго блока памяти, о т л ичающийся тем, , с целью повышения быстродействия цифрового коррелятора, в него введен блок модификации сШреса и ключ, первый вход которого соединен с третьим выходом блока управления, а второй - с выходом коммутатора, выход ключа соединен со вторым входом блока умножения, вход блока модификации гщреса подключен к четвертому выходу блока управления, а выход блока модификации адреса соединен с вторым входом первого блока памяти.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-12-05—Публикация

1976-12-13—Подача