Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сейсмических,: акустических и других сигналов.

Формула свертки, реализуемая .фильтром, имеет вид:

(1)

V-n.

где h- - весовые коэффициентыj

X. - отсчеты входного сигнала.

1

Для реализации этого алгоритма «еобходимо, очевидно, обращение к (памяти входных отсчетов. Симметрич- ность импульсной характеристики позволяет сократить число умножений, если входные отсчеты, которые должны умножаться на симметричные коэффи- циенты, предварительно просуммироват и затем умножить на соответствующий

:коэффициент. Но в этом случае в известном устройстве не повышается быстродействие системы, так как на

.одно умножение приходится дважды об- ращаться к памяти входных отсчетов. Кроме того, структура известного устройства, не позволяет распараллелить процесс вычисления.

Цель изобретения - повьшение быстродействия цифрового фильтра.

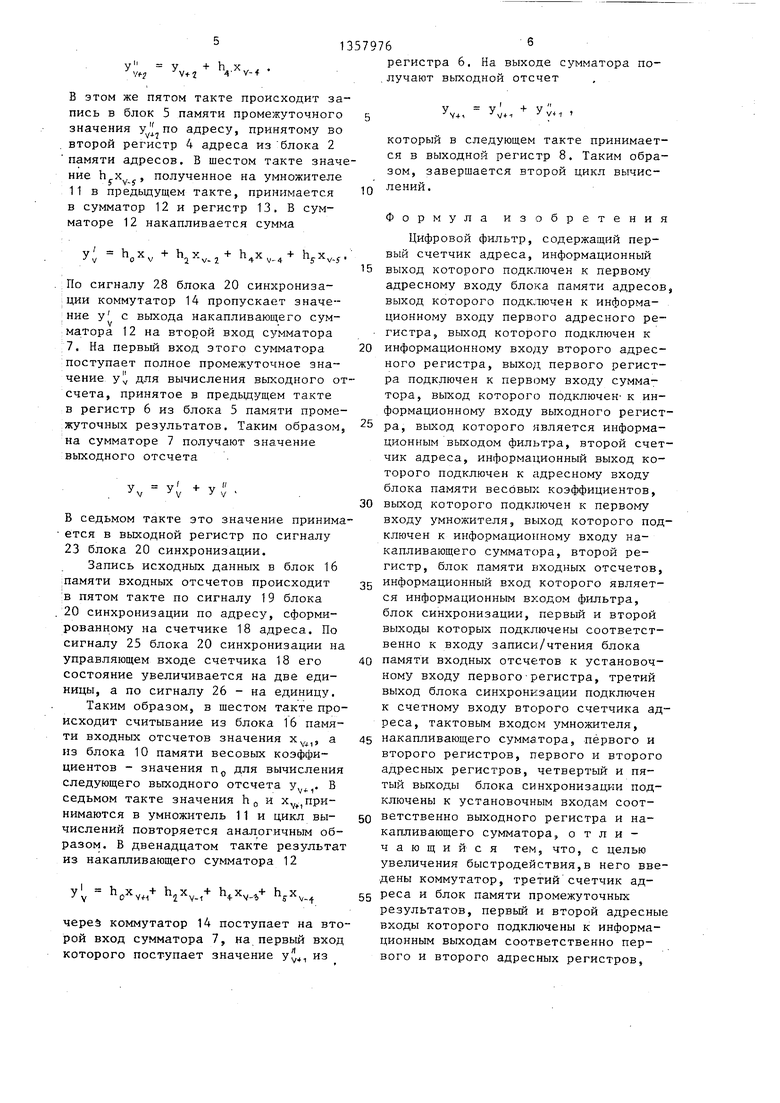

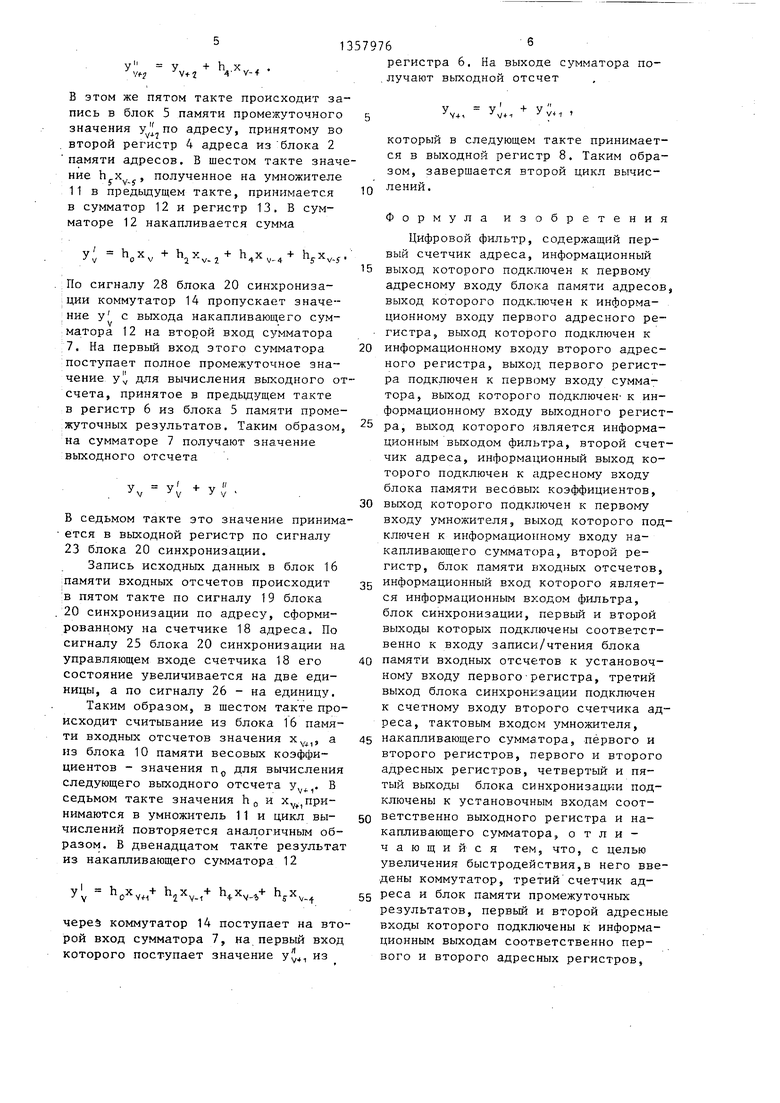

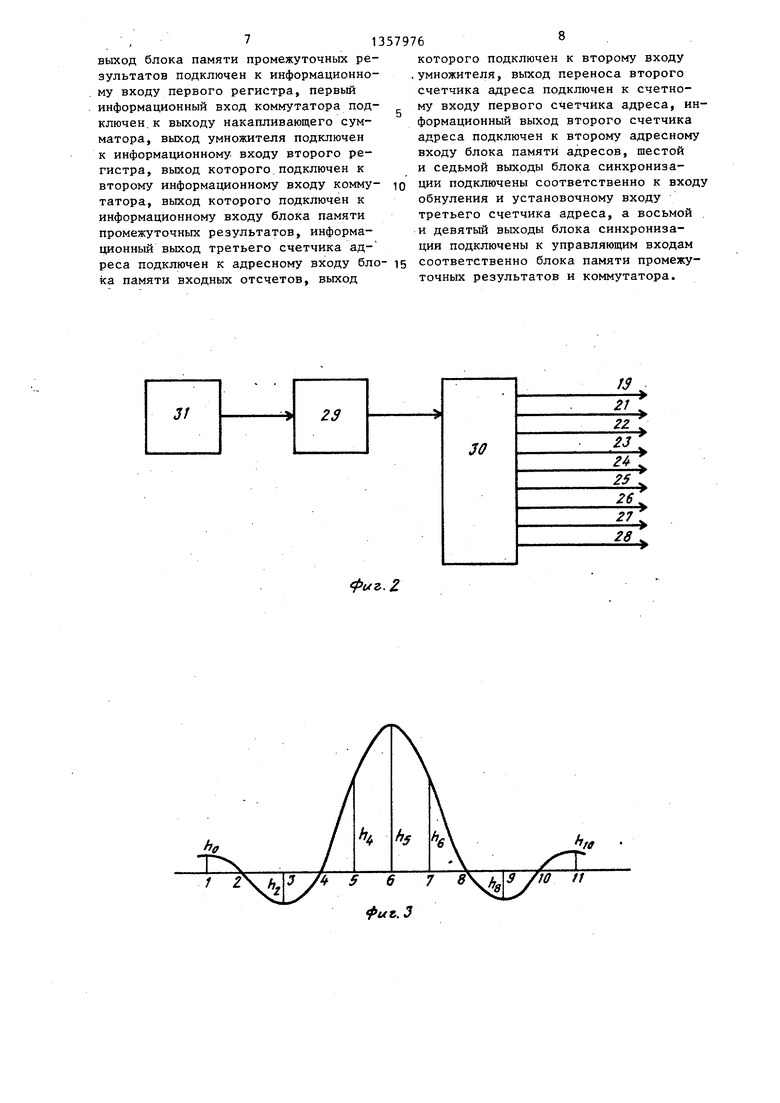

На фиг. 1 представлена блок-схема цифрового фильтра; на фиг. 2 - блок- схема блока синхронизации; на фиг.З .импульсная характеристика фильтра; ;на фиг. 4 - временные диаграммы уп равляющих сигналов, вьфабатываемых блоком синхронизации.

,

Цифровой фильтр (фиг. 1) содержит

счетчик 1 адреса, блок 2 памяти адресов, адресные регистры 3 и 4, блок 5 памяти промежуточных результатов, регистр 6, сумматор 7, выходной ре- гистр 8, счетчик 9 адреса, блок 10 памяти весовых коэффициентов, умножитель 11, накапливающий сумматор 12, регистр 13, коммутатор 14, информационный выход 15 цифрового фильтра блок 16 памяти входных отсчетов, информационный вход 17 цифрового фильтра, с четчик 18 адреса, выход 19 блока 20 синхронизации и выходы 21-28 блока 20 синхронизации.

Блок синхронизации 20 (фиг. 2) содержит счетчики 29 и 30 постоянной памяти и генератор 31 тактовых импульсов.

0

g Q

5

Q

0

g

5

Для иллюстрации работы устройства рассмотрим в качест)зе примера реализацию цифрового фильтра с импульсной характеристикой, представленной на i фиг. 3. Общее число коэффициентов равно 11. В силу симметрии характеристики общее число ненулевых коэффициентов равно (N+0/2+1 7, а число различных ненулевых коэффициентов равно 4 (3 боковых и 1 центральный). Для сокращения времени получения выходного отсчета у по формуле (1) предлагается результаты умножения hpX, .,. i , , запоминать и накапливать, так к;ак в силу симметрии h, h, h , h h.j,...) полученные промежуточные результаты будут использованы соответственно при получении следующих выходных отсче ° V., Уv.J-2 V.

Цроизведение входньпс отсчетов на центральный коэффициент не хранится, так как они принимают участие в вычислениях только один раз. Вместо (N-1)/2+1 обращений к памяти входных отсчетов (с учетом симметричности импульсной характеристики) для вычислений по формуле (1) их потребуется в два раза меньше.

Рассмотрим вычисление v-ro результирующего отсчета фильтра у при длине импульсной характеристики ,N 11, В этом случае счетчик 18 адреса работа- ет по модулю М, (N+1), счетчик 9 адреса - по модулю М (М1+1)/2 4, счетчик 1 адреса - по модулю М . С целью упрощения описания работы цифрового фильтра будем считать, что прием информации во все регистры, умножитель, накапливающий сумматор, переключение счетного триггера и счетчиков осуществляется положительным перепадом синхроимпульсов, режиму записи в блоки 5 и 16 памяти соответствует нулевое значение на управляющем входе, а режиму чтения - единичные; сигналу переноса счетчиков соотнетствует нулевое значение на вьпсоде переноса; нулевое значение на управляющем входе блока 5 памяти соответствует чтению по адресу на первом адресном входе и записи по адресу на втором адресном входе. Адресация блока 16 памяти входных отсчетов обеспечивается счетчиком 18 и блоком 20. Наблюдается последовательность адресов, формируемых для записи входных отсчетов в

313579764

этот блок, а также для чтения исход- В остальных тактах в сумматоре 12 ных данных из него.происходит последовательное накапДля адресации блока 10 памяти ве- ливание следующих произведений (ум- совых коэффициентов используется вто- ножение на нулевые коэффициенты не рой счетчик 9 адреса, который изменя- выполняется): ,, Ь,х , h х , ет свое состояние по сигналу 22 бло- Ь.х.

ка 20 синхронизации. Для адресации В третьем такте по сигналу 21 блока 5 памяти промежуточных резуль- блока 20 синхронизации происходит татов используется блок 2 памяти ад- установка в нуль регистра 6. По сиг- ресов, в котором хранятся адреса за- 10 налу 28 блока 20 синхронизации зна- писи получаемых промежуточных резуль- чение с выхода регистра 13 проходит татов и адрес чтения накопленного через коммутатор 14 на второй вход

сумматора 7. Полученная сумма у ЬдХ + (2 выхода сумма- 15 тора 7 поступает на информационный вход блока 5 памяти промежуточных результатов и записывается в блок 5 памяти по адресу, хранящемуся в регистре 4 адреса. По этому адресу бупромежуточного результата у. Производится прошивка блока 2 памяти адресов. Адрес записи из второго регистра 4 адреса поступает на второй адресный.вход блока 5 памяти. Адрес чтения принимается в первый регистр 3 адреса и поступает на первый адресный вход этого же блока. Для адреса- 20 дет храниться накапливающийся проме- ции блока 2 памяти адресов исполь- жуточный результат вычисления

V-f-ro выходного отсчета у . Б четвертом

зуются первьш 1 и второй 9 счетчики адреса. Необходимо учесть, что прошивка блока 2 памяти адресов выполне3- 25

на со сдвигом на один адрес по отно- ведения h х на выходе накапливаюшению к адресам блока 16 памяти входных отсчетов и блока 10 весовых коэффициентов для согласования длины цепочки формирования слагаемых у h,x.+ ./и у;

щего сумматора 12 и регистра 13. В это время в сумматор 12 и регистр 1 принимается произведение , выданное из умножителя з предыдущем 30 такте. В сумматоре 12 получаем сумму у ЪдХ + h X . Произведение h Ху.с выхода регистра 13 через коммутатор 14 поступает на второй вход сумматора 7. На первый вход этого

для получения выходного отсчета у :

щего сумматора 12 и регистра 13. В это время в сумматор 12 и регистр 13 принимается произведение , выданное из умножителя з предыдущем 30 такте. В сумматоре 12 получаем сумму у ЪдХ + h X . Произведение h Ху.с выхода регистра 13 через коммутатор 14 поступает на второй вход сумматора 7. На первый вход этого

памяти накопленное значение промежуточного результата Уу+ для вычисления выходного отсчета Уу+. На сумУМ Уу + y v

Цикл вычисления выходного отсчета составляет 6 тактов. В исходном состоянии счетчики 1 и 9 установлены 35 сумматора поступает принятое в пре- в нулевое состояние, а счетчик 18 - дьщущем такте в регистр 6 из блока 5 в состояние 001.

В первом такте работы фильтра в умножитель 11 по сигналу 22 блока 20

синхронизации принимается входной 40 маторе 7 выполняется сложение отсчет х и весовой коэффициент h.

Во втором такте произведение выдается из умножителя 11 и поступает на входы накапливающего сум- В шестом такте произведение h х вы- матора 12 и регистра 13. В этом же 45 дается из умножителя 11, значение такте в умножитель 11 принимаются ,,.принимается в сумматор 12 и ре- входной отсчет весовой коэффи- гистр 13. В сумматоре 12 происходит циент Ьд.накопление суммы

у у + h х„,.

V-ffe 1 V-t

50

В третьем такте в умножитель 11 принимаются значения х и h, произведение h X принимается в накапли- - вающий сумматор 12 и в регистр 13 (по управляющему сигналу 22 блока 20 синхронизации). Причем накапливающий „ сумматор 12 находится в режиме без накопления (на управляющем выходе 24 блока 20 синхронизации уровень логического нуля).

20 дет храниться накапливающийся проме- жуточный результат вычисления

25

V-f-ro выходного отсчета у . Б четвертом

fo

такте происходит прием значений х j. и h в умножитель 11 и выдачи произ ведения h х на выходе накапливающего сумматора 12 и регистра 13. В это время в сумматор 12 и регистр 13 принимается произведение , выданное из умножителя з предыдущем такте. В сумматоре 12 получаем сумму у ЪдХ + h X . Произведение h Ху.с выхода регистра 13 через коммутатор 14 поступает на второй вход сумматора 7. На первый вход этого

сумматора поступает принятое в пре- дьщущем такте в регистр 6 из блока 5

памяти накопленное значение промежуточного результата Уу+ для вычисления выходного отсчета Уу+. На сумсумматора поступает принятое в пре- дьщущем такте в регистр 6 из блока 5

маторе 7 выполняется сложение

е 7 выполняется сло

том такте произведе я из умножителя 11, принимается в сумма 13. В сумматоре 12 ление суммы

у у + h х„,.

V-ffe 1 V-t

у; ь,х -f .

с вькода регистра 13 значение , через коммутатор 14 поступает на второй вход сумматора 7, на котором суммируется с принятым в четвертом такте в регистр 6 из блока 5 памяти накопленным промежуточным результатом у ,,. для вычисления выходного отсчета

v l . V45у;;, v, + v-4

1357976

регистра 6. На выходе сумматора по- ,лучают выходной отсчет

В этом же пятом такте происходит запись в блок 5 памяти промежуточного значения yJL по адресу, принятому во второй регистр 4 адреса из блока 2 памяти адресов. В шестом такте значение Ь X , полученное на умножителе 11 в предыдущем такте, принимается в сумматор 12 и регистр 13. В сумматоре 12 накапливается сумма

у Ь„х + Кх . + h.x

а V-Z

+ h,x

у V-5

По сигналу 28 блока 20 синхронизации коммутатор 14 пропускает значе;ние у с выхода накапливающего сумматора 12 на второй вход сумматора

7. На первый вход этого сумматора поступает полное промежуточное значение у для вычисления выходного отсчета, принятое в предьщущем такте в регистр 6 из блока 5 памяти промежуточных результатов. Таким образом, на сумматоре 7 получают значение выходного отсчета

У У V - V

В седьмом такте это значение принимается в выходной регистр по сигналу 23 блока 20 синхронизации.

Запись исходньпс данных в блок 16 ;памяти входных отсчетов происходит ;в пятом такте по сигналу 19 блока 20 синхронизации по адресу, сформированному на счетчике 18 адреса. По сигналу 25 блока 20 синхронизации на управляющем входе счетчика 18 его состояние увеличивается на две единицы, а по сигналу 26 - на единицу.

Таким образом, в шестом такте происходит считывание из блока 16 памяти входных отсчетов значения х,, а из блока 10 памяти весовых коэффициентов - значения п для вычисления следующего выходного отсчета У.,. В седьмом такте значения h и х,принимаются в умножитель 11 и цикл вычислений повторяется аналогичным образом. В двенадцатом такте результат из накапливающего сумматора 12

Уу 4Xv-4+

череэ коммутатор 14 поступает на второй вход сумматора 7, на первый вход которого поступает значение у(, из

V+1

у, у.

который в следующем такте принимается в выходной регистр 8. Таким образом, завершается второй цикл вычислений.

Формула изобретения

Цифровой фильтр, содержащий первый счетчик адреса, информационный

выход которого подключен к первому адресному входу блока памяти адресов, выход KOTopoi o подключен к информационному входу первого адресного ре- гистра, выход которого подключен к

информационному входу второго адресного регистра, выход первого регистра подключен к первому входу сумматора, выход которого подключен- к информационному входу выходного регистра, выход которого является информационным выходом фильтра, второй счетчик адреса, информационный выход которого подключен к адресному входу блока памяти весовых коэффициентов,

выход которого подключен к первому входу умножителя, выход которого подключен к информационному входу накапливающего сумматора, второй регистр, блок памяти входных отсчетов,

информационный вход которого является информационным входом фильтра, блок синхронизации, первый и второй выходы которых подключены соответственно к входу записи/чтения блока

памяти входных отсчетов к установочному входу первогорегистра, третий выход блока синхронизации подключен к счетному входу второго счетчика адреса, тактовым входом умножителя,

накапливающего сумматора, первого и второго регистров, первого и второго адресных регистров, четвертый и пятый выходы блока синхронизации подключены к установочным входам соответственно выходного регистра и накапливающего сумматора, отличающийся тем, что, с целью увеличения быстродействия,в него введены коммутатор, третий счетчик адреса и блок памяти промежуточных

результатов, первый и второй адресные входы которого подключены к информационным выходам соответственно первого и второго адресных регистров.

. ,71

выход блока памяти промежуточных результатов подключен к информационному входу первого регистра, первый информационный вход коммутатора подключен, к выходу накапливающего сумматора, выход умножителя подключен к информационному входу второго регистра, выход которого,подключен к второму информационному входу комму- татора, выход которого подключен к информационному входу блока памяти промежуточных результатов, информационный выход третьего счетчика адреса подключен к адресному входу бло ka памяти входных отсчетов, выход

8

которого подключен к второму входу умножителя, выход переноса второго счетчика адреса подключен к счетному входу первого счетчика адреса, информационный выход второго счетчика адреса подключен к второму адресному входу блока памяти адресов, шестой и седьмой выходы блока синхронизации подключены соответственно к входу обнуления и установочному входу третьего счетчика адреса, а восьмой и девятый выходы блока синхронизации подключены к управляющим входам соответственно блока памяти промежуточных результатов и коммутатора.

фиг. Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1988 |

|

SU1555826A1 |

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1983 |

|

SU1149275A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах цифровой обработки сейсмических, акустических и других сигналов. Цель изобретения - увеличение быстродействия. Поставленная цель достигается за счет того, что в состав устройства входят счетчик 1 адреса, блок 2 памяти адресов, адресные регистры 3, 4, блок 5 памяти промежуточных результатов, регистр 6, сумматор 7, выходной регистр 8, счетчик адреса 9, блок 10 памяти весовых коэффициентов, умножитель 11, накапливающий сумматор 12, регистр 13, коммутатор 14, информационный выход 15 фильтра, блок 16 памяти входных отсчетов, информационный вход 17 фильтра, счетчик 18 адреса, выход 19 блока 20 синхронизации, выходы 21-28 блока 20 синхронизации. 4 ил.

Такты

/9

28

Ртг.

Редактор Е.Папп

Составитель А.Баранов Техред М.Ходанич

Заказ 6001/51 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор В.Бутяга

| Цифровой фильтр | 1982 |

|

SU1059670A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1986-07-25—Подача