тации и пятый блок сравнения, к входам которого подключены выходы второго блока коммутации и первого блока памяти, а выходы пятого блока сравнения подключены к третьему и четвертому входам второго решающего блока, при этом выходы первого и третьего решающих блоков подключены к входам элемента ИЛИ, первый выход которого подключен к четвертым входам второго и третьего блоков коммутации, а второй, тр.етий и четвертый .выходы элемента ИЛИ подключены к третьему, четвертому и пятому входам первого блока коммутации, выходы второго блока памяти подключены к первому и второму входам третьего блока сравнения, к третьему входу которого и второму входу четвертого блока сравнения подключен;, выход четвертого блока коммутации, первый и второй входы которого объединены с третьим:и четвертью входами третьего блока коммутации, а к третьему входу четвертого блока коммутации подключен выход блока регистрации знакоперемен, к первому и второму входам которого подключены соответственно выход выделителя фрон

5630

тов сигнала и первый вькод формирователя зоны анализа, второй, третий и четвертый выходы которого подключены к второму, третьему и четвертому входам блока оценки, а выход формирователя сигнала опорных частот подключен к входу делителя, первый выход которого подключен к третьему входу первого анализирующего блока, к четвертому входу которого, а также к третьим входам блока регистрации, блока фазирования, первого блока задержки, первого блока памяти, второго анализирующего блока, второго блока памяти, второго и третьего блоков задержки, выходного блока, анализатора дроблений, блока выделения тактовых интервалов без дроблений, блока регистрации знакоперемен, вторым входам третьего блока памяти, четвертого блока задержки и третьего решающе- го блока и пятым входам первого и второго решаюишх блоков, пятого блока сравнения, формирователя зоны йнализа подключен второй выход делителя, а выходы блока сравнения подключены к третьему и четвертому входам третьего решающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор двоичных сигналов | 1981 |

|

SU995346A1 |

| Регенератор двоичных сигналов | 1977 |

|

SU743211A1 |

| Измеритель краевых искажений | 1990 |

|

SU1737747A1 |

| Устройство для измерения преобладаний дискретных сигналов | 1979 |

|

SU879805A1 |

| Анализатор состояния сети обмена дискретными сообщениями | 1979 |

|

SU886261A2 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Устройство для регистрации слабых световых потоков | 1987 |

|

SU1541484A1 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

РЕГЕНЕРАТОР ДВОИЧНЫХ СИГНА-. ЛОВ, содержащий последовательно соединенные блок регистрации, первый блок задержки, первый блок коммутации и выходной блок, выход которого является выходом регенератора, последовательно соединенные первый анализирующий блок, первый блок памяти, первый блок сравнения и первый решающий блок, к третьему и четвертому входам которого подключены выходы второго блока задержки, последовательно соединенные блок выделения тактовых интервалов без дроблений, блок оченки и формирователь зоны анализа, а также анализатор дроблений, выделитель фронтов сигнала, второй анализирукяций блок, первый вход которого объединен с первыми входами блока регистрации, первого анализирующего блока, блока определения знака перепада, выдeлитeJJя фронтов сигнала и блока фазирования, выход которого через формирователь сигнала, опорных частот подключен к первому входу блока выделения тактовых интервалов без дроблений, вторым входам вьщелителя фронтов сигнала блока регистрации, первого и второго анализирующих блоков и четвертому входу формирователя зоны анализа, выход которого подключен к первому входу анализатора дроблений и второму входу блока определения знака перепада, выходы которого через последовательно соединенные второй блок памяти и второй блок сравнения подключены к входам второго блока задержки, при этом выходы первого анализирующего блока через второй блок коммутации подключены к третьему и четвертому входам первого блока сравнения, а к третьему и четвертому входам второго блока сравнения подключены через третий сл коммутатор выходы блока определения знака перепада, к третьему входу которого, а также к вторым входам блока формирования, блока выделения тактовых интервалов без дроблений и анализатора дроблений подключен выход выделителя фронтов сигнала, причем 00 выход анализатора дроблений подклюсд чен к третьему входу второго блока Од памяти, а выход второго анализирующего блока подключен к третьим вхо00 дам второго и третьего блоков комму- тации, четвертые входы которых объединены, отличающийся тем, что, с целью повышения точности регенерации двоичных сигналов, введены последовательно соединенные третий блок сравнения, третий блок задержки, второй решающий блок и элемент ИЛИ,последовательно соединенные блок регистрации знакоперемен,третий блок памяти, четвертый блок сравнения,четвертый блок задержки и третий решающий блок,а такжедел.итель, четвертый блок комму

1

Изобретение относится к области радиотехники и предназначено для использования в аппаратуре передачи данных и в качестве автономного устройства в системах связи.

Цель изобретения - повышение точности регенерации двоичных сигналов.

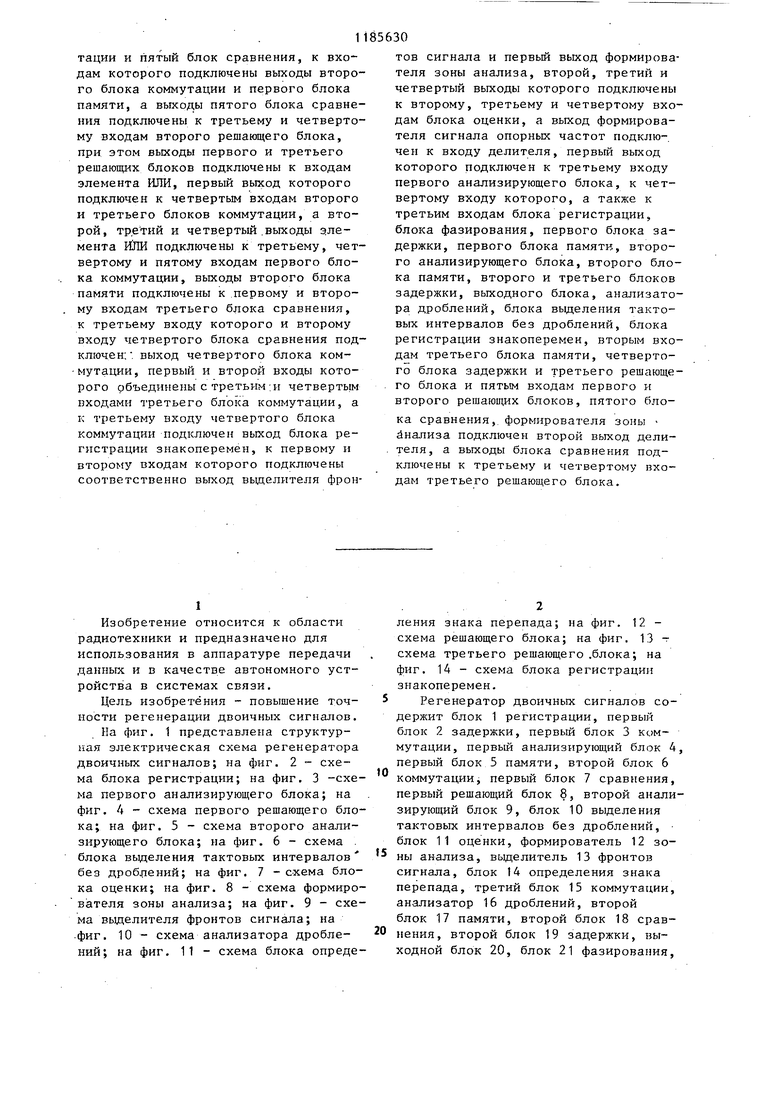

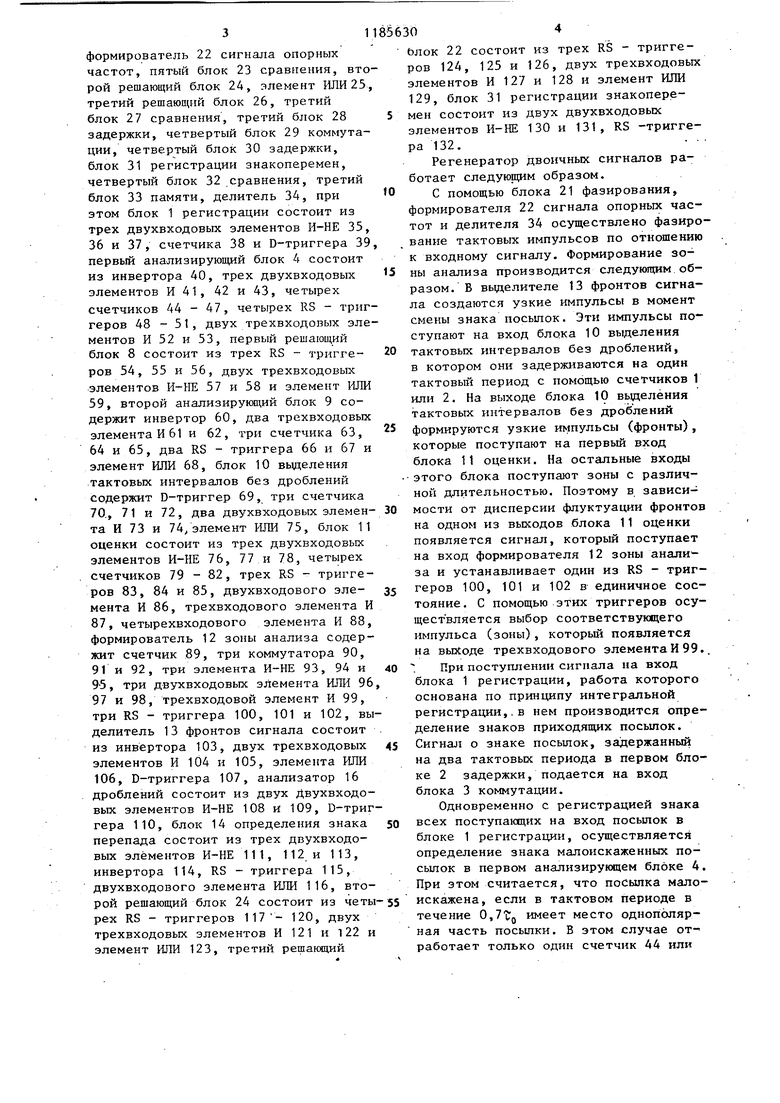

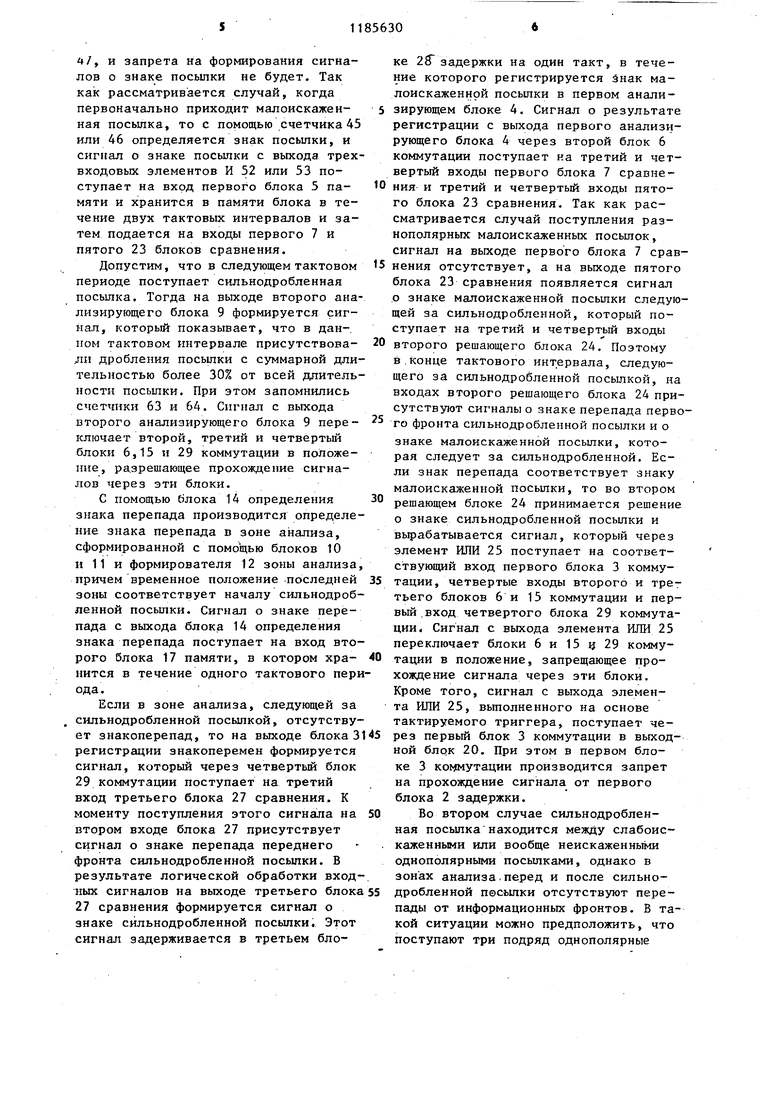

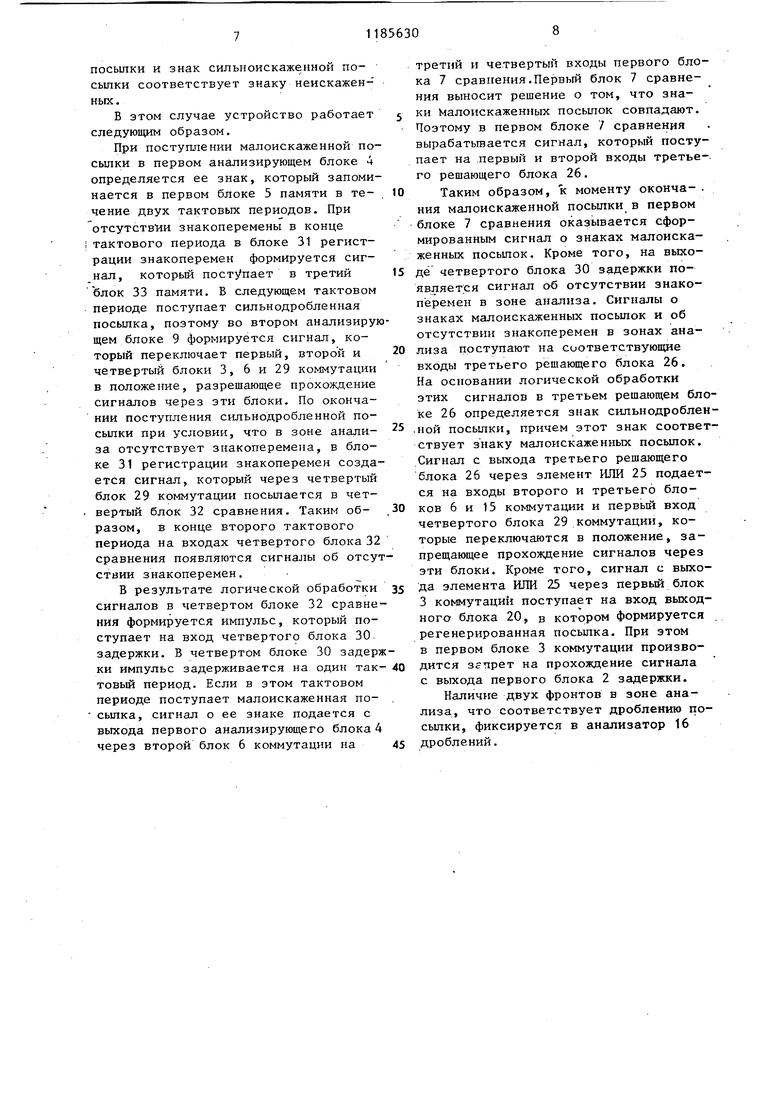

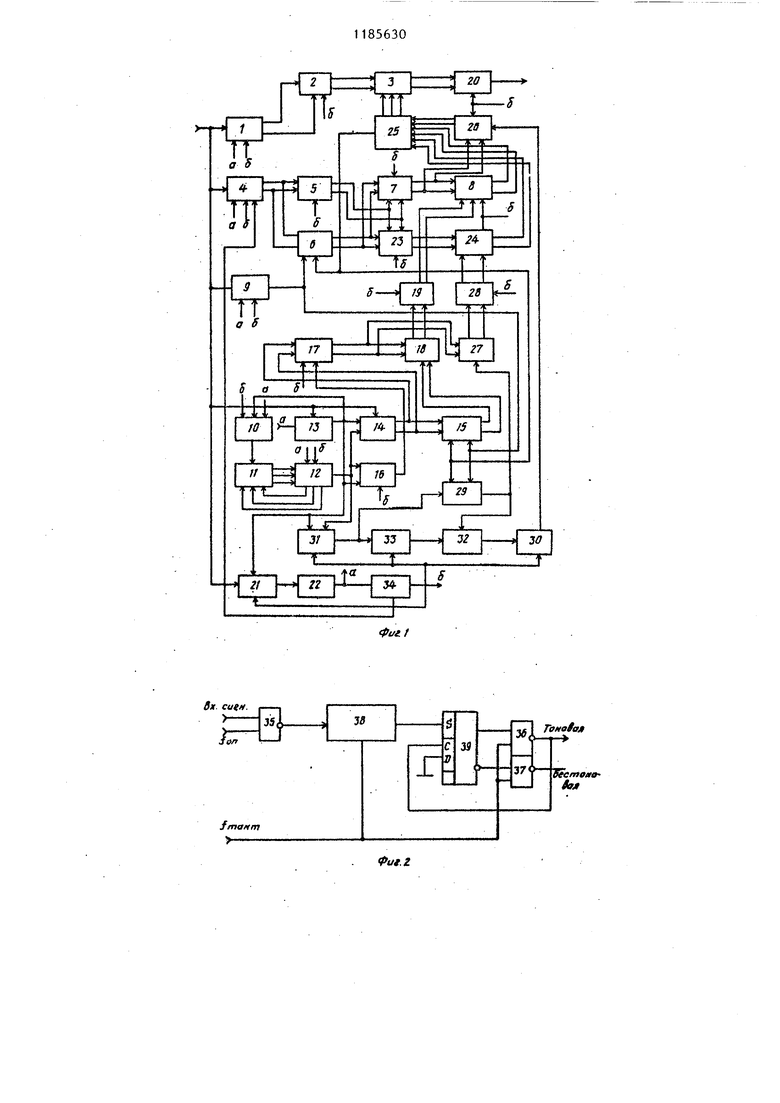

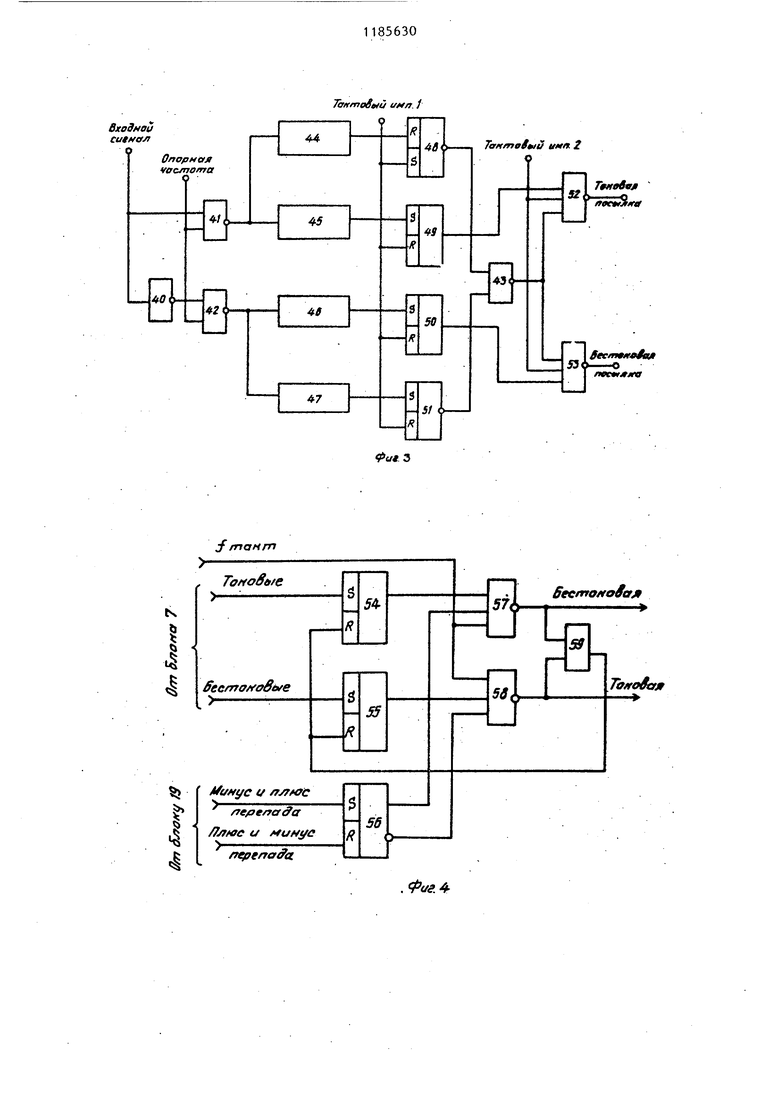

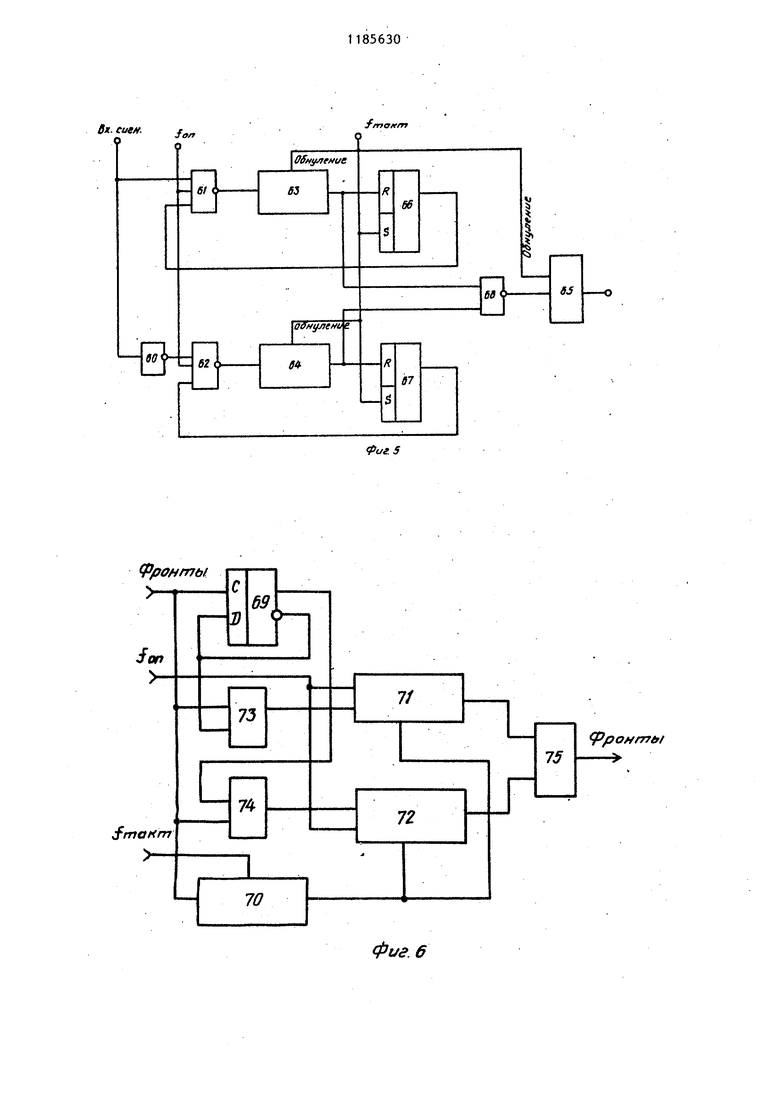

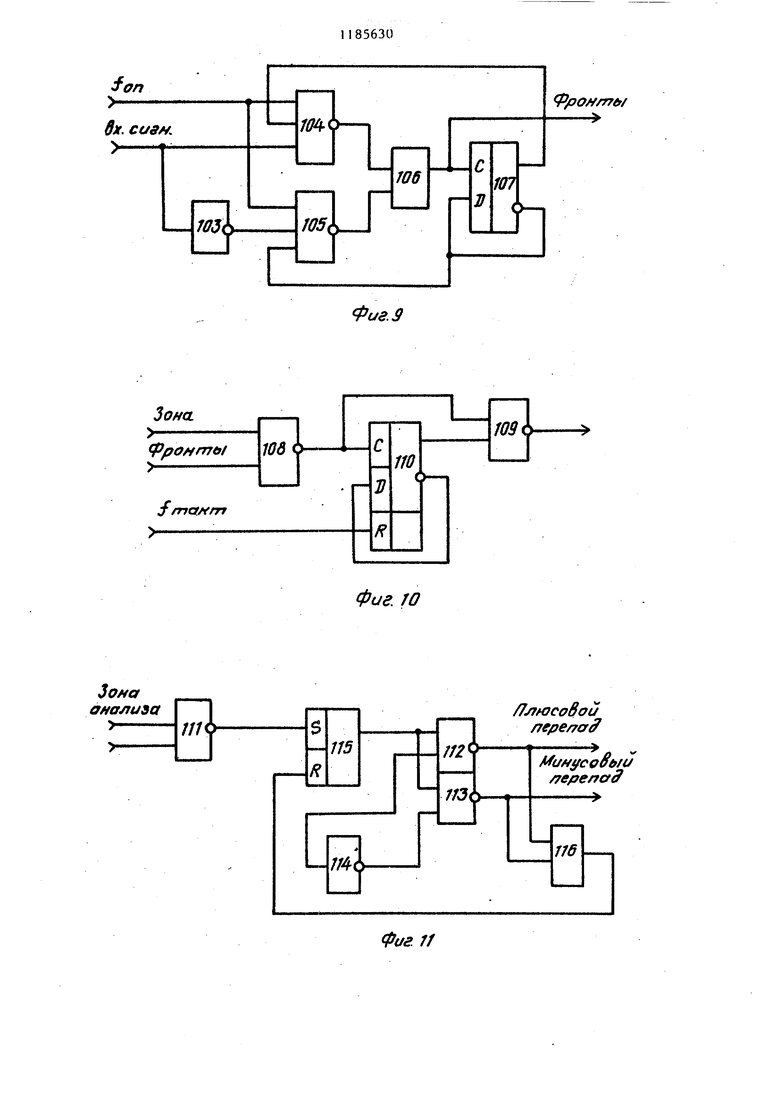

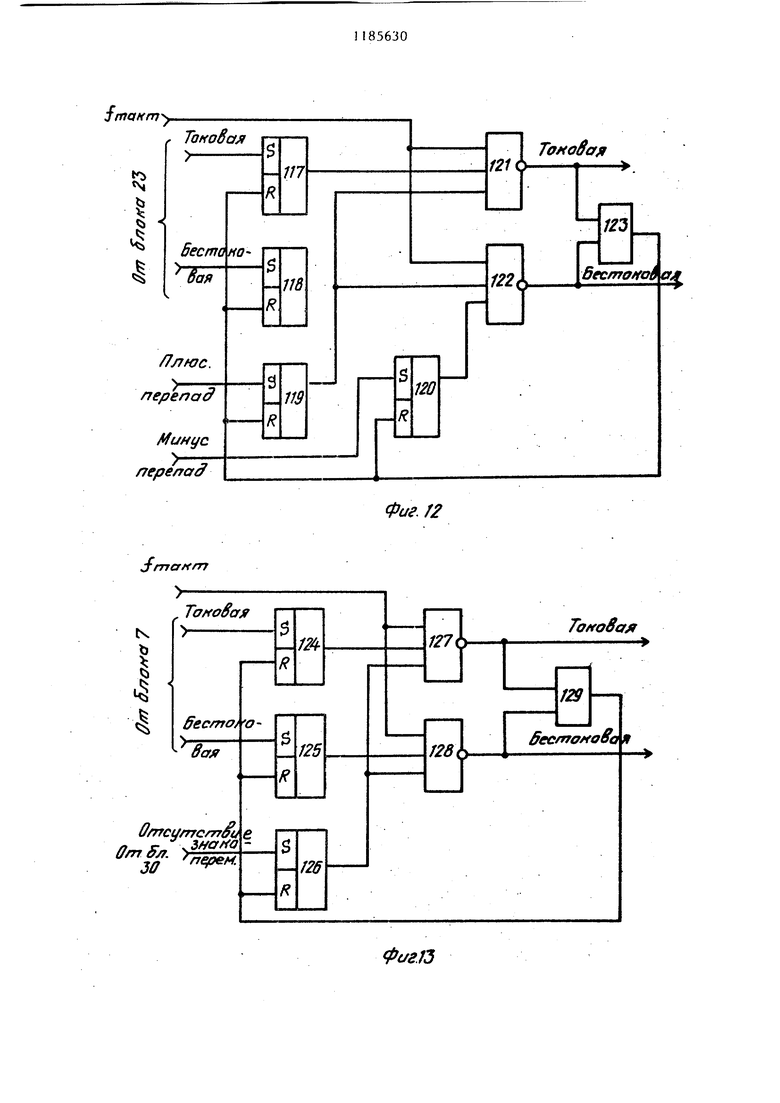

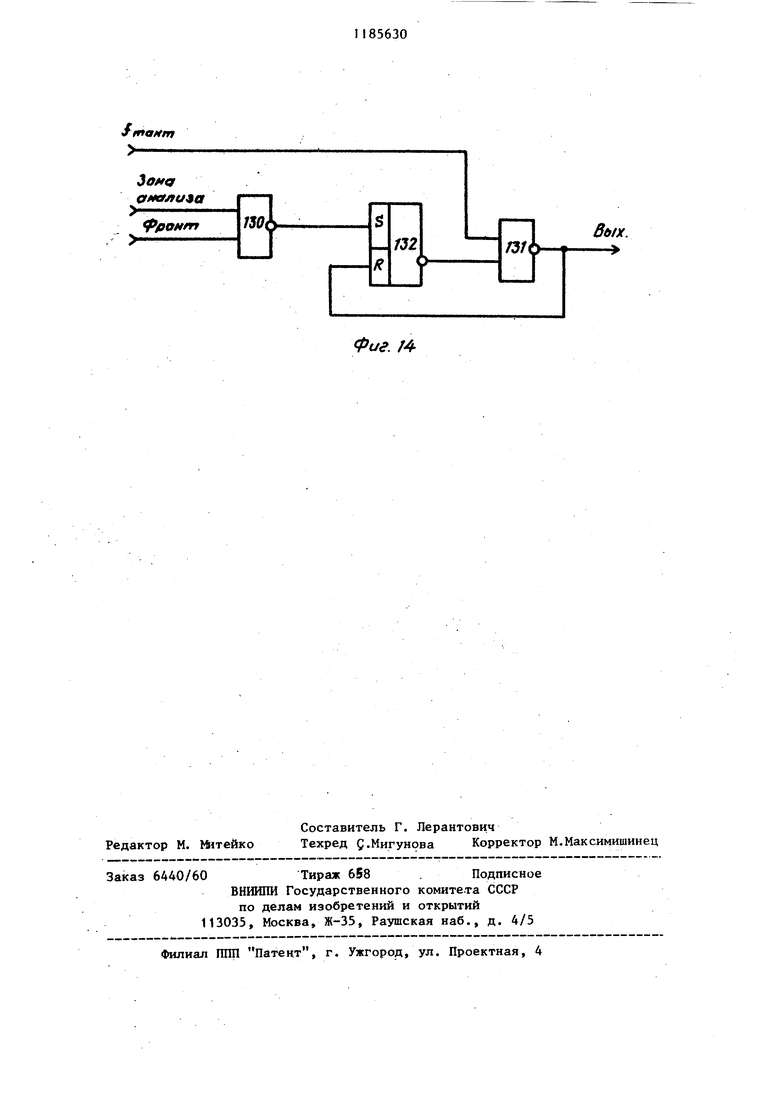

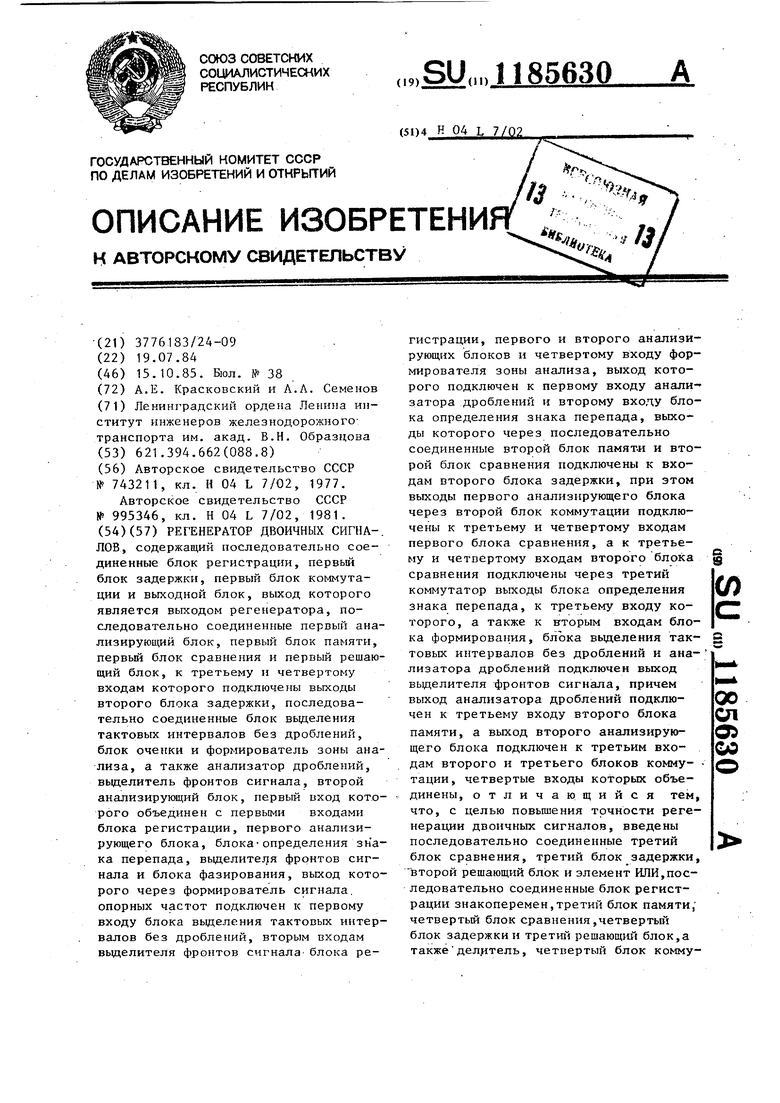

На фиг. 1 представлена структурная электрическая схема регенератора двоичных сигналов; на фиг. 2 - схема блока регистрации; на фиг. 3 -схема первого анализирующего блока; на фиг. 4 - схема первого решающего блока; на фиг. 5 - схема второго анализирующего блока; на фиг. 6 - схема . блока вьзделения тактовых интервалов без дроблений; на фиг. 7 - схема блока оценки; на фиг. 8 - схема формирователя зоны анализа; на фиг. 9 - схема вьзделителя фронтов сигнала; на фиг. 10 - схема анализатора дроблений; на фиг. 11 - схема блока определения знака перепада; на фиг. 12 схема решающего блока; на фиг. 13 схема третьего решающего .блока; на фиг. 14 - схема блока регистрации знакоперемен.

5 Регенератор двоичных сигналов содержит блок 1 регистрации, первый блок 2 задержки, первый блок 3 К(.)ммутации, первый анализирующий блок 4, первый блок 5 памяти, второй блок 6 коммутации, первый блок 7 сравнения, первый решающий блок 8, второй анализирующий блок 9, блок 10 выделения тактовых интервалов без дроблений, блок 11 оценки, формирователь 12 зо ны анализа, вьщелитель 13 фронтов сигнала, блок 14 определения знака перепада, третий блок 15 коммутации, анализатор 16 дроблений, второй блок 17 памяти, второй блок 18 сравнения, второй блок 19 задержки, выходной блок 20, блок 21 фазирования.

формирователь 22 сигнала опорных частот, пятый блок 23 сравнения, второй решающий блок 24, элемент ИЛИ 25 третий решающий блок 26, третий блок 27 сравнения, третий блок 28 задержки, четвертый блок 29 коммутации, четвертый блок 30 задержки, блок 31 регистрации знакоперемен, четвертый блок 32 сравнения, третий блок 33 памяти, делитель 34, при этом блок 1 регистрации состоит из трех двухвходовых элементов И-НЕ 35, 36 и 37, счетчика 38 и D-триггера 39 первый анализирующий блок 4 состоит из инвертора 40, трех двухвходовых элементов И 41, 42 и 43, четырех счетчиков 44 - 47, четырех RS - триггеров 48 - 51, двух трехвходовых элементов И 52 и 53, первый решающий блок 8 состоит из трех RS - триггеров 54, 55 и 56, двух трехвходовых элементов И-НЕ 57 и 58 и элемент ИЛИ 59, второй анализирующий блок 9 содержит инвертор 60, два трехвходовых элемента И 61 и 62, три счетчика 63, 64 и 65, два RS - триггера 66 и 67 и элемент ИЛИ 68, блок 10 выделения тактовых интервалов без дроблений содержит D-триггер 69, три счетчика 70., 71 и 72, два двухвходовых элемента И 73 и 74/элемент ИЛИ 75, блок 11 оценки состоит из трех двухвходовых элементов И-НЕ 76, 77 и 78, четырех счетчиков 79 -82, трех RS - триггеров 83, 84 и 85, двухвходового элемента И 86, трехвходового элемента И 87, четырехвходового элемента И 88, формирователь 12 зоны анализа содержит счетчик 89, три коммутатора 90, 91 и 92, три элемента И-НЕ 93, 94 и 95, три двухвходовых элемента ИЛИ 96 97 и 98, трехвходовой элемент И 99, три RS - триггера 100, 101 и 102, выделитель 13 фронтов сигнала состоит из инвертора 103, двух трехвходовых элементов И 104 и 105, элемента ИЛИ 106, D-триггера 107, анализатор 16 дроблений состоит из двух Двухвходовых элементов И-НЕ 108 и 109, D-триггера 110, блок 14 определения знака перепада состоит из трех двухвходовых элементов И-НЕ 111, 112 и 113, инвертора 114, RS - триггера 115, двухвходового элемента ИЛИ 116, второй решающий блок 24 состоит из четырех RS - триггеров 117- 120, двух трехвходовых элементов И 121 и 122 и элемент ИЛИ 123, третий решакндий

Ьлок 22 состоит из трех RS - триггеров 124, 125 и 126, двух трехвходовых элементов И 127 и 128 и элемент ИЛИ 129, блок 31 регистрации знакоперемен состоит из двух двухвходовых элементов И-НЕ 130 и 131, RS -триггера 132,

Регенератор двоичных сигналов работает следую цим образом.

С помощью блока 21 фазирования, формирователя 22 сигнала опорных частот и делителя 34 осуществлено фазирование тактовых импульсов по отношению к входному сигналу. Формирование зоны анализа производится следующим образом, В выделителе 13 фронтов сигнала создаются узкие импульсы в момент смены знака посылок. Эти импульсы поступают на вход блока 10 выделения тактовых интервалов без дроблений, в котором они задерживаются на один тактовый период с помощью счетчиков 1 или 2. На выходе блока 10 вьоделёния тактовых интервалов без дроблений формируются узкие импульсы (фронты), которые поступают на первый вход блока 11 оценки. На остальные входы этого блока поступают зоны с различной длительностью. Поэтому в зависимости от дисперсии флуктуации фронтов на одном из выходов блока 11 оценки появляется сигнал, который поступает на вход формирователя 12 зоны анали за и устанавливает один из RS - триггеров 100, 101 и 102 в единичное состояние, С помощью этих триггеров осуществляется выбор соответствующего импульса (зоны), которьш появляется на выходе трехвходового элемента И 99.

При поступлении сигнала на вход блока 1 регистрации, работа которого основана по принципу интегральной регистрации,.в нем производится определение знаков приходящих посылок. Сигнал о знаке посылок, задержанный на два тактовьсх периода в первом блоке 2 задержки, подается на вход блока 3 коммутации.

Одновременно с регистрацией знака всех поступающих на вход посыпок в блоке 1 регистрации, осуществляется определение знака малоискаженных посыпок в первом анализирующем блоке 4. При этом считается, что посылка малоискажена, если в тактовом периоде в течение 0,7irQ имеет место однополярная часть яосылки. В этом случае отработает только один счетчик 44 или

4/, И запрета на формирования сигналов о знаке посылки не будет. Так как рассматривается случай, когда первоначально приходит малоискаженная посылка, то с помощью счетчика 45 или 46 определяется знак посылки, и сигнал о знаке посыпки с выхода трехвходовых элементов И 52 или 53 поступает на вход первого блока 5 памяти и хранится в памяти блока в течение двух тактовых интервалов и затем подается на входы первого 7 и пятого 23 блоков сравнения.

Допустим, что в следующем тактовом периоде поступает сильнодробленная посьшка. Тогда на выходе второго анализирующего блока 9 формируется сигнал, который показывает, что в дан-, пом тактовом интервале присутствовали дробления посыпки с суммарной длительностью более 30% от всей длительности посылки. При этом запомнились счетчики 63 и 64. Сигнал с выхода второго анализирующего блока 9 переключает второй, третий и четвертьй блоки 6,15 и 29 коммутации в положение, разрешающее прохождение сигналов через эти блоки.

С помощью блока 14 определения знака перепада производится определение знака перепада в зоне анализа, сформированной с помощью блоков 10 и 11 и формирователя 12 зоны анализа, причем временное положение -последней зоны соответствует началу сильнодробленной посылки. Сигнал о знаке перепада с выхода блока 14 определения знака перепада поступает на вход второго блока 17 памяти, в котором хранится в течение одного тактового периода.

Если в зоне анализа, следующей за сильнодробленной посылкой, отсутствует знакоперепад, то на выходе блокаЗ регистрации знакоперемен фop mpyeтcя сигнал, который через четвертьй блок 29 коммутации поступает на третий вход третьего блока 27 сравнения. К моменту поступления этого сигнала на втором входе блока 27 присутствует сигнал о знаке перепада переднего фронта сильнодробленной посылки. В результате логической обработки входных сигналов на выходе третьего блока 27 сравнения формируется сигнал о знаке сйльнодробленной посылки. Этот сигнал задерживается в третьем блоке 23 задержки на один такт, в течение которого регистрируется Знак малоискаженнрй посылки в первом анализирующем блоке 4. Сигнал о результате регистрации с выхода первого анализирующего блока 4 через второй блок 6 коммутации поступает на третий и четвертый входы первого блока 7 сравнения и третий и четвертьй входы пятого блока 23 сравнения. Так как рассматривается случай поступления разнополярньпс малоискаженных посылок, сигнал на выходе первого блока 7 сравнения отсутствует, а на выходе пятого блока 23 сравнения появляется сигнал .о знаке малоискаженной посылки следующей за сильнодробленной, который поступает на третий и четвертый входы второго решающего блока 24. Поэтому в.конце тактового интервала, следующего за сильнодробленной посьткой, на входах второго решающего блока 24 присутствуют сигналы о знаке перепада первго фронта сильнодробленной посылки и о знаке малоискаженной посылки, которая следует за сильнодробленной. Если знак перепада соответствует знаку малоискаженной посылки, то во втором решающем блоке 24 принимается решение о знаке сильнодробленной посылки и вырабатывается сигнал, который через элемент ИЛИ 25 поступает на соответствующий вход первого блока 3 коммутации, четвертые входы второго и третьего блоков 6 и 15 коммутации и первый .вход четвертого блока 29 коммутации. Сигнал с выхода элемента ИЛИ 25 переключает блоки 6 и 15 ц 29 коммутации в положение, запрещающее прохождение сигнала через эти блоки. Кроме того, сигнал с выхода элемента ИЛИ 25, выполненного на основе тактируемого триггера, поступает через первый блок 3 коммутации в выходной блок 20. При этом в первом блоке 3 когдаутации производится запрет на прохождение сигнала от первого блока 2 задержки.

Во втором случае сильнодробленная посыпканаходится между слабоискаженными или вообще неискаженными однополярными посылками, однако в зонах анализа.перед и после сильнодробленной песьшки отсутствуют перепады от информационных фронтов. В такой ситуации можно предположить, что поступают три подряд однополярные

посылки и знак сильноискажеиной посылки соответствует знаку неискаженных .

В этом случае устройство работает следующим образом.

При поступлении малоискаженной посылки в первом анализирующем блоке 4 определяется ее знак, который запоминается в первом блоке 5 памяти в течение двух тактовых периодов. При отсутствии знакоперемены в конце тактового периода в блоке 31 регистрации знакоперемен формируется сигнал, который поступает в третий блок 33 памяти. В следующем тактовом периоде поступает сильнодробленная посылка, поэтому во втором анализирующем блоке 9 формируется сигнал, который переключает первый, второй и четвертый блоки 3, 6 и 29 коммутации в положение, разрешающее прохождение сигналов через эти блоки. По окончании поступления сильнодробленной посылки при условии, что в зоне анализа отсутствует знакоперемеиа, в блоке 31 регистрации знакоперемен создается сигнал, который через четвертый блок 29 коммутации посылается в четвертый блок 32 сравнения. Таким образом, в конце второго тактового периода на входах четвертого блока 32 сравнения появляются сигналы об отсутствии знакоперемен.

В результате логической обработки сигналов в четвертом блоке 32 сравнения формируется импульс, который поступает на вход четвертого блока 30. задержки. В четвертом блоке 30 задержки импульс задерживается на один тактовый период. Если в этом тактовом периоде поступает малоискаженная посылка, сигнал о ее знаке подается с выхода первого анализирующего блока 4 через второй блок 6 коммутации на

третий и четвертый входы первого блока 7 сравнения.Первый блок 7 сравнения выносит решение о том, что знаки Малоискаженных посыпок совпадают. Поэтому в первом блоке 7 сравнения вырабатьшается сигнал, который поступает на первый и второй входы третьего решающего блока 26.

Таким образом, к моменту оконча- . ния малоискаженной посылки в первом блоке 7 сравнения оказывается сформированным сигнал о знаках малоискаженных посылок. Кроме того, на выходе четвертого блока 30 за.держки появляется сигнал об отсутствии знакоперемен в зоне анализа. Сигналы о знаках малоискаженных посылок и об отсутствии знакоперемен в зонах анализа поступают на соответствующие входы третьего решающего блока 26. На основании логической обработки этих сигналов в третьем решающем блоке 26 определяется знак сильнодроблен.ной посылки, причем этот знак соответствует знаку малоискаженных посьшок. Сигнал с выхода третьего решающего блока 26 через элемент ИЛИ 25 подается на входы второго и третьего блоков 6 и 15 коммутации и первый вход четвертого блока 29 коммутации, которые переключаются в положение, запрещающее прохождение сигналов через эти блоки. Кроме того, сигнал с выхода элемента ИЛИ 25 через первый блок 3 коммутаций поступает на вход выходного блока 20, в котором формируется регенерированная посылка. При этом в первом блоке 3 коммутации производится Зсттрет на прохождение сигнала с выхода первого блока 2 задержки.

Наличие двух фронтов в зоне анализа, что соответствует дроблению посылки, фиксируется в анализатор 16 дроблений.

ix. cutH.

35

n

oeerhoaoвал

fmanm

TijHmoStiu uftn. i

, ФаеЛ

6K.cuf. j

VffffMy/r(

енис

B6

65

его

S7

poffmtfi

Фие. 6

Фромт«« 3mai

Son

89

J WCKffVf f

Jaw //Orfet ЛГ,

Swcrl

32

I Ijg K

ffm S/r. ff

EH Фие.З

/я|115

R

т

//4Лфиг. JO

// юсовой лере/га

инусоВми

/7epe/7Cfff

т

Фиг //

fdiatfirj

такт

Вб/х. -

фиг. /4

| Регенератор двоичных сигналов | 1977 |

|

SU743211A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Регенератор двоичных сигналов | 1981 |

|

SU995346A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-10-15—Публикация

1984-07-19—Подача