2.Устройство по П.1, о.т л и чающееся тем, что к положительной клемме источника питания подключен дополнительный резистор, второй вьгвод которого подключен к точке соединения резистора и диода цепи.

3.Устройство по пп. 1 и 2, о тличающееся тем, что парал1187254

лельно резистору цепи подключен второй диод, при этом его катод подключен к конденсатору.

4. Устройство по П.1, отличающееся тем, что к выходу выходного триггера подключен вход элемента И, второй вход которого подключен к входу входного инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1980 |

|

SU917323A1 |

| Формирователь импульсов | 1982 |

|

SU1095361A2 |

| Устройство защиты от дребезга контакта | 1988 |

|

SU1707748A1 |

| Цифровой фильтр | 1989 |

|

SU1672558A1 |

| Устройство для дозирования | 1985 |

|

SU1255869A2 |

| Транзисторная система зажигания | 1990 |

|

SU1756601A1 |

| Триггерное устройство | 1981 |

|

SU970649A1 |

| Устройство задержки | 1979 |

|

SU813738A1 |

| Многоканальное устройство согласования коммутационной цепи переменного тока с интегральной микросхемой | 1984 |

|

SU1307552A1 |

| Электропривод переменного тока | 1988 |

|

SU1661947A1 |

1. УСТРОЙСТВО ЗАДЕРЖКИ, содержащее входной инвертор, выход- f о ной триггер, цепь из последователь но соединенных конденсатора, резис тора и диода, подключенную параллельно выходу входного инвертора,, при этом один нз выводов конденсат ра подключен к общей шине, а другой - к входу выходного триггера, отличающееся тем, что, целью расширения функциональных во можностей и повышения помехоустойчивости, в него введен элемент И-Н выход которого подключен к другому входу выходного триггера, а входы подключены соответственно к выходу i входного инвертора и второьгу вывод конденсатора. (Л

Изобретение относится к. электронике и может быть использовано в системах автоматического управления аппаратурой, использующей бесконтактные логические элементы и предназначенной для управления технологическими процессами.

Целью изобретения является расширение функциональных возможностей за счет формирования сигналов на дополнительных выходах устройства и повышение его помехоустойчивости.

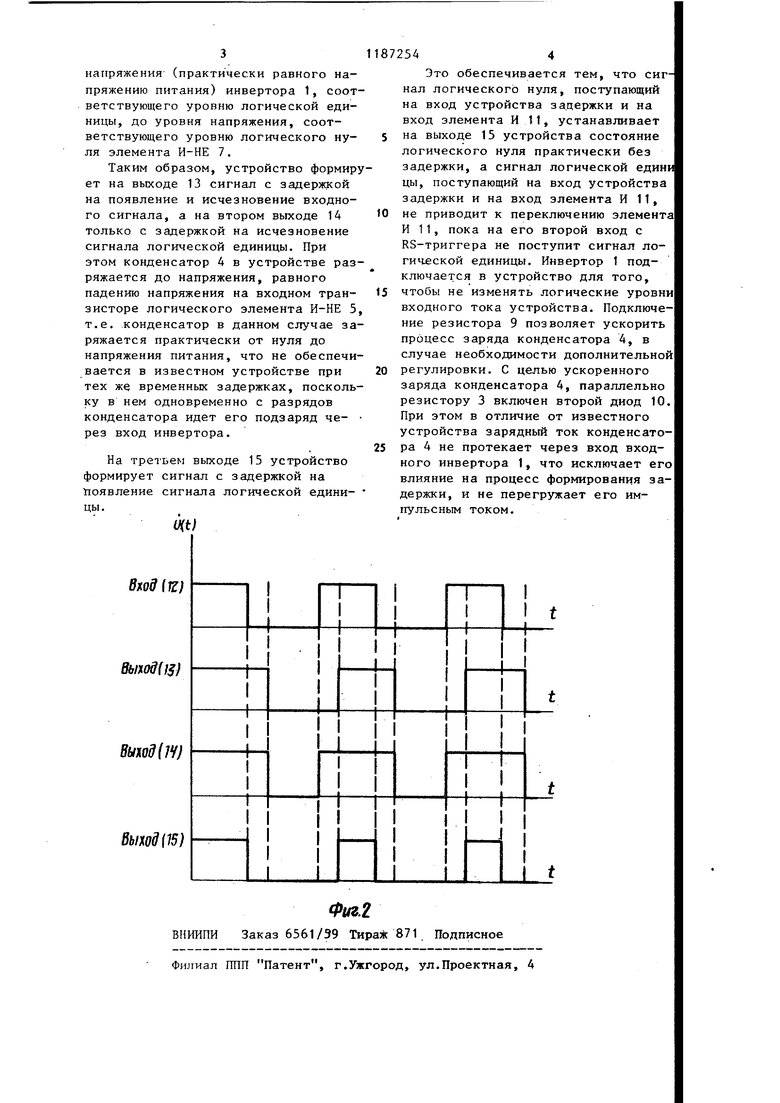

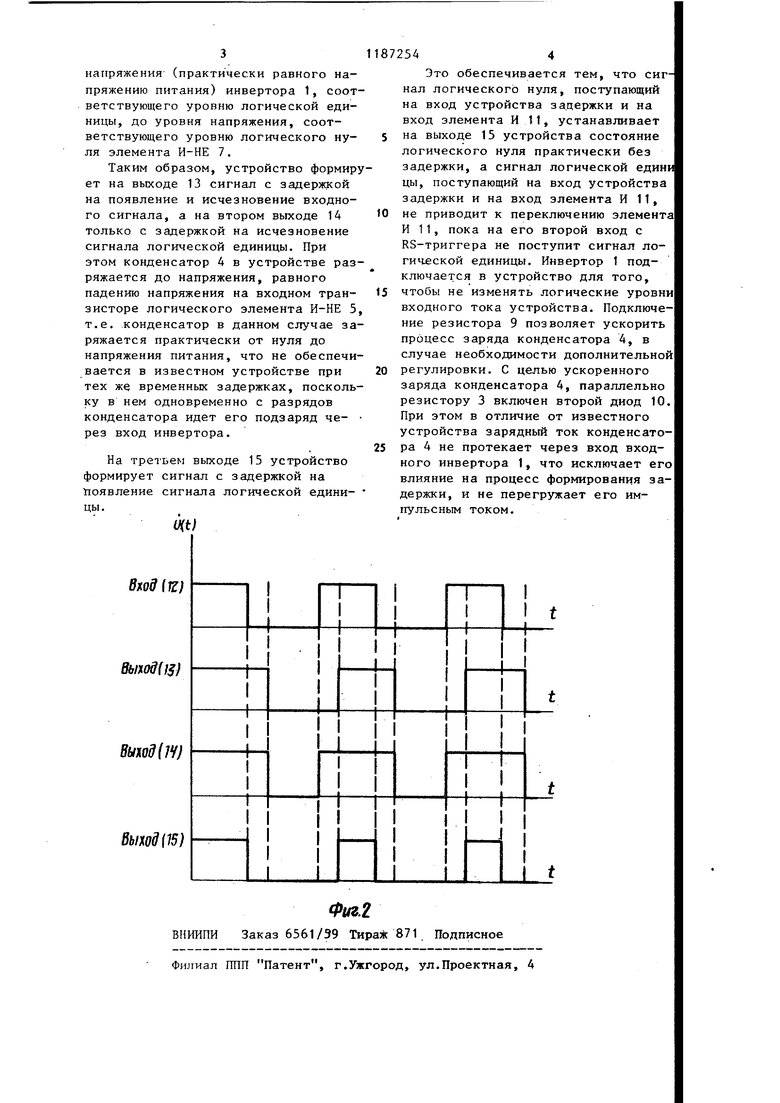

На фиг. 1 представлена принципиальная электрическая схема устройства задержкиi на фиг. 2 - временные диаграммы изменения напряжений (U) на входе и выходах в зависимости от времени (t).

Устройство задержки содержит входной инвертор 1, выходом подключенный к катоду диода 2, анод которого через резистор 3. подключен к конденсатору 4, к входу логического элемента И-НЕ 5 и входу RS-триггера 6, собранного на двух элементах И-НЕ 7 и 8, дополнптельньй резистор 9, подключенньй одним выводом к положительной клемме источника питания, а втормм вьшодом - к точке соединения катода диода 2 с резистором 3, второй диод 10, подключенный параллельно резистору 3, при этом второй диод 10 анодом подключен к аноду диода 2, а катодом - к конденсатору 4, элемент И 11, подключенный одним входом к входу 12 входного инвертора 1, являющемуся входом устройства, а другим - к выходу RS-триггера 6, который является первым выходом 13 устройства .

Второй вывод конденсатора 4 подключен к общей шине питания. Второй вход элемента И-НЕ 5 подключен к выходу входного инвертора 1. Выход

элемента И-НЕ 5 является вторым выходом 14 устройства задержки и подключен к второму входу RS-триггера 6, выход элемента И 11 является третьим выходом 15 устройства задержки.

Устройство работает следующим образом.

Если при включении задержки сигнал на выходе инвертора 1 соответствует нулю, то тогда через входы

элементов И-НЕ 5 и 7 и через диод 2 и резистор 3 конденсатор 4 заряжается до величины выходного напряжения инвертора 1, соответствующего логической единице. Время заряда конденсатора 4 определяется входными сопротивлениями элементов И-НЕ 5 и 7, током утечки диода 2 и величиной емкости конденсатора 4. По истечении времени заряда конденсатора 4 на

выходе RS-триггера и элемента И-НЕ 5 формируются сигналы логического нуля. Цри появлении сигнала логической единицы на входе инвертора 1, на его выходе формируется сигнал логического нуля. Конденсатор 4 разряжается через резистор 3, диод 2 и выход инвертора 1, а также через входы элементов И-НЕ 5 и 7. С появлением сигнала логического нуля на выходе инвертора 1 на выходе элемента И-НЕ 5 практически без задержки формируется сигнал логической единицы. На выходе RS-триггера 6 сигнал логической единицы формируется с задержкой, определяемой временем разряда

конденсатора 4 с уровня выходного 3 напряжения (практически равного напряжению питания) инвертора 1, соот ветствующего уровню логической единицы, до уровня напряжения, соответствующего уровню логического нуля элемента И-НЕ 7. Таким образом, устройство формир ет на выходе 13 сигнал с задержкой на появление и исчезновение входного сигнала, а на втором выходе 14 только с задержкой на исчезновение сигнала логической единицы. При этом конденсатор 4 в устройстве раз ряжается до напряжения, равного падению напряжения на входном транзисторе логического элемента И-НЕ 5 т.е. конденсатор в данном случае за ряжается практически от нуля до напряжения питания, что не обеспечи вается в известном устройстве при тех же временных задержках, посколь ку в нем одновременно с разрядов конденсатора идет его подзаряд через вход инвертора. На третьем выходе 15 устройство формирует сигнал с задержкой на появление сигнала логической единицы.

Вход ilZ)

Bbnodds)

Втд{14) 544 Это обеспечивается тем, что сигнал логического нуля, поступающий на вход устройства задержки и на вход элемента И 11, устанавливает на выходе 15 устройства состояние логического нуля практически без задержки, а сигнал логической едини цы, поступающий на вход устройства задержки и на вход злемента И 11, не приводит к переключению элемента И 11, пока на его второй вход с RS-триггера не поступит сигнал логической единицы. Инвертор 1 подключается в устройство для того, чтобы не изменять логические уровни входного тока устройства. Подключение резистора 9 позволяет ускорить процесс заряда конденсатора 4, в случае необходимости дополнительной регулировки. С целью ускоренного заряда конденсатора 4, параллельно резистору 3 включен второй диод 10. При этом в отличие от известного устройства зарядный ток конденсатора 4 не протекает через вход входного инвертора 1, что исключает его влияние на процесс формирования задержки, и не перегружает его импульсным током.

| Устройство задержки | 1979 |

|

SU813738A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-10-23—Публикация

1984-01-02—Подача