Ur

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления транзисторами двухтактного преобразователя | 1986 |

|

SU1334310A1 |

| ЗАРЯДНОЕ УСТРОЙСТВО ЕМКОСТНОГО НАКОПИТЕЛЯ ЭНЕРГИИ | 2015 |

|

RU2601437C1 |

| Имитатор импульсных помех | 1986 |

|

SU1396252A1 |

| Устройство для передачи информации с вращающегося объекта | 1986 |

|

SU1334173A1 |

| Устройство тактовой синхронизации сигналов с расщепленной фазой | 1985 |

|

SU1297243A1 |

| УСТРОЙСТВО ОХРАННОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2031445C1 |

| ЦИФРОВОЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА С ДВОЙНОЙ ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2037263C1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

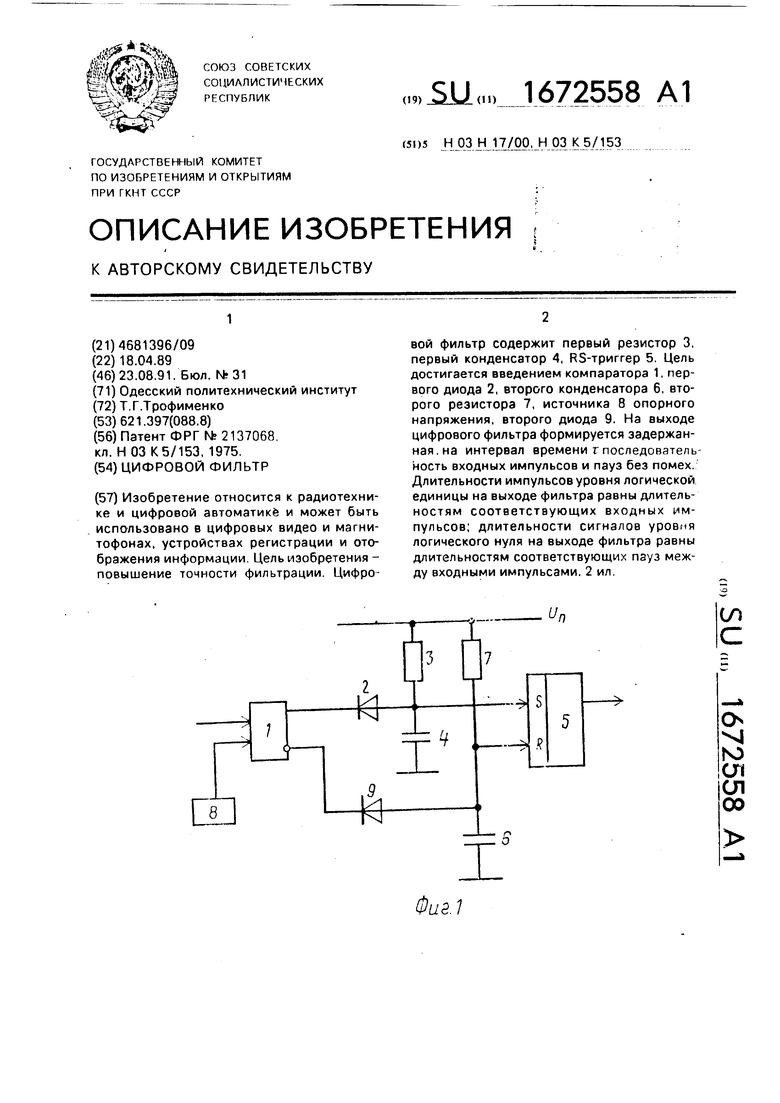

Изобретение относится к радиотехнике и цифровой автоматике и может быть использовано в цифровых видео-магнитофонах, устройствах регистрации и отображения информации. Цель изобретения - повышение точности фильтрации. Цифровой фильтр содержит первый резистор 3, первый конденсатор 4, RS - триггер 5. Цель достигается введением компаратора 1, первого диода 2, второго конденсатора 6, второго резистора 7, источника 8 опорного напряжения, второго диода 9. На выходе цифрового фильтра формируется задержанная на интервал времени Τ последовательность входных импульсов и пауз без помех. Длительности импульсов уровня логической единицы на выходе фильтра равны длительностям соответствующих входных импульсов

длительности сигналов уровня логического нуля на выходе фильтра равны длительностям соответствующих пауз между входными импульсами. 2 ил.

О

го ел

|СЛ 00

Фиг

Изобретение относится к радиотехнике и цифровой автоматике и может быть использовано в цифровых видео и магнитофонах, устройствах ре истрации и отображения информации.

Цель изобретения - повышение точности фильтрации.

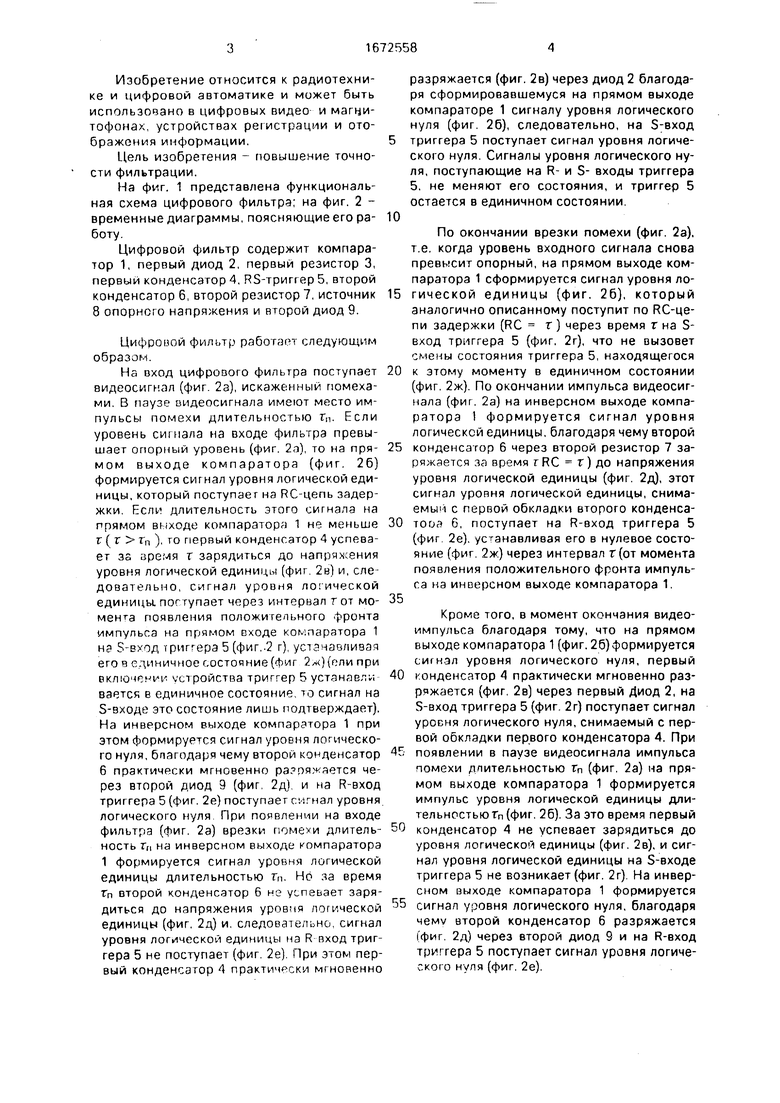

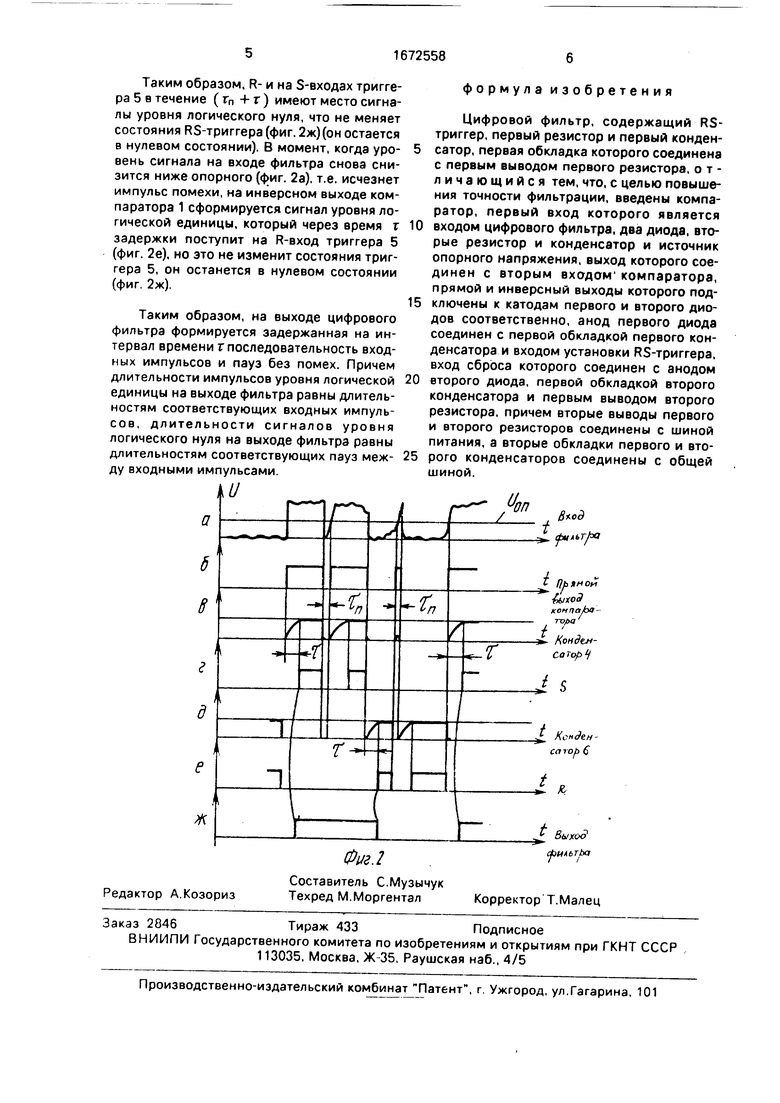

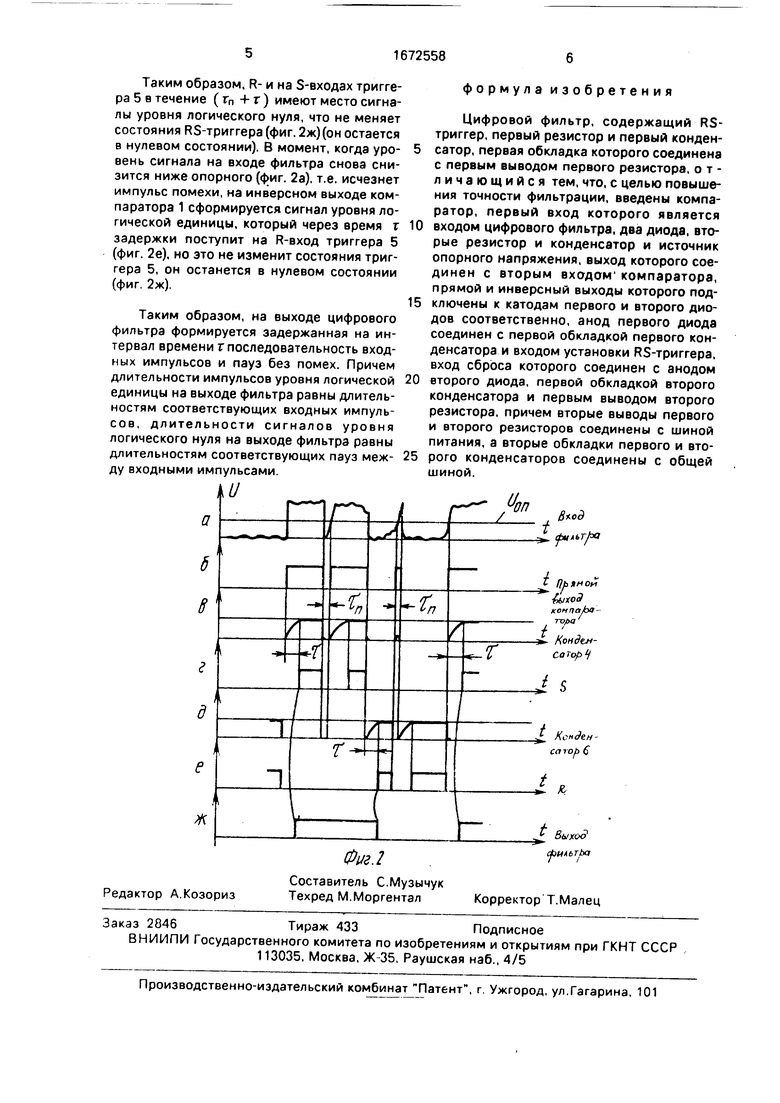

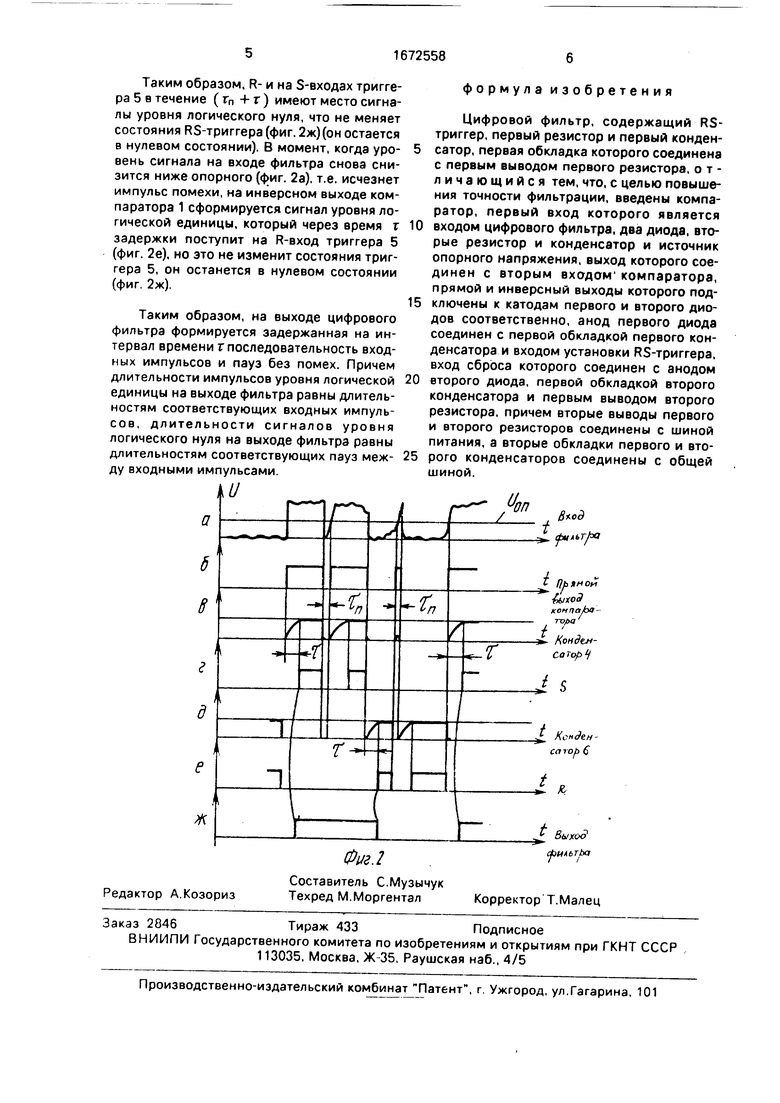

На фиг. 1 представлена функциональная схема цифрового фильтра; на фиг. 2 - временные диаграммы, поясняющие его работу.

Цифровой фильтр содержит компаратор 1, первый диод 2, первый резистор 3, первый конденсатор 4, RS-триггер 5, второй конденсатор 6, второй резистор 7, источник 8 опорного напряжения и второй диод 9.

Цифровой фильтр работает следующим образом.

На вход цифрового фильтра поступает видеосигнал (фиг. 2а), искаженный помехами. В паузе видеосигнала имеют место импульсы помехи длительностью тп. Если уровень сигнала на входе фильтра превышает опорный уровень (фиг. ), то на прямом выходе компаратора (фиг. 26) формируется сигнал уровня логической единицы, который поступает на RC-цепь задержки. Если длительность этого сигнала на прямом впходе компаратор) 1 не меньше г ( г гп ), го первый конденсатор 4 успевает за зремя т зарядиться до напряхсения уровня логической единицы (фиг 2в) и, следовательно, сигнал уровня ло:ической единицы поступает через интервал г от момента появления положительного Фронта импульса на прямом входе компаратора 1 на S-вход триггера 5 (фиг.-2 г), устанавливая его ч единичное состояние (Фиг 2ж) {ели при включении (лройства триггер 5 устянавл ; вается в единичное состояние, то сигнал на S-входе это состояние лишь подтверждает). На инверсном выходе компаратора 1 при этом формируется сигнал уровня логического нуля, благодаря чему второй конденсатор 6 практически мгновенно раяпяжается через второй диод Э (фиг, 2д) и на R-вход триггера 5 (фиг. 2е) поступает сигнал уровня логического нуля При появлении на входе фильтра (фиг. 2а) врезки помехи длительность гп на инверсном выходе компаратора 1 формируется сигнал уровня логической единицы длительностью гп. Но за время тп второй конденсатор 6 нэ успевает зарядиться до напряжения уровмя логической единицы (фиг, 2д) и, следовательно, сигнал уровня логической единицы на R вход триггера 5 не поступает (фиг. 2е) При этом первый конденсатор 4 практически мгновенно

разряжается (фиг. 2в) через диод 2 благодаря сформировавшемуся на прямом выходе компараторе 1 сигналу уровня логического нуля (фиг. 26), следовательно, на S-вход

триггера 5 поступает сигнал уровня логического нуля. Сигналы уровня логического нуля, поступающие на R- и S- входы триггера 5, не меняют его состояния, и триггер 5 остается в единичном состоянии.

0

По окончании врезки помехи (фиг. 2а), т.е. когда уровень входного сигнала снова превысит опорный, на прямом выходе компаратора 1 сформируется сигнал уровня ло5 гической единицы (фиг. 26), который аналогично описанному поступит по RC-це- пи задержки (RC т } через время т на S- вход триггера 5 (фиг, 2г), что не вызовет смены состояния триггера 5, находящегося

0 к этому моменту в единичном состоянии (фиг. 2ж). По окончании импульса видеосигнала (фиг. 2а) на инверсном выходе компаратора формируется сигнал уровня логической единицы, благодаря чему второй

5 конденсатор 6 через второй резистор 7 заряжается за время rRC т) до напряжения уровня логической единицы (фиг. 2д|, этот сигнал уровня логической единицы, снимаемым с первой обкладки второго конденса0 TODS 6, поступает на R-вход триггера 5 (фиг 2е). устанавливая его в нулевое состояние (фиг. 2ж) через интервал г (от момента появления положительного фронта импульса на инверсном выходе компаратора 1.

5

Кроме того, в момент окончания видеоимпульса благодаря тому, что на прямом выходе компаратора 1 (фиг. 26) формируется сигнал уровня логического нуля, первый

0 конденсатор 4 практически мгновенно разряжается (фиг. 2в) через первый Диод 2, на S-вход триггера 5 (фиг. 2г) поступает сигнал уровня логического нуля, снимаемый с первой обкладки первого конденсатора 4. При

5 появлении в паузе видеосигнала импульса помехи длительностью гп (фиг. 2а) на прямом выходе компаратора 1 формируется импульс уровня логической единицы длительностью тп (фиг. 26). За это время первый

0 конденсатор 4 не успевает зарядиться до уровня логической единицы (фиг. 2в), и сигнал уровня логической единицы на S-входе триггера 5 не возникает (фиг. 2г) На инверсном выходе компаратора 1 формируется

5 сигнал уровня логического нуля, благодаря чему второй конденсатор 6 разряжается | фиг. 2д) через второй диод 9 и на R-вход триггера 5 поступает сигнал уровня логического нуля (фиг. 2е).

Таким образом, R- и на S-входах триггера 5 в течение ( гп 4- г ) имеют место сигналы уровня логического нуля, что не меняет состояния RS-триггера (фиг. 2ж)(он остается в нулевом состоянии). В момент, когда уровень сигнала на входе фильтра снова снизится ниже опорного (фиг. 2а), т.е. исчезнет импульс помехи, на инверсном выходе компаратора 1 сформируется сигнал уровня логической единицы, который через время т задержки поступит на R-вход триггера 5 (фиг. 2е), но это не изменит состояния триггера 5, он останется в нулевом состоянии (фиг. 2ж).

Таким образом, на выходе цифрового фильтра формируется задержанная на интервал времени г последовательность входных импульсов и пауз без помех. Причем длительности импульсов уровня логической единицы на выходе фильтра равны длительностям соответствующих входных импульсов, длительности сигналов уровня логического нуля на выходе фильтра равны длительностям соответствующих пауз между входными импульсами.

формула изобретения

Цифровой фильтр, содержащий RS- триггер, первый резистор и первый конденсатор, первая обкладка которого соединена с первым выводом первого резистора, отличающийся тем, что, с целью повышения точности фильтрации, введены компаратор, первый вход которого является

входом цифрового фильтра, два диода, вторые резистор и конденсатор и источник опорного напряжения, выход которого соединен с вторым входом компаратора, прямой и инверсный выходы которого подключены к катодам первого и второго диодов соответственно, анод первого диода соединен с первой обкладкой первого конденсатора и входом установки RS-триггера, вход сброса которого соединен с анодом

второго диода, первой обкладкой второго конденсатора и первым выводом второго резистора, причем вторые выводы первого и второго резисторов соединены с шиной питания, а вторые обкладки первого и второго конденсаторов соединены с общей шиной.

| СПОСОБ ПЛАВЛЕНИЯ МЕТАЛЛИЧЕСКИХ ШИХТОВЫХ МАТЕРИАЛОВ В ШАХТНОЙ ПЕЧИ | 1997 |

|

RU2137068C1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-08-23—Публикация

1989-04-18—Подача