(54) УСТРОЙСТВО ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1980 |

|

SU917323A1 |

| Стабилизированный преобразователь постоянного напряжения с защитой | 1986 |

|

SU1317597A2 |

| Тиристорная система зажигания | 1989 |

|

SU1710816A1 |

| Устройство задержки | 1984 |

|

SU1187254A1 |

| Цифровой фильтр | 1989 |

|

SU1672558A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФУНКЦИОНИРОВАНИЯ БЛОКА ОБРАБОТКИ ДАННЫХ | 1998 |

|

RU2143727C1 |

| Многофазный генератор импульсов | 1980 |

|

SU949779A1 |

| Устройство для контроля наличия п-информационных сигналов | 1985 |

|

SU1398073A1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

| Устройство задержки | 1978 |

|

SU767959A1 |

1

Изобретение относится к автоматике и может быть использовано в системах автоматического управления технологическими процессами.

Известны устройства задержки, содержащие элементы задержки в виде RC-цепей и формирователи импульсов с определенным порогом срабатывания. Время задержки таких устройств нестабильно, оно зависит от момента появления входного импульса.

Началу отработки времени задержки предшествует полный заряд конденсатора, и следовательно, перерывы между входными импульсами не могут быть короче времени, необходимого для полного заряда (разряда) 1.

Недостатком этого устройства являетсято, что если время задержки значительно уменьшается т. е. перестает быть стабильным, то оно становится зависимым от уровня напряжения, до которого успел зарядиться конденсатор. То же происходит и при кратковременном исчезновении входного сигнала (появление помехи).

Известен также формирователь прямоугольных импульсов, содержаш,ий элемент

и-НЕ, вход которого подключен к шине запускающего сигнала, а выход подключен к первому входу триггера и входу инвертора, выход которого подключен к второму входу триггера. Такой формирователь прямоугольных импульсов, при введении в него элемента задержки, включенной между выходом элемента И-НЕ и первым входом триггера, часто используется как устройство задержки на появление выходного сигнала 2.

Однако если перерывы между входными импульсами короче времени необходимого для полного заряда конденсатора, то время задержки значительно сокращается. То же происходит и при кратковременном исчезновении запускающего импульса (появлении помехи), когда отработка времени задержки еще не закончилось, и появление его вновь, когда конденсатор еще полностью не зарядился.

Цель изобретения - стабилизация времени задержки.

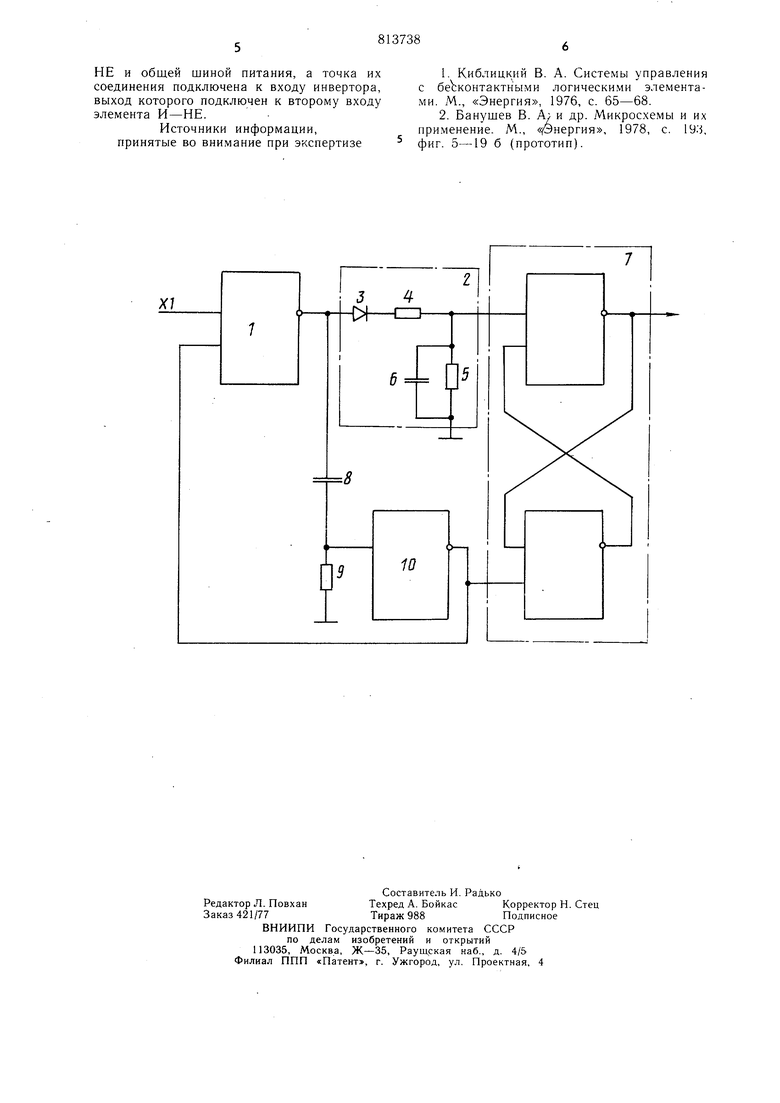

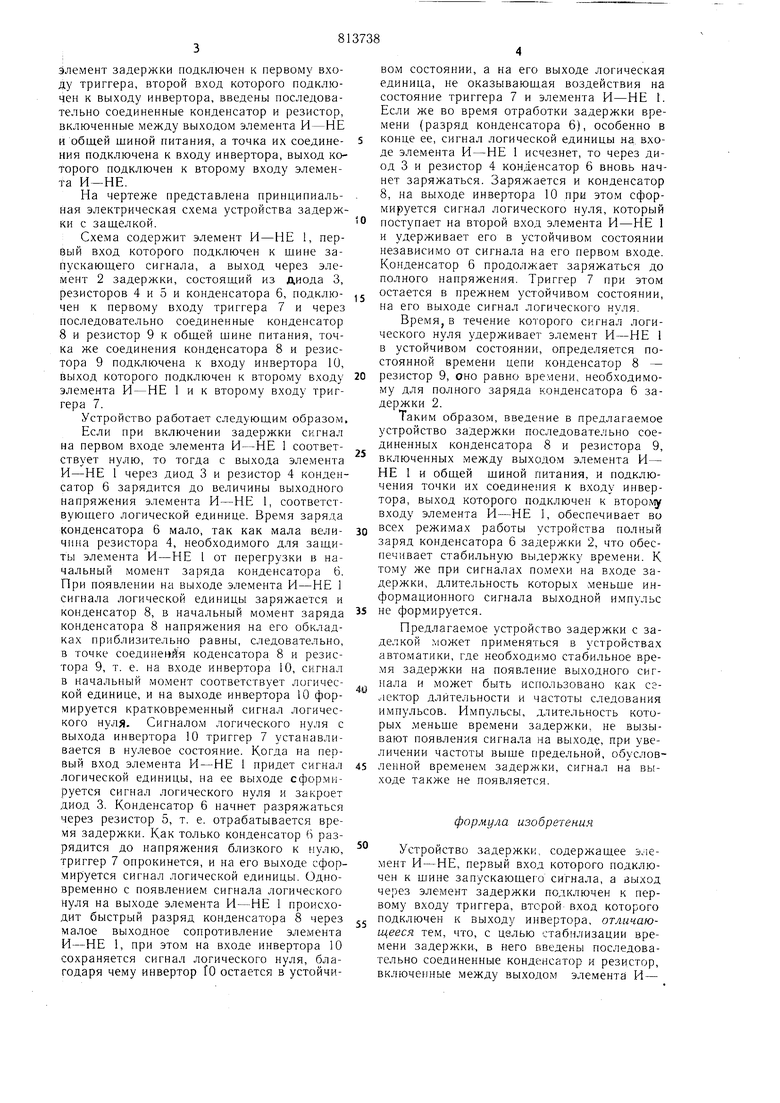

Поставленная цель достигается тем, что в устройство задержки, содержащее элемент И-НЕ, первый вход которого подключен к шине запускающего сигнала, а выход через 81 элемент задержки подключен к первому входу триггера, второй вход которого подключен к выходу инвертора, введены последовательно соединенные конденсатор и резистор, включенные между выходом элемента И-НЕ и общей шиной питания, а точка их соединения подключена к входу инвертора, выход которого подключен к второму входу элемента И-НЕ. На чертеже представлена принципиальная электрическая схема устройства задержки с защелкой. Схема содержит элемент И-НЕ 1, первый вход которого подключен к шине запускающего сигнала, а выход через элемент 2 задержки, состоящий из диода 3, резисторов 4 и 5 и конденсатора 6, подключен к первому входу триггера 7 и через последовательно соединенные конденсатор 8 и резистор 9 к общей шине питания, точка же соединения конденсатора 8 и резистора 9 подключена к входу инвертора 10, выход которого подключен к второму входу элемента И-НЕ 1 и к второму входу триггера 7. Устройство работает следующим образо.м. Если при включении задержки сигнал на первом входе элемента И-НЕ 1 соответствует нулю, то тогда с выхода элемента И-НЕ 1 через диод 3 и резистор 4 конденсатор 6 зарядится до величины выходного напряжения элемента И-НЕ 1, соответствующего логической единице. Время заря; ха конденсатора 6 мало, так как мала величина резистора 4, необходимого для защиты элемента И - НЕ 1 от перегрузки в начальный момент заряда конденсатора 6. При появлении на выходе элемента И-НЕ 1 сигнала логической единицы заряжается и конденсатор 8, в начальный момент заряда конденсатора 8 напряжения на его обкладках приблизительно равны, следовательно, в точке соединения коденсатора 8 и резистора 9, т. е. на входе инвертора 10, сигнал в начальный момент соответствует логической единице, и на выходе инвертора 10 формируется кратковременный сигнал логического нуля. Сигналом логического нуля с выхода инвертора 10 триггер 7 устанавливается в нулевое состояние. Когда на первый вход элемента И-НЕ 1 придет сигнал логической единицы, на ее выходе сформируется сигнал логического нуля и закроет диод 3. Конденсатор 6 начнет разряжаться через резистор 5, т. е. отрабатывается время задержки. Как только конденсатор 6 разрядится до напряжения близкого к нулю, триггер 7 опрокинется, и на его выходе сформируется сигнал логической единицы. Одновременно с появлением сигнала логического нуля на выходе элемента И-НЕ 1 происходит быстрый разряд конденсатора 8 через малое выходное сопротивление элемента И-НЕ 1, при этом на входе инвертора 10 сохраняется сигнал логического нуля, благодаря чему инвертор ГО остается в устойчивом состоянии, а на его выходе логическая единица, не оказывающая воздействия на состояние триггера 7 и элемента И-НЕ 1. Если же во время отработки задержки времени (разряд конденсатора 6), особенно в конце ее, сигнал логической единицы на. входе эле.мента И-НЕ 1 исчезнет, то через диод 3 и резистор 4 конденсатор 6 вновь начнет заряжаться. Заряжается и конденсатор 8, на выходе инвертора 10 при этом сформируется сигнал логического нуля, который поступает на второй вход элемента И-НЕ 1 и удерживает его в устойчивом состоянии независимо от сигнала на его первом входе. Конденсатор 6 продолжает заряжаться до полного напряжения. Триггер 7 при этом остается в прежнем устойчивом состоянии, на его выходе сигнал логического нуля. Время,в течение которого сигнал логического нуля удерживает элемент И-НЕ 1 в устойчивом состоянии, определяется постоянной времени цепи конденсатор 8 - резистор 9, оно равно времени, необходимо.му для полного заряда конденсатора 6 задержки 2. Таким образом, введение в предлагаемое устройство задержки последовательно соединенных конденсатора 8 и резистора 9, включенных между выходом элемента И- НЕ 1 и общей щиной питания, и подключения точки их соединения к входу инвертора, выход которого подключен к BTOpOiMy входу элемента И-НЕ 1, обеспечивает во всех режимах работы устройства полный заряд конденсатора 6 задержки 2, что обеспечивает стабильную выдержку времени. К тому же при сигналах по.мехи на входе задержки, длительность которых меньще информационного сигнала выходной импульс не формируется. Предлагаемое устройство задержки с заделкой может применяться в устройствах автоматики, где необходи.мо стабильное время задержки на появление выходного сигпала и может быть использовано как селектор длительности и частоты следования импульсов. Импульсы, длительность которых меньще времени задержки, не вызывают появления сигнала на выходе, при увеличении частоты выще предельной, обусловленной временем задержки, сигнал на выходе также не появляется. формула изобретения Устройство задержки, содержащее элемент И-НЕ, первый вход которого подключен к щине запускающего сигнала, а выход через элемент задержки подключен к первому входу триггера, второй вход которого подключен к выходу инвертора, отличающееся тем, что, с целью стабилизации времени задержки-, в него введены последовательно соединенные конденсатор и резистор, включенные между выходом элемента И-

НЕ и общей шиной питания, а точка их соединения подключена к входу инвертора, выход которого подключен к второму входу элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе

фиг. 5-19 б (прототип).

Авторы

Даты

1981-03-15—Публикация

1979-04-12—Подача