Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления циклическими процессами по заданным программам.

Целью изобретения является расширение функциональных возможностей устройства за счет формирования сигналов управления и временных интервалов между ними для нескольких каналов управления одновременно и независимо друг от друга.

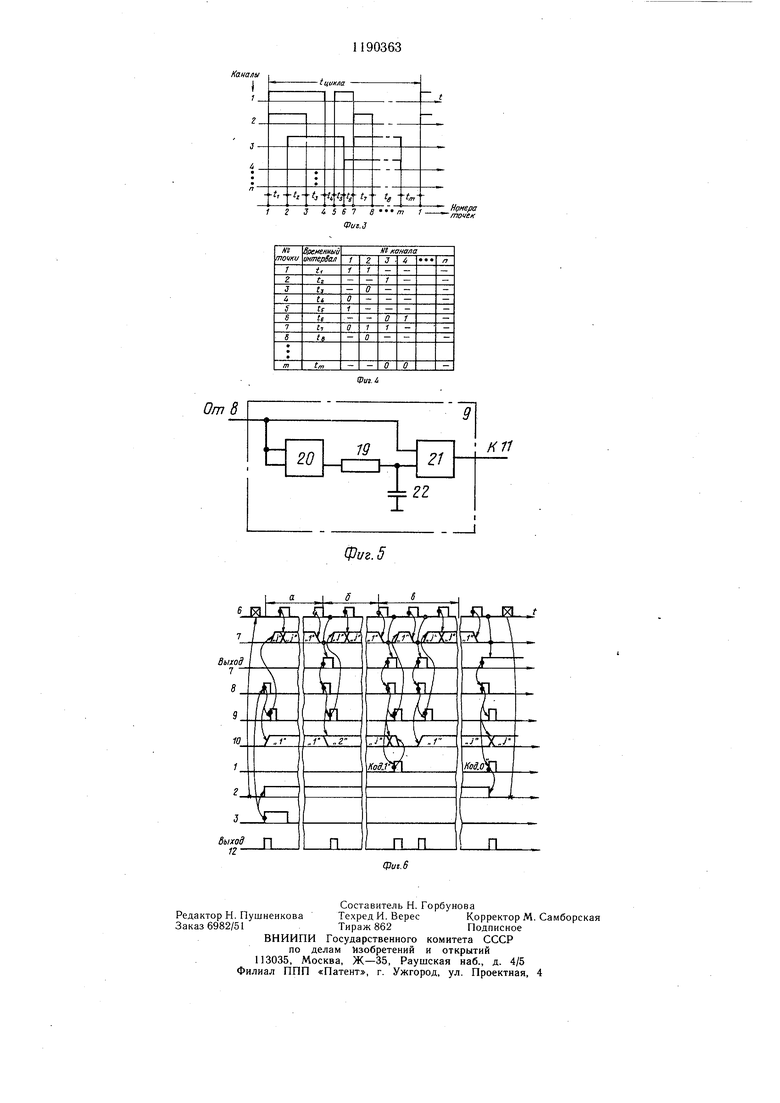

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - структура управляющего слова; на фиг. 3 - циклограммы работы каналов; на фиг. 4 - таблица временных интервалов и управляющих действий; на фиг. 5 - схема элемента задержки; на фиг. 6 - временные диаграммы работы устройства.

Устройство содержит дещифратор 1, первый триггер 2, вход устройства 3, элемент ИЛИ 4, первый элемент И- 5, генератор 6 импульсов, первый счетчик 7 импульсов, формирователь 8 импульсов, элемент 9 задержки, второй счетчик 10 импульсов, первый блок 11 памяти, второй блок 12 памяти, вторые элементы И , вторые триггеры 14i-14„, третьи элементы И 15i - 15п, выходы 16i-16„ устройства, первые и вторые выходы 17i-17п, 18i-18п второго блока памяти.

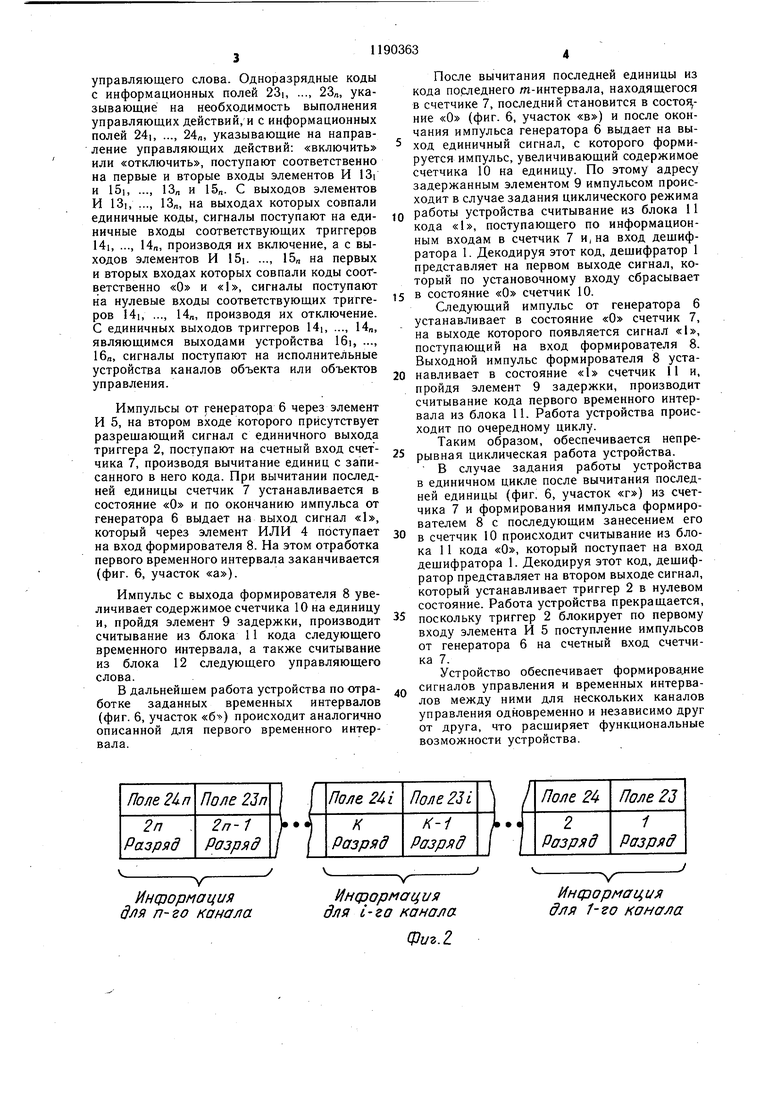

Элемент 9 задержки содержит резистор 19, четвертый и пятый элементы 20 и 21 и емкость 22.

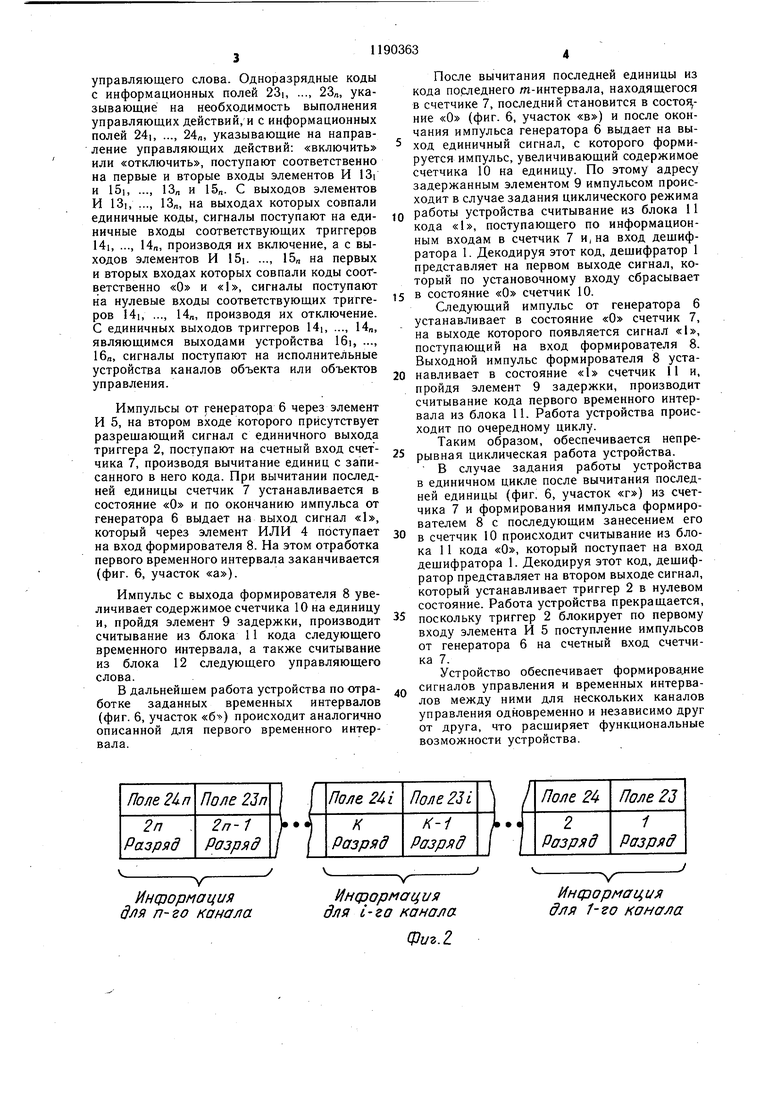

Управляющее слово блока 12 памяти имеет вид, представленный на фиг. 2. На каждый канал отведено два разряда слова. Информационные поля 23i и 24i ,..., 23п и 24„ относятся соответственно к каналам 1, ..., п. В поле 23; заносится информация, указывающая на необходимость выполнения управляющего действия В/-М канале: код «1 - производить управляющее действие, код «О - не производить управляющего действия.

В поле 24, заносится информация, определяющая направление управляющего действия в г-м канале: код «1 - «включить, код «О - «отключить.

Счетчик 7 представляет собой синхронный двоичный счетчик, работающий в режиме вычитания. Он может быть выполнен на микросхемах типа К155 ИЕ7. На выходе счетчика импульс формируется при появлении на выходах всех разрядов счетчика 7 логического «О и когда импульс от генератора 6, подаваемый через элемент И на вычитающий счетный вход, находится в состоянии логического «О. Разрядность счетчика 7 определяется разрядностью слова блока 11 памяти.

Блоки 11 и 12 представляют собой перепрограммируёмые постоянные запоминающие устройства, работающие в режиме считывания записанной в них информации, могут быть выполнены на микросхемах типа

К573 РФ2. В блок 11 записываются двоичные коды величин временных интервалов, количество которых определяется следующим образом.

В процессе подготовительной работы при анализе заданных циклограмм работы всех каналов определяют и фиксируют на общей оси времени все моменты, в которые необходимо производить соответствующие управляющие действия: включить или отклю0 чить (фиг. 3).

По полученным данным составляют таблицу, приведенную на фиг. 4, в которую

заносят номера точек фиксации 1 т,

временные интервалы i, ..., tm и обозначения управляющих действий в каналах 1, ..., п

5 в виде «1 - «включить, «О - «отключить, «- - управляющего действия не производить.

Номера точек представляют собой адреса для блоков 11 и 12, величины временных интервалов по каждому адресу - содержимое

памяти блока 11, обозначение управляющих действий по всем каналам по каждому адресу в виде управляющих слов (фиг. 2) - содержимое памяти блока 12.

Формирователь 8 импульсов предназначен для формирования импульсов укороченной длительности и может быть выполнен на микросхеме типа К155 АГ1.

Элемент 9 задержки может быть выполнен на микросхемах серии К155.

Дешифратор 1 выбирает две кодовые

комбинации кода временного интервала: код «1, в этом случае сигнал появляется на его первом выходе, код «О - сигнал появляется на втором выходе.

Счетчик 10 представляет собой обычный двоичный счетчик, разрядность которого определяется количеством точек фиксации моментов управляющих действий.

Устройство работает следующим образом.

В исходном положении счетчик 7 и 10

и триггер 2 находятся в нулевом состоянии.

0 Сигнал включения устройства, поступающий по входу 3, устанавливает триггер 2 в единичное состояние и через элемент ИЛИ 4 поступает на вход формирователя 8, формирующего с переднего фронта запускающего сигнала короткий импульс, который

5 по счетному входу устанавливает счетчик 10 в состояние «1 и поступает на вход элемента 9 задержки. Задержанный импульс с выхода элемента 9 задержки поступает на управляющий вход блока 11 памяти и производит в соответствии с адресом, поступающим из счетчика 10, считывание кода первого временного интервала, который заносится по информационным входам в счетчик 7, устанавливая его в соответствующее состояние «/.

Одновременно с этим импульс с элемента 9 задержки поступает на управляющий вход блока 12 памяти, на адресных входах которого присутствует код «1 с выхода счетчика 10, и производит считывание первого

управляющего слова. Одноразрядные коды с информационных полей 23i 23п, указывающие на необходимость выполнения управляющих действий, и с информационных полей 24л, указывающие на направление управляющих действий: «включить или «отключить, поступают соответственно на первые и вторые входы элементов И 13i и 15i, ..., 13„ и 15п. С выходов элементов И 13, ..., 13„, на выходах которых совпали единичные коды, сигналы поступают на единичные входы соответствующих триггеров 14i, ..., 14„, производя их включение, а с выходов элементов И 15i. ..., 15„ на первых и вторых входах которых совпали коды соответственно «О и «1, сигналы поступают на нулевые входы соответствующих триггеров 14i, ..., 14„, производя их отключение. С единичных выходов триггеров 14i, ..., 14п, являющимся выходами устройства 16i, ..., 16п, сигналы поступают на исполнительные устройства каналов объекта или объектов управления.

Импульсы от генератора 6 через элемент И 5, на втором входе которого присутствует разрещающий сигнал с единичного выхода триггера 2, поступают на счетный вход счетчика 7, производя вычитание единиц с записанного в него кода. При вычитании последней единицы счетчик 7 устанавливается в состояние «О и по окончанию импульса от генератора 6 выдает на выход сигнал «1, который через элемент ИЛИ 4 поступает на вход формирователя 8. На этом отработка первого временного интервала заканчивается (фиг. 6, участок «а).

Импульс с выхода формирователя 8 увеличивает содержимое счетчика 10 на единицу и, пройдя элемент 9 задержки, производит считывание из блока 11 кода следующего временного интервала, а также считывание из блока 12 следующего управляющего слова.

В дальнейшем работа устройства по отработке заданных временных интервалов (фиг. 6, участок «6-) происходит аналогично описанной для первого временного интервала.

После вычитания последней единицы из кода порледнего т-интервала, находящегося в счетчике 7, последний становится в COCTOJ ние «О (фиг. 6, участок «в) и после окончания импульса генератора 6 выдает на выход единичный сигнал, с которого формируется импульс, увеличивающий содержимое счетчика 10 на единицу. По этому адресу задержанным элементом 9 импульсом происходит в случае задания циклического режима 0 работы устройства считывание из блока 11 кода «1, поступающего по информационным входам в счетчик 7 и, на вход дешифратора 1. Декодируя этот код, дешифратор 1 представляет на первом выходе сигнал, который по установочному входу сбрасывает в состояние «О счетчик 10.

5

Следующий импульс от генератора б устанавливает в состояние «О счетчик 7, на выходе которого появляется сигнал «I, поступающий на вход формирователя 8. Выходной импульс формирователя 8 устанавливает в состояние «1 счетчик 11 и,

0 пройдя элемент 9 задержки, производит считывание кода первого временного интервала из блока 11. Работа устройства происходит по очередному циклу.

Таким образом, обеспечивается непрерывная циклическая работа устройства.

В случае задания работы устройства в единичном цикле после вычитания последней единицы (фиг. 6, участок «г) из счетчика 7 и формирования импульса формирователем 8 с последующим занесением его 0 в счетчик 10 происходит считывание из блока 11 кода «О, который поступает на вход дешифратора 1. Декодируя этот код, дешифратор представляет на втором выходе сигнал, который устанавливает триггер 2 в нулевом состояние. Работа устройства прекращается, 5 поскольку триггер 2 блокирует по первому входу элемента И 5 поступление импульсов от генератора 6 на счетный вход счетчика 7.

Устройство обеспечивает формирова ние сигналов управления и временных интерва0лов между ними для нескольких каналов управления одновременно и независимо друг от друга, что расширяет функциональные возможности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1985 |

|

SU1332263A1 |

| Весоизмерительное устройство для грузов, подвешенных в захвате конвейера | 1991 |

|

SU1806331A3 |

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для программного управления | 1982 |

|

SU1057927A1 |

| Автоматический измеритель импульсной мощности СВЧ радиосигналов | 1985 |

|

SU1287025A1 |

| Устройство для ввода аналоговых сигналов | 1990 |

|

SU1742810A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее генератор импульсов, подключенный выходом к первому входу первого элемента И, соединенного вторым входом с прямым выходом первого триггера, а выходом - со счетным входом первого счетчика импульсов, первый блок памяти, подключенный управляющим входом к выходу элемента задержки, а адресным входом - к выходу второго счетчика импульсов, дешифратор, формирователь импульсов и элемент ИЛИ, связанный первым входом с входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены Jr второй блок памяти, по числу каналов управления - вторые триггеры, вторые и третьи элементы И, подключенные выходами соответственно к единичному и .нулевому входам соответствующего триггера, первыми входами - к соответствующему первому выходу второго блока памяти, а вторыми входами - к соответствующему второму выходу второго блока памяти, соединенного управляющим входом с выходом элемента задержки, а адресным входом - с выходом второго счетчика импульсов, связанного входом обнуления с первым выходом дешифратора, а счетным входом - с входом элемента задержки и с выходом формирователя импульсов, подключенного входом к выходу ИЛИ, связанного вторым входом с выходом первого i счетчика импульсов, подключенного установочным входом к информационному выходу (Л первого блока памяти и к входу дешифратора, соединенного вторым входом с нулевым входом триггера, подключенного единичным входом к первому входу элемента ИЛИ. IHIh ;о о 00 Од со

Информация

Информация для п-го канала для L-ZO канала

V

Инсрормация для канала

Фиг.г

/ г 3 it 5 е 1 I

Фиг.З

Номера

/77Г .

| Устройство для программного управления | 1981 |

|

SU1003021A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления | 1982 |

|

SU1057927A1 |

Авторы

Даты

1985-11-07—Публикация

1984-05-31—Подача