to

САЭ

;о со

05

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство ввода информации | 1985 |

|

SU1305691A2 |

| Многоканальное устройство ввода информации | 1984 |

|

SU1196882A1 |

| Устройство для ввода информации | 1986 |

|

SU1363225A2 |

| Устройство для ввода информации | 1985 |

|

SU1317446A1 |

| Устройство для ввода информации | 1985 |

|

SU1290337A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1251181A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

Изобретение относится к вычислительной технике, может быть использовано в качестве устройства для селекции информационных каналов в Многоканальных системах сбора, регистрации и обработки измерительной информации и является дополнительным к авт.св. СССР № 1196882. Цель изобретения - повьшение надежности устройства за счет уменьшения требуемого информационного объема оперативной памяти. Это -достигается тем что в устройстве используется два блока памяти, в которых хранятся признаки соответственно безусловного выделения и выделения при выполнении соответствующих условий. 4 ил. с ts

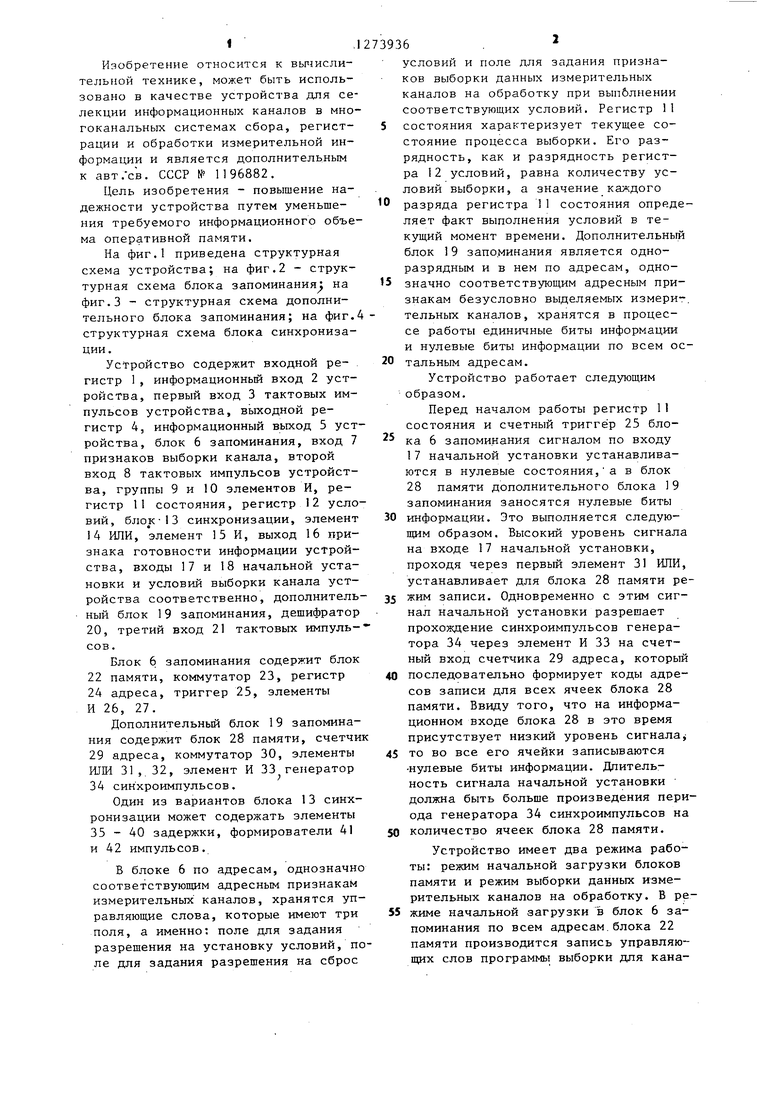

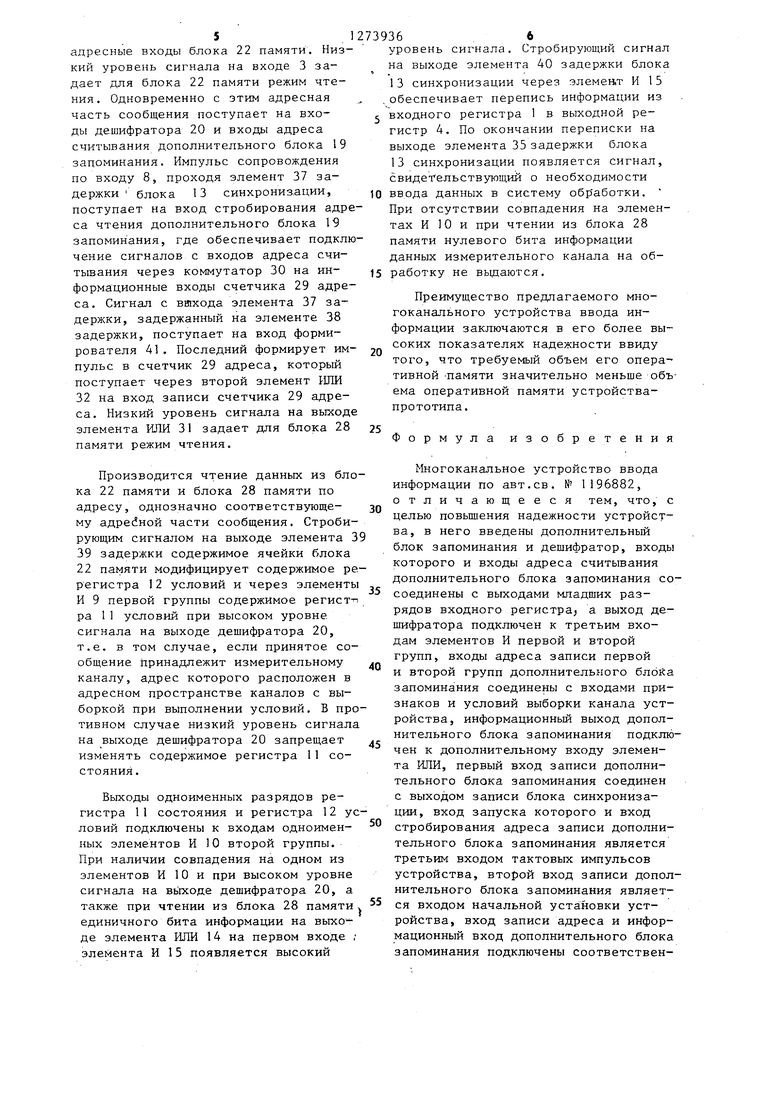

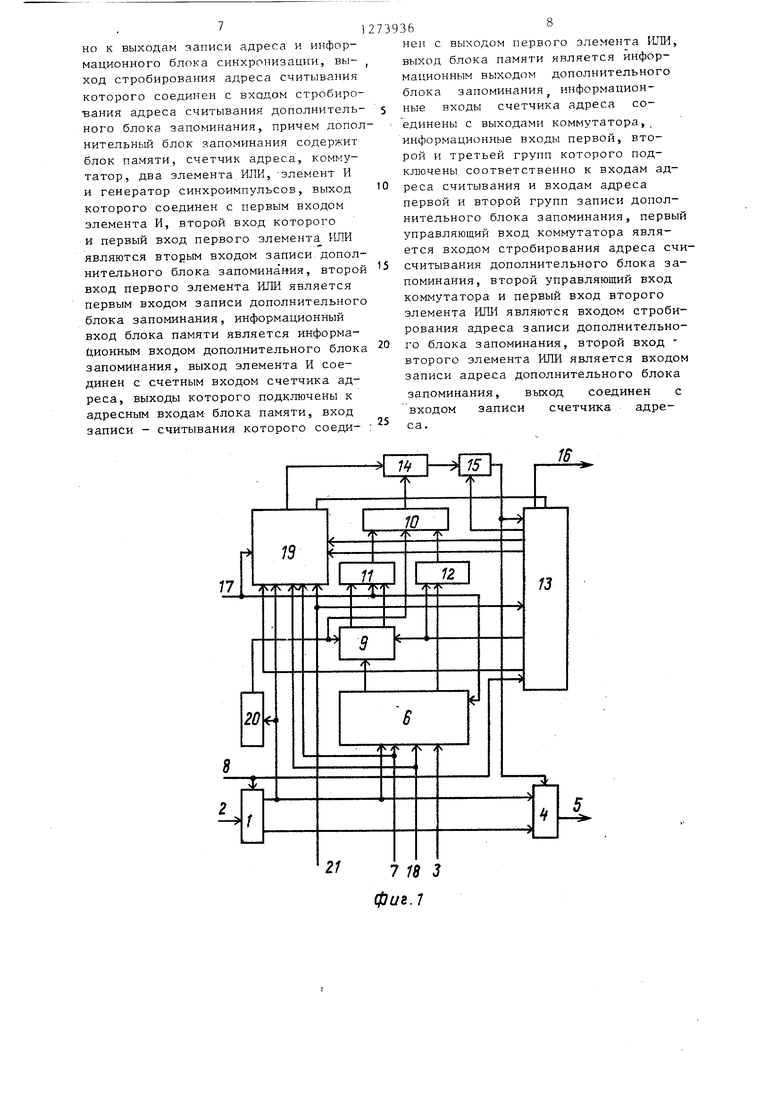

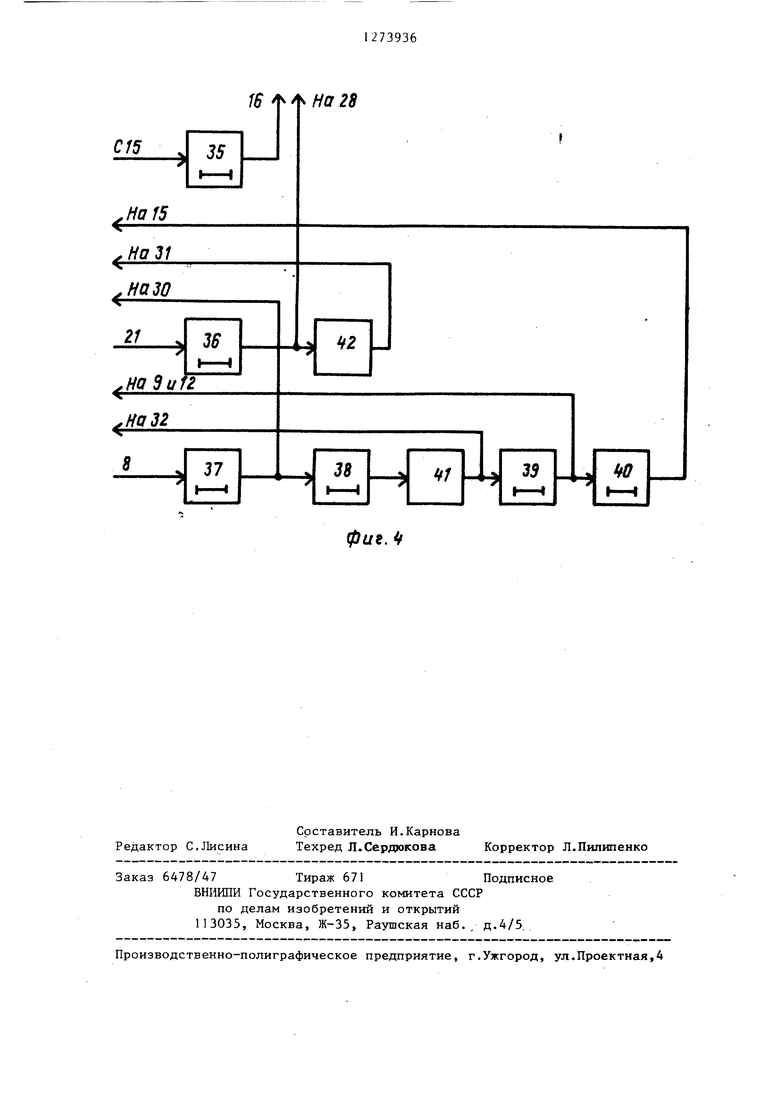

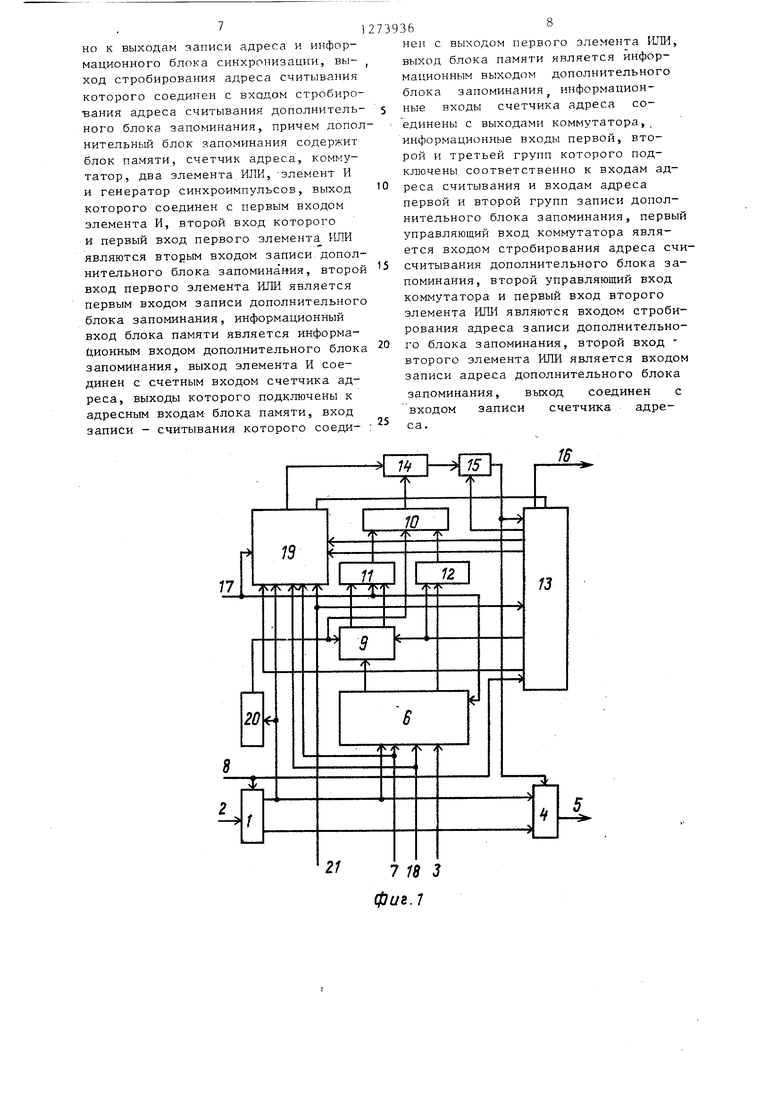

o t Изобретение относится к вычислительной технике, может быть использовано в качестве устройства для се лекции информационных каналов в мно гоканальных системах сбора, регистрации и обработки измерительной информации и является дополнительным к авт.-св. СССР № 1196882. Цель изобретения - повышение надежности устройства путем уменьшения требуемого информационного объе ма оперативной памяти. На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока запоминания на фиг.З - структурная схема дополнительного блока запоминания; на фиг. структурная схема блока синхронизации. Устройство содержит входной регистр 1, информационный вход 2 устройства, первый вход 3 тактовых импульсов устройства, выходной регистр 4, информационный выход 5 уст ройства, блок 6 запоминания, вход 7 признаков выборки канала, второй вход 8 тактовых импульсов устройства, группы 9 и 10 элементов И, регистр 11 состояния, регистр 12 усло вий, блок13 синхронизации, элемент 14 ИЛИ, элемент 15 И, выход 16 признака готовности информации устройства, входы 17 и 18 начальной установки и условий выборки канала устройства соответственно, дополнитель ный блок 19 запоминания, дешифратор 20, третий вход 21 тактовых импульсов, Блок 6 запоминания содержит блок 22 памяти, коммутатор 23, регистр 24 адреса, триггер 25, элементы И 26, 27, Дополнительный блок 19 запоминания содержит блок 28 памяти, счетчи 29 адреса, коммутатор 30, элементы ШШ 31 ,, 32, элемент И 33 генератор 34синхроимпульсов. Один из вариантов блока 13 синхронизации может содержать элементы 35- 40 задержки, формирователи 41 и 42 импульсов, В блоке 6 по адресам, однозначно соответствующим адресным признакам измерительных каналов, хранятся управляющие слова, которые имеют три поля, а именно: поле для задания разрешения на установку условий, по ле для задания разрешения на сброс 6 условии и поле для задания признаков выборки данных измерительных каналов на обработку при выпблнении соответствующих условий. Регистр 11 состояния характеризует текущее состояние процесса выборки. Его разрядность, как и разрядность регистра 12 условий, равна количеству условий выборки, а значение каждого разряда регистра 11 состояния определяет факт выполнения условий в текущий момент времени. Дополнительный блок 19 запоминания является одноразрядным и в нем по адресам, однозначно соответствующим адресным признакам безусловно выделяемых измери-. тельных каналов, хранятся в процессе работы единичные биты информации и нулевые биты информации по всем остальным адресам. Устройство работает следующим образом. Перед началом работы регистр 11 состояния и счетный триггер 25 блока 6 запоминания сигналом по входу 17 начальной установки устанавливаются в нулевые состояния,а в блок 28 памяти дополнительного блока 19 запоминания заносятся нулевые биты информации. Это выполняется следующим образом. Высокий уровень сигнала на входе 17 начальной установки, проходя через первый элемент 31 ИЛИ, устанавливает для блока 28 памяти режим записи. Одновременно с этим сигнал начальной установки разрешает прохождение синхроимпульсов генератора 34 через элемент И 33 на счетный вход счетчика 29 адреса, который последовательно формирует коды адресов записи для всех ячеек блока 28 памяти. Ввиду того, что на информационном входе блока 28 в это время присутствует низкий уровень сигналаj то во все его ячейки записываются -нулевые биты информации. Дпительность сигнала начальной установки должна быть больше произведения периода генератора 34 синхроимпульсов на количество ячеек блока 28 памяти. Устройство имеет два режима работы: режим начальной загрузки блоков памяти и режим выборки данных измерительных каналов на обработку. В режиме начальной загрузки в блок 6 запоминания по всем адресам.блока 22 памяти производится запись управляющих слов программы выборки для каналов, выделение данных от которых на обработку производится при выполнеНИИ соответствующих условий. В этом же режиме производится запись в бло 28 памяти блока 19 запоминания единичных битов информации по адресам, однозначно соответствующим адресным признакам измерительных каналов требующих безусловного выделения. В адресном пространстве адресные при знаки измерительных каналов, данные от которых подлежат выборке при выполнении соответствующих условий, имеют последовательно расположенные без промежутков адреса. Управляющее слово, записываемое по К-тому адресу блока 22 памяти, с держит единицы в разрядах поля разрещения на установку соответствующих разрядов регистра 11, которые необходимо установить при поступлении данных К-го измерительного канала. Управляющее слово, записываемое по К-му адресу, содержит единицы в разрядах поля разрешения на сброс соответствующих разрядов регистра 1I, которые необходимо сбросить при поступлении данных К-го из мерительного ,канала. Это управляющее слово содержит единицы в тех ра рядах поля признаков выборки, которые определяют условия, при выполнении которых и при приеме данных К-го измерительного канала последни выдается на обработку. Начальная загрузка блока 6 запоминания выполняется следующим образом. На входы 7 и 18 сопровождения сигнала на входе 3 поступают ко ды адресов блока 22 и коды управляю щих слов, записываемых по этим адре сам. Коды адресов и управляющих сло чередуются между собой таким образом, что первый и все последующие нечетные посылки на входам 7 и 18 я ляются кодами адресов, а второй и все последующие четные посылки явля ются кодами управляющих слов , Первый все последующие нечетные импульсы по входу 3, проходя через открытый элемент И 26, осуществляют запись адреса управляющего слова с входов 7 и 18 в регистр 24 адреса и задним фронтом модифицируют (изменяют на. противоположное) состояние счетного триггера 25. Второй и все последующие четные импульсы сопровождения по входу 3, проходя через элемент 64 И 27, осуществляют запись кода управляющего слова с входов 7 и 18 в блок 22 памяти по адресу, храня(Цемуся на регистре 24 адреса, и задним фронтом модифицируют состояние триггера 25. Выходные сигналы регистра 24 адреса подключаются к адресным входам блока 22 памяти через коммутатор 23 при единичном состоянии триггера 25. По окончании загрузки блока 6 запоминания выполняется загрузка дополнительного блока 19 запоминания . При этом на входы 7 и 18 в сопровождении сигнала на входе 21 поступают коды адресов блока 28 памяти, по которым должны быть записаны единичные биты информации, что определяет в дальнейщем безусловную выборку данных этих измерительных каналов на обработку. Каждый импульс по входу 21, поступая на вход стро- i бирования адреса записи блока 19 запоминания, подключает к входам счетчика 29 адреса через коммутатор 30 сигналы с входов 7 и 18 устройства. Одновременно с этим сигнал на входе 21 через элемент ИЛИ 32 поступает на на вход записи счетчика 29 адреса и переписывает в него код с входов 7 и 18. Сигнал с входа 21, задержанный на элементе 36 задержки блока 13 синхронизации, поступает на информационный вход блока 28 памяти, на вход записи - считывания которого поступает через элемент ИЛИ 31 сигнал с выхода формирователя 42, осуществляющего запись единичного бита информации в блок 28 памяти по адресу, хранящемуся на счетчике 29 адреса. Запись последующих единичных битов информации в блок 28 памяти производится аналогично. По окончании загрузки дополнительного блока 19 запоминания устройство готово к работе в режиме выборки данных измерительных каналов на обработку. В режиме выборки данных измерительных каналов на обработку устройство работает следующим образом. С приходом информационной посыпки на информационный вход 2 в сопровождении импульса на входе 8 по переднему фронту импульса сопровождения данные с входа 2 переписываются во входной регистр 1. По окончании записи адресная часть сообщения поступает на первые входы блока 6 запоминания и через коммутатор 23 на адресные входы блока 22 памяти. Низкий уровень сигнала на входе 3 задает для блока 22 памяти режим чтения. Одновременно с этим адресная часть сообщения поступает на входы дешифратора 20 и входы адреса считывания дополнительного блока 19 зацоминания. Импульс сопровождения по входу 8, проходя элемент 37 задержки блока 13 синхронизации, поступает на вход стробирования адре са чтения дополнительного блока 19 запоминания, где обеспечивает подклю чение сигналов с входов адреса считывания через коммутатор 30 на информационные входы счетчика 29 адре са. Сигнал с втхода элемента 37 задержки, задержанный на элементе 38 задержки, поступает на вход формирователя 41. Последний формирует им пульс в счетчик 29 адреса, который поступает через второй элемент 1-ШИ 32 на вход записи счетчика 29 адреса. Низкий уровень сигнала на выход элемента ИЛИ 31 задает для блока 28 памяти режим чтения. Производится чтение данньк из бл ка 22 памяти и блока 28 памяти по адресу, однозначно соответствующему адресной части сообщения. Строби рующим сигналом на выходе элемента 39 задержки содержимое ячейки блока 22 памяти модифицирует содержимое р регистра 12 условий и через элемент И 9 первой группы содержимое регист ра 11 условий при высоком уровне сигнала на выходе дешифратора 20, т.е. в том случае, если принятое со общение принадлежит измерительному каналу, адрес которого расположен в адресном пространстве каналов с выборкой при выполнении условий. В пр тивном случае низкий уровень сигнал на выходе дешифратора 20 запрещает изменять содержимое регистра 11 состояния. Выходы одноименных разрядов регистра 11 состояния и регистра 12 у ловий подключены к входам одноименных элементов И 10 второй группы. При наличии совпадения на одном из элементов И 10 и при высоком уровне сигнала на вьгходе дешифратора 20, а также при чтении из блока 28 памяти единичного бита информации на выходе элемента ИЛИ I4 на первом входе элемента И 15 появляется высокий ровень сигнала. Стробирующий сигнал а выходе элемента 40 задержки блока 13 синхронизации через элемент И 15 обеспечивает перепись информации из ходного регистра 1 в выходной регистр 4. По окончании переписки на выходе элемента 35 задержки блока 13 синхронизации появляется сигнал, свидетельствующий о необходимости ввода данных в систему обработки. При отсутствии совпадения на элементах И 10 и при чтении из блока 28 памяти нулевого бита информации данных измерительного канала на обработку не выдаются. Преимущество предлагаемого многоканального устройства ввода информации заключаются в его более высоких показателях надежности ввиду того, что требуемый объем его оперативной -памяти значительно меньше объема оперативной памяти устройствапрототипа. Формула изобретения Многоканальное устройство ввода информации по авт.св. № 1196882, отличающееся тем, что, с целью повьщ1ения надежности устройства, в него введены дополнительный блок запоминания и дешифратор, входы которого и входы адреса считывания дополнительного блока запоминания сосоединены с выходами младших разрядов входного регистра а выход дешифратора подключен к третьим входам элементов И первой и второй групп, входы адреса записи первой и второй групп дополнительного блойа запоминания соединены с входами признаков и условий выборки канала устройства, информационный выход дополнительного блока запоминания подключен к дополнительному входу элемента ИЛИ, первый вход записи дополнительного блока запоминания соединен с выходом записи блока синхронизации, вход запуска которого и вход стробирования адреса записи дополнительного блока запоминания является третьим входом тактовых импульсов устройства, второй вход записи дополнительного блока запоминания является входом начальной установки устройства, вход записи адреса и информационный вход дополнительного блока запоминания подключены соответственно к выходам записи адреса и информационного блока синхронизации, выход стробирования адреса считывания которого соединен с входом стробиро вания адреса считывания дополнитель ного блока запоминания, причем допо нительный блок запоминания содержит блок памяти, счетчик адреса, коммутатор, два элемента ИЛИ, -элемент И и генератор синхроимпульсов, выход которого соединен с первым входом элемента И, второй вход которого и первый вход первого элемента ИЛИ являются вторым входом записи,допол нительного блока запоминания, второ вход первого элемента ИЛИ является первым входом записи дополнительног блока запоминания, информационный вход блока памяти является информационным входом дополнительного блок запоминания, выход элемента И соединен с счетным входом счетчика адреса, выходы которого подключены к адресным входам блока памяти, вход записи - считывания которого соеди7 18 3 фив. 7 36 ней с выходом первого элемента ИЛИ, выход блока памяти является информационным выходом дополнительного блока запоминания информационные входы счетчика адреса соединены с выходами коммутатора,, информационные входы первой, второй и третьей групп которого подключены соответственно к входам адреса считывания и входам адреса первой и второй групп записи дополнительного блока запоминания, первый управляющий вход коммутатора является входом стробирования адреса счисчитывания дополнительного блока запоминания, второй управляющий вход коммутатора и первый вход второго элемента ИЛИ являются входом стробирования адреса записи дополнительного блока запоминания, второй вход второго элемента ИЛИ является входом записи адреса дополнительного блока запоминания, выход соединен с входом записи счетчика адреса.

t Т

фиб.З

фиг. 2

фие.

| Многоканальное устройство ввода информации | 1984 |

|

SU1196882A1 |

Авторы

Даты

1986-11-30—Публикация

1985-06-21—Подача