VI

4 Ю 00

о

Изобретение относится к вычислительной технике и может быть использовано для ввода аналоговой информации в ЭВМ.

Известно устройство для ввода информации, содержащее аналого-цифровой преобразователь, блок памяти, первый, второй и третий счетчики, коммутатор, первый, второй и третий элементы И, генератор, регистр, первый, второй и третий узлы выборки-хранения, элемент 2-И-ИЛИ. четвертый счетчик, второй дешифратор и элемент НЕ, первый дешифратор, входы которого совместно с входами группы второго и третьего счетчиков являются управляющими входами группы устройства, выходы аналого-цифрового преобразователя соединены с входами первой группы блока памяти.выходы которого являются выходами группы устройства, выход генератора соединен с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом первого счетчика, выходы которого соединены с входами второй группы блока памяти, вход которого соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с вторым и третьим выходами регистра, входы группы которого соединены соответственно с выводами первого дешифратора, первый выход регистра соединен с вторым входом первого элемен- та И, выходы второго счетчика соединены с входами группы коммутатора, выходы третьего счетчика соединены соответственно с входами второго элемента И. выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого счетчика, выход второго элемента ИЛИ соединен с входом регистра и является выходом устройства, выход элемента НЕ соединен с первым входом третьего элемента И, второй вход которого соединен с первым выходом второго дешифратора, второй выход которого соединен с вторым входом третьего узла выборки-хранения, выход которого соединен с первым входом аналого-цифрового преобразователя, второй вход которого соединен с входом третьего счетчика и третьим входом второго дешифратора, входы которого соединены с выходами четвертого счетчика, вход которого соединен с выходом элемента 2-2И-ИЛИ, первый вход которого соединен с вторыми входами первого и второго узлов выборки-хранения и вторым выходом регистра, третий выход которого соединен с входом элемента НЕ и вторым входом элемента 2-2И-ИЛИ, третий вход которого соединен с выходом генератора, первые входы первого и второго узлов выборки-хранения являются информационными входами . группы устройства, выходы первого и второ5 го узлов выборки-хранения соединены соответственно с первым и вторым входами коммутатора, выход которого соединен с вторым входом третьего узла выборки-хранения, выход третьего элемента И соединен

0 с входом второго счетчика, четвертый выход второго дешифратора соединен с вторым входом первого элемента ИЛИ. В данном устройстве реализуется возможность сканирования либо всей группы входов, либо

5 выбранной группы, опрос одного входа.

Недостатком такого устройства является невозможность синхронного ввода информации, например, с аналоговых входов первого, четвертого, шестого и седьмого,

0 Необходимо задать группу входов с первого по седьмой, ввести с них информацию в память, а уже затем прочитать ее. Таким образом, необходимы операции ввода аналоговой информации с второго, третьего,

5 пятого и шестого входов, что ухудшает быстродействие устройства.

Наиболее близким к предлагаемому является устройство, содержащее мультиплексор,аналого-цифровой

0 преобразователь, первый регистр, блок памяти, первый и второй счетчик и, четыре коммутатора, блок микропрограммного управления, информационные входы мультиплексора являются входами аналоговых

5 сигналов устройства, выходы первого регистра соединены с адресными входами мультиплексора, выход которого соединен с информационным входом аналого-цифрового преобразователя, выходы которого со0 единены с информационными входами второго коммутатора, выходы которого объединены с выходами первого коммутатора и соединены с информационными входами блока памяти, выходы которого соединены

5 с информационными входами четвертого коммутатора, выходы которого объединены с выходами третьего коммутатора и соединены с информационными входами первого регистра, выходы которого являются инфор0 мационными выходами устройства, информационные входы третьего коммутатора, входы установки первого счетчика, информационные входы второго регистра и командные входы блока микропрограммного

5 управления являются управляющими входами устройства, выходы первого счетчика соединены с адресными входами блока памяти, один из выходов которого соединен с вторым управляющим входом блока мик программного управления и является управляющим выходом устройства, информационные входы первого коммутатора соединены с выходами первого регистра, выходы второго регистра соединены с установочными входами второго счетчика, выход переполнения которого соединен с первым управляющим входом блока микропрограммного управления, первый, второй, четвертый, пятый и шестой выходы которого соединены соответственно с управляющими входами второго и четвертого коммутаторов, входами разрешения записи и разрешения чтения блока памяти и управляющим входом первого регистра, третий выход блока микропрограммного управления соединен с управляющими входами первого и третьего коммутаторов, девятый выход блока микропрограммного управления соединен со счетными входами счетчиков, седьмой, восьмой, десятый и одиннадцатый выходы блока микропрограммного управления соединены соответственно с управляющим входом аналого-цифрового преобразователя, стробирующим входом первого счетчика, управляющим входом второго регистра и стробирующим входом второго счетчика Данное устройство позволяет работать в режимах подготовки элементов к преобразованию и считывания накопленной информации.

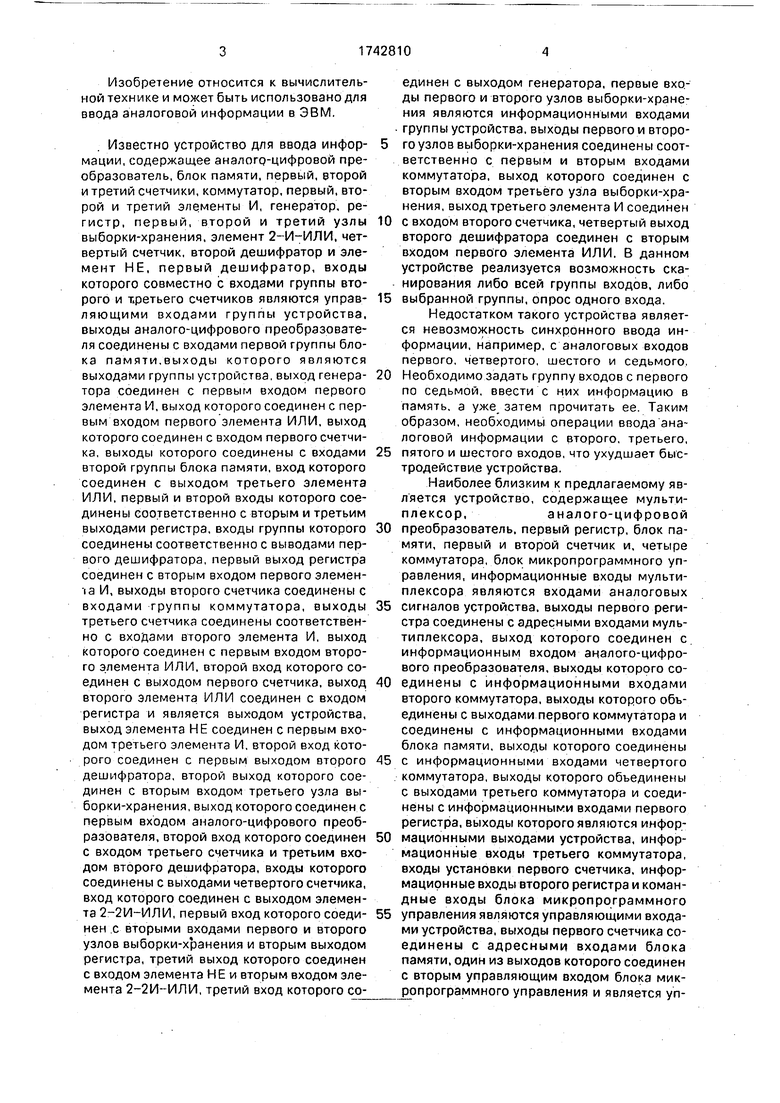

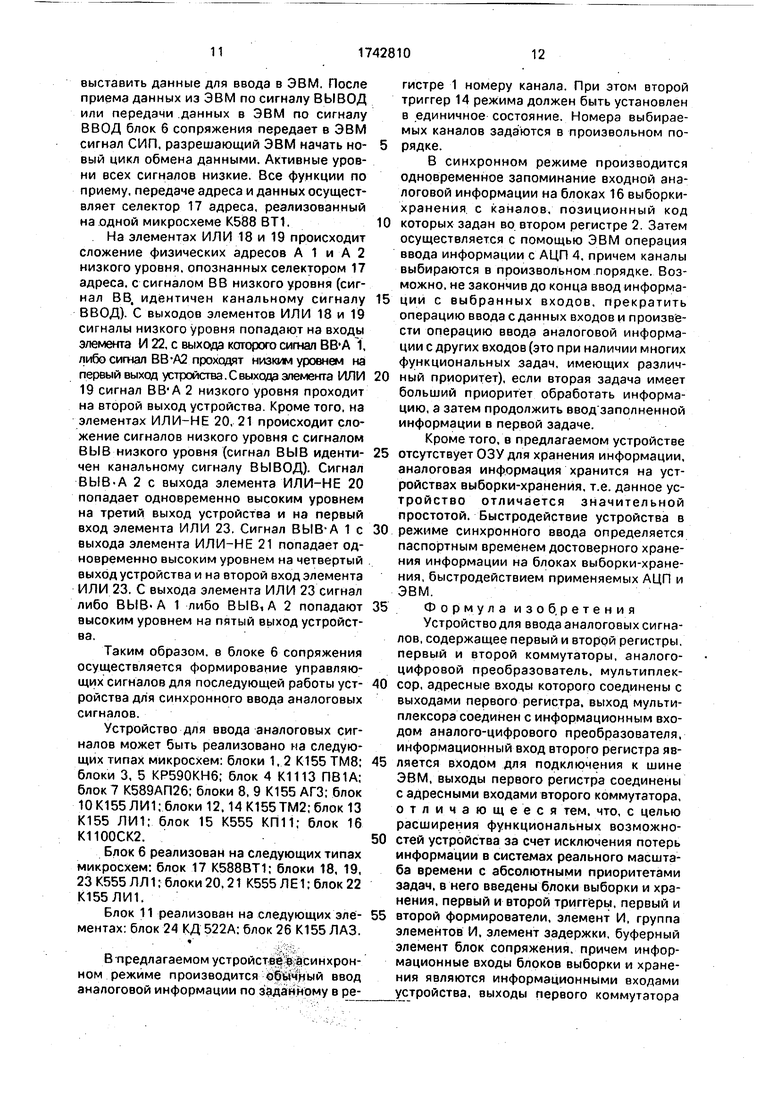

Недостатком данного устройства является невозможность использования ввода аналоговых в асинхронных процессах, характерных для систем реального времени с абсолютными приоритетами задач. Например, в системе управления технологической установкой может быть реализована задача контроля группы технологических параметров и. имеющая более высокий приоритет, задача программного управления одним из параметров (давлением, положением или скоростью вращения испытательного орга- на и т.п. ). При этом может возникнуть ситуация , иллюстрируемая на фиг. 1 Здесь процесс контроля параметров прерывается задачей программного управления. Если к моменту прерывания был осуществлен процесс запуска ввода аналоговых сигналов по нескольким каналам (например, 1,3.5, 6), но не завершен ввод результатов аналого-цифрового преобразования в память ЭВМ (пусть введены только данные по каналу 1), то при возврате управления прерванному процессу ввод должен быть продолжен. Однако ввод аналоговых сигналов в систему реального времени с абсолютными приоритетами задач приведет к смене программы

опроса каналов внутри устройства и данные по каналам 3, 5, 6 будут утеряны.

Целью изобретения является расширение функциональных возможностей за счет 5 исключения потерь информации в системах реального масштаба времени с абсолютными приоритетами задач.

Поставленная цель достигается тем, что в устройство дополнительно введены свя0 занные с интерфейсной магистралью ЭВМ блок сопряжения и буферный элемент, первый и второй формирователи, первый элемент И, элемент задержки, первый триггер, п вторых элементов И. второй триггер, п

5 блоков выборки-хранения, вторые входы которых являются входами устройства, а первые входы связаны с выходами мультиплексора, первые входы которого связаны с выходами вторых элементов И,

0 вторые входы которых объединены и связаны с выходом второго формирователя, вход которого объединен со стробирующим входом второго регистра и четвертым выходом блока сопряжения, пятый выход которого

5 связан со стробирующим входом второго триггера, выход которого соединен с управляющим входом мультиплексора, адресный вход которого соединен с выходом первого регистра информационный вход которого,

0 объединенный с информационными входами второго регистра, второго триггера, первым входом первого элемента И связан с интерфейсной магистралью ЭВМ, причем выходы второго регистра связаны с первы5 ми входами вторых элементов И, а первый выход блока сопряжения соединен с управляющим входом буферного элемента, информационный вход которого соединен с выходом АЦП, управляющий вход которого

0 соединен с выходом первого триггера, информационный вход которого соединен с шиной логического нуля устройства, а стро- бирующий вход первого триггера соединен с выходом элемента задержки, вход которо5 го объединен с информационным входом второго коммутатора и выходом первого формирователя, вход которого объединен со стробирующим входом первого регистра и третьим выходом блока сопряжения, вто0 рой выход которого соединен со вторым входом первого элемента И, выход которого соединен с установочным -входом первого триггера.

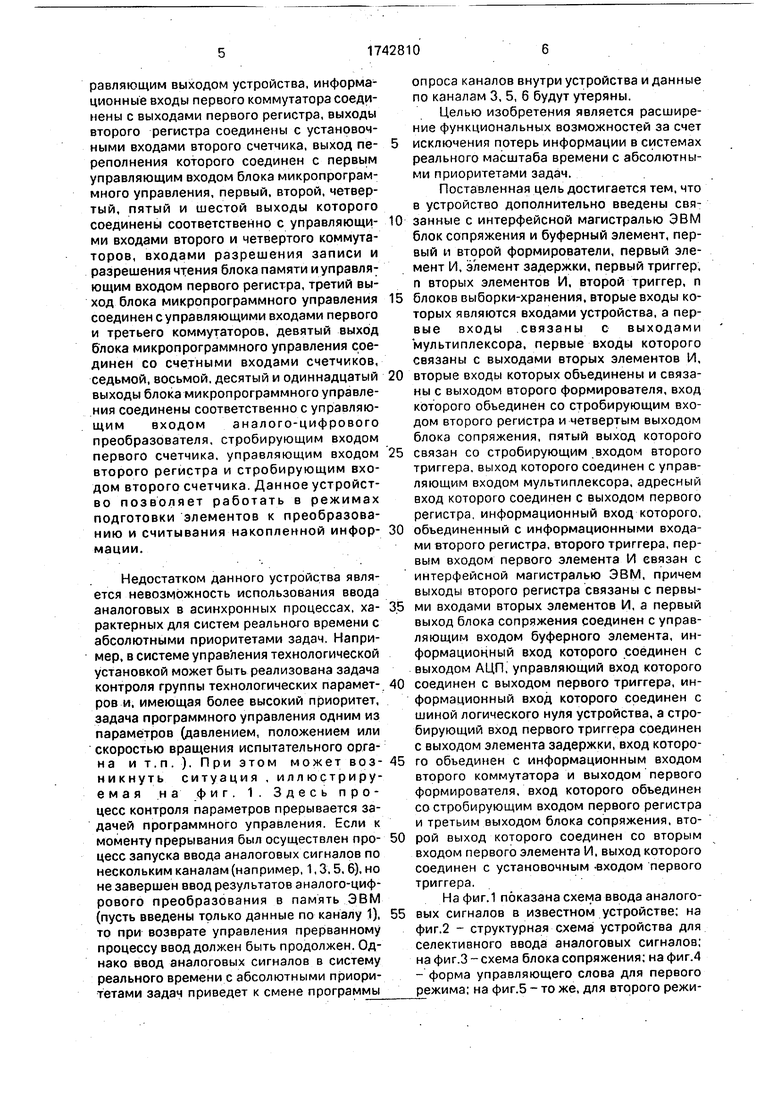

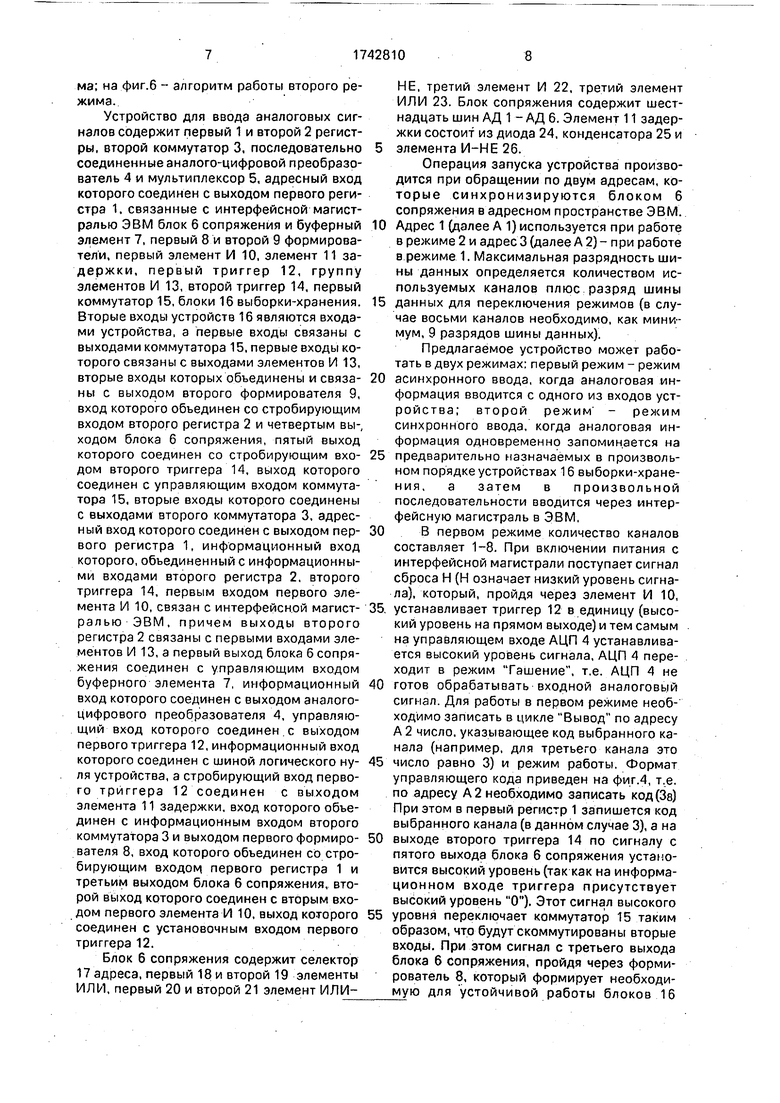

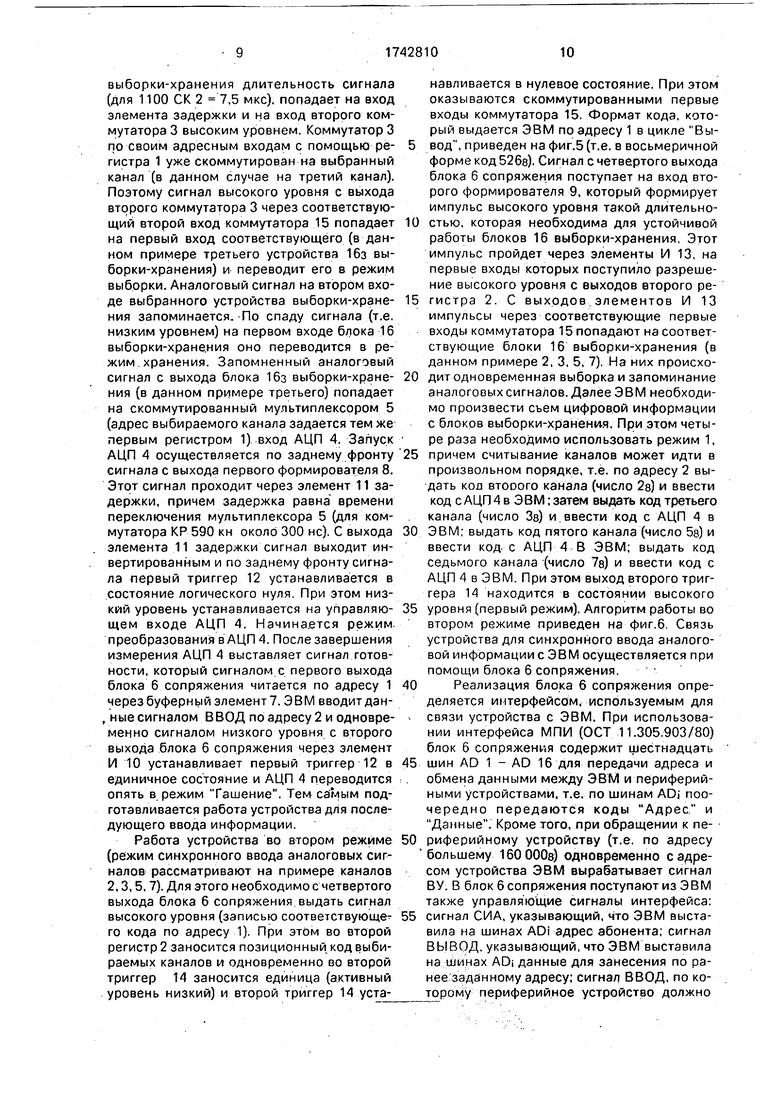

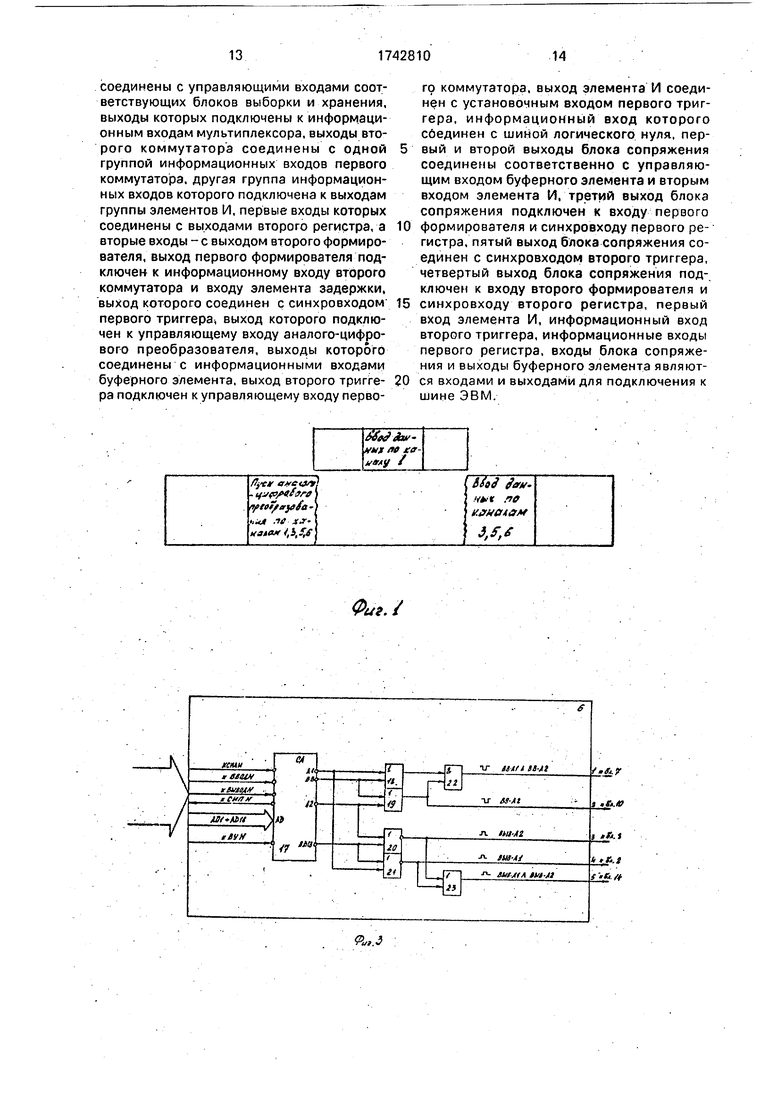

На фиг.1 показана схема ввода аналого5 вых сигналов в известном устройстве: на фиг.2 - структурная схема устройства для селективного ввода аналоговых сигналов; на фиг.З - схема блока сопряжения; на фиг.4 - форма управляющего слова для первого режима; на фиг.5 - то же, для второго режима; на фиг.6 - алгоритм работы второго режима.

Устройство для ввода аналоговых сигналов содержит первый 1 и второй 2 регистры, второй коммутатор 3, последовательно соединенные аналого-цифровой преобразователь 4 и мультиплексор 5, адресный вход которого соединен с выходом первого регистра 1. связанные с интерфейсной магистралью ЭВМ блок 6 сопряжения и буферный элемент 7, первый 8 и второй 9 формирователи, первый элемент И 10, элемент 11 задержки, первый триггер 12, группу элементов И 13, второй триггер 14, первый коммутатор 15, блоки 16 выборки-хранения. Вторые входы устройств 16 являются входами устройства, а первые входы связаны с выходами коммутатора 15, первые входы которого связаны с выходами элементов И 13, вторые входы которых объединены и связаны с выходом второго формирователя 9, вход которого объединен со стробирующим входом второго регистра 2 и четвертым выходом блока 6 сопряжения, пятый выход которого соединен со стробирующим входом второго триггера 14, выход которого соединен с управляющим входом коммутатора 15, вторые входы которого соединены с выходами второго коммутатора 3, адресный вход которого соединен с выходом первого регистра 1, информационный вход которого, объединенный с информационными входами второго регистра 2. второго триггера 14, первым входом первого элемента И 10, связан с интерфейсной магистралью ЭВМ, причем выходы второго регистра 2 связаны с первыми входами элементов И 13, а первый выход блока 6 сопряжения соединен с управляющим входом буферного элемента 7, информационный вход которого соединен с выходом аналого- цифрового преобразователя 4, управляющий вход которого соединен с выходом первого триггера 12, информационный вход которого соединен с шиной логического нуля устройства, а стробирующий вход первого триггера 12 соединен с выходом элемента 11 задержки, вход которого объединен с информационным входом второго коммутатора 3 и выходом первого формирователя 8, вход которого объединен со стробирующим входом первого регистра 1 и третьим выходом блока 6 сопряжения, второй выход которого соединен с вторым входом первого элемента И 10, выход которого соединен с установочным входом первого триггера 12.

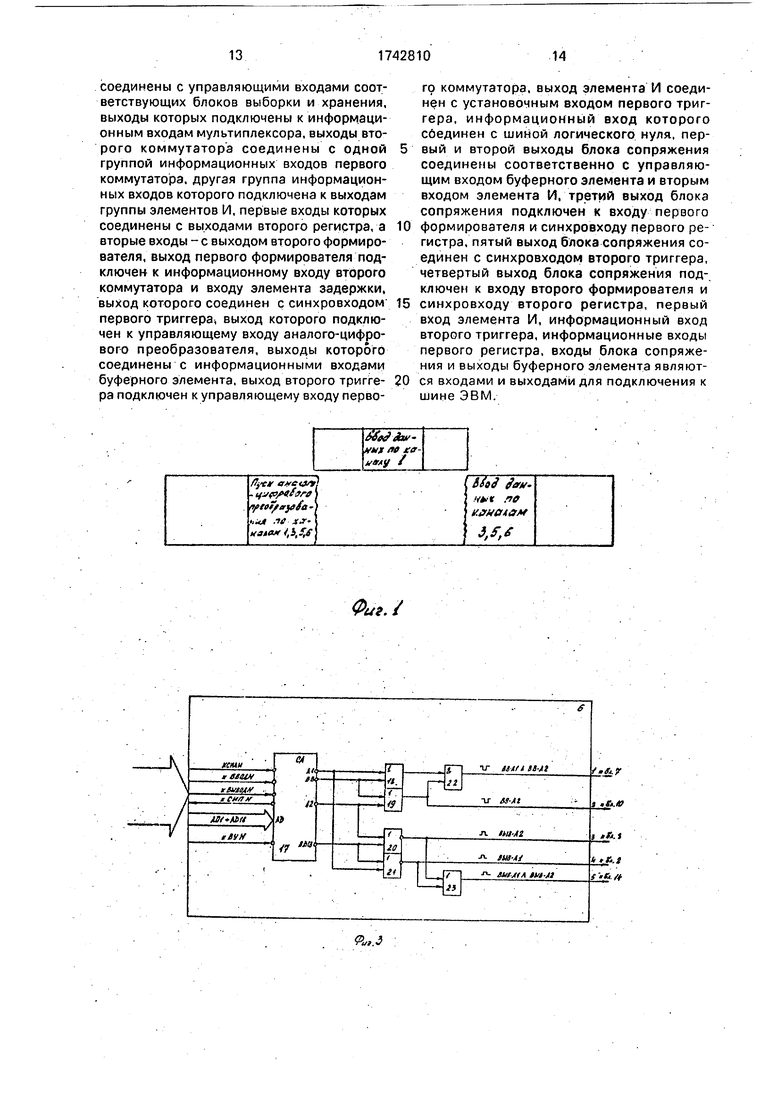

Блок 6 сопряжения содержит селектор 17 адреса, первый 18 и второй 19 элементы ИЛИ, первый 20 и второй 21 элемент ИЛИНЕ, третий элемент И 22, третий элемент ИЛИ 23. Блок сопряжения содержит шестнадцать шин АД 1 - АД 6. Элемент 11 задержки состоит из диода 24, конденсатора 25 и

элемента И-НЕ 26.

Операция запуска устройства производится при обращении по двум адресам, которые синхронизируются блоком 6 сопряжения в адресном пространстве ЭВМ.

0 Адрес 1 (далее А 1) используется при работе в режиме 2 и адрес3 (далее А 2)- при работе в режиме 1. Максимальная разрядность шины данных определяется количеством используемых каналов плюс разряд шины

5 данных для переключения режимов (в случае восьми каналов необходимо, как минимум, 9 разрядов шины данных).

Предлагаемое устройство может работать в двух режимах: первый режим - режим

0 асинхронного ввода, когда аналоговая информация вводится с одного из входов устройства; второй режим - режим синхронного ввода, когда аналоговая информация одновременно запоминается на

5 предварительно назначаемых в произвольном порядке устройствах 16 выборки-хране- ния, а затем в произвольной последовательности вводится через интерфейсную магистраль в ЭВМ,

0 В первом режиме количество каналов составляет 1-8. При включении питания с интерфейсной магистрали поступает сигнал сброса Н (Н означает низкий уровень сигнала), который, пройдя через элемент И 10,

5 устанавливает триггер 12 в единицу (высокий уровень на прямом выходе) и тем самым на управляющем входе АЦП 4 устанавливается высокий уровень сигнала, АЦП 4 переходит в режим Гашение, т.е. АЦП 4 не

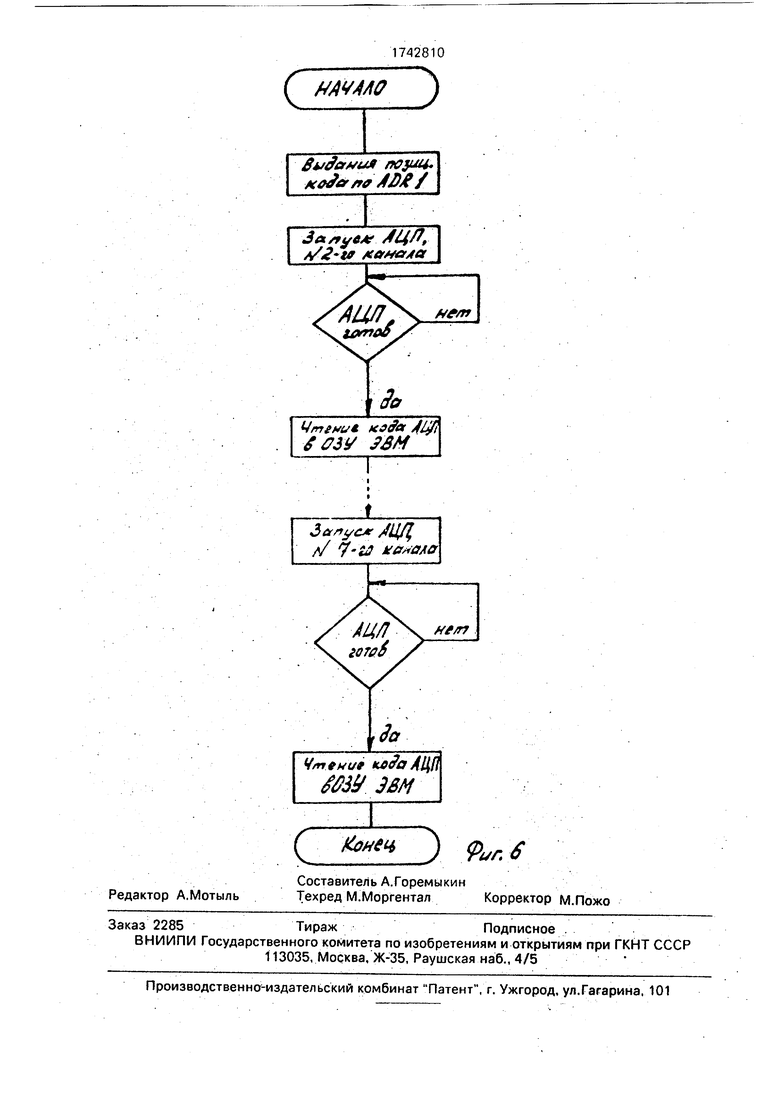

0 готов обрабатывать входной аналоговый сигнал. Для работы в первом режиме необходимо записать в цикле Вывод по адресу А 2 число, указывающее код выбранного канала (например, для третьего канала это

5 число равно 3) и режим работы. Формат управляющего кода приведен на фиг.4, т.е. по адресу А 2 необходимо записать код (3s) При этом в первый регистр 1 запишется код выбранного канала (в данном случае 3), а на

0 выходе второго триггера 14 по сигналу с пятого выхода блока 6 сопряжения установится высокий уровень (так как на информа- ционном входе триггера присутствует высокий уровень О). Этот сигнал высокого

5 уровня переключает коммутатор 15 таким образом, что будут скоммутированы вторые входы. При этом сигнал с третьего выхода блока 6 сопряжения, пройдя через формирователь 8, который формирует необходи- мую для устойчивой работы блоков 16

выборки-хранения длительность сигнала (для 1100 СК 2 7,5 мкс), попадает на вход элемента задержки и на вход второго коммутатора 3 высоким уровнем. Коммутатор 3 по своим адресным входам с помощью регистра 1 уже скоммутирован на выбранный канал (в данном случае на третий канал). Поэтому сигнал высокого уровня с выхода второго коммутатора 3 через соответствующий второй вход коммутатора 15 попадает на первый вход соответствующего (в данном примере третьего устройства 16з выборки-хранения) и переводит его в режим выборки. Аналоговый сигнал на втором входе выбранного устройства выборки-хранения запоминается. По спаду сигнала (т.е. низким уровнем) на первом входе блока 16 выборки-хранения оно переводится в режим хранения. Запомненный аналоговый сигнал с выхода блока 16з выборки-хранения (в данном примере третьего) попадает на скоммутированный мультиплексором 5 (адрес выбираемого канала задается тем же первым регистром 1) вход АЦП 4. Запуск АЦП 4 осуществляется по заднему фронту сигнала с выхода первого формирователя 8. Этот сигнал проходит через элемент 11 задержки, причем задержка равна времени переключения мультиплексора 5 (для коммутатора КР 590 кн около 300 не). С выхода элемента 11 задержки сигнал выходит инвертированным и по заднему фронту сигнала первый триггер 12 устанавливается в состояние логического нуля. При этом низкий уровень устанавливается на управляющем входе АЦП 4. Начинается режим преобразования в АЦП 4. После завершения измерения АЦП 4 выставляет сигнал готовности, который сигналом с первого выхода блока 6 сопряжения читается по адресу 1 через буферный элемент 7. ЭВМ вводит дан- , ные сигналом ВВОД по адресу 2 и одновременно сигналом низкого уровня с второго выхода блока 6 сопряжения через элемент И 10 устанавливает первый триггер 12 в единичное состояние и АЦП 4 переводится опять в режим Гашение. Тем самым подготавливается работа устройства для последующего ввода информации.

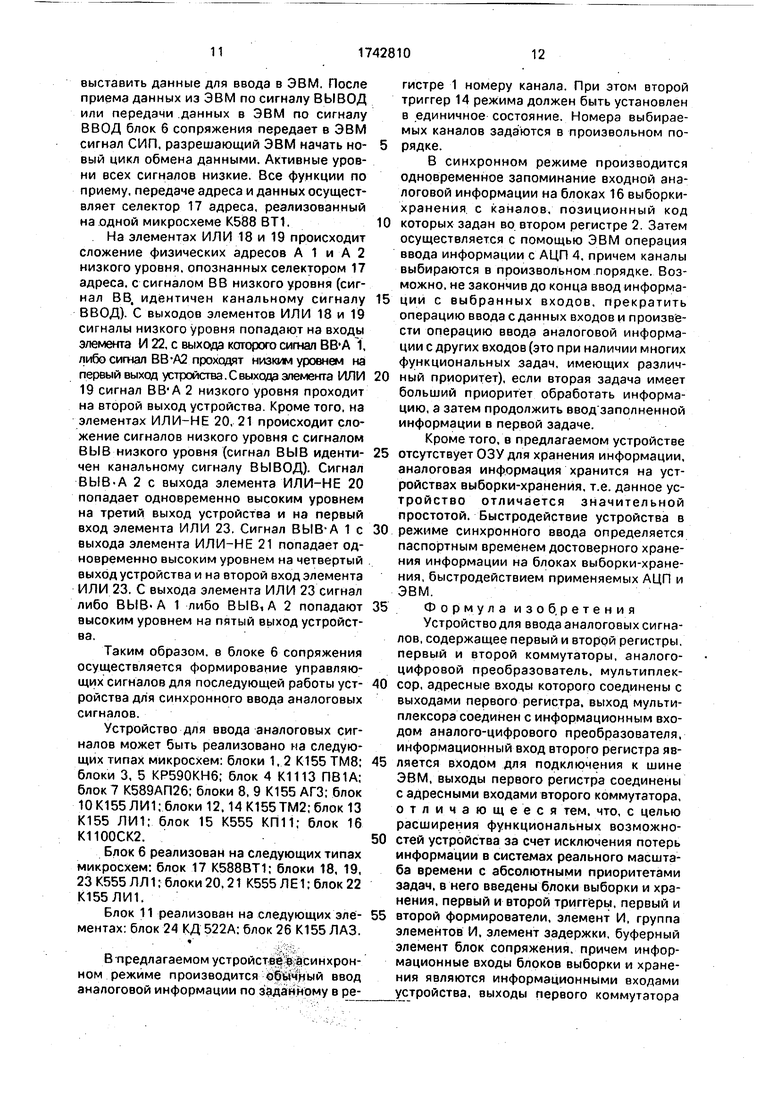

Работа устройства во втором режиме (режим синхронного ввода аналоговых сигналов рассматривают на примере каналов 2,3,5, 7). Для этого необходимо с четвертого выхода блока 6 сопряжения выдать сигнал высокого уровня (записью соответствующего кода по адресу 1). При этом во второй регистр 2 заносится позиционный код выбираемых каналов и одновременно во второй триггер 14 заносится единица (активный уровень низкий) и второй триггер 14 устанавливается в нулевое состояние. При этом оказываются скоммутированными первые входы коммутатора 15. Формат кода, который выдается ЭВМ по адресу 1 в цикле Вы- 5 вод, приведен на фиг.5 (т.е. в восьмеричной форме код 526в). Сигнал с четвертого выхода блока 6 сопряжения поступает на вход второго формирователя 9, который формирует импульс высокого уровня такой длительно0 стью, которая необходима для устойчивой работы блоков 16 выборки-хранения. Этот импульс пройдет через элементы И 13, на первые входы которых поступило разрешение высокого уровня с выходов второго ре5 гистра 2. С выходов элементов И 13 импульсы через соответствующие первые входы коммутатора 15 попадают на соответствующие блоки 16 выборки-хранения (в данном примере 2, 3, 5, 7). На них происхо0 дит одновременная выборка и запоминание аналоговых сигналов. Далее ЭВМ необходимо произвести съем цифровой информации с блоков выборки-хранения. При этом четыре раза необходимо использовать режим 1,

5 причем считывание каналов может идти в произвольном порядке, т.е. по адресу 2 выдать кол втооого канала (число 2s) и ввести код с АЦП 4 в ЭВМ; затем выдать код третьего канала (число Зв) и ввести код с АЦП 4 в

0 ЭВМ; выдать код пятого канала (число 5s) и ввести код с АЦП 4 В ЭВМ; выдать код седьмого канала (число 7в) и ввести код с АЦП 4 в ЭВМ. При этом выход второго триггера 14 находится в состоянии высокого

5 уровня (первый режим). Алгоритм работы во втором режиме приведен на фиг.6 Связь устройства для синхронного ввода аналоговой информации с ЭВМ осуществляется при помощи блока 6 сопряжения.

0 Реализация блока 6 сопряжения определяется интерфейсом, используемым для связи устройства с ЭВМ. При использовании интерфейса МПИ (ОСТ 11.305.903/80) блок 6 сопряжения содержит шестнадцать

5 шин AD 1 - АО 16 для передачи адреса и обмена данными между ЭВМ и периферийными устройствами, т.е. по шинам ADi поочередно передаются коды Адрес и Данные. Кроме того, при обращении к пе0 риферийному устройству (т.е. по адресу большему 160000s) одновременно с адресом устройства ЭВМ вырабатывает сигнал ВУ. В блок 6 сопряжения поступают из ЭВМ также управляющие сигналы интерфейса:

5 сигнал СИА. указывающий, что ЭВМ выставила на шинах ADi адрес абонента; сигнал ВЫВОД, указывающий, что ЭВМ выставила на шинах ADi данные для занесения по ранее заданному адресу; сигнал ВВОД, по которому периферийное устройство должно

выставить данные для ввода в ЭВМ, После приема данных из ЭВМ по сигналу ВЫВОД или передачи данных в ЭВМ по сигналу ВВОД блок б сопряжения передает в ЭВМ сигнал СИП, разрешающий ЭВМ начать новый цикл обмена данными. Активные уровни всех сигналов низкие. Все функции по приему, передаче адреса и данных осуществляет селектор 17 адреса, реализованный на одной микросхеме К588 ВТ1.

На элементах ИЛИ 18 и 19 происходит сложение физических адресов А 1 и А 2 низкого уровня, опознанных селектором 17 адреса, с сигналом ВВ низкого уровня (сигнал ВВ. идентичен канальному сигналу ВВОД). С выходов элементов ИЛИ 18 и 19 сигналы низкого уровня попадают на входы элемента И 22, с выхода которого сигнал ВВ А 1, либо сигнал ВВ-А2 проходят низким уровнем на первый выход устройства. С выхода элемента ИЛИ 19 сигнал ВВ А 2 низкого уровня проходит на второй выход устройства Кроме того, на элементах ИЛИ-НЕ 20, 21 происходит сложение сигналов низкого уровня с сигналом ВЫВ низкого уровня (сигнал ВЫВ идентичен канальному сигналу ВЫВОД). Сигнал ВЫВ-А 2 с выхода элемента ИЛИ-НЕ 20 попадает одновременно высоким уровнем на третий выход устройства и на первый вход элемента ИЛИ 23. Сигнал ВЫВ-А 1 с выхода элемента ИЛИ-НЕ 21 попадает одновременно высоким уровнем на четвертый выход устройства и на второй вход элемента ИЛИ 23. С выхода элемента ИЛИ 23 сигнал либо ВЫВ-А 1 либо BblBiA 2 попадают высоким уровнем на пятый выход устройства.

Таким образом, в блоке 6 сопряжения осуществляется формирование управляющих сигналов для последующей работы устройства для синхронного ввода аналоговых сигналов.

Устройство для ввода аналоговых сигналов может быть реализовано на следующих типах микросхем: блоки 1, 2 К155 ТМ8; блоки 3, 5 КР590КН6; блок 4 К1113 ПВ1А; блок 7 К589АП26; блоки 8, 9 К155 АГЗ; блок 10К155ЛИ1;6локи12.14 К155ТМ2;блок 13 К155 ЛИ1; блок 15 К555 КП11; блок 16 К1100СК2.

Блок 6 реализован на следующих типах микросхем: блок 17 К588ВТ1; блоки 18, 19, 23К555ЛЛ1;блоки20.21 К555 ЛЕ1: блок 22 К155ЛИ1.

Блок 11 реализован на следующих элементах: блок 24 КД 522А: блок 26 К155 ЛАЗ.

В предлагаемом устройстве асинхронном режиме производится обычный ввод аналоговой информации по заданному в регистре 1 номеру канала. При этом второй триггер 14 режима должен быть установлен в единичное состояние. Номера выбираемых каналов задаются в произвольном порядке.

В синхронном режиме производится одновременное запоминание входной аналоговой информации на блоках 16 выборки- хранения с каналов, позиционный код

которых задан во втором регистре 2 Затем осуществляется с помощью ЭВМ операция ввода информации с АЦП 4. причем каналы выбираются в произвольном порядке. Возможно, не закончив до конца ввод информации с выбранных входов, прекратить операцию ввода с данных входов и произвести операцию ввода аналоговой информации с других входов (это при наличии многих функциональных задач, имеющих различный приоритет), если вторая задача имеет больший приоритет обработать информацию, а затем продолжить ввод заполненной информации в первой задаче.

Кроме того, в предлагаемом устройстве

отсутствует ОЗУ для хранения информации, аналоговая информация хранится на устройствах выборки-хранения, т.е. данное устройство отличается значительной простотой. Быстродействие устройства в

режиме синхронного ввода определяется паспортным временем достоверного хранения информации на блоках выборки-хранения, быстродействием применяемых АЦП и ЭВМ.

Формула изобретения

Устройство для ввода аналоговых сигналов, содержащее первый и второй регистры, первый и второй коммутаторы, аналого- цифровой преобразователь, мультиплексор, адресные входы которого соединены с выходами первого регистра, выход мультиплексора соединен с информационным входом аналого-цифрового преобразователя, информационный вход второго регистра является входом для подключения к шине ЭВМ, выходы первого регистра соединены с адресными входами второго коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет исключения потерь информации в системах реального масштаба времени с абсолютными приоритетами задач, в него введены блоки выборки и хранения, первый и второй триггеры, первый и

второй формирователи, элемент И, группа элементов И. элемент задержки, буферный элемент блок сопряжения, причем информационные входы блоков выборки и хранения являются информационными входами

устройства, выходы первого коммутатора

соединены с управляющими входами соответствующих блоков выборки и хранения, выходы которых подключены к информационным входам мультиплексора, выходы второго коммутатора соединены с одной группой информационных входов первого коммутатора, другая группа информационных входов которого подключена к выходам группы элементов И, первые входы которых соединены с выходами второго регистра, а вторые входы - с выходом второго формирователя, выход первого формирователя подключен к информационному входу второго коммутатора и входу элемента задержки, выход которого соединен с синхровходом первого триггера, выход которого подключен к управляющему входу аналого-цифрового преобразователя, выходы которого соединены с информационными входами буферного элемента, выход второго тригге- ра подключен к управляющему входу первого коммутатора, выход элемента И соединен с установочным входом первого триггера, информационный вход которого соединен с шиной логического нуля, первый и второй выходы блока сопряжения соединены соответственно с управляющим входом буферного элемента и вторым входом элемента И, третий выход блока сопряжения подключен к входу первого формирователя и синхровходу первого регистра, пятый выход блока сопряжения соединен с синхровходом второго триггера, четвертый выход блока сопряжения подключен к входу второго формирователя и синхровходу второго регистра, первый вход элемента И, информационный вход второго триггера, информационные входы первого регистра, входы блока сопряжения и выходы буферного элемента являются входами и выходами для подключения к шине ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для ввода информации от аналоговых датчиков | 1988 |

|

SU1578706A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Устройство для контроля напряжения электропитания | 1991 |

|

SU1784982A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

Изобретение относится к вычислительной технике и может быть использовано для ввода аналоговой информации. Цель изо- Ьретений - расширение функциональных возможностей за счет исключения потерь информации в системах реального масшта7 ба времени с абсолютными приоритетами задач . Устройство содержит первый 1-й второй 2 регистры , второй коммутатор 3, последовательно соединенные АЦП 4 и мультиплексор 5. блок сопряжения 6 и буферный элемент 7. первый 8 и второй 9 формирователи, первый элемент И 10, элемент задержки 11. первый триггер 12. группу элементов И 13. второй триггер 14. первый коммутатор 15, блоки выборки-хранения 16. Устройство позволяет осуществлять ввод информации с выбранных входов в произвольном порядке. Можно прекратить операцию ввода с данных входов и произвести операцию ввода с других входов, если эта задача имеет больший приоритет, а затем продолжить ввод аналоговой информации по первой задаче, бил. (Л

Фиг./

/octjpnj пе/ ехлючем режиме

Ф«г. 4

в V S if Ъ Z W

пана канал

/ ajjpjj лерехлючемл /эежи+га

л7 J хьнлла {Ж &)

ггг$ициьмнб/и xej

Put.S

f VA4W J

бидагмия /юуД4. ко JЈЈ/

Зл/гуел M4/J V2-tff хлмсела

Чтени teoffa Jl$ f0M J3M

Зллус /Ц/% // 7-Јj

fJo

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Устройство для ввода информации от аналоговых датчиков | 1986 |

|

SU1381476A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-06-23—Публикация

1990-08-08—Подача